CA3130点击型号即可查看芯片规格书

特征

•MOSFET输入级提供:

-极高ZI=1.5 TΩ(1.5 x 1012Ω)(典型值)

-非常低II. . . . . . . . . . .15V运行时5pA(典型值)

. . . . . . . .. . . . . . . . . . .=2pA(典型值),5V运行

•单电源应用的理想选择

•共模输入电压范围包括负电源轨;输入端子可在负电源轨下摆动0.5V

•CMOS输出级允许信号摆动至任一(或两个)供电轨

•提供无铅加退火(符合RoHS)

应用

•接地参考单电源放大器

•快速采样保持放大器

•长时间计时器/单马厩

•高输入阻抗比较器(与数字CMOS的理想接口)

•高输入阻抗宽带放大器

•电压跟随器(例如,单电源D/A转换器的跟随器)

•电压调节器(允许将输出电压控制在0V以下)

•峰值检测器

•单电源全波精密整流器

•光电二极管传感器放大器

说明

15MHz,带MOSFET输入/CMOS输出的BiMOS运算放大器

CA3130A和CA3130是结合了CMOS和双极晶体管优点的运算放大器。

在输入电路中使用栅极保护P沟道MOSFET(PMOS)晶体管,以提供非常高的输入阻抗、非常低的输入电流和优异的速度性能。在输入级使用PMOS晶体管可使共模输入电压能力降至负电源端子以下0.5V,这是单电源应用中的一个重要特性。

输出电路采用CMOS晶体管对,能够将输出电压摆幅至任一电源电压端子(在很高的负载阻抗值下)的10mV以内。

CA3130系列电路在5V至16V(±2.5V至±8V)的电源电压下工作。它们可以用一个外部电容器进行相位补偿,并且具有用于调整应用的偏移电压的端子需要偏移量为空的功能。终端装置也允许输出级的行程。

•与CA3130相比,CA3130A具有更好的输入特性。

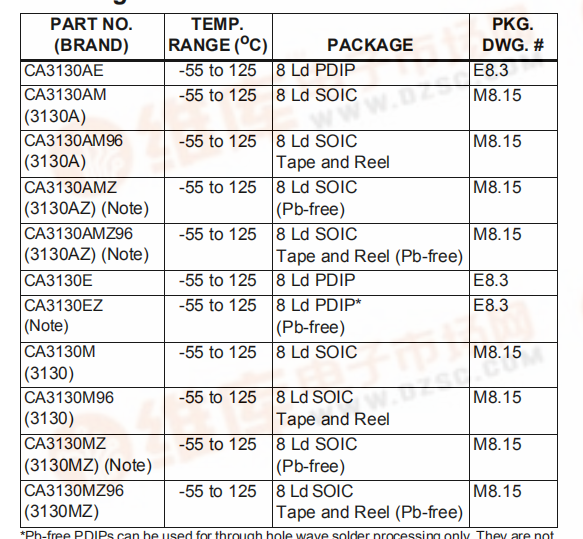

订购信息

*无铅PDIPs只能用于通孔波焊料加工。它们不适用于回流焊工艺应用。

注:Intersil无铅+退火产品采用特殊的无铅材料组;模塑料/模具连接材料和100%哑光镀锡板终饰,符合RoHS标准,并与SnPb和无铅焊接操作兼容。Intersil无铅产品在无铅峰值回流焊温度下分类为MSL,满足或超过IPC/JEDEC J STD-020的无铅要求。

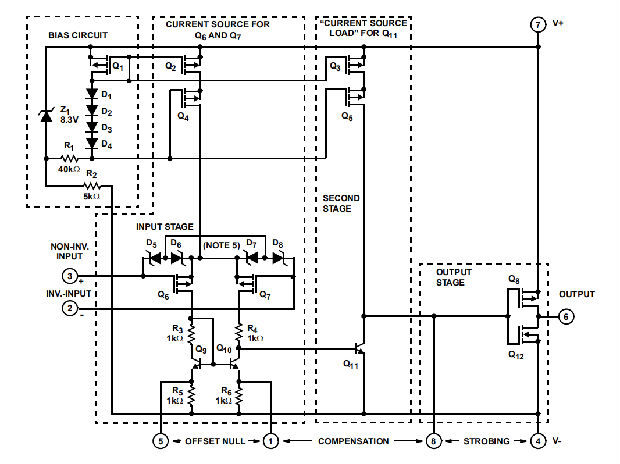

原理图

注:二极管D5到D8为MOSFET输入级提供栅氧化保护。

应用程序信息

电路说明

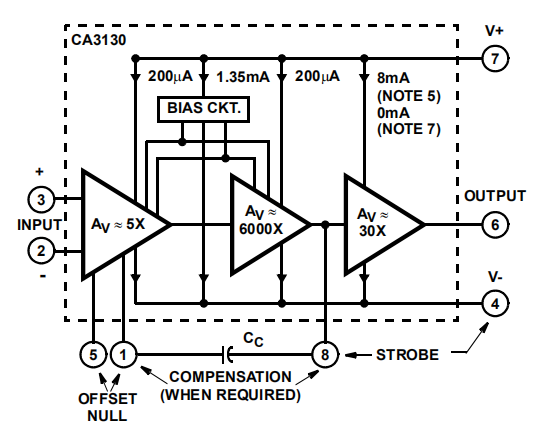

图1是CA3130系列CMOS运算放大器的框图。在许多应用中,输入端子可以在负电源轨下工作到0.5V,输出可以非常接近任一电源轨。因此,CA3130系列电路是单电源运行的理想选择。三个A级放大器级,具有图1所示的单独增益能力和电流消耗,提供CA3130的总增益。偏压电路提供两个电位供第一级和第二级共同使用。

端子8既可用于相位补偿,也可用于将输出级选通至静止状态。当端子8通过机械或电气方式连接到负极供电轨(端子4)时,端子6处的输出电位基本上上升到端子7处的正极供电轨电位。只有当放大器的欧姆负载电阻非常高时(例如,当放大器输出用于驱动比较器应用中的CMOS数字电路时),才能实现在频闪“关”状态下的输出级中基本上零电流漏的条件。

输入级

CA3130的电路如原理图所示。它包括一个差分输入级,使用PMOS场效应晶体管(Q6,Q7)工作在一对镜像双极晶体管(Q9,Q10)中,作为负载电阻与电阻R3到R6一起工作。

镜对晶体管还用作差分单端转换器,为第二级双极晶体管(Q11)提供基极驱动。如果需要,可以通过在端子1和5之间连接100000Ω电位计和将电位计滑臂连接到端子4来实现偏移零位。

笔记:

1、总电源电压(指示电压增益)=15V,输入端子偏置,使端子6的电压高于端子4+7.5V。

2、总电源电压(指示电压增益)=15V,输出端驱动至任一电源轨。

图1:CA3130系列框图

级联型PMOS晶体管Q2、Q4是输入级的恒流源。随后描述了恒流源的偏置电路。

小二极管D5到D8提供栅氧化层保护,防止高压瞬变,包括处理Q6和Q7时的静电。

第二阶段

CA3130中的大部分电压增益由第二级放大器提供,该级放大器由双极晶体管Q11及其由PMOS晶体管Q3和Q5提供的级联连接负载电阻组成。随后描述了这些PMOS晶体管的偏置电位的来源。米勒效应补偿(滚脱)是通过在端子1和8之间连接一个小电容来实现的。在大多数应用中,47pF电容器为稳定的单位增益操作提供足够的补偿。

偏压源电路

在总电源电压略高于8.3V时,电阻器R2和齐纳二极管Z1用于在串联电路(包括电阻器R1、二极管D1到D4和PMOS晶体管Q1)上建立8.3V的电压。电阻器R1和二极管D4交界处的抽头为PMOS晶体管Q4和Q5相对于端子7提供约4.5V的栅极偏置电位。通过二极管连接的PMOS晶体管Q1相对于端子7产生约2.2V的电势,为PMOS晶体管Q2和Q3提供栅极偏置。应注意,Q1与Q2和Q3均为“镜像连接(见注8)”。由于晶体管Q1、Q2、Q3被设计为相同,因此Q1中的约200μA电流在Q2和Q3中分别建立类似的电流作为第一级和第二级放大器的恒定电流源。

在总电源电压略低于8.3V时,齐纳二极管Z1变为非导体,并且在串联的R1、D1-D4和Q1上产生的电势直接随电源电压的变化而变化。因此,Q4、Q5和Q2、Q3的栅极偏置随电源电压变化而变化。这种变化会导致总电源电压低于8.3V时的电源抑制比(PSRR)下降。总电源电压低于4.5V时的工作会导致性能严重下降。

输出级

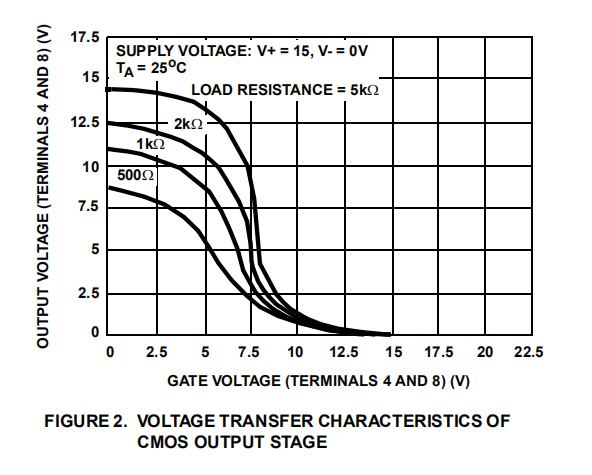

输出级由一个使用在a级模式下工作的CMOS晶体管的漏载反向放大器组成。当在非常高的电阻负载下工作时,输出可以在任一供电轨的毫伏范围内摆动。由于输出级是漏极加载放大器,其增益取决于负载阻抗。图2显示了返回到负供电轨的负载的输出级的传输特性。典型的运算放大器负载很容易由输出级驱动。由于大的信号漂移是非线性的,需要反馈才能实现良好的波形再现,因此可能会遇到瞬时延迟。作为电压跟随器,放大器可以实现0.01%精度等级,包括负供电轨。

注:有关线性电路应用中CMOS晶体管对特性的一般信息,请参阅CA3600E“CMOS晶体管阵列”数据表619号文件。

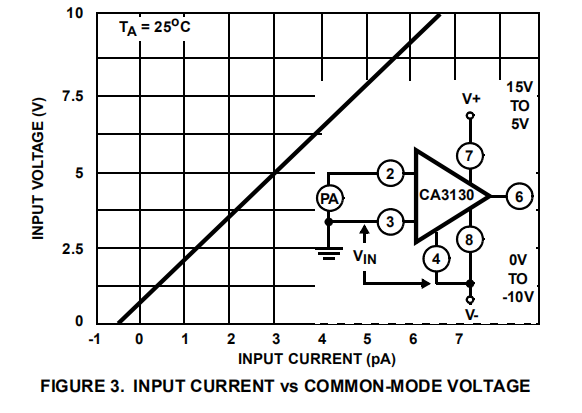

输入电流随共模输入电压的变化

如电气规格表所示,当端子2和3相对于负极电源端子4处于+7.5V的共模电位时,CA3130系列运算放大器的输入电流在TA=25oC时通常为5pA。图3包含的数据显示了在TA=25oC时输入电流随共模输入电压的变化。这些数据表明,如果共模输入电压不超过2V,电路设计者可以有利地利用这些特性来设计通常需要小于1pA的输入电流的电路,输入电流本质上是通过输入电路中的栅极保护二极管的泄漏电流的结果,因此是外加电压的函数。虽然玻璃端子对金属外壳绝缘体的有限电阻也有助于增加漏电流,但有一些有用的补偿因素。由于栅极保护网络的功能就好像它连接到端子4电位,并且CA3130的金属外壳也在内部连接到端子4,因此输入端子3基本上是“保护”免受杂散泄漏电流的影响。

偏移零位

偏置电压调零通常用100,000Ω电位计连接在端子1和5并将电位计滑臂连接至端子4。通常,当滑臂位于电位器总量程的中点时,可以进行微调。

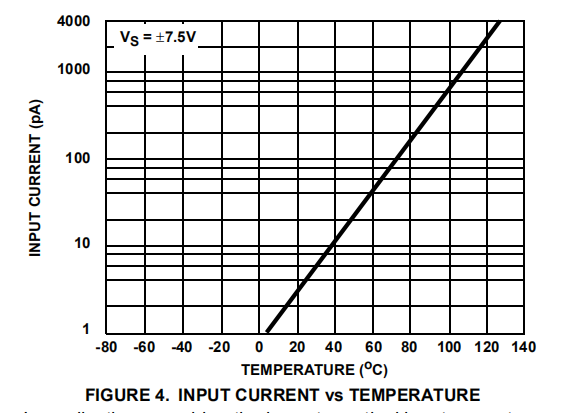

输入电流随温度变化

在25摄氏度时,CA3130系列电路的输入电流通常为5安培。输入电流的主要部分是由于通过输入电路中的栅极保护二极管的泄漏电流。与任何半导体结器件一样,包括带有结场效应管输入级的运算放大器,每升高10摄氏度,泄漏电流大约增加一倍。图4提供了输入偏置电流随CA3130温度变化的典型数据。

在需要最低实际输入电流和因“预热”效应而增加电流的应用中,建议在CA3130中使用适当的散热器。此外,当“下沉”或“源极”显著输出电流时,芯片温度升高,导致输入电流增加。在这种情况下,散热也可以非常显著地减少和稳定输入电流的变化。

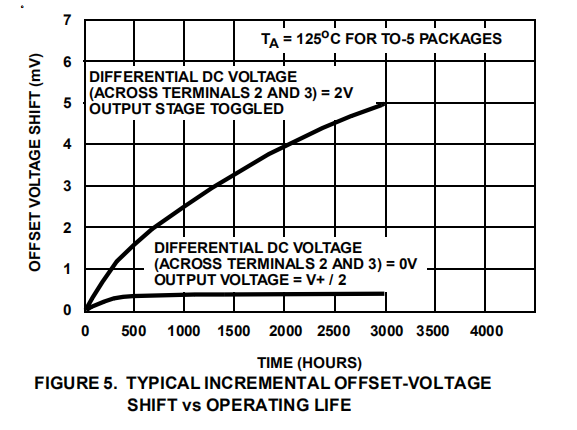

输入偏置电压(VIO)随直流偏压和器件工作寿命的变化

众所周知,当在MOSFET器件上施加直流栅源偏压时,器件的特性会发生微小的变化。这种变化的幅度在高温下增加了。如果装置的应用涉及在高温下的扩展操作,并且在端子2和3上施加显著的差分直流偏置电压,则CA3130的用户应警惕这种影响的可能影响。图5显示了与CA3130器件(金属罐封装)在寿命试验期间遇到的偏移电压偏移有关的典型数据。在较低的温度下(金属罐和塑料罐),例如在85℃时,电压的这种变化要小得多。在差分电压小且对称的典型线性应用中,这些增量变化的幅度与采用双极晶体管输入级的运算放大器中遇到的变化的幅度大致相同。2VDC差分电压示例表示放大器输出级“切换”时的条件,例如,在比较器应用中。

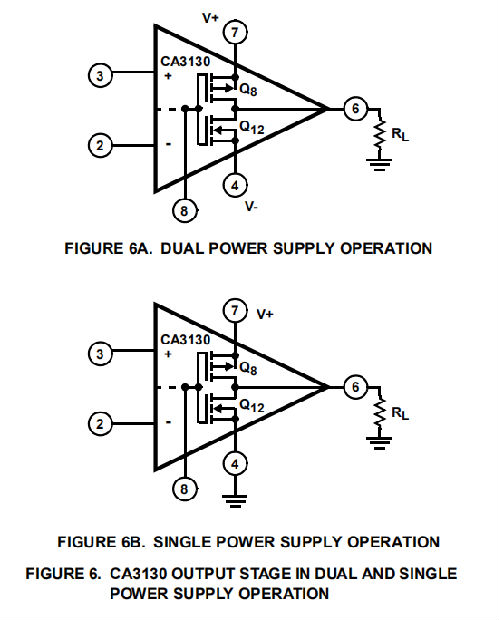

电源注意事项

由于CA3130在单电源应用中非常有用,因此有必要回顾与单电源和双电源服务下的电源电流消耗有关的一些注意事项。图6A和6B显示了为双电源和单电源操作连接的CA3130。

双电源操作:当6号端子的输出电压为0V时,两个电源提供的电流相等。当Q和Q的栅极端子相对于地的驱动越来越正时,通过Q12(从负电源)到负载的电流增加,通过Q8(从正电源)的电流相应减少。当Q8和Q12的栅极端子相对于地面的驱动越来越负时,流过Q8的电流增加,流过Q12的电流相应减少。

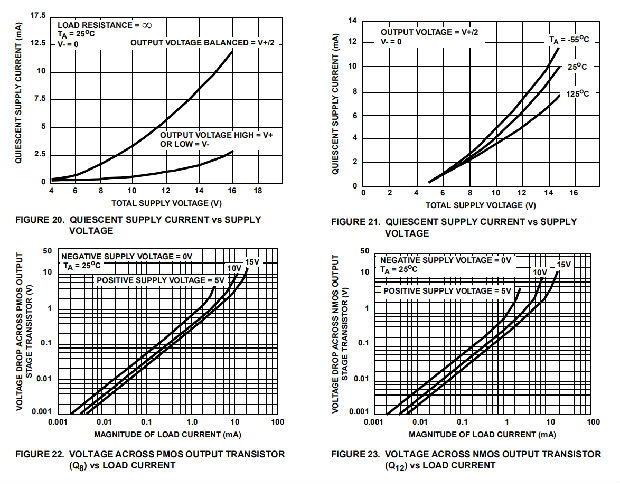

单电源操作:最初,假设RL的值很高(或断开),并且输入端偏压(端子2和3)使得输出端(6号)电压为V+/2,即Q8和Q12之间的电压降大小相等。图20显示了在这些条件下运行的CA3130的典型静态电源电流和电源电压。由于输出级作为a级放大器工作,只要晶体管在其电压传输特性的线性部分工作,在动态工作条件下,电源电流将保持恒定(见图2)。如果Q8或Q12从它们的线性区域向截止(一个非线性区域)摆动,则供电电流将相应减少。在极端情况下,例如,当端子8向下摆动至地电位(或与地连接)时,NMOS晶体管Q12被完全切断,并且到串联晶体管Q8、Q12的电源电流基本上归零。然而,CA3130中的前两个阶段,即使输出阶段被触发,仍会继续吸引适度的供电电流(参见图20中的下曲线)。图6A显示了输出级的双电源配置,通过将端子8的电位拉低到端子4的电位,该输出级也可以被选通。

现在假设在图6B的电路中的端子6和接地之间连接了标称值的负载电阻(例如,2kΩ)。再次假设输入端子偏置(端子2和3)使得输出端子(6号)电压为V+/2。由于PMOS晶体管Q现在必须同时向R和晶体管Q提供静态电流,因此在这些条件下,电源电流必须作为R量级的反函数而增加,这一点应该是显而易见的。图22显示了在几个电源电压下,PMOS晶体管Q的电压降与负载电流的函数关系。图2显示了几个负载电阻值下输出级的电压传输特性。

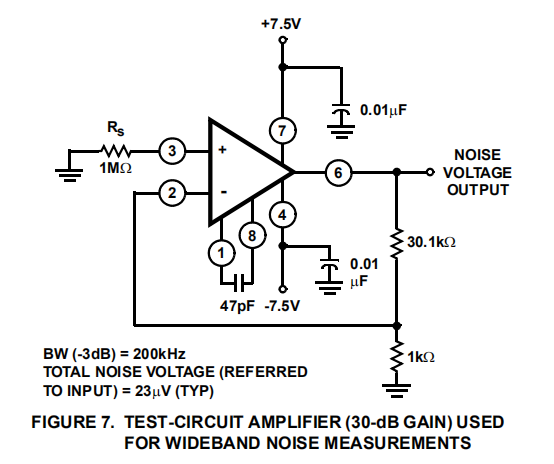

宽带噪声

从低噪声性能考虑的角度来看,在输入信号的源电阻约为1MΩ或更大的应用中,使用CA3130最为有利。在这种情况下,当图7的测试电路放大器在15V的总电源电压下工作时,总输入参考噪声电压通常仅为23μV。尽管源电阻的值提高了一个数量级,但总输入参考噪声的值基本上保持不变。这种特性是由于输入电容的电抗成为分流源电阻的一个重要因素。然而,应该注意的是,对于远大于1MΩ的源电阻值,产生的总噪声电压可以由反馈电阻和源电阻的热噪声贡献控制。

典型应用

电压跟随器

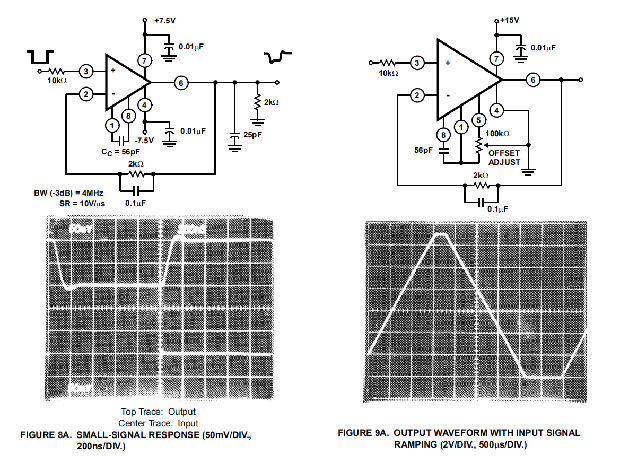

具有很高输入电阻的运算放大器,如CA3130,特别适合用作电压跟随器。图8显示了典型电压跟随器的电路,以及在分体式电源配置中使用CA3130的相关波形。

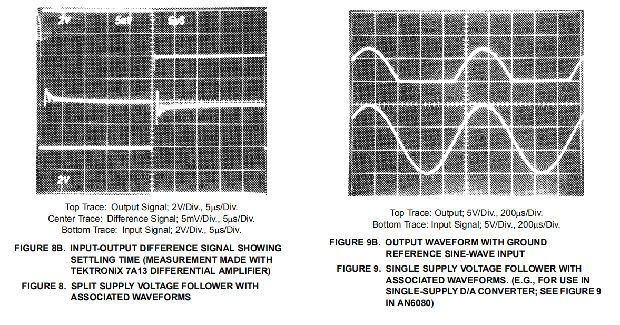

图9显示了一个电压跟随器,由一个电源操作,以及相关的波形。该跟随器电路在宽动态范围内是线性的,如图9A中输出波形的再现和输入信号的斜坡所示。图9B中的波形表明,即使输入在地电位以下摆动7.5V,跟随器也不会失去对输出相位的输入。这种独特的特性是运算放大器和比较器应用中的一个重要特性。图9B还显示CMOS输出级允许输出信号向下摆动到负电源轨电位(即,在所示情况下接地)的方式。后面描述的数模转换器(DAC)电路说明了CA3130在单电源电压跟随器应用中的实际应用。

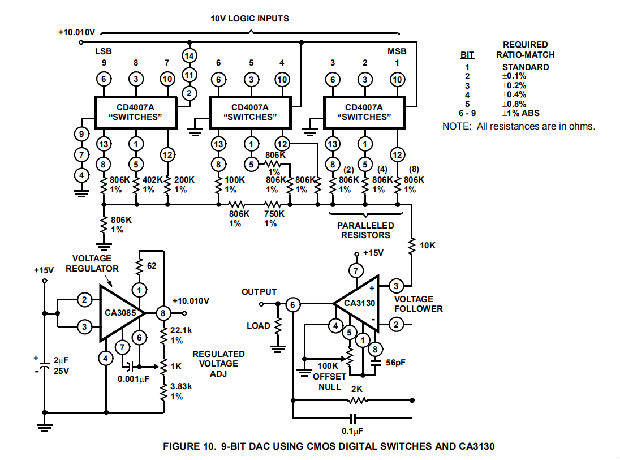

9位CMOS DAC

9位数模转换器(DAC)的典型电路如图10所示。该系统结合了多开关CMOS lCs、低成本的离散金属氧化物薄膜电阻梯形网络、作为跟随器连接的CA3130运放和简单的单电源配置中的廉价单片调节器的概念。DAC的另一个特点是它易于与CMOS输入逻辑接口,例如,图10的电路中使用了10V的逻辑电平。

该电路采用R/2R电压梯形网络,其输出电位直接通过将梯形臂端接在正极或负极电源端子上获得。每个CD4007A包含三个“反相器”,每个“反相器”作为单极双掷开关在正负电源终端处终止R/2R网络的一个臂。电阻梯是一个1%公差的金属氧化膜电阻的组件。需要最高精度的五个臂由来自同一制造批次的806000Ω电阻器的串联和并联组合装配而成。

单个15V电源为CA3130跟随放大器提供一条正极总线,并为CA3085电压调节器供电。调节器输出控制提供“刻度调整”功能,在该系统中设置为标称10V电平。线路电压调节(约0.2%)允许在电源电压变化数伏的情况下保持9位精度。CMOS积木所提供的灵活性简化了针对特定需求的DAC系统的设计。

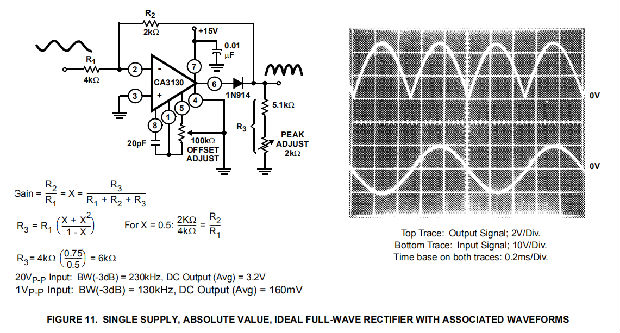

单电源,绝对值,理想全波整流器

使用CA3130的绝对值电路如图11所示。在正偏移过程中,输入信号通过反馈网络直接反馈到输出端。同时,输入信号的正偏移也驱动反向放大器的输出端子(6号)负偏移,使得1N914二极管有效地从信号路径断开放大器。在输入信号的负向漂移过程中,CA3130用作增益等于-R/R的正常反向放大器。当满足图11所示两个等式的等式时,全波输出是对称的。

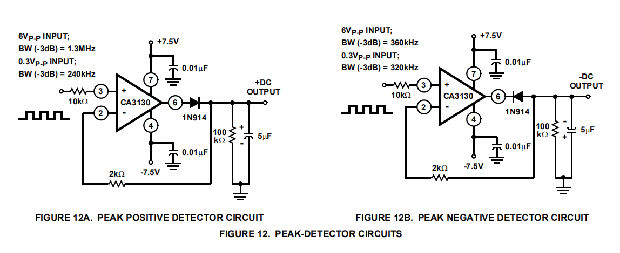

峰值检测器

峰值检测电路很容易用CA3130实现,如图12所示,峰值正电路和峰值负电路。需要注意的是,对于大信号输入,峰值负电路的带宽远小于峰值正电路的带宽。在这种情况下,CA3130的第二级限制带宽。负向输出信号偏移要求在晶体管Q的集电极处有一个正向信号偏移,该集电极在该模式下由相关电路的本征电容加载。另一方面,在Q的集电极处的负向信号漂移期间,晶体管以有源“下拉”模式工作,这样本征电容可以更快地放电。

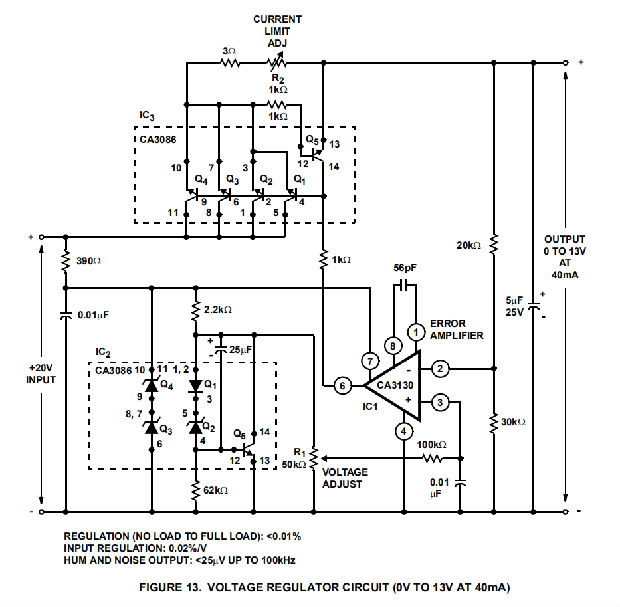

稳压电源中的误差放大器

CA3130是稳压电源中误差放大器的理想选择,因为当稳压输出电压接近零时,它可以作为误差放大器使用。图13显示了一个40mA电源的原理图,该电源能够通过在0V到13V范围内的连续调整提供调节输出电压。lC2(一个CA3086晶体管阵列lC)中的Q3和Q4起齐纳的作用,为CA3130比较器(IC1)提供电源电压。IC2中的Q1、Q2和Q5被配置为误差放大器的可调参考电压的低阻抗、温度补偿源。lC3(另一个CA3086晶体管阵列lC)中的晶体管Q1、Q2、Q3和Q4作为串通元件并联。根据电阻器R2的调整,lC3中的晶体管Q5通过将基极驱动从串联晶体管转移而起限流装置的作用。

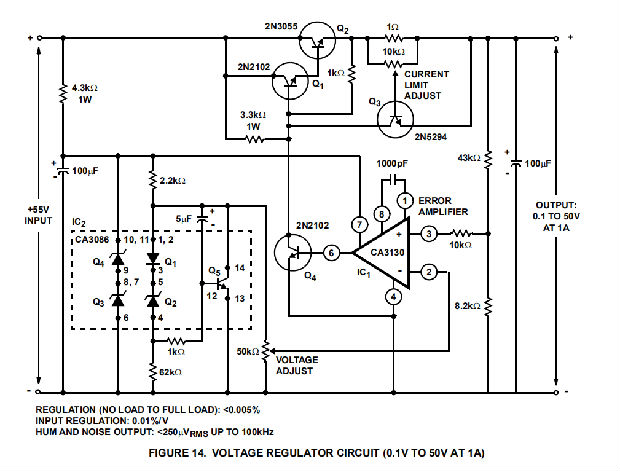

图14包含一个稳压电源的原理图,该稳压电源能够通过在0.1V到50V的范围内连续调节提供稳压输出电压,电流可达1A。误差放大器(lC1)和与lC2相关的电路如前所述,尽管lC1的输出由分立晶体管(Q4)增强,以为Darlingtonconnected串联通晶体管Q1、Q2提供足够的基极驱动。晶体管q3在前面描述的限流电路中起作用。

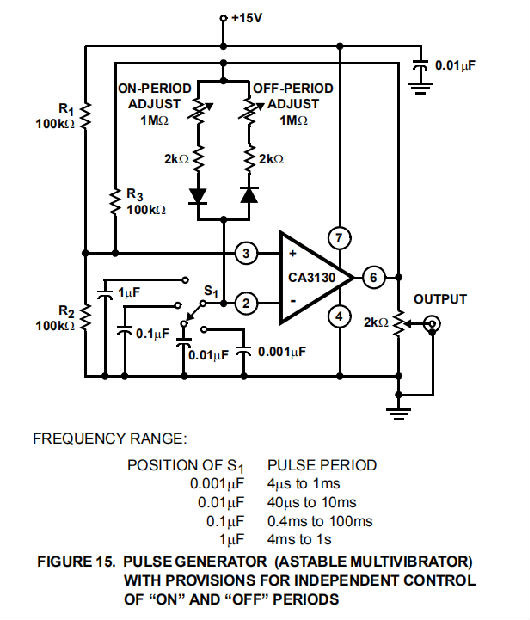

多谐振荡器

CA3130具有极高的输入电阻,这是多谐振荡器电路设计的一个吸引人的特点,因为它允许使用具有高R/C比的定时电路。图15所示为脉冲发生器(非稳态多谐振荡器)的电路图,其中规定了“开”和“关”周期的独立控制。电阻器r1和R2用于将CA3130偏置到电源电压的中点,R3是反馈电阻器。通过将S1定位到所需位置来选择脉冲重复率,并且当调整确定“接通周期”和“断开周期”的电阻器时,脉冲重复率基本保持恒定。

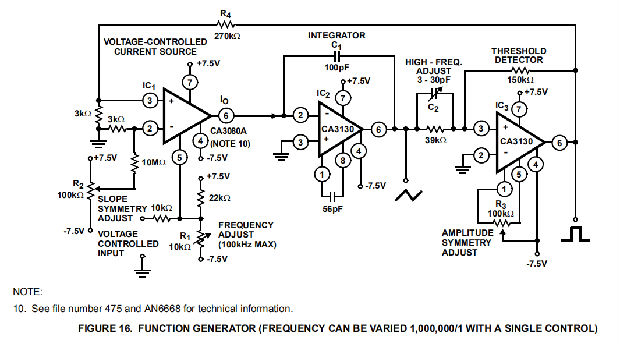

函数发生器

图16包含使用积分器和阈值检测器功能中的CA3130的函数生成器的示意图。该电路产生一个三角波或方波输出,可通过一个单独的控制R扫过1000000:1范围(0.1Hz至100kHz)。电压控制输入也可用于远程扫频控制。

频率测定系统的核心是一个操作跨导放大器(OTA)(见注10),lC1,作为压控电流源工作。输出IO是使用CA3130直接施加到积分器lC2的反馈回路中的积分电容C1的电流,以提供三角波输出。电位器R2用于调节电路的正、负向信号漂移的斜率对称性。

另一个CA3130,IC3,被用作一个控制开关来设置积分器电路三角形输出的偏移极限。电容器C2是优化电路高频方波性能的“调峰”。

电位器R3可调,以完善方波输出信号的“振幅对称性”。阈值检测器的输出通过电阻R4反馈到lC1的输入,以便在产生线性三角波时将电流源从正切换到负。

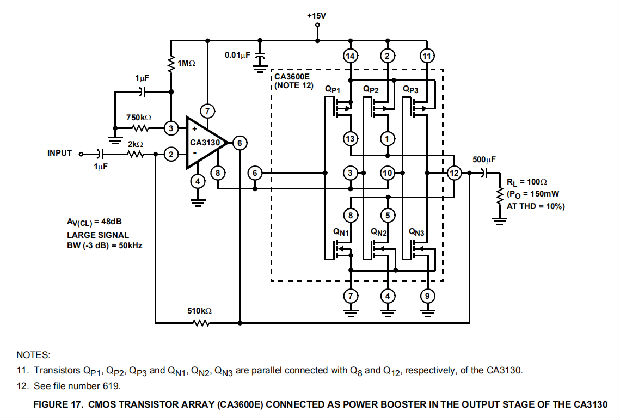

带输出级功率增压器的操作

CA3130输出级的电流源和下沉能力易于补充,以提供功率提升能力。在图17的电路中,一个CA3600E(见注12)lC阵列中的三个CMOS晶体管对与CA3130中的输出级并联。在所示的CA3600E的A级模式下,典型装置在15V运行时消耗20mA的电源电流。这种安排将CA3130输出级的当前处理能力提高约2.5倍。

图17中的放大器电路利用反馈建立48dB的闭环增益。典型的大信号带宽(-3dB)为50kHz。

注:技术信息见619号文件。

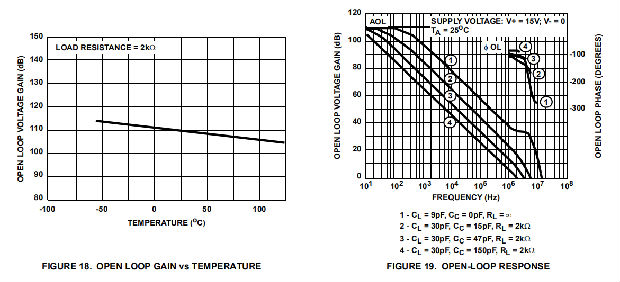

典型性能曲线

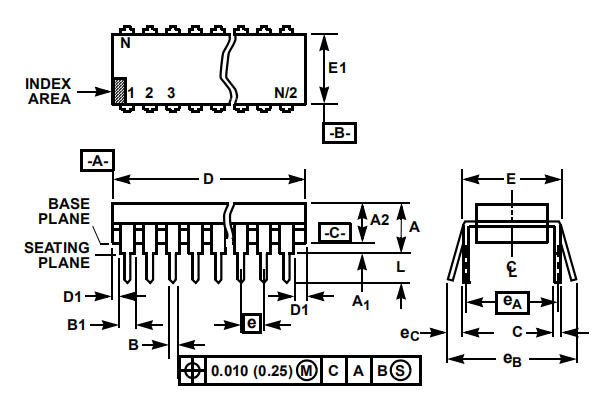

双列直插式塑料包装(PDIP)

笔记:

1、 控制尺寸:英寸。如果英制尺寸和公制尺寸之间存在冲突,则以英制尺寸为准。

2、 尺寸和公差符合ANSI Y14.5M-1982。

3、 符号定义见第95号出版物第2.2节“MO系列符号列表”。

4、 尺寸A、A1和L是在机组位于JEDEC座面规GS-3中时测量的。

5、 D、D1和E1尺寸不包括模具飞边或保护件。模子飞边或突出物不得超过0.010英寸(0.25毫米)。

6、 E和测量时,导线必须与基准面垂直。

7、 eB和eC是在导线端部测量的,导线为uncon 粗酶必须为零或更大。

8、 B1最大尺寸不包括坝筋突出。坝条突出物不得超过0.010英寸(0.25毫米)。

9、 N是终端位置的最大数目。

10、 E8.3、E16.3、E18.3、E28.3、E42.6的拐角导线(1、N、N/2和N/2+1)的B1尺寸为0.030-0.045英寸(0.76-1.14毫米)。

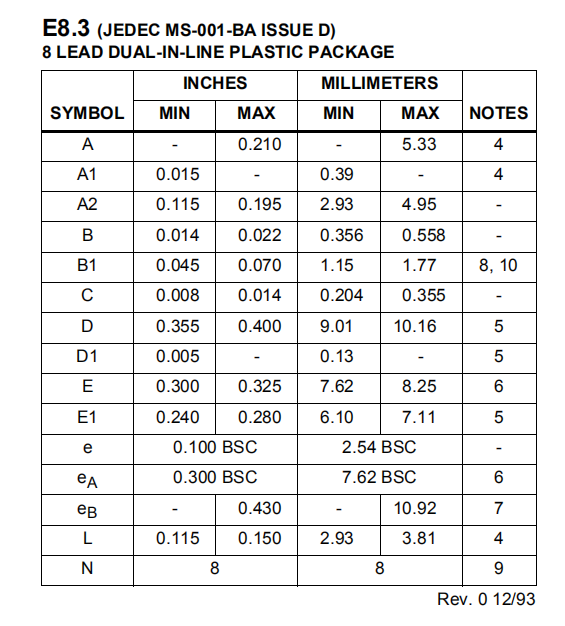

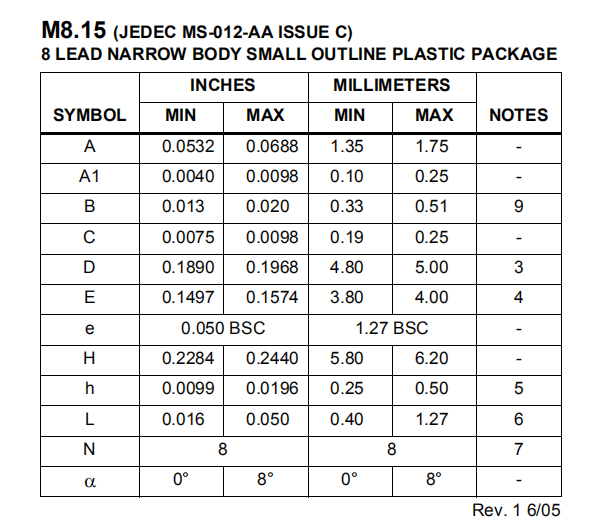

小外形塑料包装(SOIC)

笔记:

1、符号在95号出版物第2.2节的“MO系列符号列表”中定义。

2、尺寸和公差符合ANSI Y14.5M-1982。

3、尺寸“D”不包括模具飞边、突出物或浇口毛刺。模具飞边、凸出和浇口毛刺每侧不得超过0.15mm(0.006英寸)。

4、尺寸“E”不包括读写间隙或突出部分。每侧的间隙闪光和突起不得超过0.25 mm(0.010英寸)。

5、主体上的倒角是可选的。如果不存在,则视觉索引功能必须位于交叉阴影区域内。

6、“L”是焊接到基板的端子长度。

7、“N”是终端位置的数目。

8、显示的端子号仅供参考。

9、在座面上方0.36mm(0.014英寸)或更大的铅宽度“B”不得超过0.61mm(0.024英寸)的最大值。

10、控制尺寸:毫米。换算的英寸尺寸不一定准确。