目录

| 1.作用 |

| 2.工作原理 |

在计算机存储系统的层次结构中,介于中央处理器和主存储器之间的高速小容量存储器。它和主存储器一起构成一级的存储器。高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的,程序员感觉不到高速缓冲存储器的存在,因而它对程序员是透明的。今天将介绍其的作用与工作原理:

高速缓冲存储器(Cache)实际上是为了把由DRAM组成的大容量内存储器都看做是高速存储器而设置的小容量局部存储器,一般由高速SRAM构成。这种局部存储器是面向CPU的,引入它是为减小或消除CPU与内存之间的速度差异对系统性能带来的影响。Cache 通常保存着一份内存储器中部分内容的副本(拷贝),该内容副本是最近曾被CPU使用过的数据和程序代码。

高速缓冲存储器

在计算机技术发展过程中,主存储器存取速度一直比中央处理器操作速度慢得多,使中央处理器的高速处理能力不能充分发挥,整个计算机系统的工作效率受到影响。有很多方法可用来缓和中央处理器和主存储器之间速度不匹配的矛盾,如采用多个通用寄存器、多存储体交叉存取等,在存储层次上采用高速缓冲存储器也是常用的方法之一。很多大、中型计算机以及新近的一些小型机、微型机也都采用高速缓冲存储器。

高速缓冲存储器的容量一般只有主存储器的几百分之一,但它的存取速度能与中央处理器相匹配。根据程序局部性原理,正在使用的主存储器某一单元邻近的那些单元将被用到的可能性很大。因而,当中央处理器存取主存储器某一单元时,计算机硬件就自动地将包括该单元在内的那一组单元内容调入高速缓冲存储器,中央处理器即将存取的主存储器单元很可能就在刚刚调入到高速缓冲存储器的那一组单元内。于是,中央处理器就可以直接对高速缓冲存储器进行存取。在整个处理过程中,如果中央处理器绝大多数存取主存储器的操作能为存取高速缓冲存储器所代替,计算机系统处理速度就能显著提高。

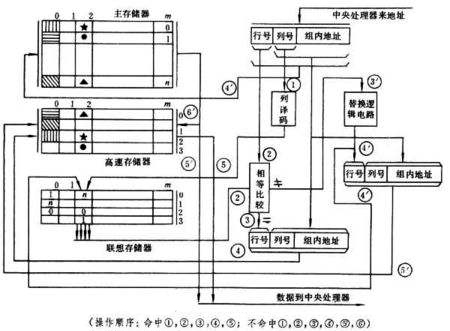

高速缓冲存储器通常由高速存储器、联想存储器、替换逻辑电路和相应的控制线路组成。在有高速缓冲存储器的计算机系统中,中央处理器存取主存储器的地址划分为行号、列号和组内地址三个字段。于是,主存储器就在逻辑上划分为若干行;每行划分为若干的存储单元组;每组包含几个或几十个字。高速存储器也相应地划分为行和列的存储单元组。二者的列数相同,组的大小也相同,但高速存储器的行数却比主存储器的行数少得多。

高速缓冲存储器原理图

联想存储器用于地址联想,有与高速存储器相同行数和列数的存储单元。当主存储器某一列某一行存储单元组调入高速存储器同一列某一空着的存储单元组时,与联想存储器对应位置的存储单元就记录调入的存储单元组在主存储器中的行号。

当中央处理器存取主存储器时,硬件首先自动对存取地址的列号字段进行译码,以便将联想存储器该列的全部行号与存取主存储器地址的行号字段进行比较:若有相同的,表明要存取的主存储器单元已在高速存储器中,称为命中,硬件就将存取主存储器的地址映射为高速存储器的地址并执行存取操作;若都不相同,表明该单元不在高速存储器中,称为脱靶,硬件将执行存取主存储器操作并自动将该单元所在的那一主存储器单元组调入高速存储器相同列中空着的存储单元组中,同时将该组在主存储器中的行号存入联想存储器对应位置的单元内。

当出现脱靶而高速存储器对应列中没有空的位置时,便淘汰该列中的某一组以腾出位置存放新调入的组,这称为替换。确定替换的规则叫替换算法,常用的替换算法有:最近最少使用算法(LRU)、先进先出法(FIFO)和随机法(RAND)等。替换逻辑电路就是执行这个功能的。另外,当执行写主存储器操作时,为保持主存储器和高速存储器内容的一致性,对命中和脱靶须分别处理。