MAX2395 点击型号查看芯片规格书

针对WCDMA/UMTS系统,该应用笔记介绍了在鉴相频率为80kHz时,使用MAX2395的一个优化的环路滤波器设计。参考频率是13MHz或26MHz,而且也展示了误差向量值(EVM)结果。

MAX2395是应用于WCDMA/UMTS发射器中完全单片集成的类似直接变频调制IC。根据该芯片的内部结构,其射频(RF)输出频率是RF本振(LO)频率的5/6倍。该本振频率是由片上整数N分频的PLL产生的。由于WCDMA系统中的栅格频率是200kHz,MAX2395 PLL需要提供240kHz步进频率(即200的6/5倍)。对于WCDMA用户终端应用中最常用的参考频率,如19.2MHz和15.36MHz,内部PLL整数分频器可以分别由80和64很容易地产生240kHz的鉴相频率。Maxim评估板是根据19.2MHz参考频率来设计的。

在UMTS系统中经常用到的13MHz或26MHz参考频率不是240kHz的整数倍,因此需要将MAX2395中PLL使用的鉴相频率减小到一个数,这个数的倍数是240kHz和13/26MHz。对于26MHz晶振来说,鉴相频率通常是80kHz,这就可以通过使用3个80kHz步进频率来获得240kHz信道栅。80kHz PLL频率表示相同本振“N分频”值的3倍,这就导致闭环相位噪声(20logN)增加10dB。

一般说来,由于PLL对EVM的影响与其综合相位误差成正比,所以误差向量值(EVM,error vector magnitude)也会降低。因为鉴相泄露在环路滤波器中的衰减变小,故需要重新设计环路滤波器以平衡综合相位误差、锁定时间和鉴相泄露衰减。

鉴相频率为240kHz的环路滤波器带宽大约是12kHz ,而鉴相频率为80kHz情况下的带宽大约是7kHz。环路滤波器元器件的对应值如下表所示:

表1.

BW = 12kHz, 240kHz comparison freq. | BW = 7kHz, 80kHz comparison freq. |

| C1 = 2.2nF | C1 = 1nF |

| C2 = 22nF | C2 = 10nF |

| R2 = 3.3k欧姆 | R2 = 7.5k欧姆 |

有关无源环路滤波器拓扑,请参考下面原理图(图1)。

图1

在Maxim WCDMA参考设计板上分别使用19.2MHz和26MHz晶振来测试MAX2395的性能。所有测试曲线图如图2至图7所示。

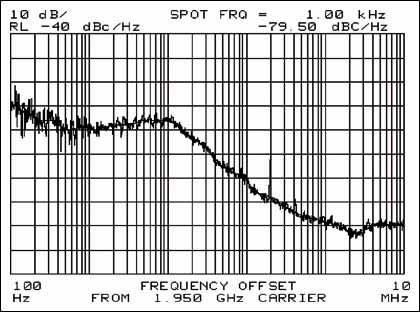

图2. 参考晶振为19.2MHz的相位噪声曲线

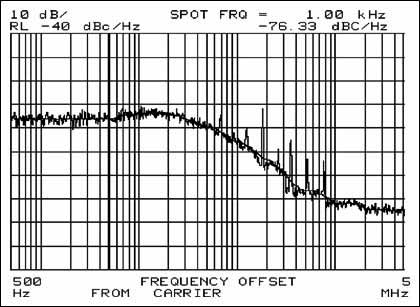

图3. 参考晶振为26MHz的相位噪声曲线

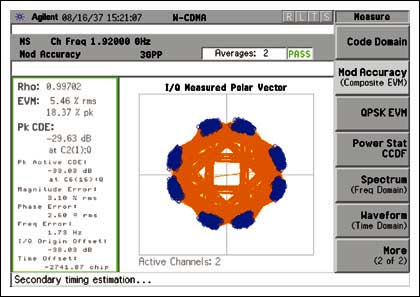

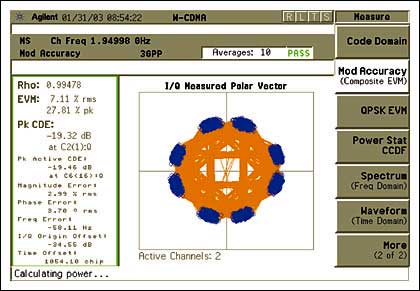

图4. 参考晶振为19.2MHz的RF输出EVM

图5. 参考晶振为26MHz的RF输出EVM

图6. 晶振为19.2MHz时,在60MHz的带宽内跳变时的PLL锁定时间

图7. 晶振为26.0MHz时,在60MHz带宽内跳变时的PLL锁定时间

鉴相频率为240kHz时,从500Hz至1.92MHz的综合相位差是1.98度,鉴相频率为80kHz时则为2.75度。前者在RF输出5.5%的EVM结果,而后者为7.2%。晶振为19.2MHz时,针对60MHz的跳变频率带宽,环路锁定时间为720µs,晶振为26MHz时的锁定时间为820µs。两种情况下的鉴相泄露衰减相似,都约为-40dBc。