晶圆代工巨无霸—台积电TSMC

电子技术

2024-07-09 10:50

1246

0

1988年,英特尔从存储芯片赛道转换到了可以将设计与生产分工的CPU赛道。张忠谋通过私人交情,拿到英特尔的资质认证,拿到了第一笔代工大单。

1994年、1997年台积电分别在中国台湾证券交易所和纽约证券交易所上市。

2000年,台积电收购世大半导体与德基半导体,规模迅速提升。

2001年,台积电率先研制出Cu/Low-K技术,而IBM的技术未能走出实验室。凭借0.13μm的优势,台积电逐渐领先联电并扩大优势。

此前,晶圆代工行业的技术皆出自IBM授权,0.13μm制程攻关阶段,IBM也是业内首个发表Cu/LowK技术的公司,希望向台积电和联电销售该技术,但台积电认为IBM技术并不成熟,因此选择建立自己的研发团队。

台积电的研发成功也意味着IBM技术霸权被终结。十年后, IBM将代工业务转给格芯,退出代工行业。

2009 年,张忠谋以78岁高龄重返台积电应对危机。张忠谋重新执掌台积电后,加大研发投入,实现了28nm制程率先量产(台积电选择后闸级路线,而三星错误的选择了前闸级路线)。

经济下行,下游需求减弱,同时新产线开发艰难,同行竞争激烈(三星通过捆绑销售策略,拿到苹果独家订单;格罗方德成立;...)台积电公司陷入困境。

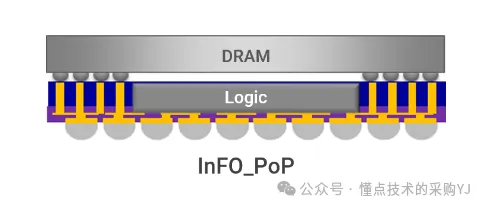

2011年,台积电入局封装行业,开发出了CoWoS与简化版的InFO技术,可让逻辑芯片与DRAM 直连。InFO相比三星的改良PoP技术厚度小30%,满足了苹果对厚度的需求。

2013年开始,台积电为苹果代工并从2016年开始彻底取代三星,成为其唯一代工商。

相较之下英特尔的10nm由于选择了错误的技术路线(放弃使用EUV光刻机,转而选择更为激进的双重曝光和四重曝光技术,引入金属钴作为连接层材料),耗费大量时间,直至2019年Q3才交付首批10nm芯片。而同一时期的台积电已量产 7nm+。

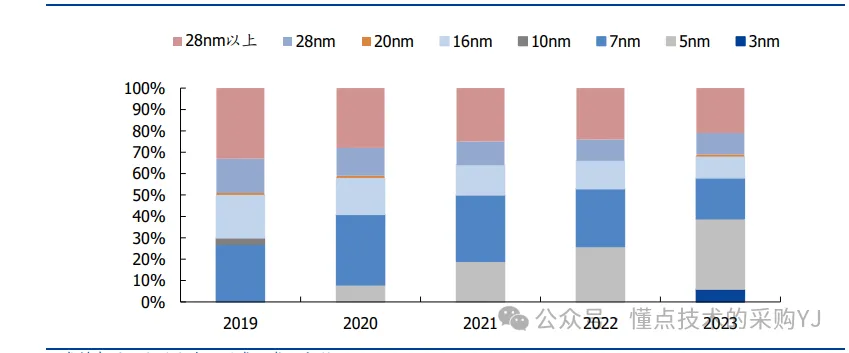

在先进制程市场,台积电已形成垄断地位,10nm以下市场占据9成市场份额。

1,高性能计算 High-Performance Computing Platform

该平台包括:CPUs,GPUs,NPUs,AI accelerators,related-ASICs,搭载于个人电脑、平板电脑、 游戏机、服务器和基站等。

1)提供领先的制程技术和连接技术(射频技术、串行解串器和光互连);

该平台包括各种类型的“智能”联网设备,从可穿戴设备、健康监测器和扬声器到家庭自动化设 备、城市和制造自动化设备。

1)制造记录良好的工艺技术:55纳米ULP、40纳米ULP、28纳米ULP、22纳米ULP/ULL和12FFC+_ULL;

3)提供专业技术,包括增强型射频和模拟、嵌入式非易失性存储器、CMOS图像传感器和MEMS传感器;

3,智能手机 Smartphone Platform

该平台为客户提供领先的工艺技术,如5nm FinFET、6nm FinFET、7nm FinFET Plus和7nm FinFET, 以及针对高端产品应用的全面IP,以进一步提高芯片性能、降低功耗和缩小芯片尺寸。

4,数字消费电子 Digital Consumer Electronics Platform

智能(AI)画质增强、超分辨率提升至8K/4K、语音命令人机界面(HMI)、用于云游戏的120/100Hz 高帧率(HFR)等功能的片上系统(SoC)。

产品包括智能座舱芯片(16nm FinFET、7nm FinFET 技术)、28nm嵌入式闪存、28nm、22nm和16nm 毫米波射频、高灵敏度CMOS图像/激光雷达。

1)用于计算密集型ADAS应用的先进CMOS 技术;

2)用于5G 连接和毫米波 (mmWave)雷达的射频技术;

3)用于下一代微控制器(MCU)和人工智能(AI)存储器的非易失性存储器(NVM)技术;

4)用于高灵敏度CMOS图像/光探测和测距(LiDAR)传感器的CMOS图像传感器(CIS)技术;

5)用于电源管理集成电路(PMIC)的BCD技术;

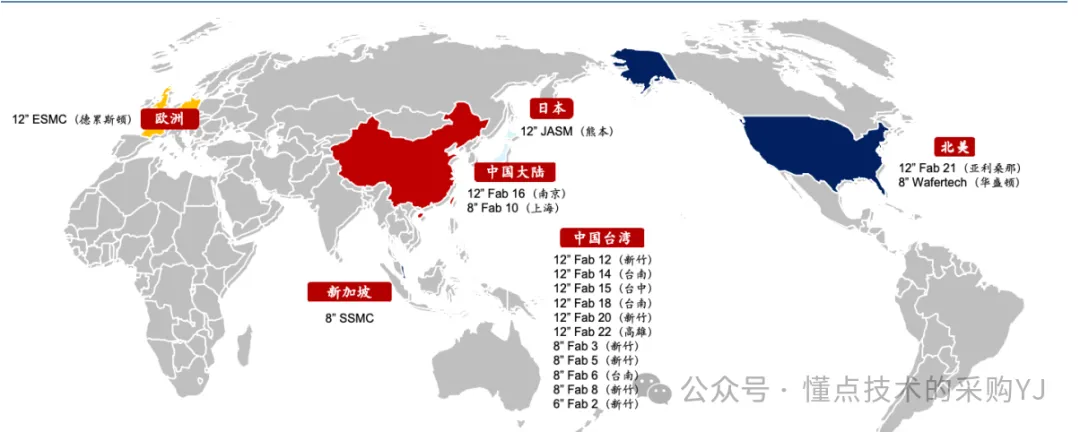

2023年台积电所拥有及管理的年产能超过1600万片。拥有共17座晶圆代工厂(9座12寸、7座8寸、1座6寸),覆盖从3nm先进制程到0.25um以上制程的逻辑芯片代工。

台积电共拥有5座先进封装厂,能够实现CoWoS、SOIC等先进封装技术。

10nm以下先进制程主要由三家公司提供——台积电、三星和英特尔;其中实现3nm制程量产的为台积电和三星。

台积电5nm产品收入占2023年营收的33%,3nm制程(苹果M3、A18 Pro、A17 Pro,AMD Zen5、RDNA 4,高通骁龙8 Gen4,联发科天玑9400,英伟达Blackwell)快速发展,2nm制程进展顺利、有望2025年实现量产。

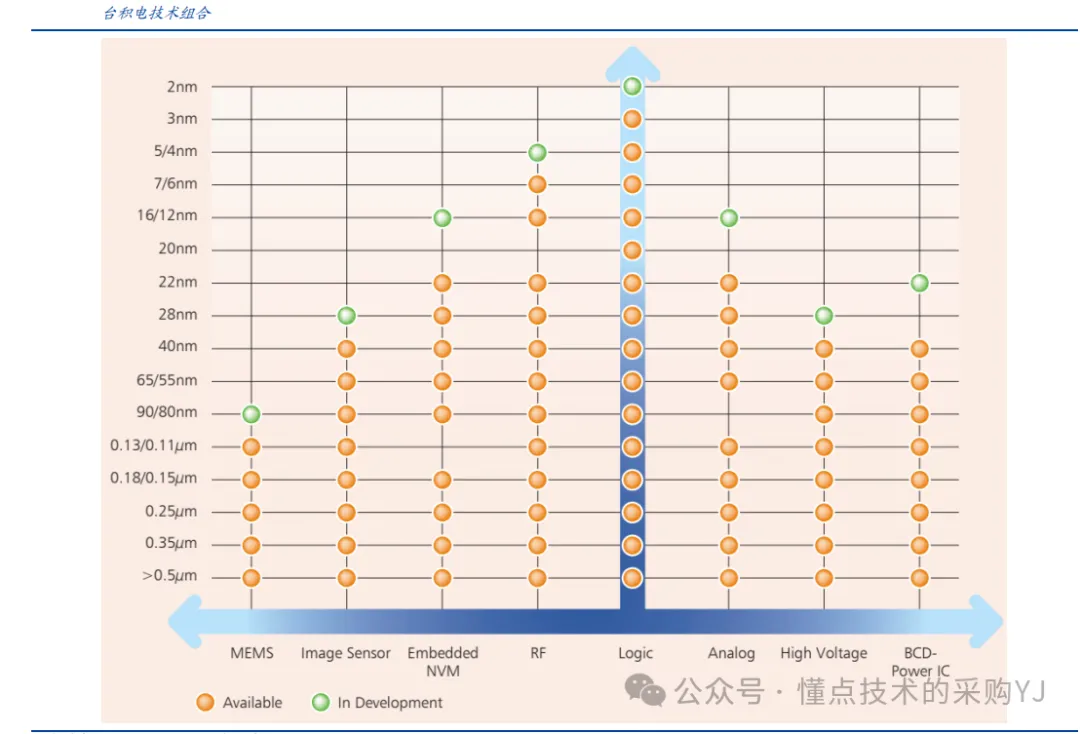

台积电提供包括MEMS、图像传感器、嵌入式非易失性存储 器(eNVM)、射频 RF、模拟(Analog)、高电压(HV)、超低功耗(ULP)和BCD -Power IC等产品。

3D Fabric包含 InFO、CoWoS、SoIC 三种封装形式。

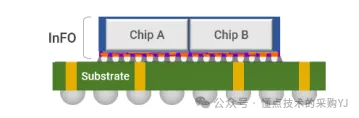

InFO:集成扇出晶圆级封装InFO,InFO具有高密度RDL(再分配层)和TIV(通 过InFOVia),可实现高密度互连和高性能,且成本相对CoWoS 更低,主要用于移动设备。分为 InFO_PoP、InFO_oS、InFO_LSI 三类。

InFO_PoP是业界首款3D晶圆级扇出封装,具有高密度RDL和TIV,可集成移动AP和DRAM封装堆叠,适用于移动应 用。

InFO_oS利用InFO技术,具有更高密度的2/2μmRDL线宽/间距,可集成多个用于5G网络应用的高级逻辑小芯片。

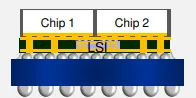

InFO_LSI 用于UH-带宽Chiplet 集成,将SoC芯片与高密度本地硅互连(LSI)和 InFO技术集成。

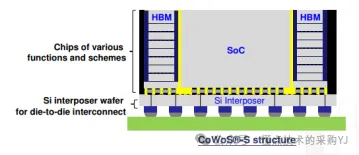

CoWoS:主要用于AI 芯片封装。CoWoS 封装技术主要分为两步:

1)CoW(Chipon-Wafer)实现晶片堆叠:将 SoC芯片与HBM集成在硅中介层。

2)WoS(Waferon-Substrate)将芯片堆叠在基板上:把CoW芯片与基板连接,整合成CoWoS。可以减少芯片的空间、减少功耗和成本。CoWoS为高性能计算应用提供同类最佳的性能和最高的集成密度。具体细分为CoWoS-S、CoWoS-R、CoWoS-L三种细分形式。

CoWoS-S技术用于高级SoC和HBM的硅中介层2.5D系统集成。

登录icspec成功后,会自动跳转查看全文