XC3S50A-4TQG144C点击型号即可查看芯片规格书

XC3S50A-4TQG144C 中文资料规格参数

| 技术参数 | 频率 | 250 MHz |

针脚数 | 144 | |

RAM大小 | 6912 B | |

逻辑门数量 | 50000 | |

输入/输出数 | 108 Input | |

电源电压 | 1.14V ~ 1.26V | |

| 封装参数 | 安装方式 | Surface Mount |

引脚数 | 144 | |

封装 | TQFP-144 | |

| 外形尺寸 | 封装 | TQFP-144 |

| 物理参数 | 工作温度 | 0℃ ~ 85℃ (TJ) |

| 其他 | 产品生命周期 | Active |

包装方式 | Each | |

制造应用 | 通信与网络, 消费电子产品, Consumer Electronics, Communications & Networking, Consumer Electronics, Communications & Networking | |

| 符合标准 | RoHS标准 | RoHS Compliant |

含铅标准 | Lead Free | |

REACH SVHC标准 | No SVHC | |

| 海关信息 | ECCN代码 | EAR99 |

香港进出口证 | NLR |

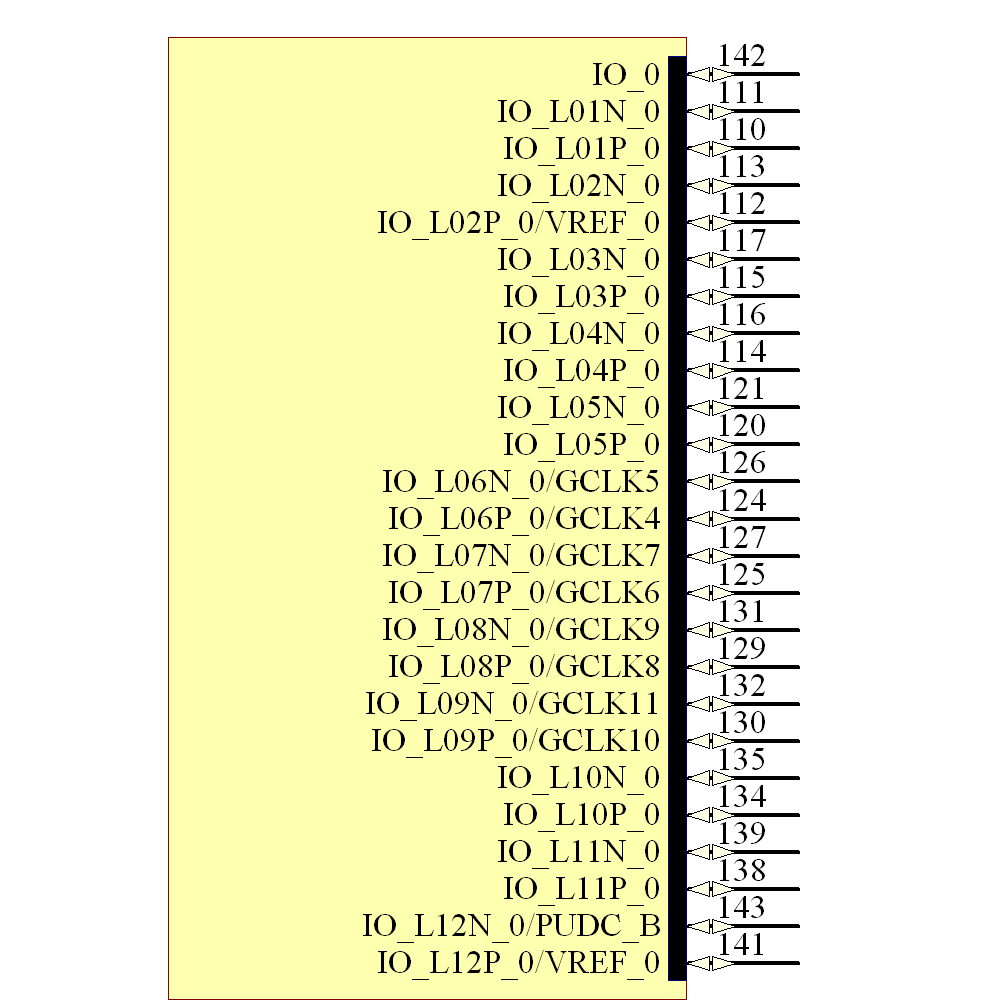

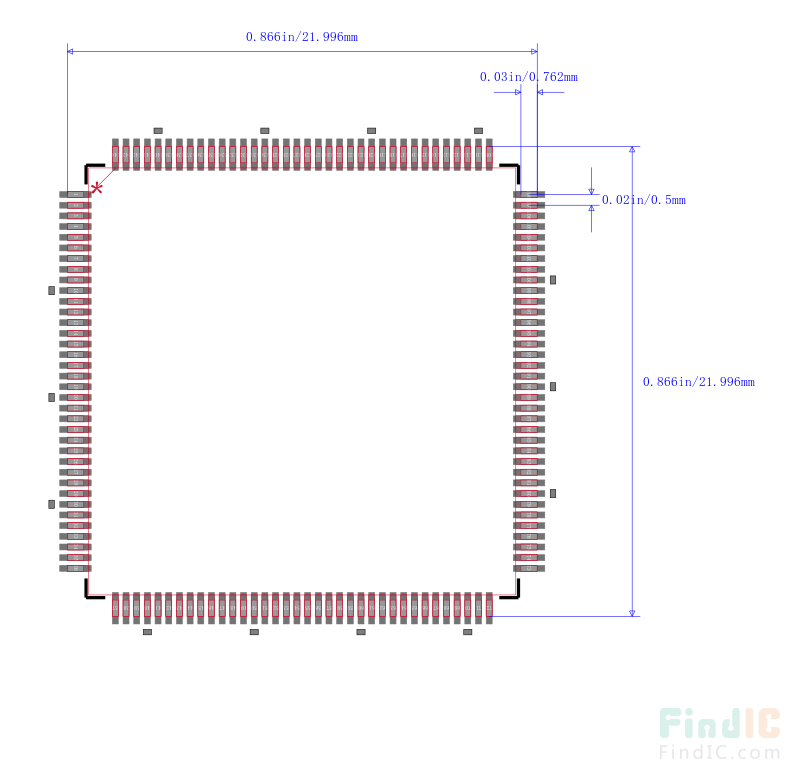

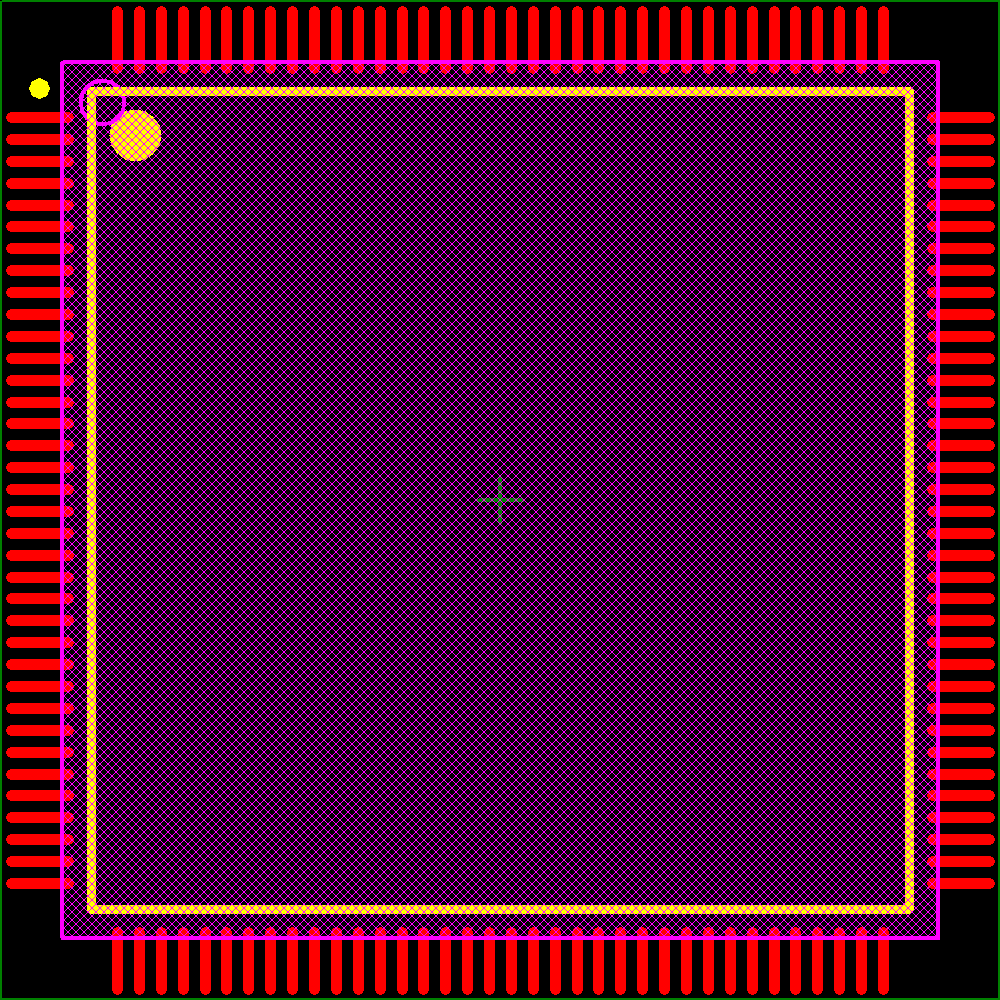

XC3S50A-4TQG144C 引脚图 | 封装图 | 封装焊盘图

XC3S50A-4TQG144C 引脚图

XC3S50A-4TQG144C 封装图

XC3S50A-4TQG144C 封装焊盘图

产品概述

XILINX XC3S50A-4TQG144C 芯片, FPGA, SPARTAN-3A, 50K系统门, 144TQFP

TheXC3S50A-4TQG144Cis a Spartan®-3A FPGA solves the design challenges in most high-volume, I/O-intensive electronic applications. The five-member family offers densities ranging from 50000 to 1.4 million system gates. The Spartan®-3A FPGA is a part of the Extended Spartan-3A family, which also include the non-volatile Spartan®-3AN and the higher density Spartan®-3A DSP FPGAs. This family builds on the success of the earlier Spartan®-3E and Spartan®-3 FPGA families. New features improve system performance and reduce the cost of configuration. This family enhancement, combined with proven 90nm process technology, deliver more functionality and bandwidth per dollar than ever before, setting the new standard in the programmable logic industry. It is a superior alternative to mask programmed ASICs. FPGA avoids the high initial cost, lengthy development cycles and the inherent inflexibility of conventional ASICs and permit field design upgrades.

.Suspend, hibernate modes reduce system power

.Multi-voltage, multi-standard SelectIO™ interface pins

.Abundant, flexible logic resources

.Hierarchical SelectRAM™ memory architecture

.Up to eight Digital Clock Managers (DCMs)

.Eight low-skew global clock networks, eight additional clocks per half device

.Configuration interface to industry-standard PROMs

.CompleteXilinxISE® and WebPACK™ development system software support plus Spartan-3A starter kit

.MicroBlaze™ and PicoBlaze™ embedded processors