MT47H128M16RT-25E:C点击型号即可查看芯片规格书

MT47H128M16RT-25E:C 中文资料规格参数

| 技术参数 | 工作电压 | 1.80 V |

供电电流 | 190 mA | |

针脚数 | 84 | |

时钟频率 | 400 MHz | |

位数 | 16 | |

存取时间 | 2.5 ns | |

存取时间(Max) | 0.4 ns | |

工作温度(Max) | 85 ℃ | |

工作温度(Min) | 0 ℃ | |

电源电压 | 1.7V ~ 1.9V | |

| 封装参数 | 安装方式 | Surface Mount |

引脚数 | 84 | |

封装 | FBGA-84 | |

| 外形尺寸 | 封装 | FBGA-84 |

| 物理参数 | 工作温度 | 0℃ ~ 85℃ |

| 其他 | 产品生命周期 | Unknown |

包装方式 | Tray | |

制造应用 | 计算机和计算机周边, Computers & Computer Peripherals | |

| 符合标准 | RoHS标准 | RoHS Compliant |

含铅标准 | Lead Free | |

REACH SVHC标准 | No SVHC | |

REACH SVHC版本 | 2015/12/17 | |

| 海关信息 | ECCN代码 | EAR99 |

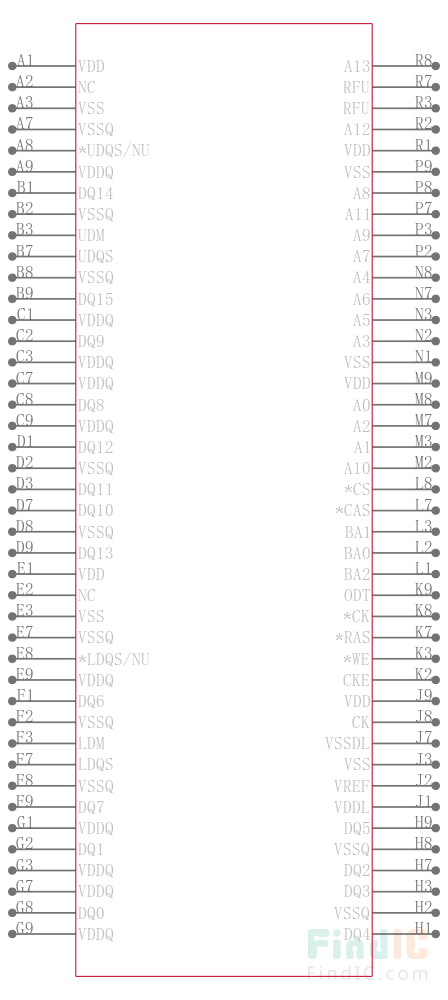

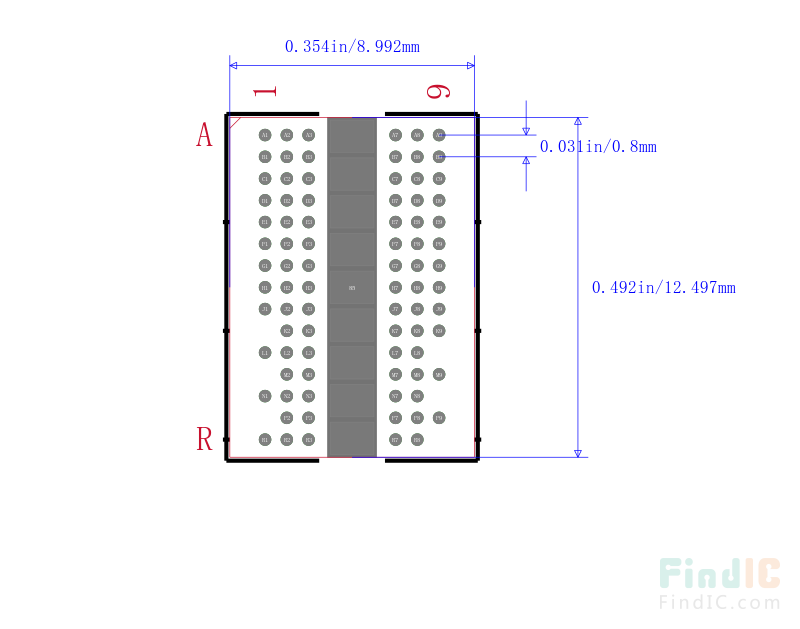

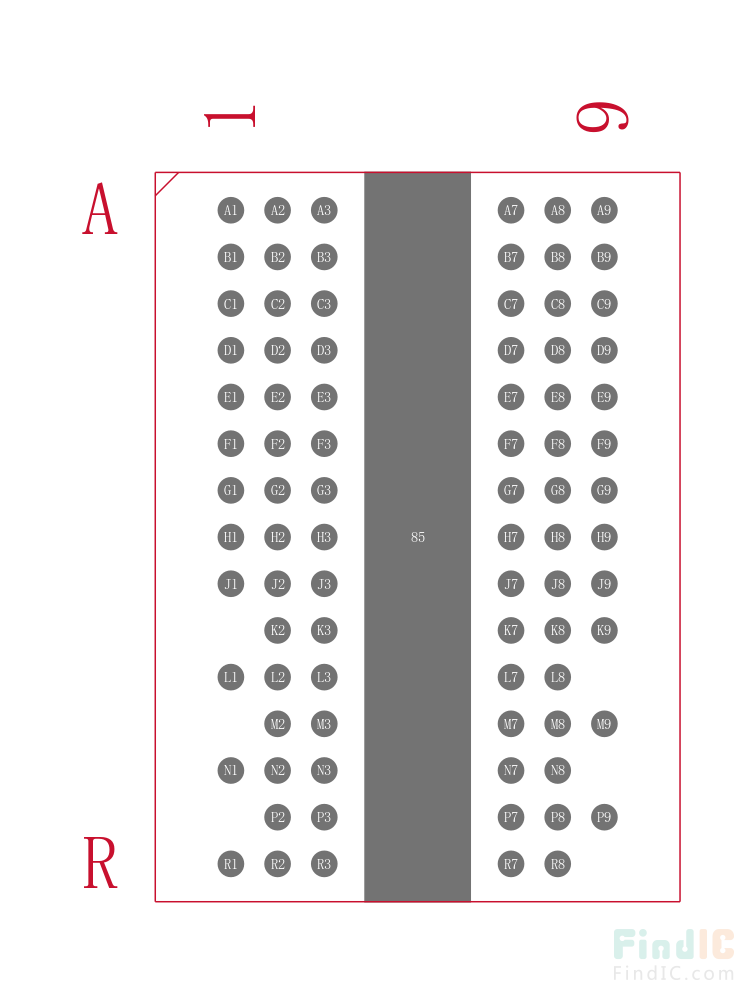

MT47H128M16RT-25E:C 引脚图 | 封装图 | 封装焊盘图

MT47H128M16RT-25E:C 引脚图

MT47H128M16RT-25E:C 封装图

MT47H128M16RT-25E:C 封装焊盘图

产品概述

MICRON MT47H128M16RT-25E:C 芯片, 存储器, SDRAM, DDR2. 2GB, 84FBGA

MT47H128M16RT-25E:C是一款DDR2 SDRAM, 采用双倍数据速率架构实现高速运行. 双数据速率结构本质上是一种4n预取体系结构, 其接口设计用于在I/O球每个时钟周期传输两个数据字. DDR2 SDRAM的单READ或WRITE操作包含单4n-位宽双时钟周期数据传输在内部DRAM核心, 以及四个相应的n位宽半时钟周期数据传输在I/O球. 双向数据选通 (DQS, DQS#)与数据一起在外部传输, 用于接收器的数据捕获. DQS是选通信号,在READ过程中由DDR2 SDRAM传输, 在WRITE过程中由存储器控制器传输. DQS与READ数据边缘对齐, 与WRITE数据中心对齐. x16产品有两个数据选通, 一个用于低字节 (LDQS, LDQS#), 另一个用于高字节 (UDQS, UDQS#).

.VDD = 1.8V ±0.1V, VDDQ = 1.8V ±0.1V

.JEDEC标准1.8V I/O (与SSTL_18兼容)

.差分数据选通 (DQS, DQS#)选项

.4n位预取架构

.重复输出选通 (RDQS)选项, 用于x8

.DLL与DQ对齐以及DQS转换带CK

.8 内部存储单元, 并行操作

.可编程CAS延迟 (CL)

.Posted CAS Additive Latency (AL)

.WRITE延迟=READ延迟 - 1 tCK

.4或8种可编程突发长度

.可调数据输出驱动强度

.64ms, 8192周期刷新

.片上终端 (ODT)

.支持JEDEC时钟抖动规范