L6713A点击型号即可查看芯片规格书

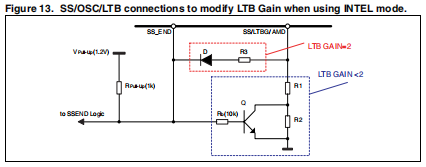

LTB增益修改(可选)

内部增益可以通过SS/LTBG/AMD引脚进行修改,如中所示图13。SS/LTBG/AMD引脚也用于设置软启动时间,因此SS/LTBG/AMD引脚必须在软启动完成后进行修改。使用D二极管和R3电阻器(图13中的红色方块),在软启动后电流从SS/LTBG/AMD引脚到SGND的流量为零,因此内部增益不是修改。As结果LTB增益为默认值(LTB增益=2)。为了降低LTB增益,必须使用由Q、R1和R2(蓝色)组成的电路图13中的正方形。)软启动后,来自SS/LTBG/AMD引脚的电流仅依赖于R1电阻,因此减小R1电阻值可以降低LTB增益。R1和R2之和必须选择电阻器以获得所需的软启动时间。

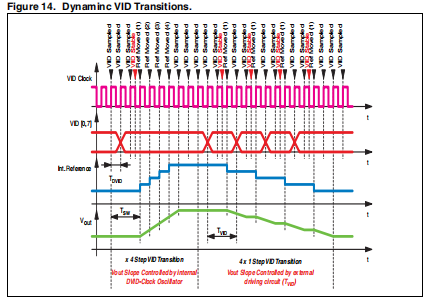

动态视频转换

该设备能够管理允许输出电压的动态视频编码变化设备正常运行期间的修改。OVP和UVP信号(以及AMD模式)在每个VID转换期间被屏蔽,并且在转换以32个时钟周期延迟结束,以防止由于过渡。当动态改变调节电压(D-VID)时,系统需要充电或相应地对输出电容放电。这意味着一个额外的ID-VID需要尤其是在提高输出稳压时,必须设置过电流阈值时考虑。可以使用以下关系:

对于DV LS6,选择VRDAC输出或VRDAC为25毫伏25毫伏(对于AMD DAC)和TVID是每个LSB转换之间的时间间隔(外部驱动)。动态视频期间克服OC阈值会导致设备进入恒流限制减慢了输出电压dV/dt也导致了故障在D-VID测试中。L6713A检查内部上升沿上的VID代码修改(参见图14)附加DVID时钟,等待下一下降沿的确认。一旦新的代码是稳定的,在下一个上升沿,参考开始上升或下降在LSB增加每个VID时钟周期,直到达到新的VID代码。在过渡期间,忽略VID代码更改;设备在转换后重新开始监视VID在下一个上升边缘完成。频率(VID)取决于时钟选择的工作模式:对于Intel模式,它在1MHz范围内,以确保兼容性与规格同时,对于AMD模式,这个频率降低到约250kHz。当L6713A在AMD模式下执行D-VID转换时,DVID引脚被拉高,只要设备正在执行转换(还包括额外的32个时钟延迟)

启用和禁用

L6713A有三种不同的电源:为内部控制逻辑提供VCC引脚,VCCDRx提供低端驱动,BOOTx提供高端驱动。如果电压在针脚VCC和VCCDRx不高于电气规范中规定的接通阈值特点是,该设备关闭:所有驱动器保持关闭的MOSFET显示高负载阻抗。一旦设备正确供应,就可以保证正常运行该器件可以由OUTEN管脚驱动,控制电源时序。设置无引脚,设备实现软启动编程电压。做空引脚到SGND,复位设备(在这种情况下,SS_END/PGOOD对SGND短路)从任何锁存状态,也禁用保持所有MOSFET转动的设备关闭以显示对负载的高阻抗。

软启动

L6713A实现了软启动,以平稳地为输出滤波器充电,避免了高峰值输入电源所需的电流。设备增加了根据所选操作,以不同方式调零至编程值模式和输出电压随闭环调节而增加。只有当所有的电源都高于其自身的开启阈值并且外部引脚被释放时,该设备才能实现软启动。在数字软启动结束时,SS_end/PGOOD信号被释放。保护措施是在此阶段激活;当参考电压达到0.6V时,欠电压启用而过电压总是以一个取决于所选操作的阈值启用模式或由ROVP编程的固定阈值(参见“过电压和可编程OVP“部分)。

英特尔模式

一旦L6713A接收到所有正确的电源并启用,并且Intel模式选择后,启动软启动阶段,延时为T1=1ms(min)。之后,参考文献根据SS/LTBG/AMD设置,在T2中上升至VBOOT=1.081V(1.100V-19mV)并等待T3=75μsec(典型值),在此期间设备读取VID线。输出电压将然后以与之前相同的斜率上升到T4中的编程值(参见图15)。

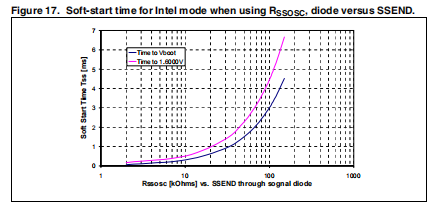

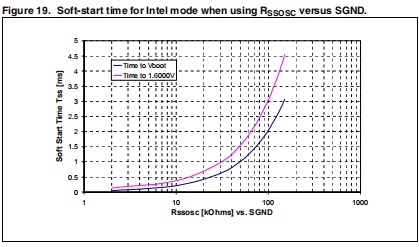

SS/LTB/AMD定义了用于从零阶跃至编程值;此振荡器独立于频率通过OSC引脚编程的主振荡器。特别是,它允许精确编程启动时间到VBOOT(T2),因为它是一种独立于可编程视频显示器的固定电压。总软启动时间依赖于编程的VID结果(见图17和图19)。

软启动时保护有效,参考电压达到0.6V后,UVP启用而在VBOOT之前,OVP始终以固定的1.24V阈值和阈值激活从VID(或编程的VOVP)在VBOOT之后(见中的红色虚线图15)。

注:如果在T3期间编程的VID选择了低于VBOOT的输出电压,则输出从VBOOT开始,电压将上升到编程电压。

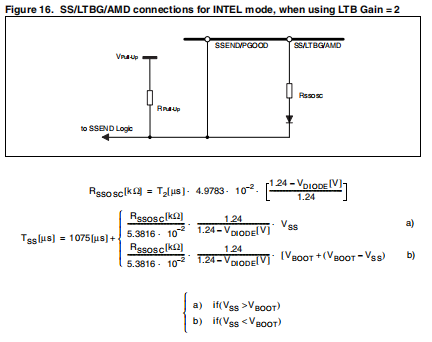

使用LTB增益=2时的SS/LTB/AMD连接SS/LTB/AMD引脚根据电阻RSSOSC通过信号二极管与SSEND/PGOOD引脚连接(见图16)。

其中TSS是达到编程电压VSS和RSSOSC所花费的时间连接在SS/LTBG/AMD和SSEND(通过信号二极管)之间,单位为kΩ。

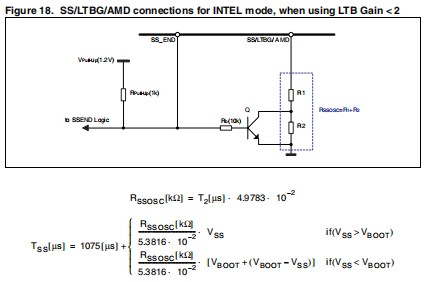

使用LTB增益<2时的SS/LTB/AMD连接当使用LTB增益<2时,等效RSSOSC电阻由R1+R2),因为在软启动没有完成之前,Q晶体管是关闭的(见图18)。

其中TSS是达到编程电压VSS和RSSOSC所花费的时间连接在SS/LTBG/AMD和SGND(RSSOSC=R1+R2)之间,单位为kΩ。

AMD模式

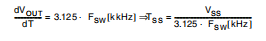

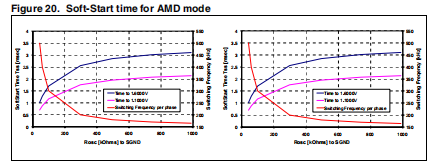

一旦L6713A接收到所有正确的电源并启用,AMD模式选择后,它通过将基准从零步进到编程值来启动软启动VID代码(参见图15);现在用于步进参考的时钟与主时钟相同由OSC引脚编程的振荡器,SSOSC引脚在这种情况下不适用。然后,软启动时间结果(见图20):

其中TSS是达到VSS所花费的时间,FSW是主开关频率由OSC引脚编程。软启动期间保护激活,在参考电压达到0.6V,而OVP始终在固定的1.800V阈值(或编程VOVP)。

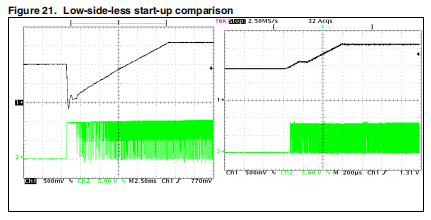

低侧启动

为了避免启动过程中负载侧出现任何类型的负欠冲,L6713A在使LS驱动器能够切换时执行一个特殊的序列:在软启动阶段LS驱动器结果禁用(LS=关闭),直到HS开始切换。这样可以避免危险输出电压上的负尖峰,如果在预偏压输出上启动可能发生(见图21)。该设备的这一特殊功能屏蔽了仅从观点:如果出现过电压,仍然允许保护打开LS MOSFET需要。

输出电压监视器和保护

L6713A通过引脚VSEN监控调节电压,以管理OVP、UVP以及良好(适用时)条件。当编程不同的操作模式(Intel或AMD,见表11),但是对保护事件的响应仍然与下面描述的相同。当使用偏移函数时,OVP、UVP和PGOOD阈值根据偏移电压:在软启动期间(见“软启动”一节),在屏蔽的情况下,保护也处于活动状态在D-VID转换期间,在转换后有额外的32时钟周期延迟完成以避免错误触发。

欠压

如果VSEN监控的输出电压低于编程值-750mV以上对于一个以上的时钟周期,L6713A关闭所有mosfet并锁存条件:要恢复,需要循环Vcc或OUTEN引脚。这是独立于选择操作模式。

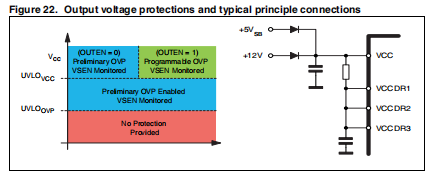

初步过电压

在VCC低于UVLOVCC阈值时提供保护是必须避免的HS MOSFET故障时CPU损坏。事实上,由于设备是由对于12V总线,对于低于开启阈值(UVLOVCC)的任何电压,它基本上是“盲”的。在为了给负载提供全面保护,在VCC时提供初步的OVP保护在LovUVCC内。只要VSEN管脚电压更大,这种保护就会开启低侧mosfet大于1.800V,滞后350mV。设置后,保护驱动LS MOSFET门到源的电压取决于施加在VCCDRx上的电压通过这些引脚的开启阈值(UVLOVCCDR)。这种保护还取决于OUTEN管脚状态如图22所示。当设备关闭时,一种在所有情况下为输出提供保护的简单方法(然后避免图22左边的不受保护的红色区域)包括提供控制器通过5VSB总线,如图22右图所示:5VSB以前总是存在的+12V,在HS短路的情况下,LS MOSFET由5V驱动,确保可靠负载保护。对于Intel和AMD模式。

过压和可编程OVP

一旦VCC超过开启阈值且设备启用(OUTEN=1),L6713A提供过电压保护:当VSEN感应到的电压克服OVP阈值,控制器永久性地打开所有低端MOSFET和关闭所有高侧MOSFET以保护负载。OSC/故障引脚驱动电压高(5V)并且需要电源或外部引脚循环才能重新启动OVP阈值根据选择的操作模式而变化(参见表11)。OVP阈值也可以通过OVP引脚编程:让引脚浮动,它内部拉高,并根据表11设置OVP阈值。连接OVP引脚到SGND通过电阻ROVP,OVP阈值变为存在的电压在大头针处。由于OVP引脚提供恒定的IOVP=12.5μa电流(见表4),因此编程电压变为:

最大值(100pF)与最大值。

PGOOD(仅适用于AMD模式)

它是软启动程序完成后释放的开路漏极信号。它被拉低了当输出电压低于编程电压的-300mV时。

集成的大电流驱动器允许使用不同类型的功率MOS(也可以是多个MOS降低等效RdsON),保持快速开关转换。高压侧mosfet的驱动器使用BOOTx引脚供电,PHASEx引脚用于返回。低端mosfet的驱动器使用vcdrx引脚作为电源和PGNDx引脚为了回报。VCCDRx引脚上的最低电压要求设备开始运行。VCCDRx针脚必须连接在一起。该控制器包含一个复杂的反射击系统,以尽量减少低的一面体二极管传导时间保持良好效率节省肖特基二极管的使用:当高压侧MOSFET关闭时,其源上的电压开始下降;当电压达到2V时,低压侧MOSFET栅极驱动突然应用。当低侧MOSFET关闭时,检测到LGATEx引脚上的电压。当电压降到1V以下时高压侧MOSFET栅极驱动突然应用。如果电感器中的电流是负的,那么高侧MOSFET的源就永远不会放下。即使在这种情况下,也允许打开低侧MOSFET,一个看门狗控制器启用:如果高侧MOSFET的源不下降,则低侧MOSFET被打开,从而允许感应器的负电流再循环。这个即使电流为负,机械装置也能使系统进行调节。CDRX和VCIC引脚也与电源引脚分开信号接地(SGND引脚)和电源接地(PGNDx引脚),以便最大限度地开关抗扰度。不同驱动器的独立供电具有很高的灵活性在选择MOSFET时,允许使用逻辑电平MOSFET。几种供应组合可以选择优化应用程序的性能和效率。电源转换输入也是灵活的;5V,12V总线或任何允许转换的总线(见最大占空比限制)可自由选择。

系统控制回路补偿

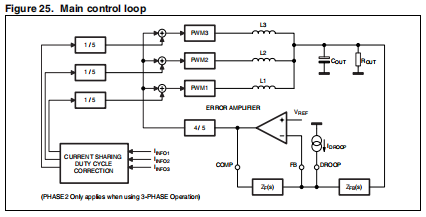

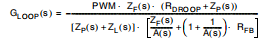

控制回路由均流控制回路(见图9)和平均电流模式控制回路。在适当增益的情况下,每个环路都会对PWM使其调节误差最小化:均流控制回路当平均电流模式控制回路固定输出电压等于VID编程的参考值。图25显示了该块系统控制回路图。系统控制回路如图26所示。IDROOP提供的当前信息通过下降管脚流入RFB实现对输出电压的依赖性读取电流。

该系统可以用等效单相变流器进行建模差分是等效电感器L/N(其中每相有一个L电感器)环路增益结果(在补偿引脚后打开环路获得):

基于L6713A的虚拟现实嵌入

将VRD嵌入应用程序时,必须格外小心,因为整个VRD是一个开关式DC/DC调节器,也是其中最常见的系统工作是一个数字系统,如MB或类似的。事实上,最新的MB已经变得更快而且功能强大:高速数据总线越来越普遍和开关感应噪声如果不遵循其他布局指南,VRD生成的数据可能会影响数据完整性。在路由高交换路径时,必须主要考虑几个容易的点电流(高开关电流会导致杂散电感上的电压尖峰会影响附近记录道的噪声的轨迹):保持大电流开关VRD轨迹和数据总线之间的安全防护距离,尤其是高速数据总线,使噪声耦合最小化。为I/O子系统路由偏差跟踪时,保持安全防护距离或适当过滤必须在VRD附近行走。噪声的可能原因可以定位在相位连接,MOSFET栅极驱动以及输入电压路径(来自输入大容量电容器和HS漏极)。还有PGND连接如果不坚持使用电源接地平面,则必须考虑。这些连接必须小心远离噪音敏感的数据总线。由于产生的噪声主要是由于VRM的开关活动,所以噪声排放量取决于电流转换的速度。为了降低噪音排放水平另外,除了前面的指导方针,还可以适当地降低当前坡度调谐HS门电阻和相位缓冲网络。