特征

●低失真:5MHz时为-95dBc

●增益+1带宽:400MHz

●提供SOT23-5包装

●高开环增益:95dB

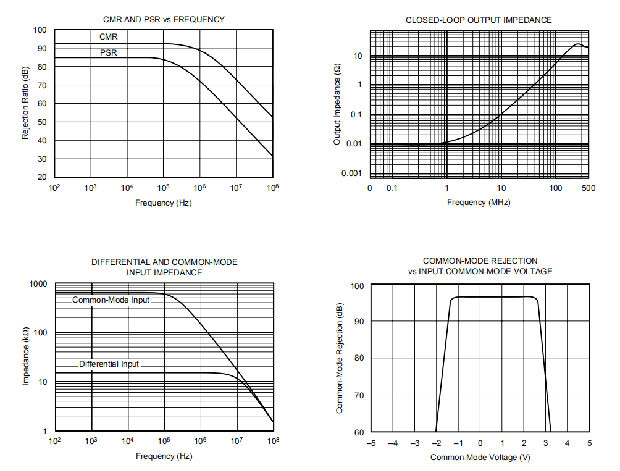

●高共模抑制:90dB

●快速12位设置:13ns(0.01%)

●低噪声:2.7nV/√Hz

●高输出电流:±60mA

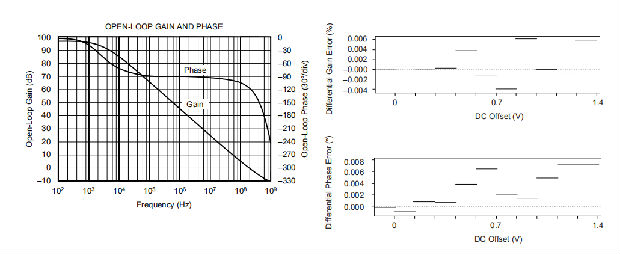

●非常低的差分增益/相位误差:0.007%/0.008°

应用

●ADC/DAC缓冲放大器

●低失真中频放大器

●高分辨率成像

●医学成像

●低噪声前置放大器

●高CMR差分放大器

●测试仪器

●专业音频

说明

OPA642提供了以前在单片操作中无法达到的速度和动态范围amp.使用OPA642是一种具有两个内部增益级的单位增益稳定电压反馈结构,可在较宽的频率范围内实现极低的谐波失真。“经典”差分输入提供了精密运算放大器的所有常见优点,例如与宽带电流反馈运算放大器相比,偏置电流消除和极低的反向电流噪声。快速的稳定时间、优异的差分增益/相位性能、低电压噪声和高输出电流驱动使OPA642成为大多数高动态范围应用的理想选择。

单位增益稳定性使OPA642特别适用于低增益差分放大器、跨阻放大器、+2视频线驱动器增益、宽带积分器和低失真ADC放大器。如果需要更高的增益甚至更低的谐波失真度,请考虑OPA643,它是OPA642的更高增益带宽和更低噪声版本。

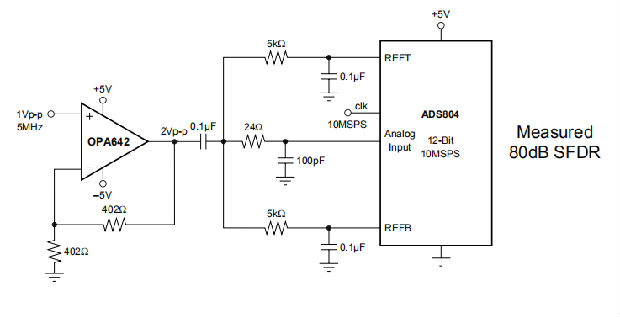

高动态范围10MSPS数字化仪

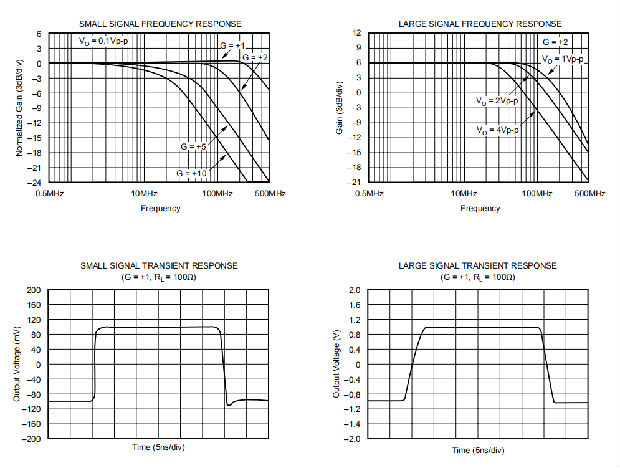

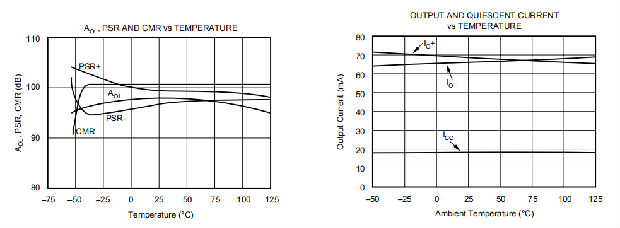

典型性能曲线

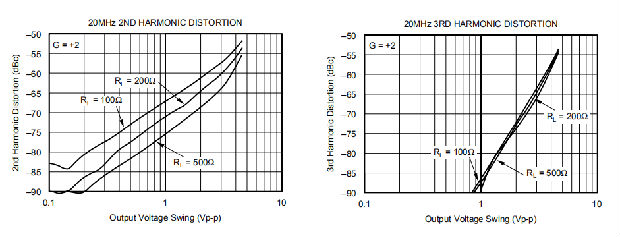

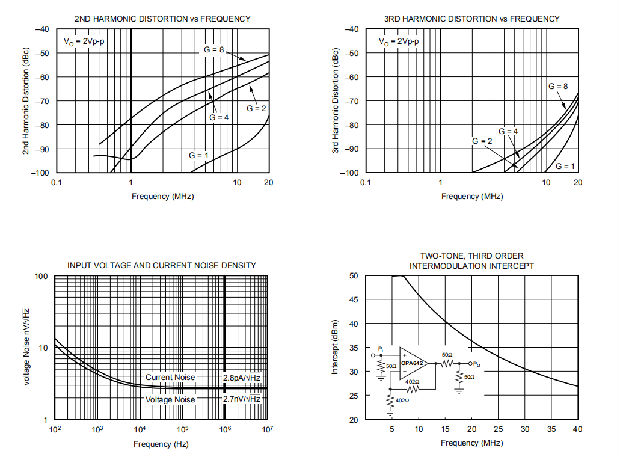

TA=+25°C,VS=±5V,RL=100Ω,RF=402Ω,G=+2,除非另有说明。RF=25Ω,增益为+1。

应用程序信息

宽带电压反馈操作

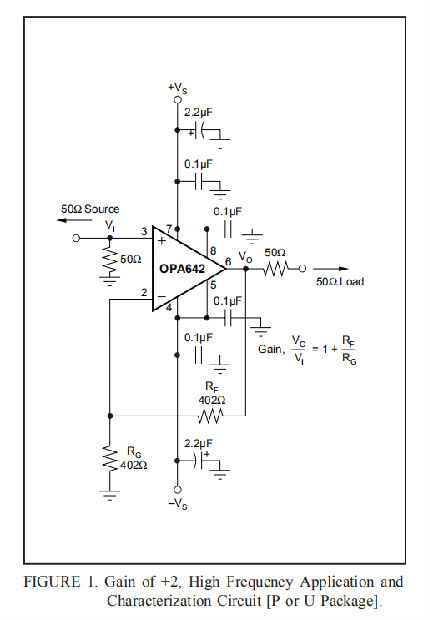

OPA642的速度和动态范围的结合很容易在各种应用电路中实现,只要遵守良好设计实践的简单原则。例如,如图1所示,良好的电源去耦对于实现尽可能低的谐波失真和平滑的频率响应至关重要。正确的PC板布局和仔细的组件选择将使OPA642在所有应用中的性能最大化,如本数据表其余部分所述。

图1显示了作为大多数典型性能曲线基础的+2配置增益。大多数曲线的特征是使用50Ω驱动阻抗的信号源和50Ω并联负载阻抗的测量设备。在图1中,VI端子处的50Ω并联电阻器与测试发生器的源阻抗匹配,而VO端子上的50Ω串联电阻器为测量设备负载提供匹配电阻器。一般来说,数据表规格是指输出引脚处的电压摆动(图1中的VO)。串并联匹配电阻产生的100Ω负载,加上804Ω的总反馈网络负载,使OPA642具有大约90Ω的有效负载。

缓冲高性能ADC

为了实现高动态范围a/D转换器的全部性能,在设计输入放大器接口电路时必须非常小心。首页上的示例电路显示了一个典型的交流耦合接口到一个非常高的动态范围转换器。信号在0伏左右的范围内对称地工作。2Vp-p摆幅然后通过阻断电容器电平偏移到直流参考电平,这是由转换器内部参考电压的一个良好解耦的电阻分压器产生的。为了对转换器的额定无杂散动态范围(SFDR)产生可忽略的影响,放大器的SFDR应至少大于10dB。在首页示例中,OPA642的插入对ADS804的失真有不可估量的影响,ADS804在5MHz Nyquist输入信号下实现了80dB的SFDR。

为了在8针SO-8或DIP封装中实现尽可能低的失真,需要在引脚5和8上增加0.1μF去耦电容器。如图1所示。虽然引脚5和引脚8分别内部连接到引脚4和引脚7(8引脚运算放大器的标准电源引脚),但附加电容器有助于分离封装引线电感,并将5MHz下的二次谐波抑制提高约4dB。SOT23-5封装的更短的连接线和电源线提供了最佳的失真性能,同时只需要两个电源连接。

成功应用OPA642进行ADC缓冲需要仔细选择放大器输出端的串联电阻,以及ADC输入端的附加并联电容器。在某种程度上,这种RC网络的选择将由经验决定每种型号的变流器。许多高性能的CMOS adc,如ADS804,在输入端有并联电容器时性能更好。该电容器为采样过程中产生的瞬态电流提供低源阻抗。改进的SFDR是通过增加电容器获得的,电容器的值通常在转换器数据表中被推荐。外部电容器与A/D输入的内置电容相结合,为OPA642提供了一个重要的电容性负载。如果没有串联隔离电阻,结果可能是放大器中不希望达到的峰值或失去稳定性。由于CMOS A/D输入的直流偏置电流可以忽略不计,电阻对整体增益或偏移精度没有影响。参考典型性能曲线中“RS与电容性负载”的曲线图,以获得串联电阻器的良好启动值。这将确保对ADC输入的平坦频率响应。增加外部电容值将使串联电阻减小,或者,保持该电阻不变,将限制信号并降低转换器输入的高频噪声。

视频线驱动

大多数视频分配系统设计有75Ω系列电阻器,以驱动匹配的75Ω电缆。为了向75Ω匹配负载提供1的净增益,放大器通常设置为+2的电压增益,以补偿电缆任一端串联和并联75Ω电阻器形成的分压器的6dB衰减。如果50Ω电阻器的所有参考值都被75Ω值取代,则图1的电路适用于此要求。通常,放大器增益进一步增加到2.2,这恢复了典型长电缆线路的额外直流损耗。这一变化要求图1中的增益电阻(RG)从402Ω减小到335Ω。在任何一种情况下,OPA642的增益平坦度和差分增益/相位性能都将在视频分发应用中提供优异的结果。差分增益和相位测量彩色副载波频率(NTSC系统中为3.58MHz)与大信号输出电平(代表复合视频信号中的亮度信息)的总体小信号增益和相位的变化。OPA642在单匹配视频电缆的典型150Ω负载下,在正视频(负同步)信号的标准亮度范围内,显示的差分增益/相位误差小于0.01%/0.01°。负面视频信号也会出现类似的表现。实际上,由于OPA642的线性高频输出阻抗,即使在两个视频负载下也能获得类似的性能。

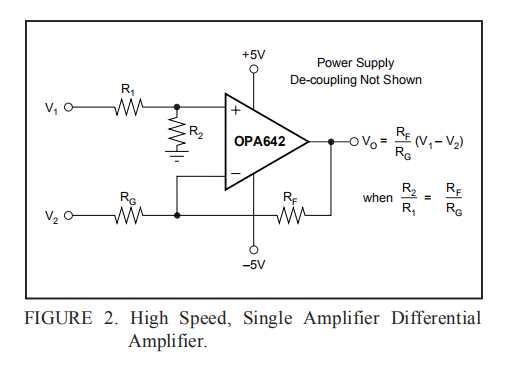

单运放差分放大器

OPA642的电压反馈架构,其高共模比,将提供卓越的性能差分放大器配置。图2显示了一个典型的配置。此设计的起点是选择200Ω到2kΩ范围内的RF值。较低的值降低了所需的RG,增加了V2源和OPA642输出的负载。较高的值会增加输出噪声,并加剧寄生板和器件电容的影响。选择RF后,必须设置RG以获得V2所需的反转增益。请记住,带宽将大约由增益带宽积(GBP)除以噪声增益(1+RF/RG)来设置。对于精确的差分操作(即良好的CMR),比率R2/R1必须设置为RF/RG。通常,最好将R2和R1的绝对值分别设置为RF和RG;这样可以使分压器电阻相等,并消除输入偏置电流的影响。然而,为了调整驱动源V1上的负载,调整R2和R1的值有时是有用的。在大多数情况下,可实现的低频CMR将受到电阻值精度的限制。OPA642本身的90dB CMR不会确定整个电路的CMR,除非电阻比匹配到优于0.003%。如果有必要对CMR进行微调,则R2是建议的调整点。

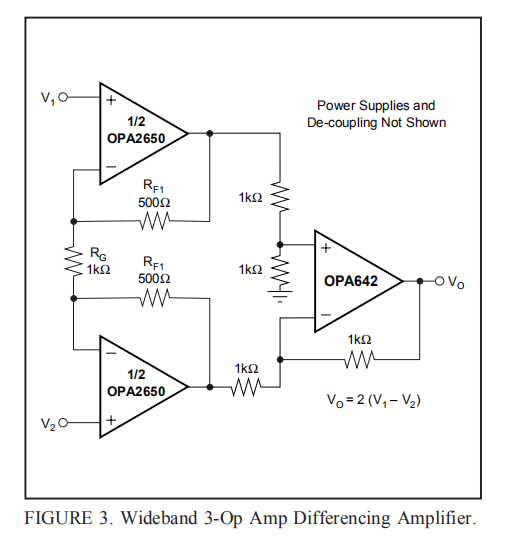

三运算放大器差分(仪器拓扑)

单运放差分放大器的主要缺点是输入阻抗相对较低。当差分输入端需要高阻抗时,可以使用OPA642作为差分级来构建标准仪表放大器(INA)拓扑。图3显示了一个例子,其中两个输入放大器封装在一起作为一个双电压反馈运算放大器OPA2650。与使用两个额外的OPA642器件相比,这种方法节省了电路板空间、成本和功耗,并且由于输入放大器的中等负载,仍然可以获得非常好的噪声和失真性能。在该电路中,由于四个匹配的1kΩ电阻器,输出的共模增益始终为1,而差分增益由(1+2RF1/RG)设置,使用图3中的值等于2。差分到单端的转换仍然由OPA642输出级执行。高阻抗输入允许V1和V2源端接或阻抗匹配,无需差分放大器进一步加载。如果V1和V2输入已经是真正的差分输入,例如信号变压器的输出,则可以在它们之间使用一个匹配的终端电阻。但是,请记住,对于V1和V2输入,必须始终存在定义的直流信号路径;对于变压器情况,中心抽头次级连接到地面将提供最佳的直流操作点。

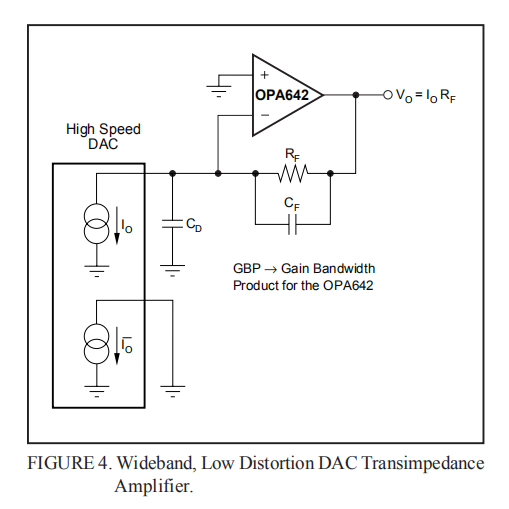

DAC跨阻放大器

高频DDC-dac需要一个低失真的输出放大器,以保持其SFDR性能进入真实的负载。单端输出驱动实现如图4所示。在该电路中,只使用互补输出驱动信号的一侧。该图显示了连接到OPA642的虚拟接地和结的信号输出电流,OPA642被设置为跨阻级或“I-V转换器”。DAC未使用的电流输出接地。如果DAC要求其输出端接至非接地的合规电压进行操作,则适当的电压电平可应用于OPA642的非逆变输入端。这个电路的直流增益等于射频。在高频下,DAC输出电容将在OPA642的噪声增益中产生零,这可能导致闭环频率响应的峰值。在射频中加入CF以补偿噪声增益峰值。为了实现平坦的跨阻频率响应,反馈网络中的该极点应设置为:

其转角频率ƒ-3dB约为:

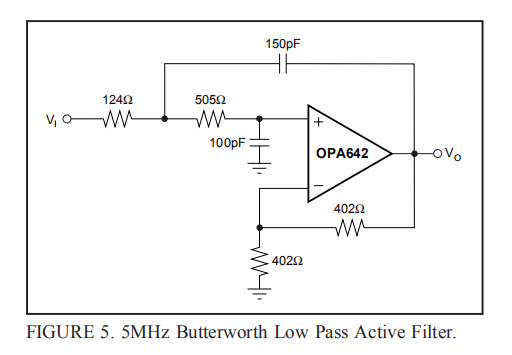

有源滤波器

大多数有源滤波器拓扑将使用OPA642的宽带和单位增益稳定性提供优异的性能。采用电容反馈的拓扑需要单位增益稳定的电压反馈运算放大器。SallenKey滤波器简单地将运算放大器用作RC网络中的非反转增益级。电流或电压反馈运算放大器可用于Sallen-Key实现。

图5显示了一个示例Sallen-Key低通滤波器,其中OPA642被设置为提供+2的低频增益。选择滤波器组件值,以获得最大平坦的巴特沃斯响应,带宽为5MHz–3dB。电阻值已经过轻微调整,以补偿该配置中由OPA642提供的150MHz带宽的影响。该滤波器可与ADC驱动器建议相结合,以提供中等(2极)奈奎斯特滤波、限制噪声和带外分量到ADC的输入中。该滤波器将提供高SFDR A/D转换器(如ADS804(12位、10MSPS、80dB SFDR)所需的极低谐波失真。

操作建议

优化电阻值

由于OPA642是一个单位增益稳定的电压反馈运算放大器,反馈和增益设置电阻器可使用范围广泛的电阻值。这些值的主要限制是通过动态范围(噪声和失真)和寄生电容来设置的。对于非反相单位增益跟随器应用,反馈连接应采用25Ω电阻器,而不是直接短路。这将隔离反向输入电容和输出引脚,并改善频率响应平坦度。通常,反馈电阻值应在200Ω和1kΩ之间。低于200Ω时,反馈网络将呈现额外的输出负载,这会降低OPA642的谐波失真性能。高于1kΩ时,反馈电阻上的典型寄生电容(约0.2pF)可能会导致放大器响应中的非故意频带限制。

一个好的经验法则是将RF和RG的并行组合(图1)设定为小于约200Ω。组合阻抗RF | | RG与逆变输入电容相互作用,在反馈网络中增加一个极点,从而使正向响应为零。假设反向节点上寄生2pF,保持RF | | RG<200Ω将使该极保持在400MHz以上。就其本身而言,这个约束意味着反馈电阻RF可以在高增益下增加到几个kΩ。只要射频形成的磁极和并联的寄生电容不在感兴趣的频率范围内,这是可以接受的。

在反向配置中,必须注意额外的设计考虑。RG成为输入电阻,因此成为驱动源的负载阻抗。如果需要阻抗匹配,可以将RG设置为所需的终端值。然而,在低反向增益时,所产生的反馈电阻值可以为放大器输出提供一个重要的负载。例如,如果逆变增益为2,且输入匹配电阻为50Ω(=RG),则需要一个100Ω的反馈电阻器,这将有助于输出负载与外部负载并联。在这种情况下,最好同时增加RF和RG值,然后用第三个对地电阻来实现输入匹配阻抗。总输入阻抗变成RG和附加并联电阻的并联组合。

带宽与增益

当闭环信号显示增益反馈增加时,增益反馈减小。理论上,这种关系用规范中显示的增益带宽积(GBP)来描述。理想情况下,GBP除以非反转信号增益(也称为噪声增益,或NG)将预测闭环带宽。实际上,这只在相位裕度接近90°时成立,就像在高增益配置中一样。在低信号增益下,大多数放大器将表现出更复杂的响应和更低的相位裕度。OPA642经过优化,在增益为2的情况下,给出最大平坦的二阶巴特沃斯响应。在这种配置中,OPA642具有大约60°的相位裕度,并且将显示150MHz的典型-3dB带宽。当相位裕度为60°时,闭环带宽大约比GBP除以噪声增益的预测值大√2。增加增益将使相位裕度接近90°,带宽更接近预测值(GBP/NG)。当增益为+10时,典型规范中显示的21MHz带宽与使用简单公式预测的带宽和210MHz的典型GBP一致。

输出驱动能力

OPA642已经过优化,可以驱动双端传输线的高要求负载。当驱动50Ω线路时,在电缆中使用一个50Ω的串联,并在电缆末端使用一个50Ω的终端负载。在这些条件下,电缆的阻抗在很宽的频率范围内表现为电阻,OPA642上的总有效负载与反馈网络的电阻并联为100Ω。技术规格显示在这样一个负载中有一个保证的±2.5V摆幅,然后在终端电阻处减小到±1.25V的摆幅。保证的±35mA输出驱动过温为该负载提供了足够的电流驱动裕度。当驱动高阻抗负载时,可以实现更高的电压波动(和更低的失真)。

单个视频负载通常显示为驱动放大器的150Ω负载(使用标准75Ω电缆)。OPA642提供足够的电压和电流驱动,以支持NTSC信号最多3个并行视频负载(总负载50Ω)。在只有一个负载的情况下,OPA642实现了异常低的0.007%/0.008°dG/dP误差。

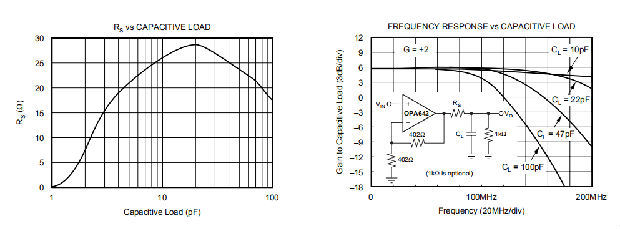

驱动电容性负载

对运算放大器来说,最苛刻,也是最常见的负载条件之一是电容性负载。像OPA642这样的高速、高开环增益放大器,当电容性负载直接施加在输出引脚上时,其稳定性和闭环响应峰值非常敏感。简单地说,电容性负载与放大器的开环输出电阻发生反应,在环路中引入额外的极点,从而减小相位裕度。这个问题已经成为应用程序注释和文章的热门话题,并且已经提出了一些解决这个问题的外部解决方案。当主要考虑频率响应平坦度、脉冲响应保真度和/或失真时,最简单和最有效的解决方案是通过在放大器输出和电容性负载之间插入一个串联的隔离电阻,将电容性负载与反馈回路隔离。这并没有从环路响应中消除极点,而是将其移位,并在更高频率下添加零。附加零位的作用是消除电容性负载极的相位滞后,从而增加相位裕度,提高稳定性。

典型性能曲线显示了推荐的RS与电容性负载以及负载下产生的频率响应。设置推荐电阻器的标准是负载处的最大带宽、平坦频率响应。由于现在在输出管脚和负载电容之间有一个无源低通滤波器,输出管脚本身的响应通常有点峰值,并且在RC网络的滚降作用后变得平坦。在大多数应用程序中,这不是一个问题,但是如果负载下的期望信号摆幅非常接近放大器的摆幅极限。这种限幅最有可能发生在脉冲响应应用中,其中频率峰值表现为阶跃响应中的过冲。

大于2pF的寄生电容性负载会开始降低OPA642的性能。很长的PC板轨迹、不匹配的电缆以及与多个设备的连接很容易导致超过此值。始终仔细考虑这种影响,并尽可能靠近OPA642输出引脚添加推荐的串联电阻器(见电路板布局指南)。

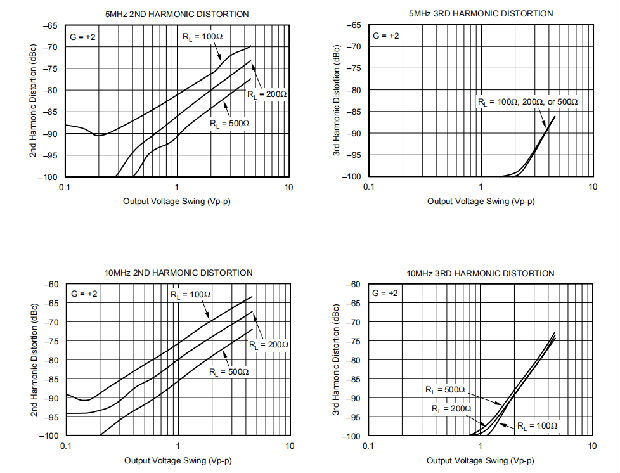

失真性能

OPA642能够以高频率和低增益传输异常低的失真信号。典型性能曲线中的畸变图显示了各种情况下的典型畸变。大多数曲线图的动态范围限制为100dB。在信号电平超过0.5V和/或基频超过500kHz之前,OPA642的失真不会上升到–100dBc以上。音频带失真≤–120分贝。

一般来说,在基波信号达到很高的频率或功率之前,二次谐波将主导失真,而三次谐波分量可以忽略不计。然后聚焦于二次谐波,增加负载阻抗直接改善失真。请记住,在非反相配置中,总负载包括反馈网络这是RF+RG的总和,而在反向配置中,这只是RF(图1)。增大输出电压摆幅直接增加谐波失真。输出摆幅增加6dB通常会增加二次谐波12dB和三次谐波18dB。增加信号增益也会增加二次谐波失真。同样,增加6分贝的增益将增加第二和第三谐波6分贝,即使在恒定的输出功率和频率。最后,由于环路增益随频率的衰减,失真随着基频的增加而增加。相反地,失真将改善到低频,直至大约3kHz的主开环极点。从2Vp-p的–90dBc二次谐波到500Ω,G=+2 1MHz下的失真(根据典型性能曲线),20kHz下的二次谐波失真应大约为–90dB–20log(1MHz/20kHz)=–124dBc。

OPA642具有极低的三阶谐波失真。这也提供了一个非常好的双音,三阶互调截获,如典型性能曲线所示。当通过50Ω匹配电阻器驱动时,截距曲线定义为50Ω负载,以便与射频MMIC设备直接比较。该网络将输出端到负载的电压摆幅衰减6dB。如果OPA642直接驱动到高阻抗设备(例如ADC)的输入端,则不会采用这种6dB的衰减。在这些条件下,截距至少增加6dBm。截距用于预测两个相邻频率的互调杂散。如果两个测试频率f1和f2是根据平均频率和δ频率fO=(f1+f2)/2和∆f=| f2–f2 |/2规定的,则这两个三阶杂音将以fO±(3•∆f)出现。两个相等的测试音调功率电平和这些互调杂散功率电平之间的差由2•(IM3–PO)给出,其中IM3是从典型性能曲线中提取的截距,PO是两个紧密间隔的测试频率之一在50Ω负载下的功率电平(dBm)。例如,在10MHz时,增益为+2的OPA642在匹配的50Ω负载下的截距为46dBm。如果两个频率的全包络需要为2Vp-p,则要求每个音调为4dBm。三阶互调杂散音调将低于测试音调功率电平(-80dBm)2•(46–4)=84dBc。如果同样的2Vp-p双音包络线直接传送到ADC的输入端,而没有匹配的损耗或50Ω网络的负载,截距将增加到至少52dBm。在相同的信号和增益条件下,但现在直接在轻负载下行驶,杂散音调将至少比1Vp-p测试音调信号电平低2•(52–4)=96dBc。

噪声性能

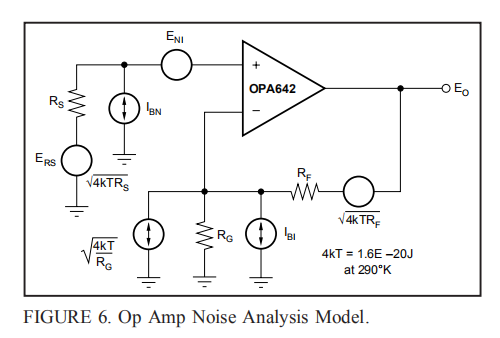

OPA642以低输入噪声项补充其超低谐波失真。输入参考电压噪声和两个输入参考电流噪声项结合在一起,可在各种工作条件下产生较低的输出噪声。图6显示了包含所有噪声项的运算放大器噪声分析模型。在这个模型中,所有的噪声项都被认为是以nV/√Hz或pA/√Hz表示的噪声电压或电流密度项。

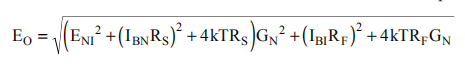

总的输出点噪声电压可以计算为输出噪声电压贡献项的平方根。这种计算方法是在输出端叠加所有的噪声功率,然后取平方根得到一个点噪声电压。方程式1显示了输出噪声电压的一般形式,使用图6所示的术语。

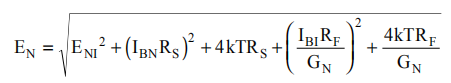

将该表达式除以噪声增益(GN=1+RF/RG)将得到非逆变输入下的等效输入参考点噪声电压,如等式2所示。

对图1所示OPA642电路的这两个方程进行评估,可得出总输出点噪声电压为6.7nV/√Hz,等效输入点噪声电压为3.35nV/√Hz。

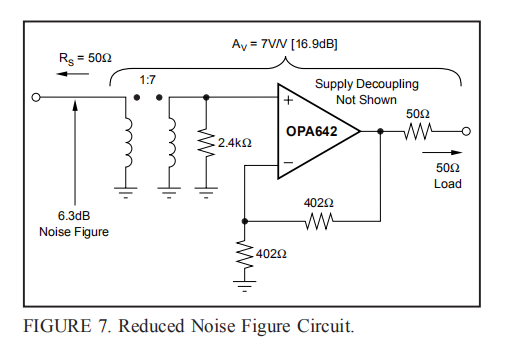

窄带通信系统通常关心放大器的噪声系数。总输入参考电压噪声表达式(公式2)可用于计算噪声系数。方程3显示了这个噪声系数表达式,使用式2的EN表示非反相配置,其中输入端接电阻器RT已设置为与源阻抗匹配(如图1所示)。

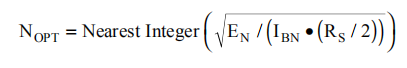

对图1电路的方程式3进行计算,得出噪声系数=17.6dB。输入变压器耦合可用于降低该噪声系数。宽带脉冲变压器可以提供一个无噪声的电压增益和一个更优化的源阻抗,以最小化噪声系数。图7显示了根据图1的电路构建的示例,其中变压器匝数比已设置为最小噪声系数的最接近整数。最佳匝数比的计算公式如下:

这一优化很大程度上取决于所选的放大器和配置。

直流偏移控制

OPA642由于其高开环增益、高共模抑制、高电源抑制以及低输入偏移电压和偏置电流偏移误差,可提供优异的直流信号精度。任何封装类型的高级(B)版本提供小于1mV的输入偏移电压。为了充分利用这种低的输入偏置电压,还需要仔细注意输入偏置电流的消除。OPA642的高速输入级具有相对较高的输入偏置电流(25μa典型输入引脚),但两个输入电流之间的匹配非常接近,通常为100nA的输入偏置电流。通过匹配两个输入端的源阻抗,可以大大降低总输出偏移电压。例如,向图1的电路添加偏置电流消除的一种方法是将175Ω串联电阻器插入50Ω端接电阻器的非逆变输入端。当输入端阻抗为50Ω时,输入端的阻抗将增加到50Ω。由于这现在等于反向输入(RF | | RG)外的阻抗,电路将抵消输出的偏置电流增益,只留下偏置电流乘以反馈电阻作为输出端的残余直流误差项。使用402Ω反馈电阻器,该输出误差现在将小于3μa•402Ω=1.2mV。

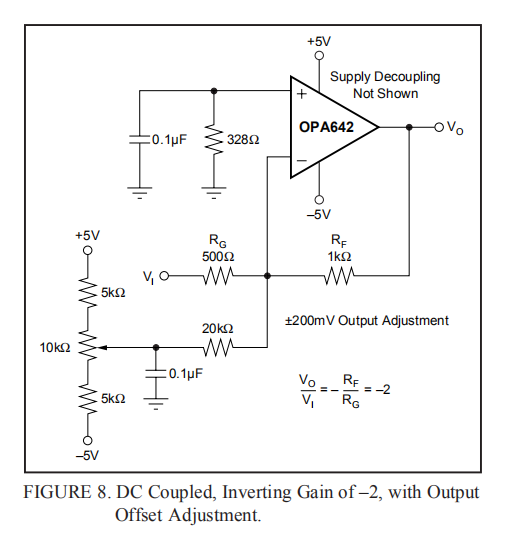

有时需要微调输出偏移零点或直流工作点调整。在运算放大器电路中引入直流偏移控制有许多技术。这些技术中的大多数最终都会减少到通过反馈电阻设置直流电流。选择一种技术的一个关键考虑因素是确保它对期望的信号路径频率响应的影响最小。如果信号路径打算是非反相的,则偏移控制最好作为反相求和信号应用。如果信号路径要反转,可以考虑对非反转输入应用偏移控制。对于直流耦合信号,在某些配置中,直流偏移信号可以设置直流电流回到必须考虑的源中。对反向运算放大器输入进行调整也可以改变噪声增益和频率响应平坦度。图8显示了对信号频率响应影响最小的直流耦合信号路径的偏移调整示例。在这种情况下,输入被引入到一个逆变增益电阻器,直流调节的附加电流加在逆变节点上。设置此电流的电阻网络比信号通路电阻大得多。这将确保这种调整对环路增益和频率响应的影响最小。

热分析

OPA642在大多数操作条件下不需要散热。所需的最高结温将设置如下所述的最大允许内部功耗。在任何情况下,最高结温不得超过175℃。

工作结温度(TJ)由TA+PD•θJA给出。总内部功耗(PD)是静态功率(PDQ)和输出级(PDL)中分配的用于传输负载的附加功率之和动力。静止功率就是指定的空载供电电流乘以整个部件的总供电电压。PDL将取决于所需的输出信号和负载,但对于接地电阻负载,当输出固定在等于1/2电源电压的电压时(对于相等的双极电源),PDL将处于最大值。在此条件下,PDL=VS2/(4•RL),其中RL包括反馈网络负载。

注意,决定内部功耗的是输出级的功率而不是负载。

作为最坏情况的例子,使用图1电路中的OPA642N(SOT23-5封装)计算最大TJ,该电路在最高规定环境温度+85°C下运行。PD=10V•26mA+5^2/(4•(100Ω| 804Ω))=330mW。最大TJ=+85°C+0.33W•150°C/W=135°C。

电路板布局指南

要获得最佳的性能与高频放大器,如OPA642需要仔细注意板布局寄生和外部元件类型。优化性能的建议包括:

a) 将信号输入/输出引脚的寄生电容降至最低。输出端和反向输入端上的寄生电容会导致不稳定:在非换向输入端,它会与源阻抗发生反应,导致无意的带宽限制。为了减少不必要的电容,信号I/O引脚周围的所有地面和电源平面上都应该打开一个窗口。地面和动力飞机应该在飞机上的其他地方完好无损。

b) 将电源插脚与高频0.1F去耦电容器之间的距离(<0.25“)减至最小。在设备引脚处,接地和电源平面布局不应靠近信号输入/输出引脚。避免狭窄的电源和接地痕迹,以尽量减少引脚和去耦电容器之间的电感。主电源连接(插脚4和7)应始终与这些电容器断开连接。引脚5和8上的可选输出级电源连接可用于稍微改善谐波失真和稳定时间(对于8针封装部件)。将0.1μF去耦电容器放在离这些引脚很近的地方,以提高性能。主电源引脚上还应使用较大的(2.2μF至6.8μF)去耦电容器,在较低频率下有效。这些可以放置在离设备稍远的地方,并且可以在PC板的相同区域中的多个设备之间共享。

c) 仔细选择和放置外部组件将保持OPA642的高频性能。电阻器应为非常低的电抗类型。表面贴装电阻工作最好,并允许更紧凑的整体布局。金属薄膜和碳成分轴向引线电阻器也能提供良好的高频性能。同样,保持他们的导线和PC板跟踪长度尽可能短。切勿在高频应用中使用线绕式电阻器。由于输出引脚和逆变输入引脚对寄生电容最为敏感,因此始终将反馈和串联输出电阻器(如有)尽可能靠近输出引脚。其他网络元件,如非转换输入端接电阻器,也应放在靠近封装的地方。如果允许双面元件安装,将反馈电阻器直接放置在电路板另一侧的封装下方,位于输出和反向输入引脚之间。即使低寄生电容分流外部电阻,过高的电阻值也会产生显著的时间常数,从而降低性能。好的轴向金属膜或表面贴装电阻器与电阻器并联时大约有0.2pF。对于电阻值>1.5kΩ,该寄生电容会在500MHz以下增加一个极和/或零,从而影响电路运行。保持电阻值尽可能低,以符合负载驱动的考虑。典型性能规范中使用的402Ω反馈是设计的良好起点。注意,对于单位增益跟随器应用,建议使用25Ω反馈电阻器,而不是直接短路。这有效地将反向输入电容与输出引脚隔离,否则会导致+1频率响应增益的轻微峰值。

d) 与板上其他宽带设备的连接可以通过短的直接记录道或通过板上传输线进行。对于短连接,将跟踪和到下一个设备的输入视为集中电容负载。应使用相对较宽的迹线(50至100 mils),最好在其周围打开地面和动力飞机。估计总电容性负载,并根据推荐的RS与电容性负载的曲线设置RS。低寄生电容性负载(<5pF)可能不需要RS,因为OPA642名义上是补偿的,可以在2pF寄生负载下工作。更高的寄生电容。当信号增益增加(增加空载相位裕度)时,允许不带RS的负载。如果需要较长的记录道,并且双端接传输线固有的6dB信号损耗是可接受的,则使用微带线或带状线技术实现匹配阻抗传输线(请参阅有关微带和带状线布局技术的ECL设计手册)。50Ω的环境通常不需要在船上,事实上,更高的阻抗环境将改善失真,如失真与负载图所示。根据电路板材料和迹线尺寸定义的特性板迹线阻抗,在目标器件输入端使用匹配的串联电阻,从OPA642的输出端进入跟踪。还要记住,终端阻抗将是并联电阻和目标设备输入阻抗的并联组合:这个总有效阻抗应设置为与跟踪阻抗匹配。多个目的地设备最好作为单独的传输线来处理,每一个都有自己的串联和并联终端。如果双端接传输线的6dB衰减不可接受,则长记录道只能在源端串联端接。在这种情况下,将轨迹视为电容性负载,并设置串联电阻值,如RS与电容性负载的关系图所示。这将无法保持信号完整性以及双端接线路。如果目的设备的输入阻抗较低,则由于串联输出形成的分压器进入终端阻抗,会有一些信号衰减。

e) 不建议将OPA642这样的高速零件套入。插座引入的额外引线长度和管脚间电容会产生非常麻烦的寄生网络,几乎不可能实现平滑、稳定的频率响应。将OPA642焊接到电路板上可获得最佳效果。如果需要DIP封装的插座,高频埋入式插销(如McKenzie Technology#710C)可以产生良好的效果。

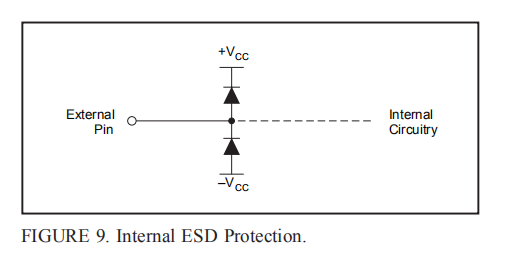

输入和ESD保护

OPA642是建立在一个非常高速互补双极工艺。由于这些非常小的几何器件,内部结击穿电压相对较低。这些细分反映在绝对最大评级表中。如图9所示,所有设备引脚都由内部ESD保护二极管保护电源。

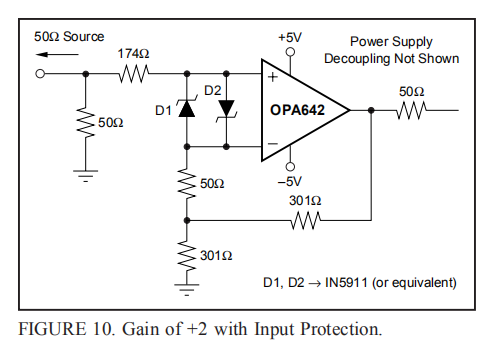

这些二极管提供适度的保护,以输入高于电源的过驱动电压。保护二极管通常可支持30mA连续电流。如果可能有更高的电流(例如,在带有±15V电源部件驱动至OPA642的系统中),应在两个输入端添加限流串联电阻器。保持这些电阻值尽可能低,因为高值会降低噪声性能和频率响应。

高输入过驱动信号也会在+和–输入之间造成显著的电压差。当该电压超过最大额定电压±1.2V时,应在两个输入端添加外部肖特基保护二极管。同样,由这些二极管增加的电容会降低噪声和交流性能,只应在必要时使用。图9显示了OPA642的全功能输入保护电路。这是图1的电路,输入端有附加的限制电阻,输入端有肖特基钳位二极管。选择这些电阻值是为了限制噪声和频率响应的退化,实现直流偏置电流抵消,并限制过驱动条件下的电流。

设计工具

示范板

在使用OPA642的三种封装风格的电路性能的初始评估中,有几个PC板可用。两块部分组装的电路板可用于销售,以支持DIP(P后缀)和SO-8(U后缀)包。这些电路板部分装配了电源和I/O连接器,但没有加载放大器或电阻网络。两块板都配置为低失真,非反相放大器操作。从当地BurrBrown经销商处订购以下零件号的电路板:

DEM-OPA64XP-N用于OPA642P和OPA642PB(8针DIP封装)

DEM-OPA64XU-N适用于OPA642U和OPA642UB(8针SO封装)

OPA642的SOT23-5封装版本可以使用一个单独的未填充板进行评估,该板用于Burr Brown提供的许多SOT23-5封装放大器。该委员会可从伯尔布朗文学部作为一个不受欢迎的董事会附于描述性文件。此板DEM-OPA6xxN可通过索取文献编号MKT-348免费获得。

宏模型和应用程序支持

在分析模拟电路和系统的性能时,使用SPICE对电路性能进行计算机模拟是非常有用的。这对于视频和射频放大器电路尤其如此,因为寄生电容和电感会对电路性能产生重大影响。OPA642的SPICE模型可通过Burr Brown网页获得()或者是Burr Brown应用部门的磁盘(1-800548-6132)。申请部门也可以通过这个号码获得设计帮助。这些模型可以很好地预测各种运行条件下的小信号交流和瞬态性能。它们在预测谐波失真或dG/dP特性方面做得不好。这些型号不试图区分封装类型在其小信号交流性能。