AD7441点击型号即可查看芯片规格书

AD7451点击型号即可查看芯片规格书

特征

快速吞吐量:1 MSPS

规定用于2.7 V至5.25 V的VDD

最大吞吐量下的低功耗:

当VDD=3 V时,1 MSPS时最大4 mW

最大9.25 mW,1 MSPS,VDD=5 V

伪差分模拟输入

宽输入带宽:输入频率为100 kHz时为70 dB SINAD

灵活的电源/串行时钟速度管理

无管道延迟

高速串行接口:SPI®-/QSPI™-/微丝™-/DSP兼容

断电模式:最大1μA

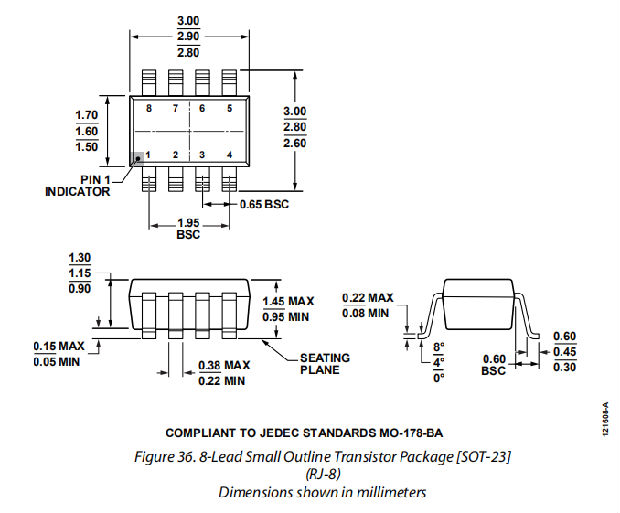

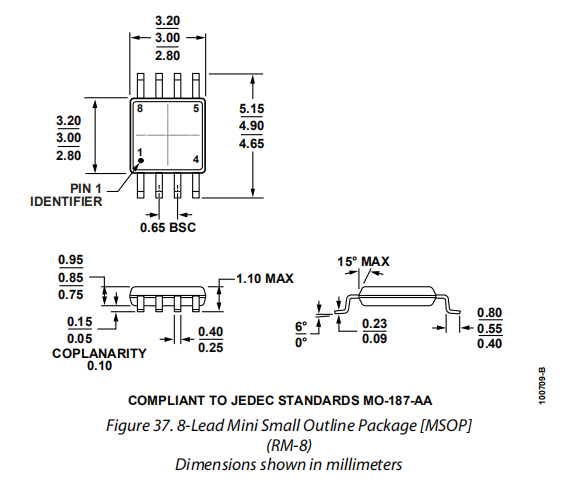

8-引线SOT-23和MSOP封装

应用

传感器接口

电池供电系统

数据采集系统

便携式仪器

一般说明

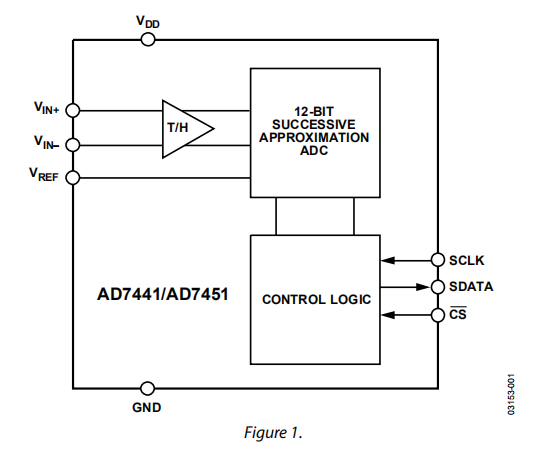

AD7441/AD7451分别是10-/12位高速、低功耗、单电源、逐次逼近(SAR)和模数转换器(adc),具有伪差分模拟输入。这些部件的工作电压为2.7伏至5.25伏,在高达1毫秒/秒的高吞吐率下实现极低的功耗。

AD7441/AD7451包含一个低噪声、宽带宽、差分跟踪保持(T/H)放大器,可处理高达3.5 MHz的输入频率。这些器件的参考电压由外部施加在VREF引脚上,其范围从100 mV到VDD,具体取决于电源和适合的应用。

转换过程和数据采集由CS和串行时钟控制,允许设备与微处理器或DSP接口。转换开始时,输入信号在CS下降沿采样。这些部分的SAR架构确保没有管道延迟。

产品亮点

1、 使用2.7 V至5.25 V电源操作。

2、 高吞吐量,低功耗。AD7441/AD7451采用3V电源,以1 MSPS的吞吐率提供4MW的最大功耗。

3、 伪差分模拟输入。

4、 灵活的电源/串行时钟速度管理。转换率由串行时钟决定,当通过串行时钟速度增加而减少转换时间时,允许功率降低。这些部件还具有关机模式,以在较低的吞吐量下最大限度地提高功率效率。

5、 可变电压参考输入。

6、 没有管道延迟。

7、 通过CS输入和一次性转换控制精确控制采样瞬间。

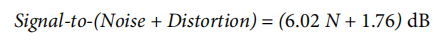

8、 ENOB>10位,典型参考电压为500 mV。

功能框图

时序图

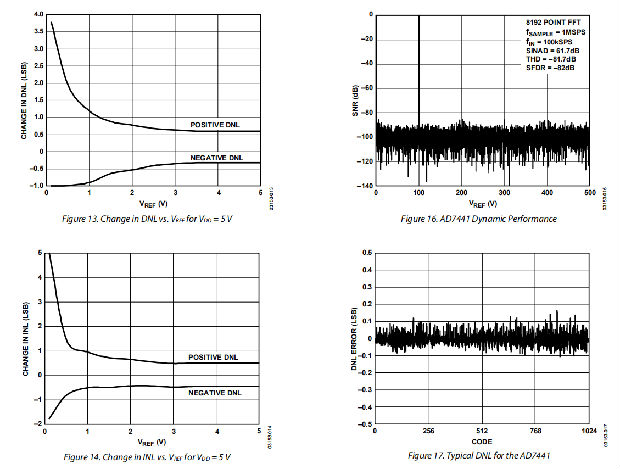

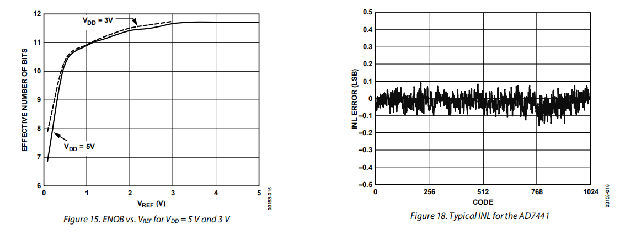

典型性能特征

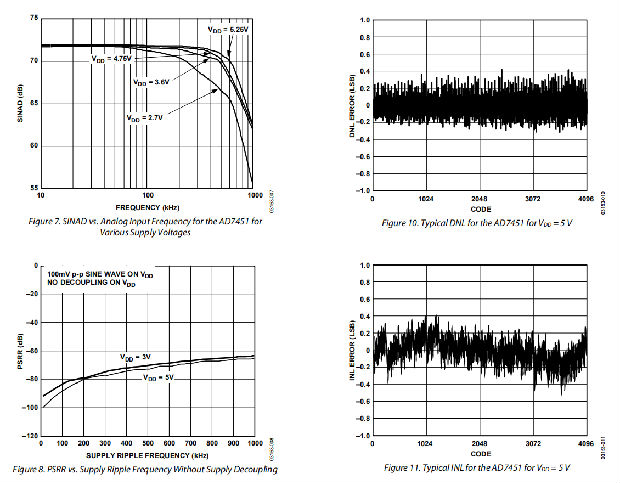

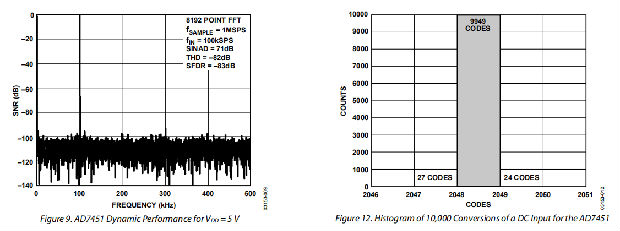

TA=25°C,fS=1 MSPS,fSCLK=18 MHz,VDD=2.7 V至5.25 V,VREF=2.5 V,除非另有说明。

术语

信噪比

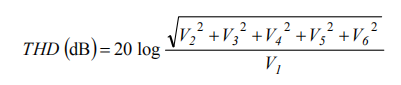

这是在ADC输出端测得的SINAD比率。信号是基波的均方根振幅。噪声是所有非基本信号的总和,不超过采样频率的一半(f/2),不包括直流电。该比率取决于数字化过程中量化层级的数量:层级越多,量化噪音越小。对于具有正弦波输入的理想N位转换器,理论SINAD比由:

因此,对于12位转换器,SINAD为74db;对于10位转换器,SINAD为62db。

总谐波失真(THD)

THD是谐波的均方根和与基波的比值。在AD7441/AD7451中,THD为

式中:V1是基波的均方根振幅。V2、V3、V4、V5和V6是第二至第六次谐波的均方根振幅。

峰值谐波或杂散噪声

基频谐波值(不包括ADC)的最大杂散值fS/2定义为ADC的最大杂散值。通常情况下,该规范的值由频谱中最大的谐波决定,但对于谐波埋在噪声层中的ADC来说,这是一个噪声峰值。

互调失真

当输入由两个频率(fa和fb)的正弦波组成时,具有非线性的有源器件在mfa±nfb的和频和差频下产生畸变产物,其中m,n=0,1,2,3,依此类推。互调失真项是指m和n都不等于零的项。例如,二阶项包括(fa+fb)和(fa−fb),而三阶项包括(2fa+fb)、(2fa−fb)、(fa+2fb)和(fa−2fb)。

AD7441/AD7451使用CCIF标准进行测试,其中两个输入频率接近输入带宽的顶端。在这种情况下,二阶项的频率通常与原始正弦波相距甚远,而三阶项的频率通常接近输入频率。因此,二阶和三阶项是分开指定的。互调失真的计算是根据THD规范进行的,其中它是单个失真产物的rms和与基本原理总和的均方根振幅的比值,用分贝表示。

光圈延迟

这是从采样时钟的前沿到ADC实际采样的时间量。

孔径抖动

这是实际采样的有效时间点上的样本对样本的变化。

全功率带宽

ADC的全功率带宽是指输入频率,在该频率下,重构的基波振幅降低0.1db或3db(对于全刻度输入)。

积分非线性

这是与通过ADC传输函数端点的直线的最大偏差。

微分非线性(DNL)

这是ADC中任何两个相邻代码之间的实测和理想1 LSB变化之间的差值。

偏移误差

这是第一个代码转换(000…000到000…001)与理想状态(即AGND+1 LSB)的偏差。

增益误差

这是偏移误差调整后最后一个代码转换(111…110到111…111)与理想值(即VREF−1 LSB)的偏差。

跟踪并保持采集时间

跟踪保持采集时间是跟踪保持放大器保持在跟踪模式下,使其输出达到并稳定在所应用输入信号的0.5 LSB范围内所需的最短时间。

电源抑制比

电源抑制比定义为满标度频率(f)下ADC输出的功率与应用于频率fS的ADC vdd电源的100 mV p-p正弦波的功率之比。此输入的频率从1 kHz到1 MHz不等。

其中:

Pf是ADC输出中频率f处的功率。

Pfs是ADC输出中频率fs下的功率。

操作理论

电路信息

AD7441/AD7451是10-/12位、高速、低功耗、单电源、逐次逼近、带伪差分模拟输入的模数转换器(ADC)。这些部件使用一个2.7伏到5.25伏的电源供电,当使用18兆赫的SCLK供电时,其吞吐量可达1毫秒/秒。AD7441/AD7451需要对VREF引脚应用外部参考。

AD7441/AD7451有一个SAR ADC,一个片上差分跟踪保持放大器,以及一个串行接口,位于8线SOT-23或MSOP封装中。串行时钟输入从部件访问数据,并为SAR ADC提供时钟源。AD7441/AD7451具有断电选项,可降低转换之间的功耗。断电功能通过标准串行接口实现,如操作模式部分所述。

变频器操作

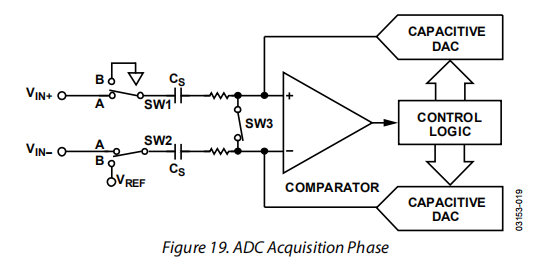

AD7441/AD7451是基于两个电容式dac的SAR adc。图19和图20分别显示了采集和转换阶段ADC的简化示意图。ADC由控制逻辑、一个SAR和两个电容式DAC组成。在图19(采集阶段),SW3闭合,SW1和SW2处于位置A,比较器保持在平衡状态,采样电容器阵列采集输入端的差分信号。

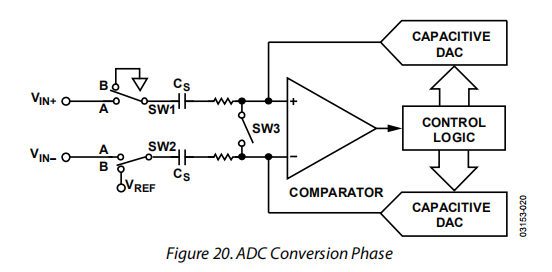

当ADC开始转换时(见图20),SW3打开,SW1和SW2移动到位置B,导致比较器变得不平衡。转换开始后,两个输入断开。控制逻辑和电荷再分配dac用于从采样电容阵列中添加和减去固定数量的电荷,以使比较器回到平衡状态。当比较器重新平衡时,转换完成。控制逻辑产生ADC输出代码。驱动VIN+和VIN-引脚的源的输出阻抗必须匹配;否则两个输入的稳定时间不同,会导致误差。

ADC传递函数

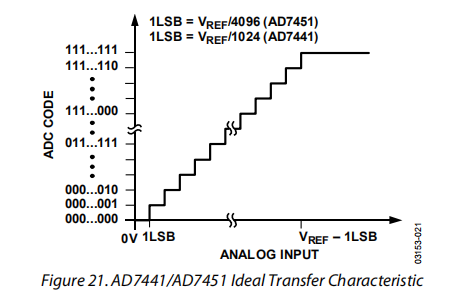

AD7441/AD7451的输出编码是直接(自然)二进制的。设计的代码转换在连续的LSB值(1lsb、2lsb等)下发生。AD7451的LSB大小是VREF/4096,AD7441的LSB大小是VREF/1024。AD7441/AD7451的理想传输特性如图21所示。

典型接线图

图22显示了设备的典型连接图。在此设置中,GND引脚连接到系统的模拟接地层。VREF引脚连接到AD780,AD780是一个2.5V的解耦参考源。信号源通过单位增益缓冲器连接到VIN+模拟输入。将直流电压连接到VIN–引脚,为VIN+输入提供伪接地。用10μF钽电容和0.1μF陶瓷电容将VDD管脚与AGND解耦。使用至少0.1μF的电容器将参考引脚与AGND解耦。转换结果以16位字输出,其中4个前导零,后面是12位或10位结果的MSB。AD7441的10位结果后跟两个尾随零。

模拟量输入

AD7441/AD7451具有伪差分模拟输入。VIN+输入与信号源耦合,必须具有vp-p的振幅,以利用部件的整个动态范围。直流输入被施加到VREF上。施加到该输入上的电压为VIN-输入提供一个接地偏移或伪接地。伪差分输入将模拟输入信号地与ADC地分开,允许取消直流共模电压。

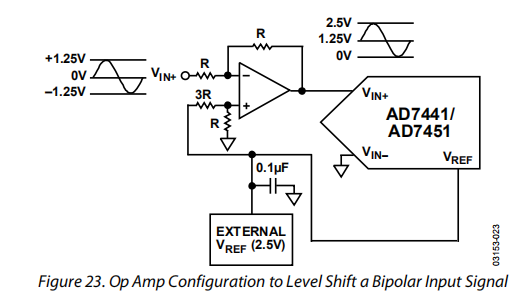

由于ADC是从单一电源供电,所以有必要对地面双极信号进行电平偏移,以满足输入要求。运算放大器(例如,AD8021)可以被配置成重新缩放和电平偏移地基(双极)信号,使其与AD7441/AD7451的输入范围兼容(参见图23)。

当转换发生时,伪地对应于0,最大模拟输入对应于AD7451的4096和AD7441的1024。

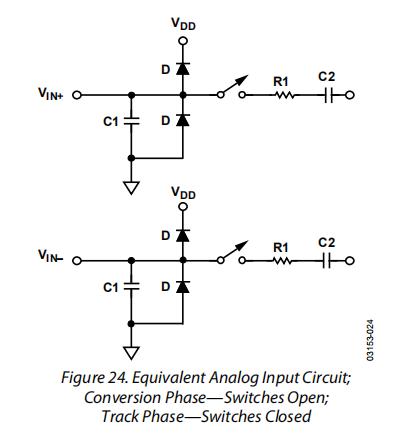

模拟输入结构

图24显示了AD7441/AD7451模拟输入结构的等效电路。四个二极管为模拟输入提供ESD保护。必须注意确保模拟输入信号不会超过电源轨300毫伏以上。这导致这些二极管正向偏压并开始传导到基片中。这些二极管可传导高达10毫安,而不会对零件造成不可逆转的损坏。C1电容器(见图24)通常为4 pF,主要归因于管脚电容。电阻器是由开关的导通电阻组成的集中元件。这些电阻器的值通常约为100Ω。C2电容器是ADC采样电容器,通常具有16 pF的电容。

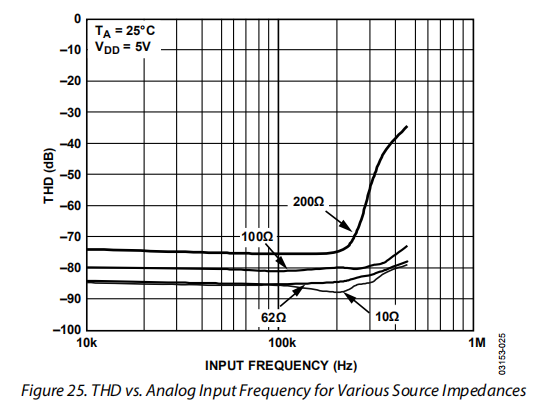

对于交流应用,建议通过在相关模拟输入引脚上使用RC低通滤波器从模拟输入信号中移除高频分量。在谐波失真和信噪比非常重要的应用中,建议从低阻抗源驱动模拟输入。大的源阻抗会显著影响ADC的交流性能,这就需要使用输入缓冲放大器。放大器的选择是特定应用的函数。

当没有放大器用于驱动模拟输入时,建议将源阻抗限制在低值。最大源阻抗取决于可容忍的总谐波失真量。THD随着源阻抗的增加和性能的降低而增大。

图25显示了不同源阻抗下THD与模拟输入信号频率的关系图。

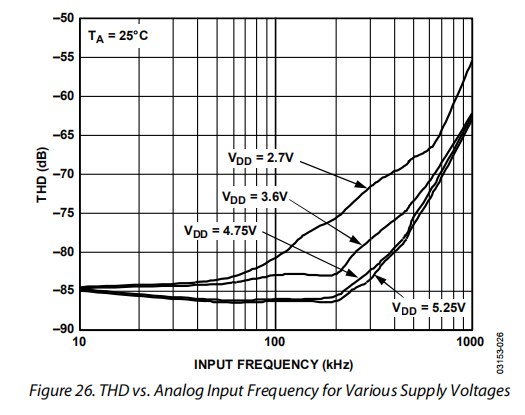

图26显示了不同电源电压下THD与模拟输入频率的关系图,而采样频率为1 MSPS,SCLK为18 MHz。在这种情况下,源阻抗为10Ω。

数字输入

应用于AD7441/AD7451的数字输入不受限制模拟输入的最大额定值的限制。相反,应用的数字输入,即CS和SCLK,可以达到7V,并且不受模拟输入上VDD+0.3V限制的限制。输入不受VDD+0.3v限制的主要优点是避免了电源排序问题。如果在VDD之前应用了CS或SCLK,则不会出现闭锁风险,因为在VDD之前应用大于0.3V的信号时,模拟输入会出现闭锁。

参考文献

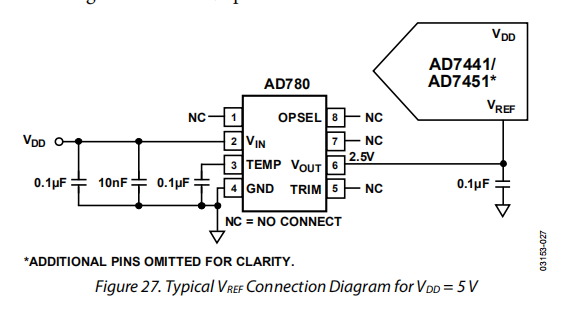

需要外部电源为AD7441/AD7451提供参考。该参考输入的范围从100毫伏到VDD。对于2.7 V至5.25 V的电源,规定的参考电压为2.5 V。为应用选择的参考输入不得大于电源。参考源中的误差会导致AD7441/AD7451传输函数中的增益误差,并增加部件的指定满标度误差。VREFpin上必须放置至少0.1μF的电容器。AD7441/AD7451的合适参考源包括AD780和ADR421。图27显示了VREF引脚的典型连接图。

串行接口

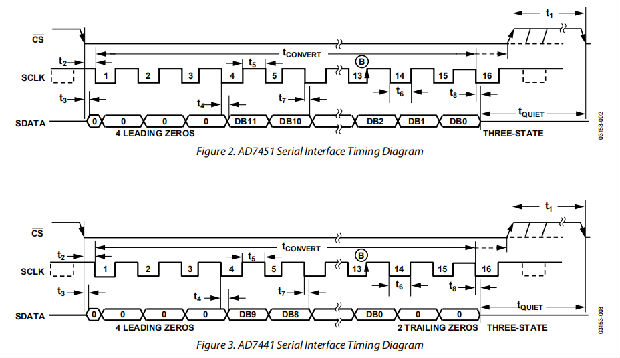

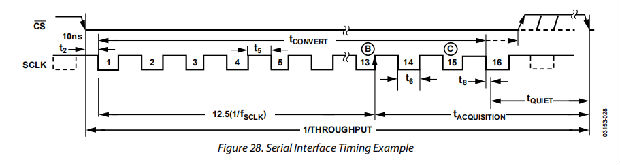

图2和图3分别显示了AD7451和AD7441串行接口的详细时序图。串行时钟提供转换时钟,并在转换期间控制来自设备的数据传输。

CS启动转换过程并设置数据传输帧。

CS的下降沿使轨道保持进入保持模式,并使总线脱离三种状态。对模拟输入进行采样,此时开始转换。转换需要16个SCLK周期才能完成。

一旦出现13个SCLK下降沿,跟踪并保持在下一个SCLK上升沿上回到跟踪模式,如图2和图3中的B点所示。在第16个SCLK下降沿,SDATA线回到三个状态。

如果CS上升沿出现在16个SCLK之前,则转换终止,SDATA线路返回到3个状态。

来自AD7441/AD7451的转换结果作为串行数据流提供在SDATA输出上。这些位在SCLK输入的下降沿时钟输出。AD7451的数据流由四个前导零和12位转换数据组成,先提供MSB。AD7441的数据流由四个前导零组成,后面是10位转换数据,后面是两个尾随的零,这也是首先提供给MSB的。在这两种情况下,输出编码都是直接(自然)二进制的。

执行转换需要16个串行时钟周期以及从AD7441/AD7451访问数据。CS变低提供DSP或微控制器读入的第一个前导零。然后,剩余数据从第二个前导零开始,在随后的SCLK下降沿上计时。因此,串行时钟上的第一下降时钟边缘提供第二前导零。数据传输中的最后一位在第16个下降沿有效,在前一个(15)下降沿已打卡。一旦转换完成,并且在16个时钟周期之后访问了数据,重要的是要确保在开始下一个转换之前,有足够的时间来满足采集和安静时间规范(参见定时示例1和定时示例2部分)。为了使用18MHz时钟实现1 MSPS,18时钟脉冲串执行转换,并在下一次转换之前留出足够的时间用于采集和安静时间。

在具有较慢SCLK的应用中,可以在每个SCLK上升沿(即SCLK的第一个上升沿)读入数据在CS下降沿提供了前导零,并且第15个SCLK边缘提供了DB0。

定时示例1

fSCLK=18mhz,吞吐量为1msps,周期时间为:

周期包括:

因此,如果t2=10 ns,则

这296纳秒满足290纳秒的默契要求。

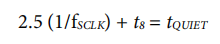

从图28可以看出,默契包括:

式中t8=35ns。这允许tQUIET的值为122 ns,满足60ns的最低要求。

定时示例2

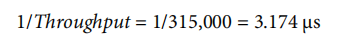

如果fSCLK=5 MHz和315 kSPS的吞吐量,则周期时间为:

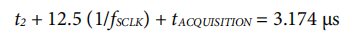

周期包括:

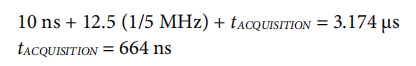

因此,如果t2为10 ns,则

此664 ns满足290 ns的要求默契。来自图28,默契包括:

式中t8=35ns。这允许tQUIET的值为129 ns,满足60ns的最低要求。

在这个例子中,以及其他较慢的时钟值,信号可以在转换完成之前获得,但是仍然需要在转换之间留出60 ns的最小值。在实施例2中,在图28中的大约C点处完全获取信号。

操作模式

AD7441/AD7451的工作模式是通过在转换期间控制CS信号的逻辑状态来选择的。有两种工作模式:正常模式和断电模式。转换启动后CS被拉高的点决定了部件是否进入断电模式。

同样,如果已经断电,CS控制设备是恢复正常运行还是保持断电。这些模式提供了灵活的电源管理选项,可以针对不同的应用需求优化功耗/吞吐量比率。

正常模式

此模式用于实现最快的吞吐量性能。当AD7441/AD7451始终保持完全通电时,用户不必担心任何通电时间。图29显示了AD7441/AD7451在该模式下的运行示意图。转换开始在CS的下降沿(见串行接口部分)。到确保零件保持完全通电,CS必须保持在较低位置,直到CS下降沿后经过至少10个SCLK下降沿。

如果CS在第10个SCLK下降沿之后,但在第16个SCLK下降沿之前的任何时间处于高电平,则部件保持通电,但是转换终止,SDATA返回到三个状态。完成转换和访问完整转换需要16个串行时钟周期结果。CS可以高怠速直到下一次转换,也可以低怠速到下一次转换之前的某个时间。一旦数据传输完成,也就是说,当SDATA返回到三个状态时,另一个转换可以在安静时间tQUIET之后启动,从而使CS变低。

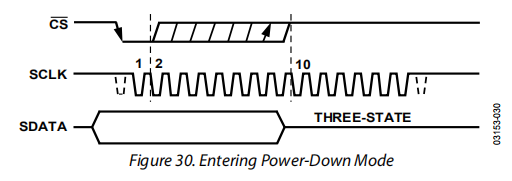

断电模式

此模式适用于要求较低吞吐量的应用程序;在每次转换之间关闭ADC,或以高吞吐量执行一系列转换,然后在这些转换突发之间关闭ADC一段相对较长的时间。当AD7441/AD7451处于断电模式时,所有模拟电路均断电。为了使AD7441/AD7451进入断电模式,转换过程必须中断,在SCLK的第二个下降沿之后和第十个下降沿之前的任何地方使CS高,如图30所示。

一旦CS在SCLKs窗口中处于高位,部件进入断电状态,CS下降沿启动的转换终止,SDATA返回到三个状态。从CS上升沿到SDATA三态启用的时间永远不大于t8(请参阅章节)。如果定时规格CS在第二个SCLK下降沿之前变高,则部件将保持在正常模式并且不会断电。这避免了由于CS线路故障而导致的意外断电。

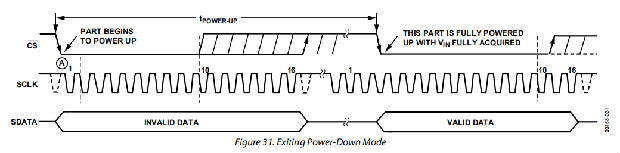

要退出掉电模式并再次接通AD7441/AD7451的电源,执行虚拟转换。在CS的下降沿,设备开始通电,只要CS保持在低位,直到第10个SCLK下降沿之后,设备就会继续通电。设备在1μs后完全通电,如中所示,下一次转换产生有效数据。

如果在SCLK的第10个下降沿之前CS处于高位,则AD7441/AD7451将再次进入断电状态。这避免了由于CS线路上的故障或CS较低时8个SCLK周期的意外突发而导致的意外加电。所以尽管设备可能在CS下降沿开始通电,只要它发生在第10个SCLK下降沿之前,它就会再次在CS上升沿断电。

通电时间

AD7441/AD7451的通电时间通常为1μs,这意味着在SCLK的任何频率高达18mhz时,一个虚拟周期始终足以允许设备通电。一旦虚拟循环完成,ADC将完全通电,并正确获取输入信号。静态时间tQUIET必须仍然允许从虚拟转换后总线返回到三个状态的点开始CS的下一个下降边缘。

当以1 MSPS的最大吞吐量运行时,AD7441/AD7451在一个虚拟周期(即1μs)内通电并获取±0.5 LSB的信号。当从具有虚拟循环的断电模式通电时,如图31所示,在部件断电时处于保持模式的跟踪和保持在第一次之后返回到跟踪模式SCLK边缘零件在CS下降沿后接收。如图31中的A点所示。

尽管在任何SCLK频率下,一个虚拟周期足以为设备通电并获取VIN,但并不一定意味着必须始终经过16个SCLK的完整虚拟周期来通电并完全获取VIN;1μs足以通电设备并获取输入信号。

例如,当将5mhz SCLK频率应用于ADC时,周期时间为3.2μs(即1/(5mhz)×16)。在一个虚拟循环中,3.2μs,部件通电,并完全获得VIN。然而,在使用5mhz SCLK的1μs后,仅经过5个SCLK周期。在此阶段,ADC已完全通电,并且获取信号。因此,在这种情况下,CS可以在第10个SCLK下降沿之后升高,并在一个时间tQUIET之后再次降低,以启动转换。

当电源首次应用于AD7441/AD7451时,ADC可在断电模式或正常模式下通电。因此,最好允许虚拟循环过去,以确保零件在尝试有效转换之前完全通电。同样,如果用户希望部件在断电模式下通电,那么可以使用虚拟循环来确保设备处于断电模式,方法是执行图30中所示的循环。一旦向AD7441/AD7451供电,通电时间与从断电模式通电的时间相同。正常模式下完全通电大约需要1μs。在执行虚拟循环之前,无需等待1μs,以确保所需的操作模式。相反,在向ADC供电后,可以直接发生假周期。如果在虚拟转换之后直接执行第一次有效转换,则必须注意确保允许足够的采集时间。

如前所述,当从断电模式通电时,部件在第一个SCLK边缘返回到跟踪模式在CS下降沿后使用。然而,当ADC在电源接通后开始通电时,跟踪保持已经处于跟踪模式。这意味着(假设有监控ADC电源电流的设备),如果ADC在所需的操作模式下通电,则无需假周期来改变模式。因此,也不需要假循环来放置轨道并保持在轨道上。

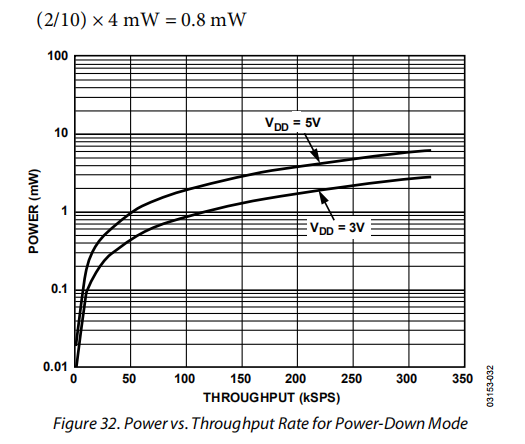

功率与吞吐量

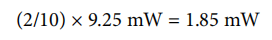

通过在不转换时在设备上使用断电模式,ADC的平均功耗在较低的吞吐量下降低。图32显示了当吞吐量降低时,设备如何在断电状态下保持更长时间,并且平均功耗也相应降低。例如,如果AD7441/AD7451以100ksps的吞吐量和18mhz的SCLK在连续采样模式下工作,并且设备在转换之间处于断电模式,则正常操作期间的功耗最大等于9.25mw(对于VDD=5v)。

如果通电时间是一个虚拟周期(1μs),剩余的转换时间是另一个周期(1μs),那么可以说AD7441/AD7451在每个转换周期中消耗9.25 mW,持续2μs。(此功耗数据假定进入断电模式的时间非常短。随着用于进入断电模式的时钟脉冲数的增加,此功率值也会增加)。AD7441/AD7451的剩余8μs功耗仅为5μW。

计算图32中的幂数如下:

如果吞吐量=100ksps,则循环时间=10μs,每个周期消耗的平均功率为:

在相同的情况下,如果VDD=3v,正常运行期间的功耗最大为4mw。

现在可以说AD7441/AD7451在每个转换周期中耗散4mw,持续2μs。

因此,在吞吐量为100 kSPS的每个循环中消耗的平均功率为,

为了在320 kSPS以上的吞吐量下获得最佳的功率性能,建议降低串行时钟频率。

微处理器与DSP接口

AD7441/AD7451上的串行接口允许部件直接连接到一系列不同的微处理器上。本节介绍如何将AD7441/AD7451与一些更常见的微控制器和DSP串行接口协议相连接。

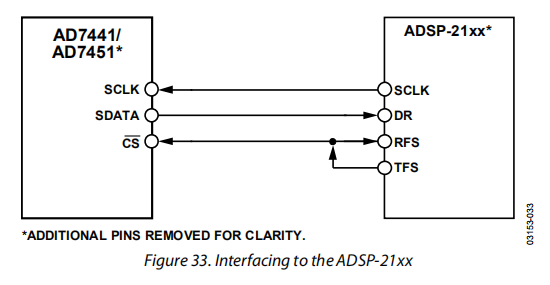

AD7441/AD7451至ADSP-21xx

ADSP-21xx系列DSP直接与AD7441/AD7451接口,无需任何粘合逻辑。运动控制寄存器的设置如下:

TFSW=RFSW=1 交替框架

INVRFS=INVTFS=1 激活低帧信号

DTYPE = 00 右对齐数据

SLEN=1111 16位数据字

ISCLK=1 内部串行时钟

TFSR=RFSR=1 把每一个字框起来

IRFS = 0

ITFS = 1

为了实现掉电模式,将SLEN设置为1001以发出8位SCLK突发。

连接图如图33所示。ADSP-21xx将运动的TFS和RFS捆绑在一起,TFS被设置为输出,RFS被设置为输入。DSP以交替成帧模式工作,运动控制寄存器按说明设置。在上生成的帧同步信号TFS与CS相连,并且,与所有信号处理应用一样,等距采样是必需的。然而,在本例中,定时器中断用于控制ADC的采样率,并且在某些情况下,不能实现等距采样。

例如,定时器寄存器加载一个值,该值在所需的采样间隔内提供中断。当接收到中断时,用TFS/DT(ADC控制字)传输一个值。TFS用于控制RFS,从而控制数据的读取。串行时钟的频率设置在SCLKDIV寄存器中。当使用TFS发送指令时,即AX0=TX0,检查SCLK的状态。DSP等待SCLK变高、变低和变高后,才开始传输。如果定时器和SCLK值的选择使得要发送的指令发生在SCLK的上升沿上或附近,则可以传输数据或等待下一个时钟边缘。

例如,ADSP-2111的主时钟频率为16mhz。如果SCLKDIV寄存器加载值为3,则获得2 MHz的SCLK,并且每一个SCLK周期经过8个主时钟周期。如果定时器寄存器加载值803,则在中断之间以及随后的传输指令之间发生100.5 SCLK。由于传输指令发生在SCLK边缘,这种情况导致非平衡采样。如果中断之间的sclk数是N的整数,则由DSP实现等距采样。

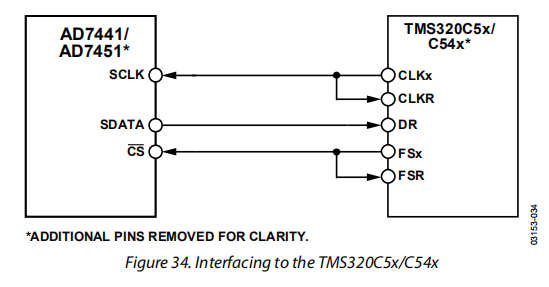

AD7441/AD7451至TMS320C5x/C54x

TMS320C5x/C54x上的串行接口使用连续的串行时钟和帧同步信号,将数据传输操作与AD7441/AD7451等外围设备同步。CS输入允许在TMS320C5x/C54x和AD7441/AD7451之间轻松连接,无需任何粘合逻辑。TMS320C5x/C54x的串行端口设置为在内部CLKx(Tx串行时钟)和FSx(Tx帧同步)的突发模式下工作。串行端口控制寄存器(SPC)必须具有以下设置:FO=0、FSM=1、MCM=1和TXM=1。格式位FO可以设置为1,将字长度设置为8位,以便在AD7441/AD7451上实现断电模式。连接图如所示。注意,对于信号处理应用,来自TMS320C5x/C54x的帧同步信号必须提供等距采样。

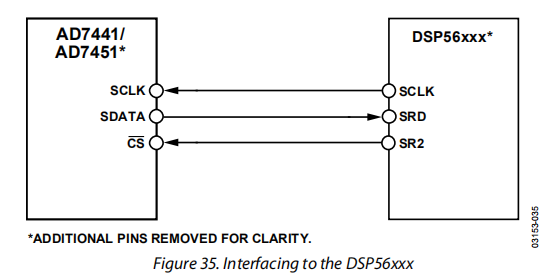

AD7441/AD7451至DSP56xxx

图35中的连接图显示了如何将AD7441/AD7451连接到摩托罗拉DSP56xxx系列DSP的SSI(同步串行接口)。SSI在同步模式下运行(CRB中的SYN位=1),内部生成的1位时钟周期帧同步用于Tx和Rx(CRB中的位FSL1=1和位FSL0=0)。通过在CRA中设置位WL1=1和位WL0=0,将字长度设置为16。为了在AD7441/AD7451上实现断电模式,可以通过在CRA中设置B it WL1=0和Bit WL0=0将字长度更改为8位。注意,对于信号处理应用,来自DSP56xxx的帧同步信号必须提供等距采样。

接地和布局提示

安装AD7441/AD7451的印刷电路板的设计必须使模拟和数字部分分开并限制在电路板的某些区域内。这有助于使用容易分离的地平面。最小腐蚀技术通常对接地层最好,因为它提供了最好的屏蔽。数字和模拟接地层只能在一个地方连接:一个星形接地点,尽可能靠近AD7441/AD7451上的GND引脚。

避免在设备下方运行数字线路,因为这会将噪声耦合到模具上。模拟接地层必须允许在AD7441/AD7451下运行,以避免噪声耦合。连接到AD7441/AD7451的电源线必须使用尽可能大的迹线,以提供低阻抗路径,并减少故障对电源线的影响。

时钟等快速开关信号必须用数字接地屏蔽,以避免辐射噪声到电路板的其他部分,时钟信号决不能在模拟输入附近运行。避免数字和模拟信号交叉。电路板两侧的迹线必须彼此成直角。这减少了电路板上的馈通效应。微带技术是目前为止最好的,但并不总是可以与双面板。

在这种技术中,电路板的元件侧专用于接地层,而信号则放在焊料侧。良好的解耦也很重要。所有模拟电源必须与10μF钽电容器并联,0.1μF电容器接地。为了从这些解耦组件中获得最佳效果,它们必须尽可能靠近设备。

评估绩效

评估板包包括一个完全组装和测试的评估板、文档和软件,用于通过评估板控制器从PC控制板。评估板控制器可与AD7441和AD7451评估板以及许多其他模拟设备,包括以CB指示符结尾的评估板一起使用,以演示和评估AD7441和AD7451的交流和直流性能。

该软件允许用户在AD7441/AD7451上执行ac(快速傅立叶变换)和dc(代码直方图)测试。有关更多信息,请参阅评估工具包附带的AD7441/AD7451应用说明。

外形尺寸

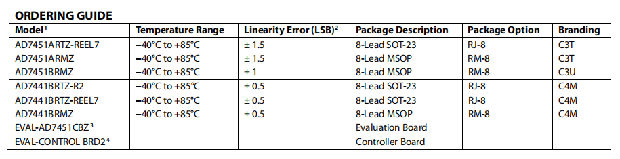

1、Z=符合RoHS的零件。

2、这里的线性误差是指积分非线性误差。

3、它可以用作独立的评估委员会,也可以与评估委员会控制器一起使用,以进行评估/演示。

4、评估板控制器是一个完整的单元,允许PC控制所有模拟设备,并与以CB标志结束的所有模拟设备进行通信。要订购完整的评估套件,您必须订购ADC评估板(EVAL-AD7451CB或EVAL-AD7441CB)、EVAL-CONTROL BRD2和一台12伏交流变压器。有关更多信息,请参阅评估工具包附带的AD7451/AD7441应用说明。