CDCE421点击型号即可查看芯片规格书

特征

•单个3.3V电源

•高性能时钟发生器,包括集成频率合成器的晶体振荡器电路

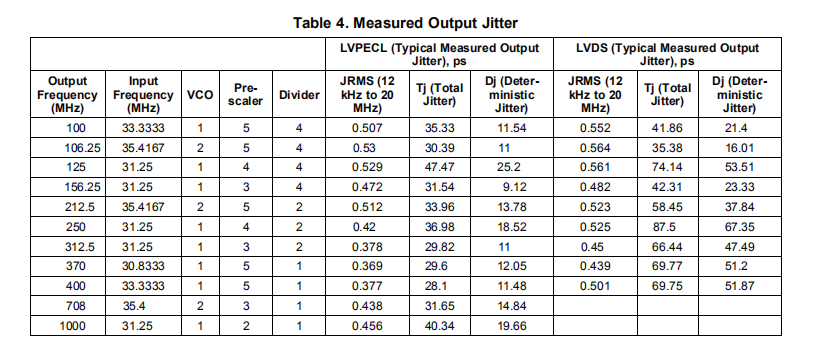

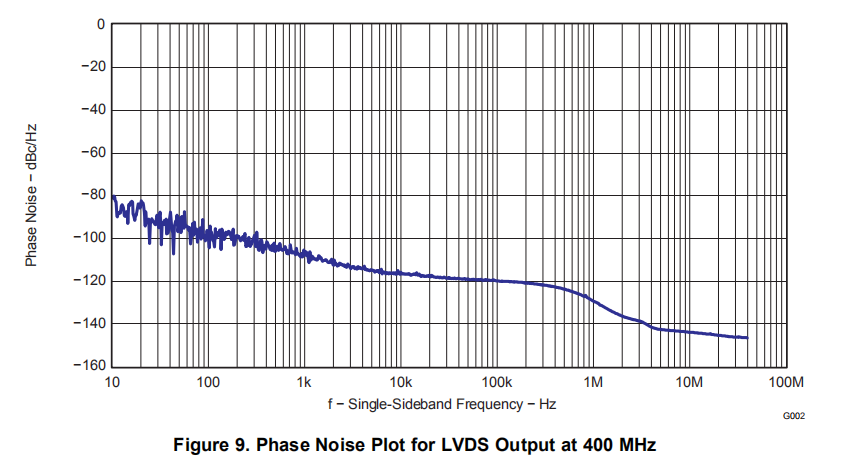

•低输出抖动,低至380 fs(rms集成在10 kHz–20 MHz之间)

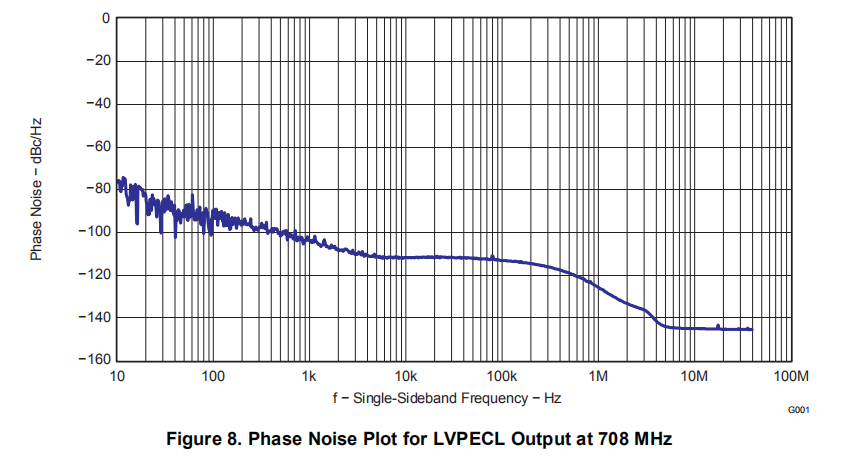

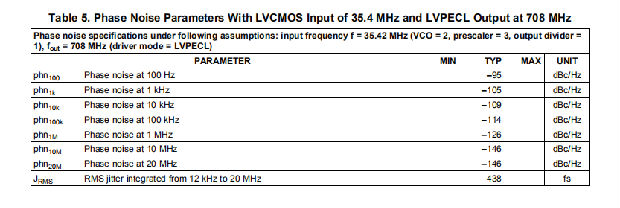

•高频下的低相位噪声;在708 MHz时,在10 kHz时小于-109 dBc/Hz,在10 MHz偏移下小于-146 dBc/Hz

•支持27.35 MHz到38.33 MHz之间的晶体频率

•输出频率范围从10.9 MHz到766.7 MHz,从875.2 MHz到1175 MHz

•低压差分信号(LVDS)输出,100-Ω差分片外终端,10.9-MHz至400 MHz频率范围

•差分低压正射极耦合逻辑(LVPECL)输出,10.9-MHz至1.175-GHz频率范围

•两个完全集成的压控振荡器(VCO)支持宽输出频率范围

•全集成可编程环路滤波器

•LVDS模式下的典型功耗为240兆瓦,LVPECL模式下为300兆瓦

•芯片启用控制引脚

•简单的串行接口允许在制造后编程

•集成片上非易失性存储器(EEPROM),无需向设备施加高压即可存储设置

•模具或QFN24包装

•ESD保护超过2 kV HBM

•工业温度范围–40°C至85°C

应用

•低成本、高频晶体振荡器

说明

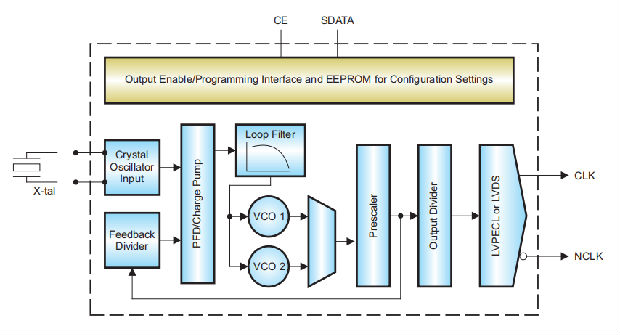

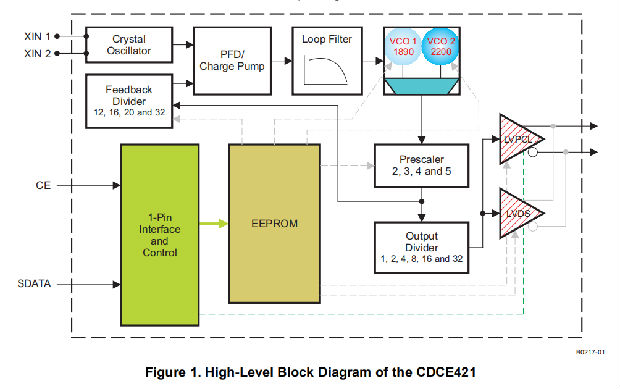

CDCE421是一种高性能、低相位噪声的时钟发生器。它有两个完全集成、低噪声、基于LC的压控振荡器(VCO),工作频率范围为1.750-2.350-GHz。它有一个集成晶体振荡器,与外部AT切晶体一起工作,为基于PLL的频率合成器产生稳定的频率基准。

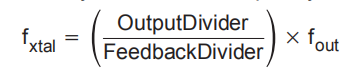

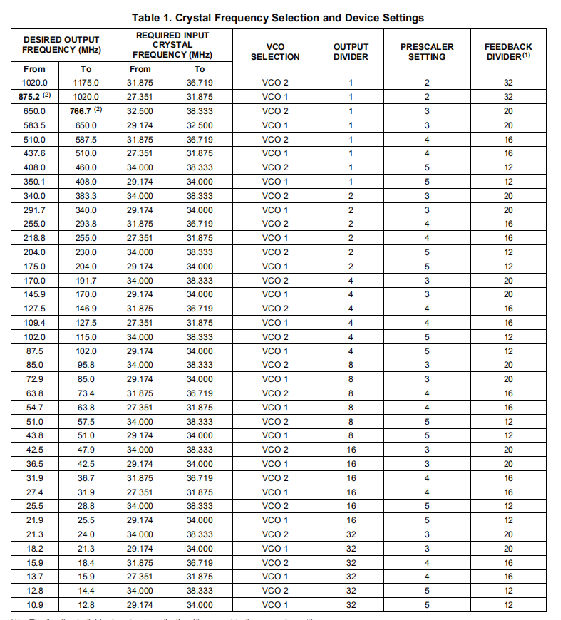

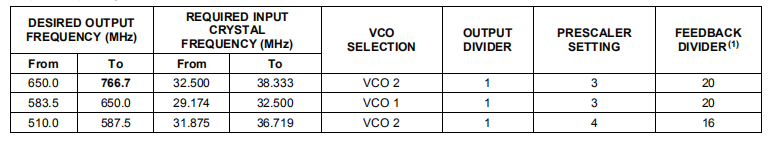

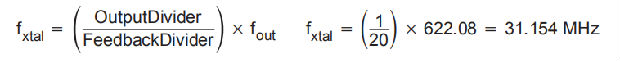

输出频率(fout)与输入晶体(fxtal)的频率成正比。预分频器、反馈分频器、输出分频器和VCO选择是相对于(fxtal)设置的(fout)。对于所需频率(fout),请查看表1,并在同一行中找到相应的设置。使用方程式1计算所需输出所需的精确晶体振荡器频率。

输出分配器(1)=1、2、4、8、16或32

反馈分配器(2)=12、16、20或32

(1)、输出分配器和反馈分配器应来自表1中的同一行。

(2)、反馈分频器根据表1中的预分频器设置自动设置。

CDCE421的高级框图如图1所示。

CDCE421支持一个差分LVDS时钟输出或一个差分LVPECL输出。

所有设备设置可通过德州仪器专有的简单串行接口进行编程。

该装置在3.3V供电环境下工作,其特点是在-40°C至85°C之间工作。

CDCE421有模具或QFN-24包装。

在CDCE421中,反馈分频器根据预分频器设置自动设置。预分频器和反馈分频器的乘积为60或64,如表1所示,以保持控制回路的稳定。

设备设置和配置

(1)、反馈分频器根据预分频器设置自动设置。

(2)、频率范围不连续

设备设置示例

下面的例子说明了计算产生所需输出频率所需的切割晶体频率的过程。

假设需要产生622.08MHz的输出频率,表1显示期望的输出频率在583.5和680MHz之间。

(1)、反馈分频器根据预分频器设置自动设置。

因此,这意味着设备必须配置:

VCO=VCO 1

输出分配器=1

预分频器设置=3

为了确定在这些设置下获得622.08MHz所需的正确晶体频率,将数值代入方程式1。

AT切频应为31.154 MHz(介于29.174 MHz和32.500 MHz之间)。如表1所示)。

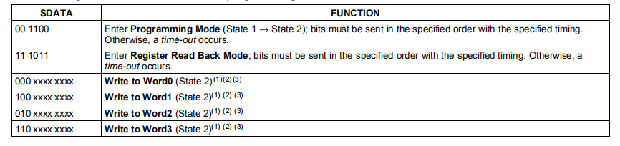

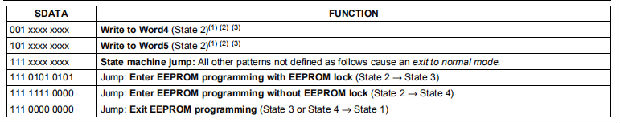

串行接口与控制

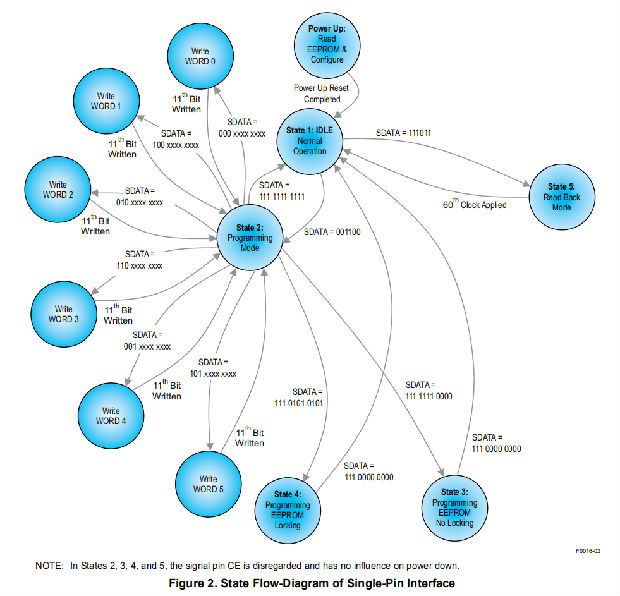

CDCE421使用独特的德州仪器专有接口协议,可通过设备的单个输入引脚进行配置和编程。架构只允许从这个输入引脚写入设备。读取寄存器的内容可以通过在输入pin上发送read命令并监视输出pin(LVDS或LVPECL)来实现。在输出引脚不能用于读取内容的情况下,控制接口的软件必须说明写入EEPROM的内容以及编程时间。监控输出验证编程模式,并循环通电设备验证EEPROM是否保持正确配置。

CDCE421可通过SDATA输入引脚进行配置和编程。为此,方波编程序列必须写入设备,如下节所述。在EEPROM编程阶段,设备需要3.3 V±100 mV的稳定VCC,以安全写入EEPROM单元。每次写入WordX后,写入的数据被锁存、生效,并在实际数据存储到EEPROM之前提供前瞻性。

下表总结了所有有效的编程命令。

(1)、每个上升沿都会导致一个位被锁定。

(2)、在位之间,可能会出现一些更长的时间延迟,但这对数据没有影响。

(3)、写入WordX的长度预计为10位。在第10位之后,相应的字被锁存,其效果可以作为前瞻函数来观察。

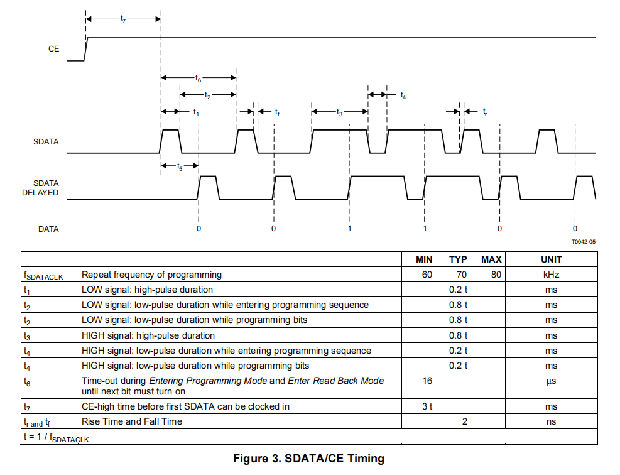

进入编程模式

图3显示了要写入SDATA的数据的计时行为。显示的顺序是00 1100。如果高周期短于t1,则将其解释为0。如果高周期与t3一样长,则将其解释为1。这种行为是通过将输入信号SDATA按时间t5转换为信号SDATA_DELAYED来实现的。如图3所示,SDATA_DELAYED可用于锁存(或选通)SDATA。t1–t7、tr和tf的定时规范如图3所示。

EEPROM编程

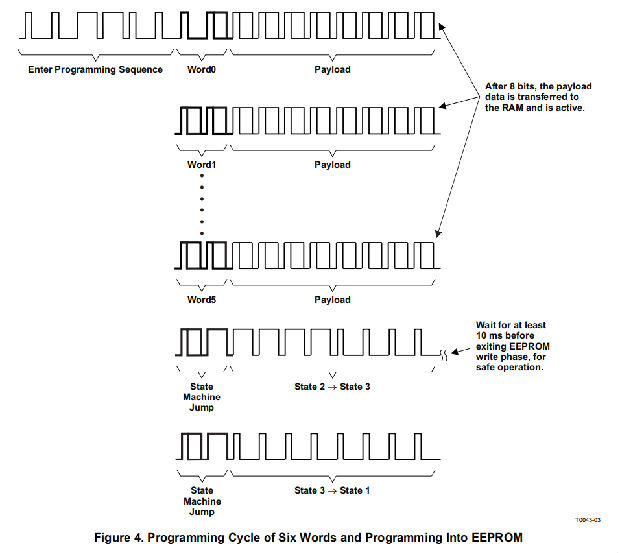

通过写入Word0到Word5来加载RAM中的所有寄存器,在返回到状态2之后,再进入状态3(编程EEPROM,不锁定)或状态4(对EEPROM进行锁定编程),Word0–Word5的内容保存在EEPROM中。对EEPROM编程时,在状态3或状态4下等待10毫秒,然后再转到状态2(空闲状态)。

注:当通过串行总线写入设备进行功能测试和验证时,只访问RAM。

例:6字编程周期及EEPROM编程

下面的序列显示了如何进入编程模式以及如何编写不同的单词。单词0…单词5的地址以粗体显示。在单词address之后,相应单词的有效负载被记录下来。在这个例子中,接下来是从状态2→状态3跳转进入带有EEPROM锁的EEPROM编程。在EEPROM编程状态下,需要等待至少10毫秒才能安全编程。最后一个命令是从状态3跳转到状态1(正常操作)。重新通电并确认设备是否按程序运行。

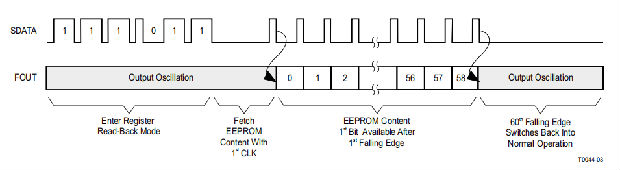

进入寄存器回读模式及相关时序图

与进入编程模式序列类似,进入寄存器读回模式写入SDATA。命令发出后,SDATA输入被重新配置为时钟输入。通过应用一个时钟,EEPROM内容被读入移位寄存器。现在,通过在SDATA上进一步应用时钟,EEPROM内容可以在OUTP/OUTN处时钟输出和观察。有59位要计时。随着第61个时钟上升沿,输出/输出引脚重新配置为正常工作。

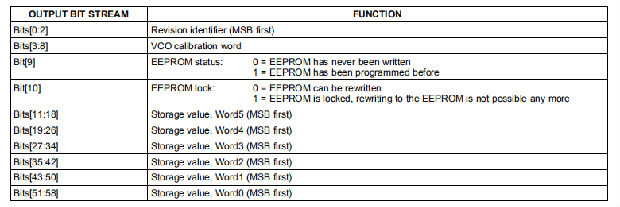

下表总结了输出比特流的内容。需要注意的是:位0首先被打卡。

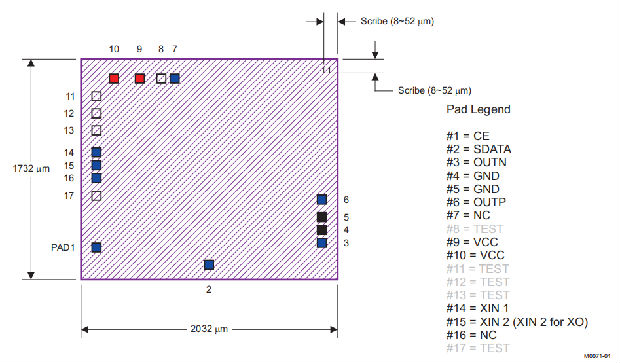

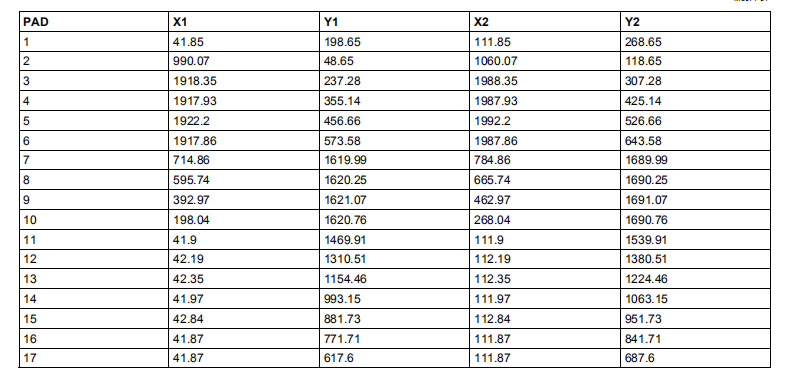

包装(模具)

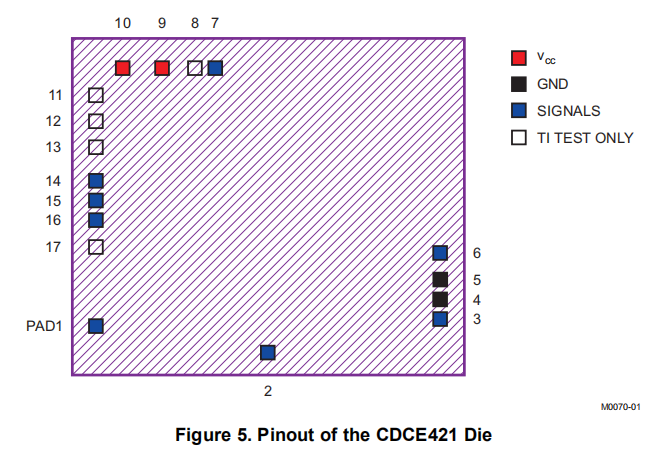

CDCE421有模具或QFN 24针封装。模具版本垫的位置和编号如图5所示。

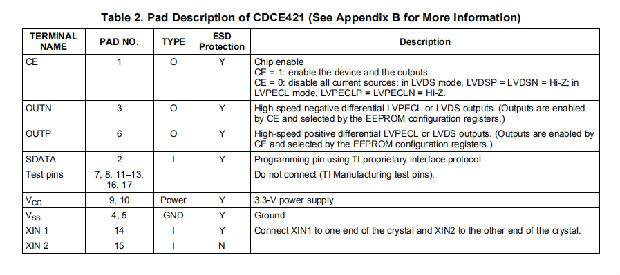

焊盘说明

表2显示了CDCE421模具的引脚描述。

包装(QFN24)

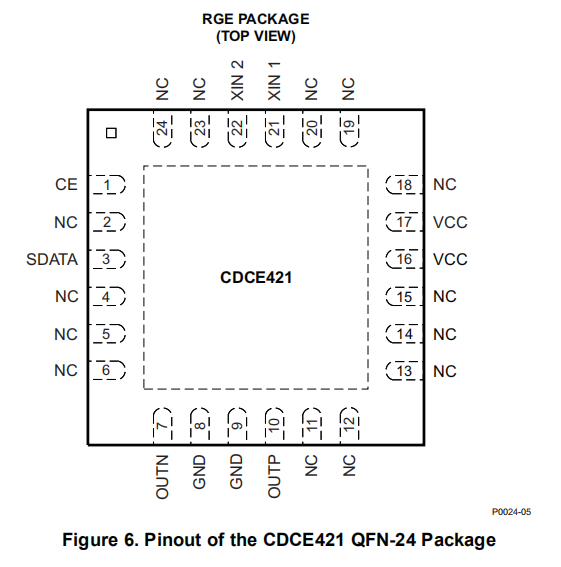

CDCE421还采用QFN 24针封装。显示了QFN包的占地面积。焊盘位置和编号如图6所示。

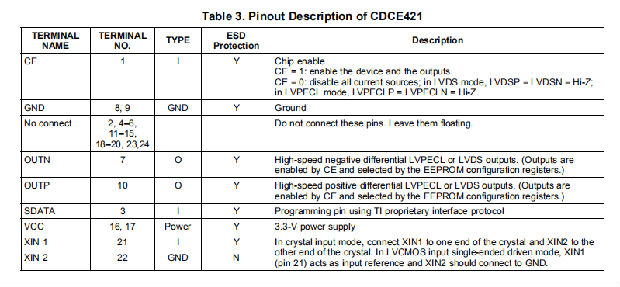

管脚说明

表3显示了CDCE421 QFN-24封装的引脚描述。

输出(LVPECL或LVDS)

CDCE421设备有两组输出驱动器,LVPECL和LVDS,其中的输出是线或在一起的。一次只能选择一个输出;另一个则进入高阻抗状态(Hi-Z)。

如果设备配置为LVPECL,输出缓冲器转到Hi-Z,终端电阻确定设备禁用模式(CE=L)下输出的状态(LVPECLP=LVPECLN=Hi-Z)。如果设备配置为LVDS模式,如果设备被禁用(CE=L),输出将转到Hi-Z。

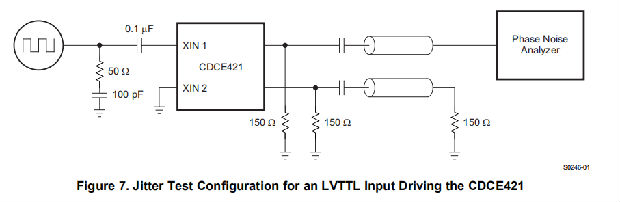

输入时钟模式下的抖动特性

使用LVCMOS输入信号驱动封装在QFN-24封装中的CDCE421器件来执行抖动特性测试。

对于CDCE421被35.42mhz的外部和更干净的LVCMOS输入参考的情况,图8显示了在708mhz从100hz到40mhz的输出的SSB相位噪声图。注意输出抖动对输入参考抖动的依赖性。测试设置见图13。

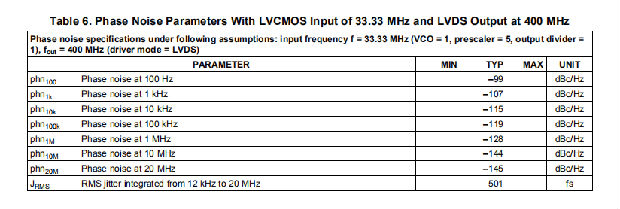

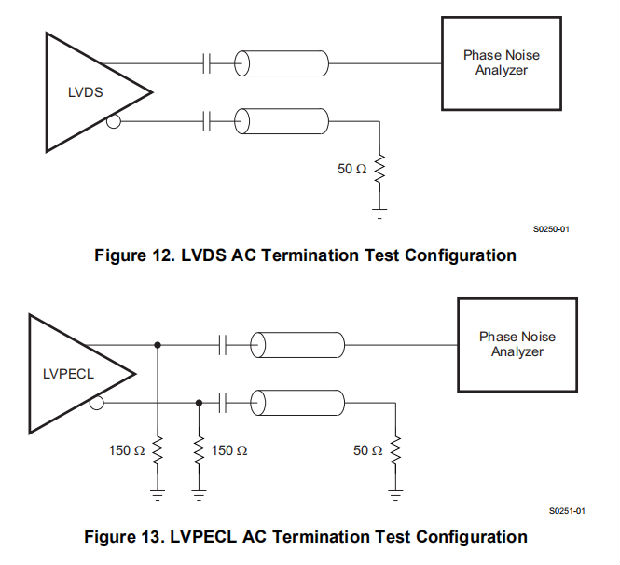

对于CDCE421被33.33mhz的干净外部LVCMOS输入所引用的情况,图9显示了载波在400mhz从100hz到40mhz的输出的SSB相位噪声图。测试设置见图12。

附录A:测试配置

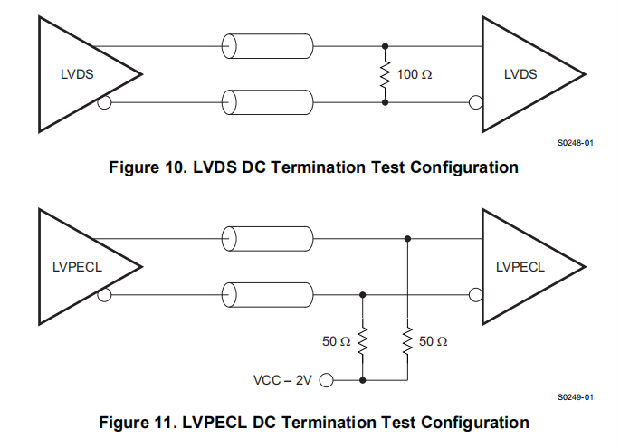

测试设置用于描述CDCE421设备在交流和直流终端。下图说明了用于终止被测设备驱动的时钟信号的所有四种设置。

附录B:包装

CDCE421的包装和接线由振荡器供应商负责。

CDCE421被设计成安装在一个常用的6针振荡器封装中,其中pin2(N/C)是编程管脚,与用于XO设计的CE一起使用。