DS90LV047A点击型号即可查看芯片规格书

特征

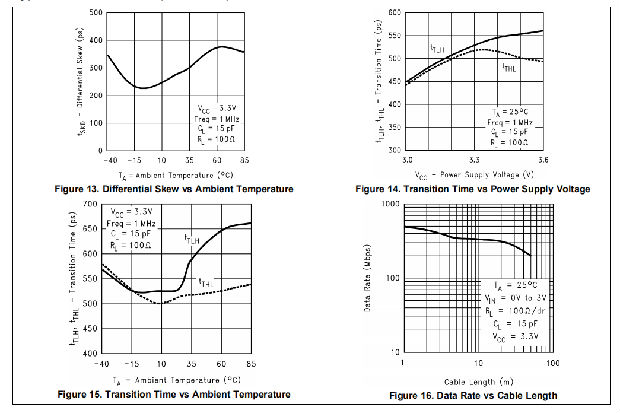

•>400 Mbps(200 MHz)交换速率

•穿线引线简化PCB布局

•300 ps典型差分偏差

•400 ps最大差分偏差

•1.7ns最大传播延迟

•3.3V电源设计

•±350 mV差分信号

•低功耗(静态3.3伏时为13兆瓦)

•可与现有5-V LVDS接收器进行互操作

•断电时LVDS输出的高阻抗

•符合TIA/EIA-644 LVDS标准

•工业工作温度范围(−40°C至+85°C)

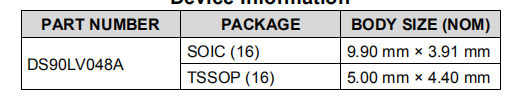

•表面贴装SOIC和薄型TSSOP封装

应用

•多功能打印机

•LVDS–LVCMOS翻译

说明

DS90LV047A器件是一种四芯CMOS流过差分线路驱动器,专为要求超低功耗和高数据速率的应用而设计。该设备采用低压差分信号(LVDS)技术,可支持超过400 Mbps(200 MHz)的数据速率。

DS90LV047A接受低电压TTL/CMOS输入电平,并将其转换为低压(350毫伏)差分输出信号。此外,驱动器支持三态功能,该功能可用于禁用输出级、禁用负载电流,从而将设备降至典型的13兆瓦的超低闲置功率状态。DS90LV047A有一个流通引脚,便于PCB布局。

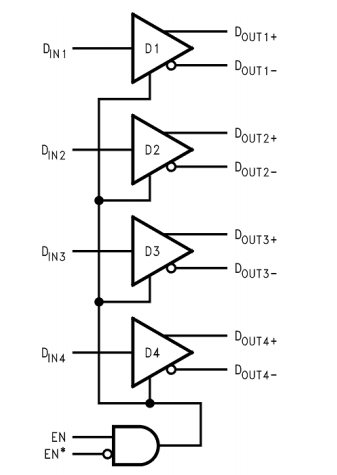

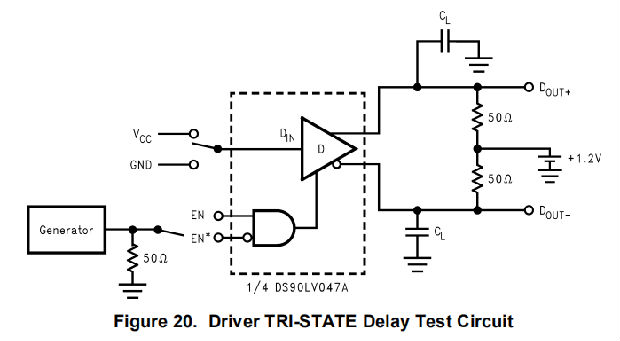

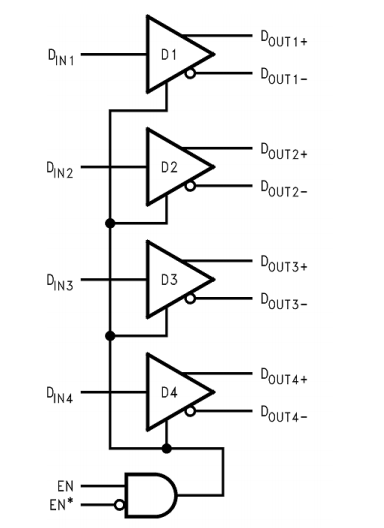

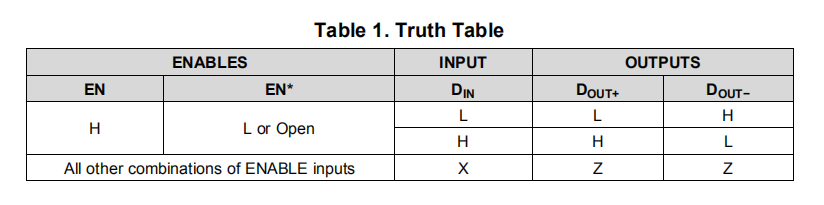

EN和EN*输入被“与”组合在一起并控制三态输出。启用对所有四个驱动程序都是通用的。DS90LV047A和伴生线路接收器(DS90LV048A)为高速点对点接口应用提供了大功率psuedo ECL设备的新替代方案。

设备信息

(1)、有关所有可用的软件包,请参阅数据表末尾的订购附录。

功能图

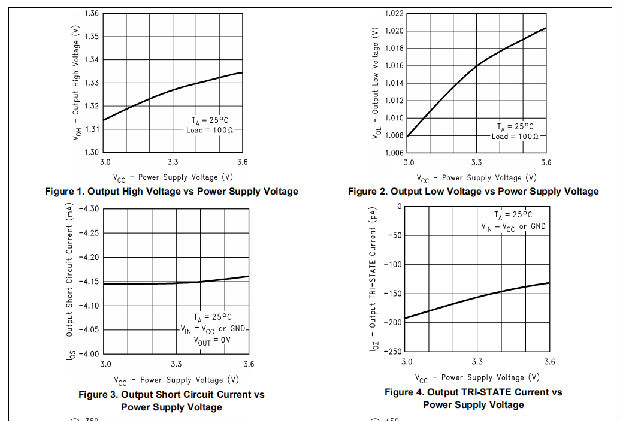

典型特征

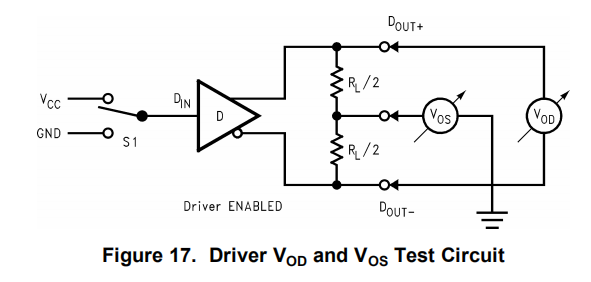

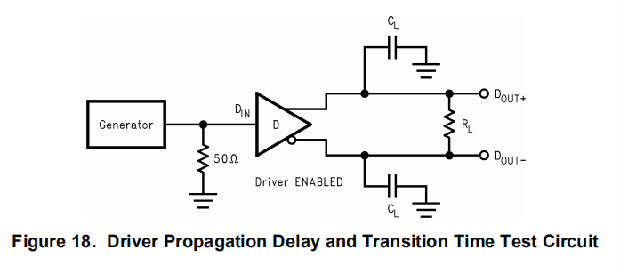

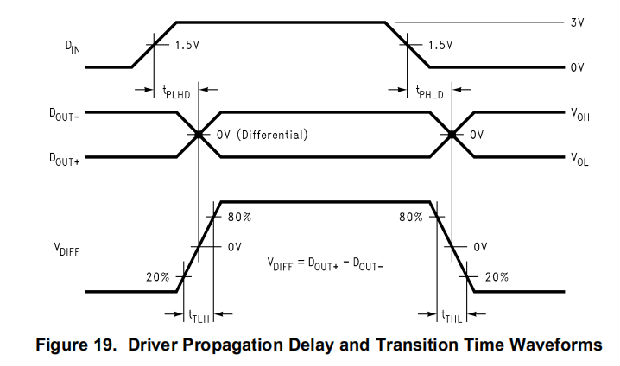

参数测量信息

详细说明

概述

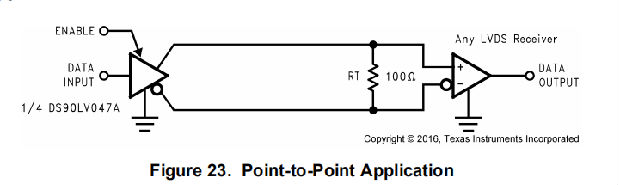

LVDS驱动程序和接收器主要用于简单的点对点配置,如图23所示。这种配置为驱动器的快速边缘速率提供了一个干净的信令环境。接收器通过一个平衡的介质连接到驱动程序,该介质可以是标准的双绞线电缆、平行对电缆或简单的PCB迹线。通常,介质的特性微分阻抗在100Ω的范围内。终端电阻为100Ω(选择与介质匹配),并尽可能靠近接收器输入引脚。终端电阻器将驱动器输出电流(电流模式)转换为接收器检测到的电压。其他配置是可能的,例如多接收器配置,但必须考虑中流连接器、电缆头和其他阻抗不连续性以及地面移动、噪声容限值和总终端负载的影响。

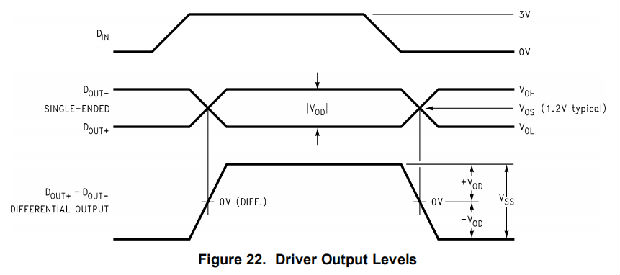

DS90LV047A差分线路驱动器是一种平衡电流源设计。一般来说,电流模式驱动器具有高输出阻抗并为一系列负载提供恒定电流(另一方面,电压模式驱动器为一系列负载提供恒定电压)。电流通过负载在一个方向切换以产生逻辑状态,在另一个方向切换以产生另一个逻辑状态。输出电流通常为3.1毫安,最小为2.5毫安,最大为4.5毫安。电流模式驱动器要求(如上所述)使用电阻终端来终止信号并完成回路,如图23所示。不允许使用交流或未端接的配置。3.1毫安回路电流在100Ω终端电阻上形成310毫伏的差分电压,接收器检测到的差动噪声裕度最小为250毫伏(驱动信号减去接收器阈值(250毫伏–100毫伏=150毫伏)。如图22所示,信号中心位于+1.2V(驱动器偏移,VOS)附近。

注意:稳态电压(VSS)峰间摆幅是差分电压(VOD)的两倍,通常为620 mV。

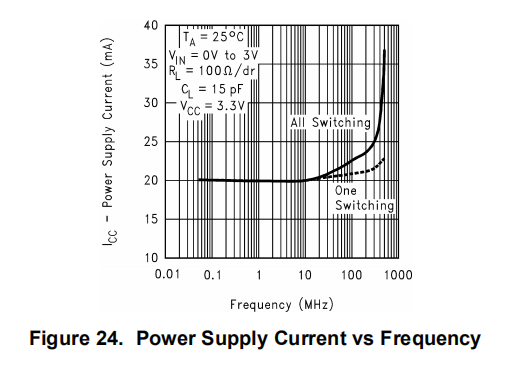

电流模式驱动器比电压模式驱动器(如RS-422驱动器)提供了实质性的好处。它的静态电流相对于开关频率保持相对平稳。而RS-422电压模式驱动器在大多数情况下从20兆赫到50兆赫呈指数增长。这是由于当内部门切换时,在设备的轨道之间流动的重叠电流造成的。而电流模式驱动器在其输出之间切换一个固定的电流,而没有任何实质性的重叠电流。这类似于一些ECL和PECL器件,但没有ECL/PECL设计的重静态ICC要求。小于80%的LVDS所需电流小于PECL。该驱动器的交流规格比其他现有的RS-422驱动器提高了10倍。

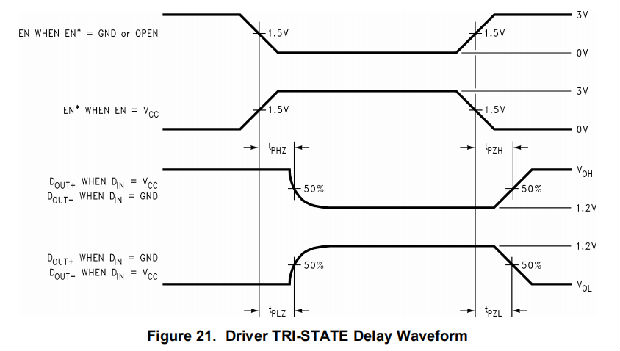

三态功能允许禁用驱动器输出,从而在不需要传输数据时获得更低的功率状态。

功能框图

功能描述

LVDS故障保护

本节讨论LVDS互连的故障安全偏置的常见问题,特别是DS90LV047A驱动器输出和DS90LV048A接收器输入。

LVDS接收机是一种高增益、高速器件,它将一个小的差分信号(20mv)放大到CMOS逻辑电平。由于接收机的高增益和严格的阈值,请注意防止噪声作为有效信号出现。

接收器的内部故障安全电路设计用于产生或吸收少量电流,为浮动、端接或短路的接收器输入提供故障保护(高输出电压的稳定已知状态)。

1.打开输入引脚:DS90LV048A是四路接收机设备,如果应用程序只需要1个、2个或3个接收机,则未使用的信道输入必须保持打开状态。不要将未使用的接收器输入连接到接地或任何其他电压。输入由内部高值上拉和下拉电阻偏置,以将输出设置为高状态。这种内部电路确保了开放输入的高、稳定的输出状态。

2.终止输入:或者在LV907A电源断开的情况下,如果一个DS907A电缆处于断开状态,或者在LV907A驱动器处于断开状态的情况下,或者在LV907A电源断开的情况下-Ω输入端接电阻器。拔掉电缆会成为漂浮的天线。如果电缆接收到超过10毫伏的差分噪声,接收器可能会将该噪声视为有效信号并切换。为了确保任何噪声被视为共模而不是差分,必须使用平衡互连。双绞线电缆比扁平带状电缆具有更好的平衡性。

3.输入短路:如果发生使接收器输入短路的故障,从而导致0-V差分输入电压,接收器输出将保持在高状态。在设备的共模范围内(GND至2.4 V),不支持短路输入故障保护。它只在输入短路且不施加外部共模电压的情况下受支持。

外部低值上拉电阻和下拉电阻(用于更强的偏置)可用于在存在更高噪声水平的情况下提高故障安全性。上拉电阻和下拉电阻应在5-kΩ到15-kΩ的范围内,以最大限度地减小驱动器的负载和波形失真。共模偏置点应设置为约1.2 V(小于1.75 V),以与内部电路兼容。

设备功能模式

表1列出了DS90LV047A的功能模式。

应用与实施

注意

以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

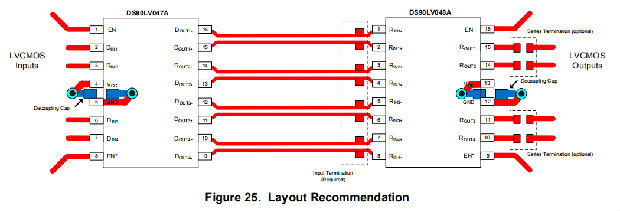

DS90LV047A有一个流通引脚,允许简单的PCB布局。该装置一侧的LVDS信号可以很容易地匹配驱动器和接收器之间的差分对迹线的电气长度,并且允许这些迹线靠近以耦合噪声作为共模。噪声隔离是通过LVDS信号在设备一侧和TTL信号在另一侧实现的。

典型应用

设计要求

使用LVDS设备时,务必记住指定受控阻抗PCB轨迹、电缆组件和连接器。传输介质的所有组件应具有约100Ω的匹配差分阻抗。它们不应引入主要的阻抗不连续性。

平衡电缆(例如,双绞线)通常比不平衡电缆(带状电缆)更好地减少噪音和信号质量。由于场对消效应,平衡电缆往往产生较少的电磁干扰,并且容易拾取电磁辐射作为共模(而不是差模)噪声,该噪声被LVDS接收器拒绝。

对于小于0.5 M的电缆距离,大多数电缆可以有效地工作。对于0.5 M≤d≤10 M的距离,CAT5(5类)双绞线电缆工作良好,容易获得,价格相对便宜。

详细设计程序

探测LVDS传输线

始终使用高阻抗(>100kΩ)、低电容(<2pf)示波器探头,范围宽(1GHz)。不恰当的探测会产生欺骗的结果。

数据速率与电缆长度曲线测试程序

将29−1位的伪随机位序列(PRBS)编程到函数生成器(Tektronix)中HFS9009),并通过50Ω电缆和SMB连接器连接到驱动器输入端。使用示波器(Tektronix 11801B)来探测结果眼图,在接收器的输入端进行差分测量。一个100Ω的电阻被用来在电缆的远端端接这对线。在电缆的远端,在接收器的输入端进行测量,并用于该图的抖动分析(图16)。输入信号的频率增加,直到被测特定电缆长度的测量抖动(ttcs)等于单位间隔(ttui)的20%。从许多系统设计开始,20%的抖动是一个合理的起点。使用的数据是NRZ。在差分眼图的0-V差分电压下测量抖动。可以使用新的DS90LV047-048AEVM评估DS90LV047A和DS90LV048A。

图24显示了非常好的典型性能,可作为数据速率与电缆长度的设计指南。增加抖动百分比会分别增加曲线,使设备在较长的电缆长度上传输更快。这放宽了系统的抖动容忍度,允许更多的抖动进入系统,这可能会降低系统的可靠性和效率。或者,降低抖动百分比对系统有相反的效果。根据上述信号质量标准,曲线下的区域被视为安全操作区域。有关眼图测试的更多信息,请参阅AN-808long传输线和数据信号质量(SNLA028)。

应用曲线

电源建议

尽管DS90LV047A在静止状态下消耗的功率非常小。在较高的开关频率下,存在一个动态电流分量,它会增加整体功耗。DS90LV047A电源连接必须将此额外的电流消耗考虑到最大功率要求。

布局

布局指南

•至少使用4个PCB层(从上到下);LVDS信号、接地、电源、TTL信号。

•将TTL信号与LVDS信号隔离,否则TTL可能耦合到LVDS线路上。最好将TTL和LVDS信号放在不同的层上,这些层由电源/地平面隔离。

•使驱动器和接收器尽可能靠近(LVDS端口侧)连接器。

电源去耦建议

旁路电容器必须用在电源引脚上。在电源引脚处并联使用高频陶瓷(建议采用表面贴装)0.1-μF和0.001-μF电容器,最小值电容器最靠近设备电源引脚。印刷电路板上附加的分散电容器提高了去耦能力。必须使用多个通孔将去耦电容器连接到电源平面。必须在印刷电路板电源和接地之间的电源入口点连接10-μF(35-V)或更大的固体钽电容器。

微分记录道

使用与传输介质(即电缆)和终端电阻的差分阻抗匹配的受控阻抗轨迹。一旦差分对迹线离开IC,应尽可能靠近它们(短截线长度必须小于10 mm)。这有助于消除反射并确保噪声作为共模耦合。事实上,我们已经看到,相距1毫米的差分信号比相距3毫米的记录道辐射的噪声要小得多,因为磁场对消在距离较近的记录道上要好得多。此外,在差分线路上产生的噪声更有可能表现为被接收器拒绝的共模。

匹配迹线之间的电气长度以减少偏差。一对信号之间的偏差意味着信号之间的相位差,这会破坏差分信号和EMI的磁场抵消优势。

注意:传播速度,v=c/Er,其中c(光速)=0.2997mm/ps或0.0118英寸/秒。

对于差分记录道,不要仅仅依赖自动布线功能。仔细检查尺寸以匹配差分阻抗,并为差动线路提供隔离。尽量减少线路上的过孔和其他不连续性。

避免90°转弯(这会导致阻抗不连续)。使用圆弧或45°斜面。

在一对记录道内,两个记录道之间的距离必须最小化,以保持接收器的共模抑制。在印刷电路板上,这个距离必须保持恒定,以避免微分阻抗的不连续性。允许在连接点处出现轻微违规。

终止

使用与差分阻抗或传输线最匹配的终端电阻。电阻器必须在90Ω和130Ω之间。记住,电流模式输出需要终端电阻来产生差分电压。LVDS在没有电阻端接的情况下不工作。通常情况下,在接收器端连接一个电阻就足够了。

表面贴装1%到2%的电阻是最好的。PCB存根、元件引线以及从终端到接收器输入的距离必须最小化。终端电阻器和接收器之间的距离应小于10 mm(最大12 mm)。

布局示例