L9822E点击型号即可查看芯片规格书

八个低RDSon数据输出

(25°C时IO=1A时为0.5Ω,VCC=5V±5%)

8位串行输入数据(SPI)

8位串行诊断输出

过载和开路条件

输出短路保护

CHIPENABLESELECTFUNCTION(低电平有效)

每个输出的内部36V夹紧

与另一个八进制级联

.低静态电流(最大10mA)

.MULTIWATT15、PowerSO20和SO20L

说明

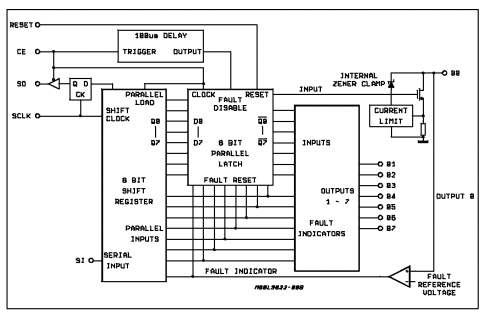

L9822E是一个八进制低压侧电磁阀驱动器重点研究了多功率BCD技术适用于澳大利亚的行车灯、继电器和电磁阀移动环境。DMOS超过了L9822E具有非常低的功耗。数据通过串行方式传输到设备串行外围接口(SPI)协议。L9822具有输出状态监视功能功能。

管脚说明

VCC公司

逻辑电源电压-标称5V

接地

设备地面。这个逻辑电路和功率输出级的接地装置。

重置

异步复位L9822ESP内部的输出级、并行锁存器和移位寄存器。

此引脚处于低激活状态,不能保持浮动状态。通电清除功能可以通过一个外部电阻器将该引脚连接到VCC用外部电容器接地。

总工程师

芯片启用。数据从移位寄存器传输到信号上升沿的输出端。该信号的下降沿设置移位寄存器输出电压检测位来自输出级。SO引脚的输出驱动器是此引脚低时启用。所以串行输出。此引脚是移位寄存器,当CE高时,它是三态的。A此管脚上的数据位为高表示特殊输出为高。该引脚上的数据位低表示输出低。将串行输出位与前一位进行比较串行输入位外部微控制器执行L9822提供的诊断数据。硅串行输入。该引脚是串行数据输入。高潮在此Pin上,将编程一个ParticularRoutPuttoBeoff,开一会儿就可以了。

SCLK

串行时钟。该引脚为移位寄存器计时。新的所以数据会出现在这个引脚的每一个上升沿上新的数据将被锁存到每一个slk's fal ling edge到移位寄存器中。输出00-07电源输出引脚输入和输出位与07位相对应,首先通过SPI接收公共汽车和00是最后。输出端提供限流和电压传感器故障功能指示和保护。额定负载电流这些输出为500mA,但电流限制设置为最小值1.05A。输出也有车载夹具设置为约36V用于再循环感应负载电流。

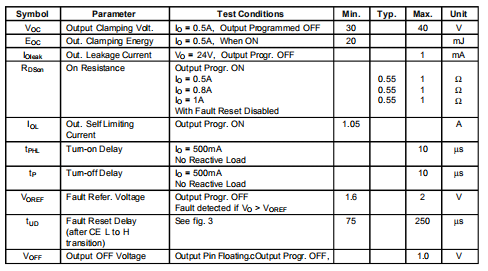

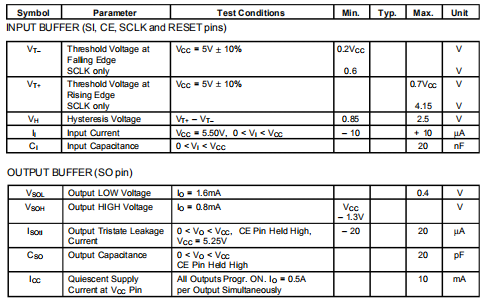

电气特性(VCC=5V±5%。Tj=–40至125°C;除非另有规定)

电气特性(续)

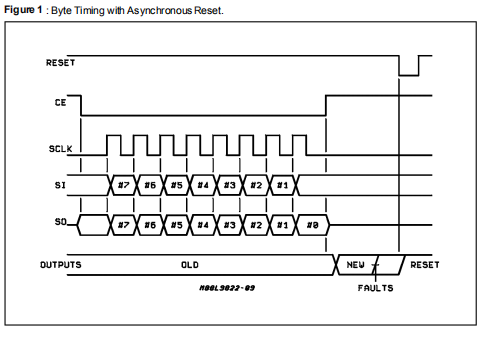

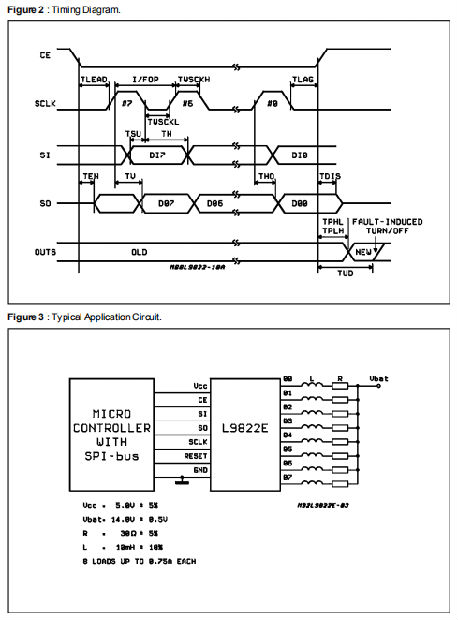

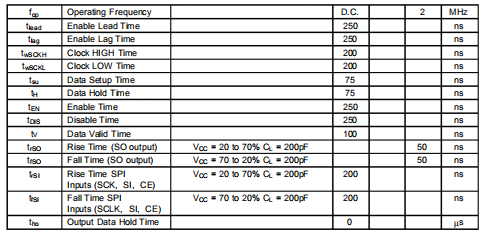

串行外围接口(见图2,时序图)

功能描述

L9822ESPDMOS输出一个低操作po werdevicefeatu环,八个1ΩRDSON dmos驱动器输出级有瞬态保护电路。每个信道由输出锁存器和公共复位线独立控制所有八个输出。驱动器的饱和度低短路保护和直流电以及电磁阀、灯和继电器等电阻负载。数据通过这些串行接口(SPI)传输到设备协议。那个电路通过串行输入接收8位串行数据(SI)存储在内部寄存器中以控制输出驱动程序。串行输出(SO)提供8表示电压水平的诊断数据位在驱动器输出端。这使得微处理器诊断输出驱动器的状况。输出饱和电压由不饱和状态的比较器能够通过断层打开特定河流重置线路。该电路还可与其他八进制驱动器级联,以阻塞8位多个数据。芯片启用(CE)时选择设备线路低。另外,(SO)被置于三态模式取消选择设备时。负边缘(CE)传输驱动器的电压电平对移动寄存器和(CE)的积极影响将来自换档寄存器的新数据锁存到两个驱动器上。当CE低时,数据位包含在移位寄存器每数据位存在于SI时的SCLK正跃迁输入被锁存到移位寄存器负迁移。

内部块说明

设备的内部架构基于三个内部主块:用于与SPI总线对话的八进制移位寄存器、写入设备的控制位的八进制锁和八进制加载驱动程序数组。移位寄存器移位寄存器有串行和并行输入以及串行和并行输出。串行输入ac接收来自SPIBUS的数据,串行输出同时将数据发送到SPI总线。这个平行输出锁紧在adata的L9822ESPattheend侧的平行板上转移。那个在数据传输周期开始时,并行输入卡阻诊断数据到换档寄存器。

平行闩锁

并行锁存器保存来自移位的输入数据注册。然后这些数据驱动输出级。锁存器中的单个寄存器可以通过以保护过载的故障条件输出阶段。整个锁闩也被清除了通过复位信号。

输出级

输出级提供主动低驱动信号适用于0.75A连续负载。每个输出有一个电流限制电路输出电流至少为1.05A,以允许高in 急流。另外,输出内部齐纳值设置为36伏以钳制感应瞬变在关闭时。每个输出也有一个电压比较表输出节点。如果on输出引脚上的电压超过1.8V,则故障为假设和锁闩驱动这个特定的阶段复位,关闭输出以保护它。此操作的说明如下。这些组件还提供诊断反馈数据给转变注册。另外,比较器为台南内部下拉电流如果输出为程序关闭,输出引脚开路。定时数据传输图2显示了使用SPI总线。

CE高-低过渡

当芯片启用(CE)引脚为拉低。Thetri-stateSerialOutput(SO)引脚驱动程序将使CE较低的时间成为可能。在CE引脚的边缘,诊断数据来自输出级中的电压比较器将接入移位寄存器。如果特定输出是高,一个逻辑信号会被塞进移位寄存器。如果输出低,逻辑零将在这里装的最重要的位(07)应该是显示串行输入(SI)引脚。一个零引脚将编程一个输出,而一个将编程输出关闭。

SCLK跃迁

然后应拔出串行时钟(SCLK)引脚高。在这一点上,来自最重要输出(07)的诊断位将出现在最高点这里表示07针脚高于1.8V。然后将SCLK引脚调低至高。新的SO数据将出现在每个边缘之后的SCLK和新的SI数据将被锁存到L9822ESPhift寄存器坠落边缘。Anun有限数量的数据可以通过设备移位寄存器(输入SI引脚,输出SOpin),允许其他spi设备级联在一个菊花链与L9822ESP。

CE低到高转变

一旦最后一个数据位移到L9822ESP,CE销应拉高。在CE的上升沿,移位寄存器数据是横向的,输出级将由新数据驱动。内部160μs延迟定时器也将在该上升沿启动(参见图德)。在160μs期间,输出将为仅由模拟限流电路保护由于故障导致平行锁存复位条件它持续了一段时间。这个降低部件,以克服高涌流打开后可能立即流动。一旦延迟时间已过,输出电压为通过比较器和任何体积大于1.8的输出进行感应瓦雷拉切多夫,应该是注意,SCLK引脚在CE引脚的两个传输位置都应较低,以避免换档注册.thescrk输入由计算机控制使SCLK引脚在CE引脚高。

故障条件检查

可以用以下方法检查故障情况。输入新的控制字节。等等160微秒左右,以使输出稳定下来。在同一个控制器上计时,并观察设备输出的诊断数据。诊断位应与第一次打卡。任何不同之处都会指向错误打开输出。如果输出由计时为0,1作为输出的直径,输出pin仍然很高并且存在短路或过载情况。如果输入1时,输出被编程关闭,一个零作为诊断的依据回来了输出,没有把输出引脚拉高