DS90CF386点击型号即可查看芯片规格书

DS90CF366点击型号即可查看芯片规格书

特点

•支持20 MHz至85 MHz移位时钟

•85 MHz灰度下的Rx功耗<142 mW(典型值)

•Rx断电模式<1.44 mW(最大)•ESD额定值>7 kV(HBM),>700 V(EIAJ)

•支持VGA、SVGA、XGA和单像素SXGA

•PLL不需要外部组件

•兼容TIA/EIA-644 LVDS标准

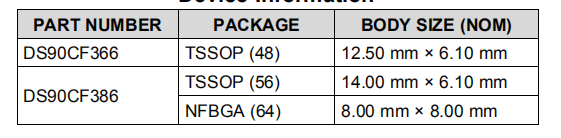

•轻薄的56针或48针TSSOP封装

•DS90CF386还提供64针0.8毫米细间距球栅阵列(NFBGA)封装

应用

•视频显示器

•打印机和图像

•数字视频传输

•机器视觉

•打开本地设计院至RGB桥

说明

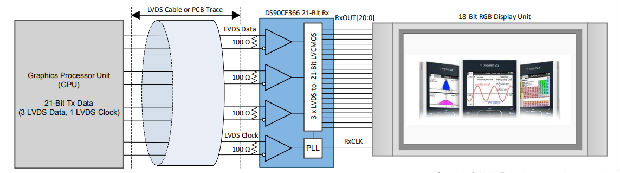

DS90CF386接收器将四个LVDS(低压差分信号)数据流转换回并行的28位LVCMOS数据。DS90CF366接收器也可用,它将三个LVDS数据流转换回并行的21位LVCMOS数据。两个接收机的输出在下降沿上选通。上升沿或下降沿选通发射机将与下降沿选通接收机互操作,无需任何转换逻辑。

接收机LVDS时钟以20兆赫至85兆赫的速率工作。设备相位锁定到输入的LVDS时钟,在LVDS数据线上采样串行位流,并将其转换为并行输出数据。在85 MHz的输入时钟速率下,每条LVDS输入线以595 Mbps的比特率运行,因此DS90CF386的最大吞吐量为2.38 Gbps,DS90CF366的最大吞吐量为1.785 Gbps。

使用这些串行链路设备是解决EMI和电缆尺寸问题的理想选择,这些问题与通过宽、高速并行传输数据相关LVCMOS接口。两种设备均采用TSSOP包装。DS90CF386还提供64针0.8毫米细间距球栅阵列(NFBGA)封装,与56针TSSOP封装相比,该封装可减少44%的PCB占地面积。

设备信息

(1)、有关所有可用的软件包,请参阅数据表末尾的订购附录。

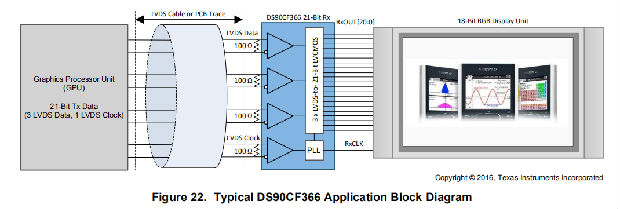

典型应用程序框图(DS90CF366)

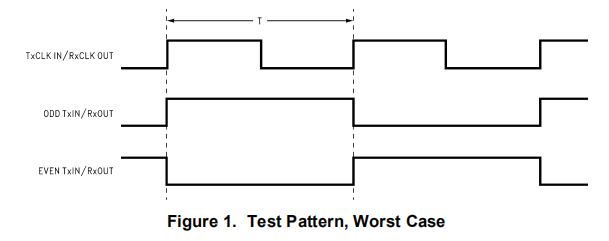

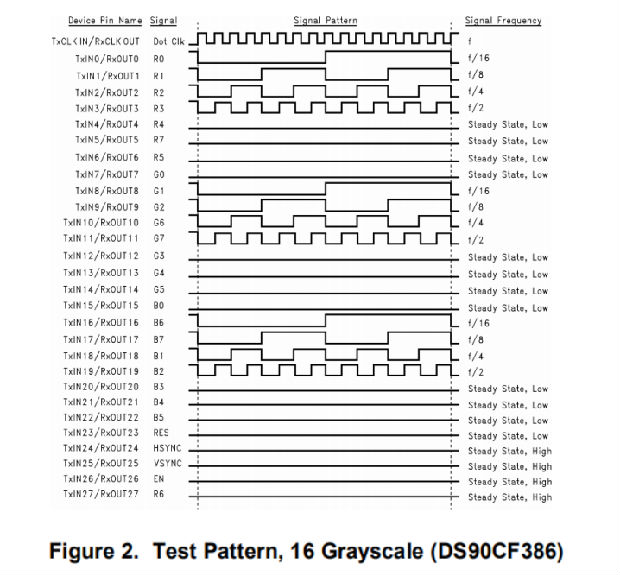

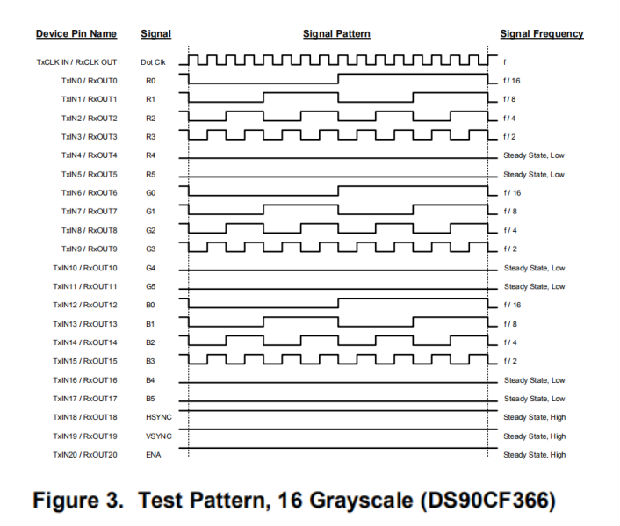

时序图

(1)、最坏情况下的测试模式会产生数字电路、LVDS I/O和CMOS或LVCMOS I/O的最大切换。

(2)、16灰度测试模式测试典型LCD显示模式的设备功耗。测试模式近似于在显示器上产生一组16条垂直条纹所需的信号切换。

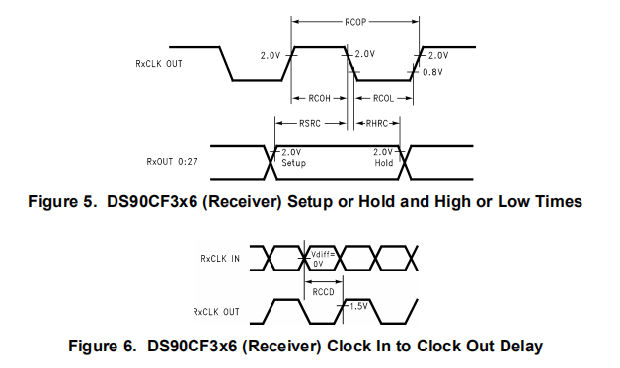

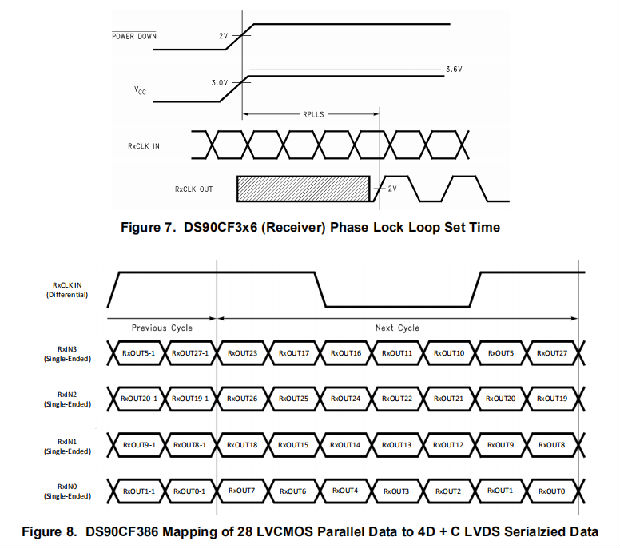

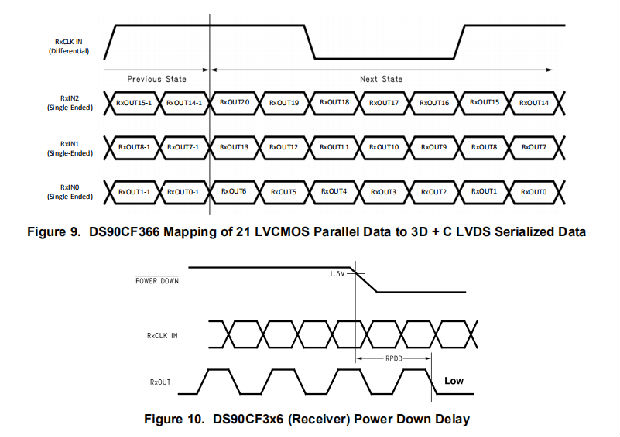

(3)、图1和图3显示了下降沿数据选通(TxCLK IN/RxCLK OUT)。

(4)、推荐的针到信号映射。客户可以选择不同的定义。

(1)、最坏情况下的测试模式会产生数字电路、LVDS I/O和CMOS或LVCMOS I/O的最大切换。

(2)、16灰度测试模式测试典型LCD显示模式的设备功耗。测试模式近似于在显示器上产生一组16条垂直条纹所需的信号切换。

(3)、图1和图3显示了下降沿数据选通(TxCLK IN/RxCLK OUT)。

(4)、推荐的针到信号映射。客户可以选择不同的定义。

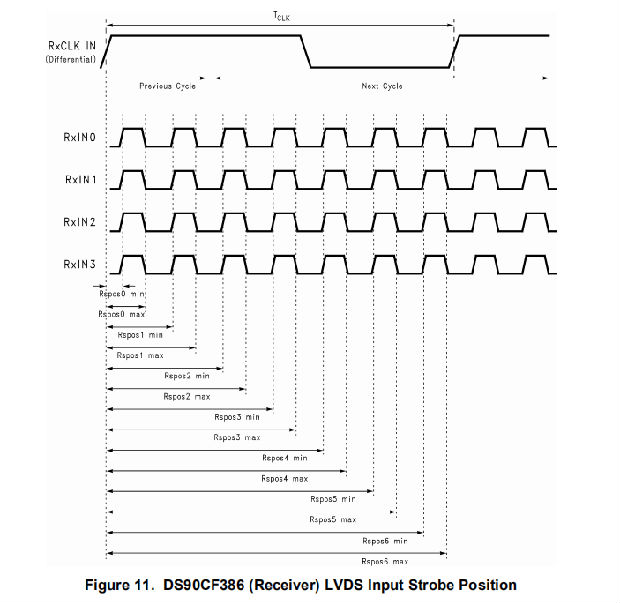

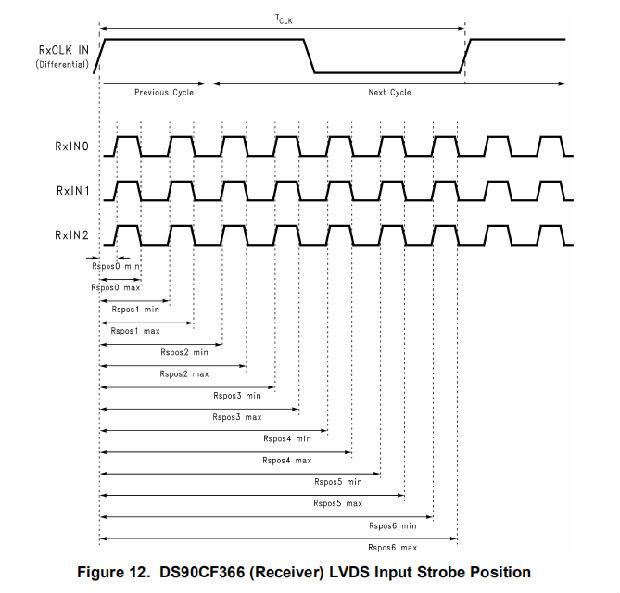

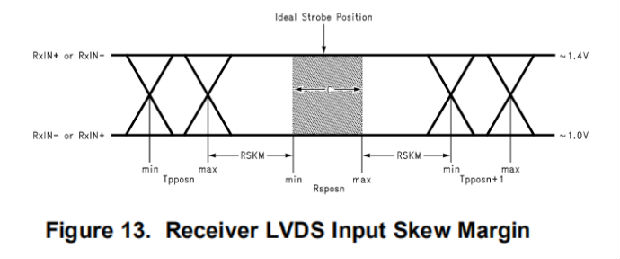

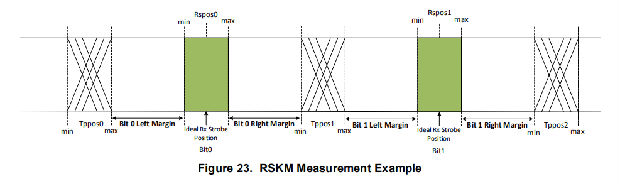

C: 设置和保持时间(内部数据采样窗口)由Rspos(接收器输入选通位置)最小值和最大值定义

Tppos:变送器输出脉冲位置(最小和最大)

电缆歪斜:通常每英尺10 ps–40 ps,取决于介质

RSKM=电缆倾斜(类型、长度)+源时钟抖动(周期到周期)(1)+ISI(符号间干扰)(2)

(1)、周期到周期抖动取决于发送源。时钟抖动应保持在85MHz时小于250ps。

(2)、 ISI取决于互连长度;可能为零。

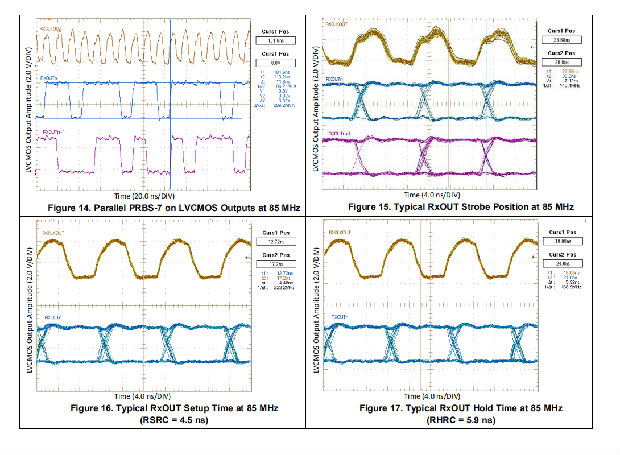

典型特征

详细说明

概述

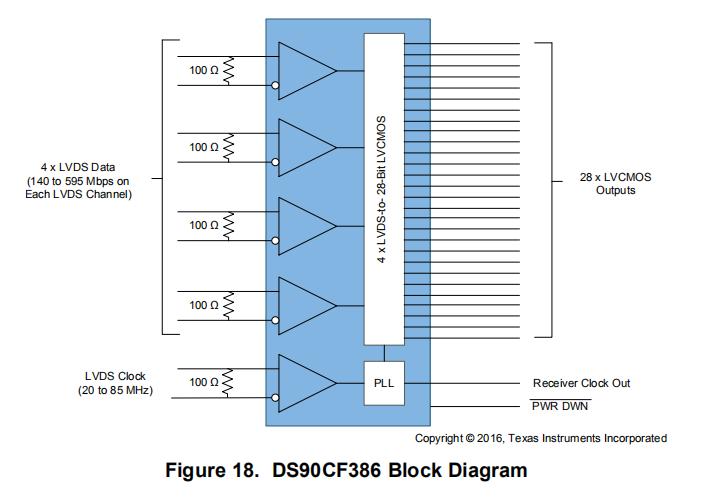

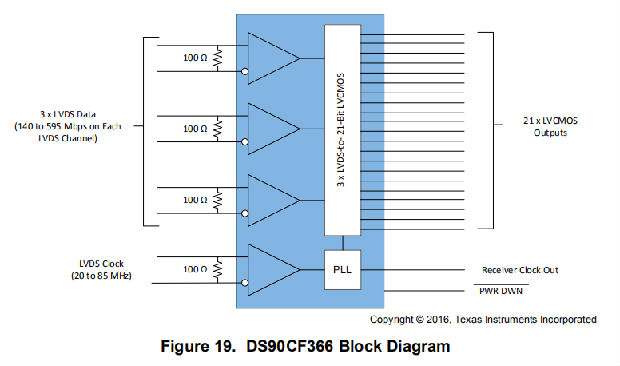

DS90CF386是一个接收器,它将四个LVDS(低压差分信号)数据流转换为并行的28位LVCMOS数据(RGB的24位和HSYNC、VSYNC、DE和CNTL的4位)。这个DS90CF366是一个接收器,它将三个LVDS数据流转换为并行的21位LVCMOS数据(18位RGB和3位HSYNC、VSYNC和DE)。一个内部锁相环锁定到输入的LVDS时钟范围从20到85兆赫。锁定的锁相环确保了稳定的时钟,以便在接收机时钟输出下降沿上对输出的LVCMOS数据进行采样。这些设备具有一个PWR DWN引脚,当没有活动的输入数据时,将设备置于低功耗模式。

功能框图

特性描述

DS90CF386和DS90CF366由几个关键块组成:

•LVDS接收器

•锁相环(PLL)

•串行LVDS到并行LVCMOS转换器

•LVCMOS驱动器

LVDS接收器

DS90CF386有五个差动LVDS输入,DS90CF366有四个差动LVDS输入。对于DS90CF386,四个LVDS输入包含来自28位源发送器的序列化数据。

对于DS90CF366,三个LVDS输入包含来自21位源发送器的序列化数据。剩余的LVDS输入包含与数据对相关联的LVDS时钟。

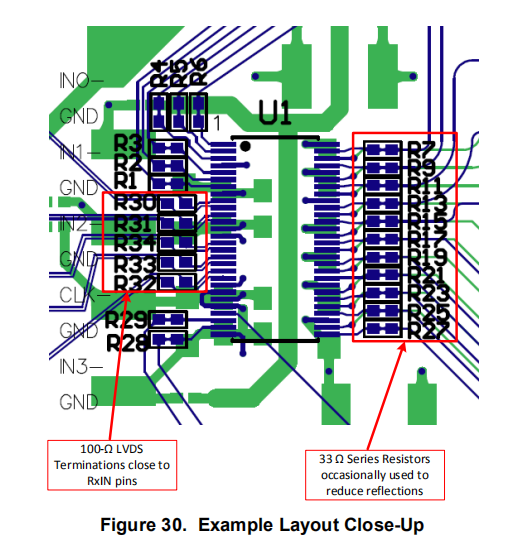

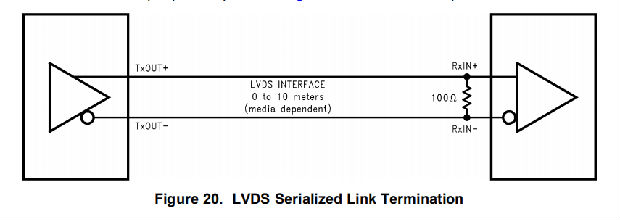

LVDS输入端接

DS90CF386和DS90CF366要求在接收器输入的每个差分对上的真线路和补码线路上安装一个100Ω终端电阻器。为了防止由于短线引起的反射,该电阻应尽可能靠近设备输入引脚。图20显示了一个示例。

锁相环(PLL)

FPD Link I设备使用内部PLL来恢复通过LVDS接口传输的时钟。然后将恢复的时钟用作参考,以确定每个时钟周期接收的七个串行位的采样位置。序列化LVDS数据流中每个位的宽度是时钟周期的七分之一。差分偏差(一个差分对内的Δt)、互连偏差(一个差分对与另一个差分对的Δt)和时钟抖动都将减少LVDS串行数据流采样的可用窗口。每个VCC对地的单独旁路将最小化传递到PLL的噪声,从而创建一个低抖动LVDS时钟,以改善总体抖动预算。

串行LVDS到并行LVCMOS转换器

在锁相环锁定到输入的LVDS时钟后,接收器将每个LVDS差分数据对反序列化为每个时钟周期的七个并行LVCMOS数据输出。对于DS90CF386,LVDS数据输入映射到LVCMOS输出,如图8所示。对于DS90CF366,根据图9,LVDS数据输入映射到LVCMOS输出。

LVCMOS驱动器

来自DS90CF386和DS90CF366的LVCMOS输出是来自串行LVDS差分数据对的反序列化并行单端数据。每个LVCMOS输出由PLL和RxCLKOUT下降沿上的频闪进行时钟控制。所有未使用的DS90CF386和DS90CF366 RxOUT输出可以保持浮动。

设备功能模式

电源顺序和断电模式

这个DS90CF386和DS90CF366可通过断言PWR DWN引脚(低电平有效)随时进入断电模式。DS90CF386和DS90CF366还设计用于防止发射机或接收机意外断电。如果发射板断电,接收器时钟(输入和输出)停止。数据输出(RxOUT)保持时钟停止时的状态。当接收器板断电时,接收器输入由故障保护偏置电路控制。在初始通电和断电条件下,LVDS输入为高Z。每个输入电流被限制在5毫安,这样就避免了给设备供电时发生闩锁的可能性。

应用与实施

注意

以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

DS90F386和DS90CF366是为多种数据传输应用而设计的。在这些应用中使用串行LVDS数据线允许在窄的总线宽度上进行有效的信号传输,从而降低成本、功率和空间。

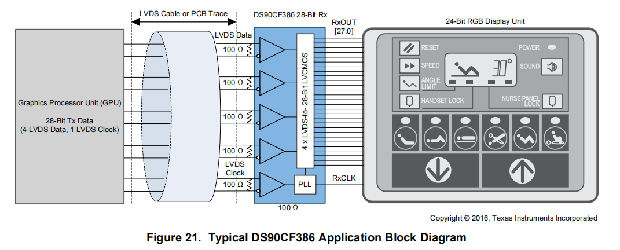

典型应用

图21和图22显示了DS90CF386和DS90CF366作为OpenLDI到RGB桥接器的典型应用。

设计要求

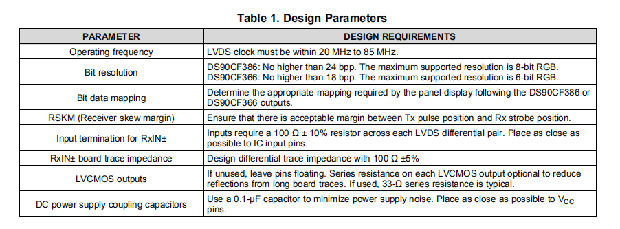

对于这个设计示例,请遵循表1中的要求。

详细设计程序

要使用DS90CF386或DS90CF366进行设计,请确定以下各项:

•电缆接口

•位分辨率和工作频率

•从接收器到端点面板显示的位映射

•RSKM与发射机脉冲位置余量的互操作性

电缆

发射机和接收机之间的电缆接口需要支持差分LVDS对。DS90CF366需要四对信号线,DS90CF386需要五对信号线。理想的电缆接口在整个路径上具有恒定的100Ω差分阻抗。还建议电缆歪斜保持在120ps以下(假设85mhz时钟速率),以便在接收机处保持足够的数据采样窗口。

根据应用和数据速率的不同,Tx和Rx之间的互连介质可能有所不同。例如,对于较低的数据速率(时钟速率)和较短的电缆长度(<2m),介质的电气性能就不那么重要。对于高速或远距离应用,介质的性能变得更加重要。某些电缆结构提供更紧密的斜交(导线和线对之间的电长度匹配)。例如,双同轴电缆的距离长达5米,最大数据传输速率为2.38 Gbps(DS90CF366)和1.785 Gbps(DS90CF386)。

位分辨率和工作频率兼容性

端点面板显示器的位分辨率显示DS90CF386或DS90CF366中是否有足够的可用位来输出每像素所需的数据。DS90CF386有28个并行LVCMOS输出,因此可以提供高达24 bpp(位/像素)的位分辨率。在每个时钟周期中,剩余的位是三个控制信号(HSync、VSync、DE)和一个备用位。DS90CF366有21个并行LVCMOS输出,因此可以提供高达18 bpp(位/像素)的位分辨率。在每个时钟周期中,剩余的位是三个控制信号(HSync、VSync、DE)。

每帧的像素数和端点面板显示的刷新率指示反序列化器时钟所需的工作频率。要确定所需的时钟频率,请参考方程式1。

f_Clk = [H_Active + H_Blank] × [V_Active + V_Blank] × f_Vertical

其中

•H_Active=活动显示水平线

•H_Blank=消隐周期水平线

•V_Active=活动显示垂直线

•V_Blank=消隐周期垂直线

•f_Vertical=刷新率(Hz)

•f_Clk=LVDS时钟的工作频率

在每一帧中,都有一个与未在面板上主动显示的水平行和垂直列相关联的消隐周期。必须包括这些消隐周期像素以确定所需的时钟频率。考虑以下示例来确定所需的LVDS时钟频率:

• H_Active = 640

• H_Blank = 40

• V_Active = 480

• V_Blank = 41

• f_Vertical = 59.95 Hz

因此,用方程式2确定所需的工作频率。

[640 + 40] × [480 + 41] × 59.95 = 21239086 Hz ≈ 21.24 MHz

由于DS90CF386和DS90CF366中PLL的工作频率在20到85 MHz之间,因此DS90CF386和DS90CF366可以支持具有上述要求的面板显示。

如果特定消隐间隔未知,则消隐间隔中的像素数可以近似为活动像素的20%。方程式3可用作工作LVDS时钟频率的保守近似值:f_Clk ≈ H_Active × V_Active × f_Vertical × 1.2

使用此近似值,本节中示例的工作频率用方程式4估算。

640 × 480 × 59.95 × 1.2 = 22099968 Hz ≈ 22.10 MHz

接收器和端点面板显示器之间的数据映射

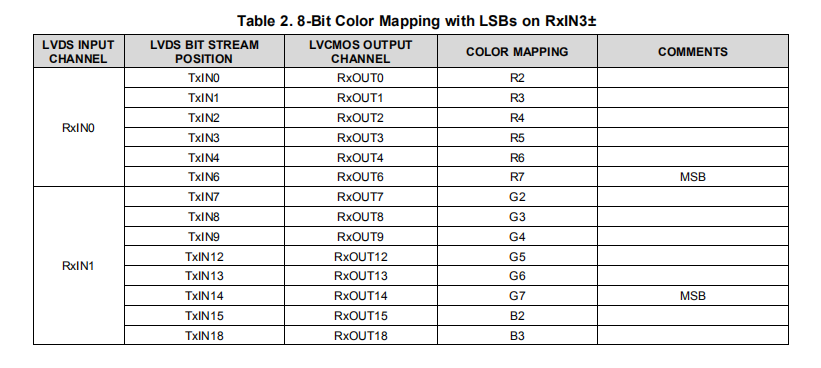

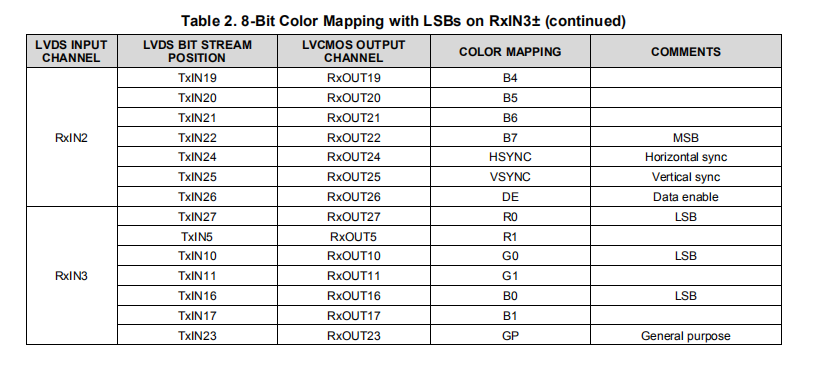

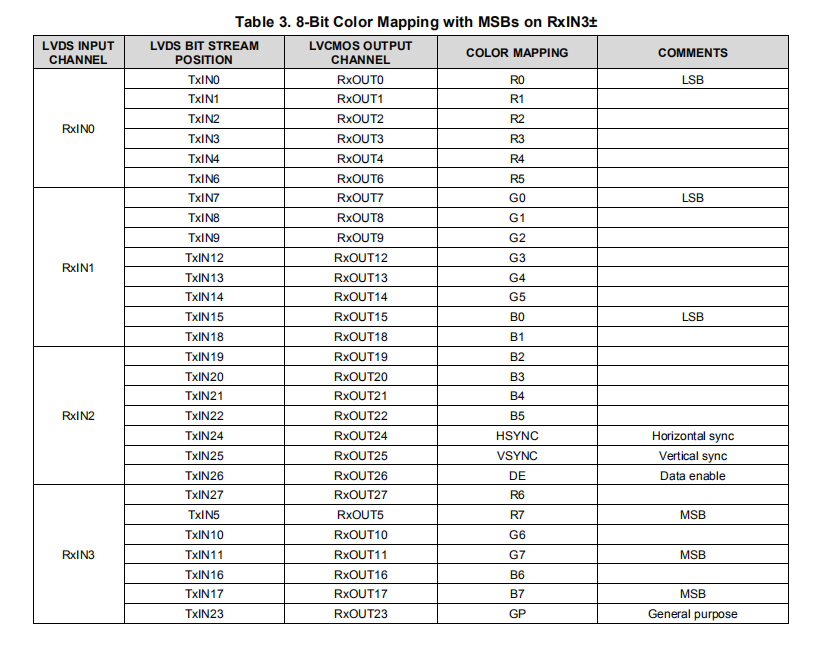

确保LVCMOS输出被映射为与反序列化程序之后的端点显示RGB映射要求对齐。有关8位RGB数据的两种常用映射拓扑,请参见以下内容。

1.lsb映射到RxIN3±。

2.MSB映射到RxIN3±。

表2和表3描述了如何将这两种流行拓扑映射到DS90CF386输出。

如果DS90CF386或DS90CF366用于支持18 bpp,则通常使用表2,其中RxIN3±(如适用)保留为“无连接”。通过这种映射,RGB数据的msb保留在RXIN0±、RXIN1±和RXIN2±上,而原始8位RGB分辨率的两个lsb从RxIN3±中忽略。

RSKM互操作性

在将接收机设计成系统应用程序时,最重要的因素之一是评估有多少RSKM(接收机倾斜裕度)可用。在每个LVDS时钟周期中,LVDS数据流携带7个序列化数据位。理想情况下,每个位的传输脉冲位置将每隔(n×T)/7秒出现一次,其中n=位位置,T=LVDS时钟周期。同样,理想情况下,每个位的Rx选通位置将每隔((n+0.5)×T)/7秒发生一次。然而,在实际系统中,由于电缆倾斜、时钟抖动和ISI的影响,LVDS Tx和Rx的每一位都会有非理想的脉冲和选通位置。这个概念如图23所示。

为了确定整个LVDS位流的绝对最小值,必须考虑位0-6的所有左右边距。这个绝对最小值对应于RSKM。

为了提高LVDS发射机和接收机之间的RSKM性能,设计者通常会将LVDS时钟相对于LVDS数据提前或延迟。相对于LVDS数据移动LVDS时钟可以改善发射机的设置和保持时间的位置,而不是接收机的设置和保持时间。

如果左位边距小于右位边距,则可以延迟LVDS时钟,以使输入数据的Rx选通位置看起来延迟。如果右位边距小于左位边距,则所有LVDS数据对都可以均匀地延迟,以便输入数据的LVDS时钟和Rx选通位置似乎提前。为了延迟LVDS数据或时钟对,设计者要么增加PCB跟踪长度,要么在LVDS发送器和接收器之间安装电容器。需要注意的是,当使用这些技术时,所有串行位位置都会均匀地向右或向左移动。

在设计带有第三方OpenLDI发射机的DS90CF386或DS90CF366接收机时,用户必须根据Tx脉冲位置和Rx选通位置计算偏差余量预算(RSKM),以确保传输无误。有关计算RSKM的更多信息,请参阅应用说明,信道链路I和FPD链路I设备的接收机倾斜裕度(SNLA249)。

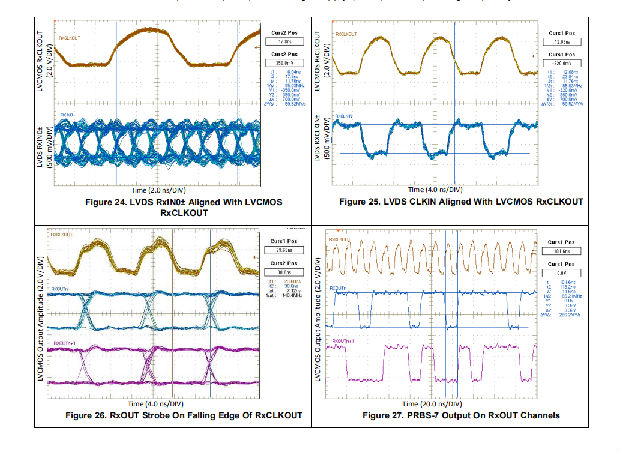

应用曲线

以下应用曲线是DS90C385A系列化器与DS90CF386反序列化器接口的示例,其工作频率为85 MHz,标称温度(25oC)和电压供应(3.3 V)。

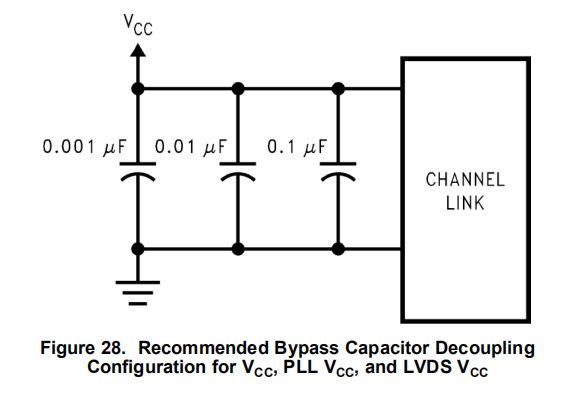

电源建议

正确的电源去耦对于确保稳定的电源供应和最小的电源噪声非常重要。需要旁路电容器来减少开关噪声的影响,这可能会限制性能。对于保守方法,建议在每个VCC(VCC、PLL VCC、LVDS VCC)和接地层之间使用三个并联连接的去耦电容器(表面贴装的多层陶瓷型)。三个电容值分别为0.1μF、0.01μF和0.001μF。首选电容器尺寸为0402。图28显示了一个示例。设计师应采用宽的电源和接地线路,并确保每个电容器都有自己的接地平面通孔。这有助于降低电源滤波的整体电感。如果电路板空间限制了旁路电容器的数量,则PLL VCC应接受最多的滤波。接下来是LVDS VCC引脚,最后是逻辑VCC引脚。

布局

布局指南

与任何高速设计一样,电路板设计者必须通过限制可能对高频和EMI性能产生不利影响的反射和串扰来最大限度地提高信号完整性。以下实践是优化设备性能的建议布局指南。

•确保差分对记录道始终紧密耦合,以消除来自其他信号的噪声干扰,并充分利用差分信号的共模噪声抵消效果。

•在给定差分对的信号轨迹上保持相等的长度。

•通过减少信号轨迹上通孔的数量来限制阻抗不连续性。

•消除轨迹上的任何90o角,改用45o弯头。

•如果必须在一个信号极性上存在过孔,则在差分对的另一个极性上镜像过孔实现。

•匹配所选物理介质的差分阻抗。该阻抗还应与通过接收器输入端差分对连接的终端电阻值匹配。

•如有可能,对LVDS输入使用短记录道。

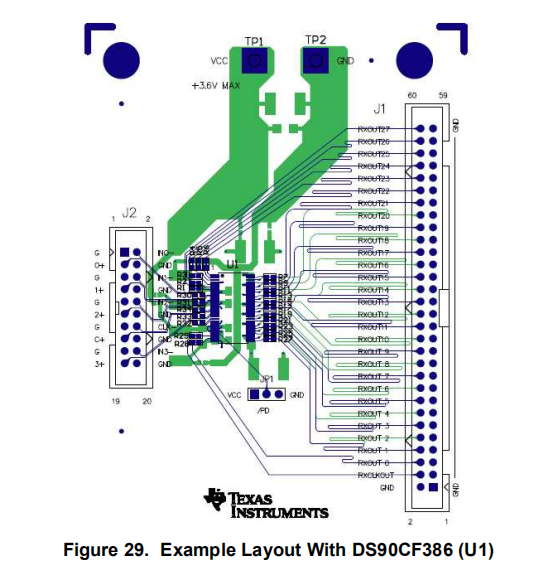

布局示例

下图显示了DS90CF386的布局示例。蓝色的痕迹对应顶层,绿色的痕迹对应底层。请注意,DS90CF386的差分对输入是紧密耦合的,并且靠近连接器引脚。此外,观察电源去耦电容器应尽可能靠近电源引脚,并带有通孔,以最小化电感。此布局中说明的原理也适用于48针DS90CF366。