DAC715点击型号即可查看芯片规格书

特征

●高速16位并行双缓冲接口

●电压输出:0至+10V

●13、14、15位线性等级

●16位单调超温(L级)

●功耗:最大600mW

●自动调整增益补偿和D/A转换器

●28-引线DIP和SOIC封装

说明

DAC715是一个完整的单片数字-模拟转换器,包括+10V温度补偿基准、电流-电压放大器、双缓冲16位并行接口和一个异步清除功能,可立即将输出电压设置为满量程的一半。

在±12V或±15V电源下工作时,输出电压范围为0至+10V。增益和双极性偏移调整的设计使得它们可以通过外部电位器或外部D/A进行设置转换器输出放大器有接地短路保护。

28针DAC715采用0.3英寸塑料浸渍和宽体塑料SOIC封装。DAC715P、U、PB和UB的温度范围为-40°C至+85°C,而DAC715PK、UK、PL和UL的温度范围为0°C至+70°C。

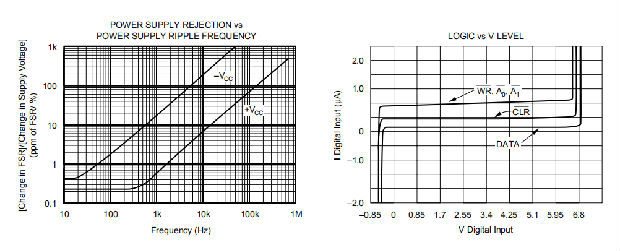

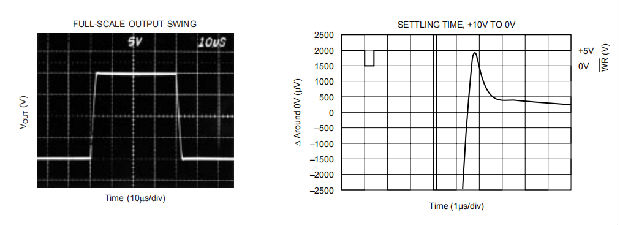

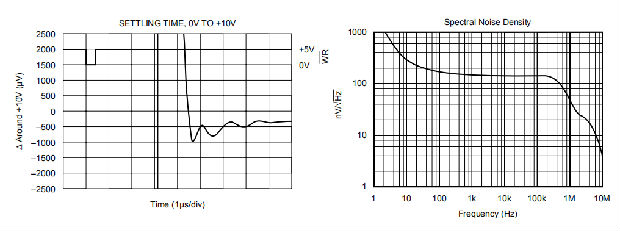

典型性能曲线

TA=+25°C,VCC=±15V时,除非另有说明。

规范讨论

线性误差

线性误差定义为模拟输出与传输特性端点之间绘制的直线的偏差。

微分线性误差

差分线性误差(DLE)是指从一个相邻状态到下一个状态的输出变化与1LSB的偏差。当数字输入码由一个码字变为相邻码字时,其输出步长为1/2LSB~3/2LSB。如果DLE大于-1LSB,则认为D/A是单调的。

单调性

如果为了增加数字输入值,输出增加或保持不变,则D/A转换器是单调的。对于性能等级DAC715P/U、DAC715PB/UB、DAC715PK/UK和DAC715PL/UL,DAC715的单调性在13、14、15和16位的规格温度范围内得到保证。

沉降时间

稳定时间是指输入改变后,D/A输出在其最终值附近的误差带内稳定的总时间(包括转换时间)。对于10V和1LSB的输出阶跃变化,设定的稳定时间在满标度范围(FSR)的±0.003%范围内。1LSB的变化是在主进位(FFFFh到0000h,0000h到FFFFh:BTC代码)处测量的,这是发生最坏情况的稳定时间的输入转换。

总谐波失真

总谐波失真定义为谐波值平方和的平方根与基频值的比值。以采样率fs下基频振幅的%表示。

信噪比(SINAD)

SINAD除了量化和内部随机噪声功率外,还包括了输出噪声功率定义中的所有谐波分量和突出杂散分量。在指定的输入频率和采样率fs下,SINAD用dB表示。

数模故障脉冲

当输入改变状态时,从数字输入注入模拟输出的电荷量。它是在输入代码的半刻度处测量的,其中尽可能多的开关将状态从FFFFh更改为0000h。

数字馈通

当未选择D/A时,数字输入上的高频逻辑活动通过设备耦合并显示为输出噪声。这种噪声是数字反馈。

操作

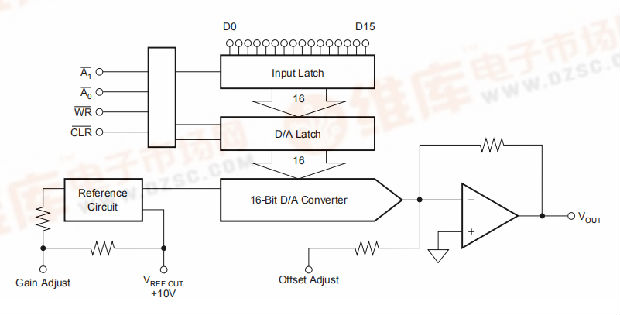

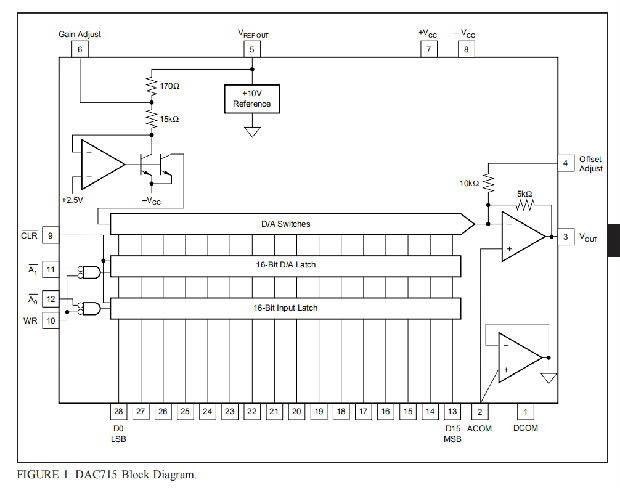

DAC715是一个单片集成电路16位D/a转换器,配有16位D/a开关和梯形网络、电压基准、输出放大器和微处理器总线接口。

接口逻辑

DAC715具有双缓冲数据锁存器。输入数据锁存器保存一个16位数据字,然后将其加载到第二个锁存器(D/a锁存器)中。这种双缓冲结构允许同时更新多个D/A转换器。所有数字控制输入低电平有效。参考图1所示的框图。

所有锁闩均为水平触发。当启用输入为逻辑“0”时出现的数据将进入锁存器。当使能输入返回逻辑“1”时,数据被锁存。

CLR输入重置输入锁存器和D/A锁存器,以提供半标度输出。

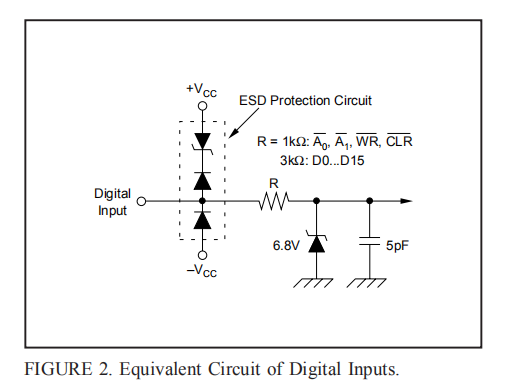

逻辑输入兼容性

DAC715数字输入是TTL兼容(1.4V开关电平),低泄漏,高阻抗。因此,输入适合于由任何类型的5V逻辑家族驱动,例如CMOS逻辑。数字输入的等效电路如图2所示。

如果不连接,输入将浮动到逻辑“0”。建议将任何未使用的输入连接到DCOM,以提高抗噪性。

当电源关闭时,数字输入保持高阻抗。

输入编码

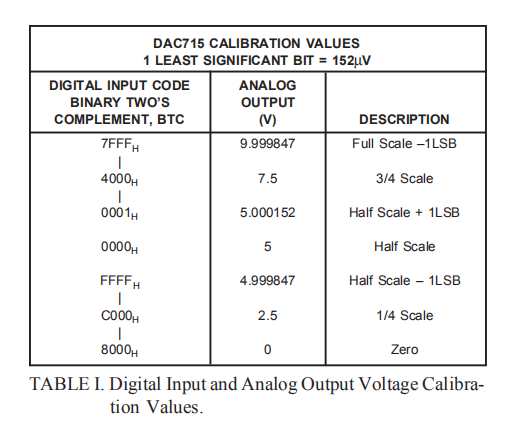

DAC715被设计成接受二进制2的补码(BTC)输入码。对于单极模拟输出配置,7FFF的数字输入提供全刻度输出,8000H给出零输出,以及0000H提供半标度输出。

内部参考

DAC715包含+10V参考电压。参考输出可用于驱动外部负载,源电流高达2mA。负载电流应该是恒定的,否则转换器的增益会改变。

输出电压摆幅

DAC715的输出放大器的输出范围是0到+10V。提供+0.4V或更高的电压。

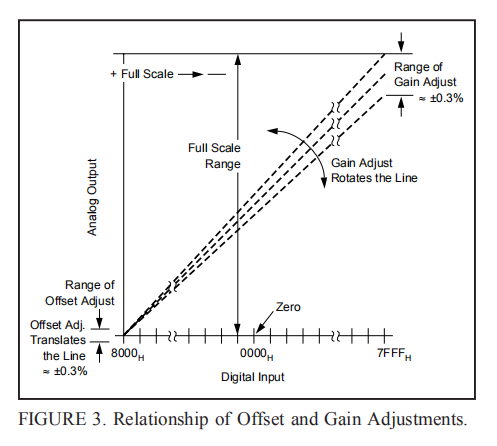

增益和偏移调整

图3说明了单极性连接D/a转换器的偏移和增益调整之间的关系。应首先调整偏移量,以避免调整的相互作用。校准值和代码见表一。这些调整的最小范围为±0.3%。

偏移量调整

应用产生零输出电压的数字输入代码,并将偏移电位计或偏移调整D/A转换器调整为0V。

增益调整

应用提供最大正电压输出的数字输入。调整增益电位计或增益调整D/A转换器,以获得该正满标度电压。

安装

一般注意事项

由于DAC715的高精度,接地和接触电阻等系统设计问题变得非常重要。具有10V满标度范围的16位转换器的1LSB值为152μV。负载电流为5mA时,串联布线和连接器电阻仅为60mΩ,将导致300μV的电压降。要了解这在系统布局方面的含义,典型的1盎司覆铜印制电路板的电阻率为1/2 mΩ/平方。对于5mA负载,10毫英寸宽60毫英寸长的印刷电路导体将导致150μV的电压降。

DAC715的模拟输出具有152μV(–96dB)的LSB大小。在感兴趣的频率范围内,D/A的噪声下限必须保持在该水平以下。DAC715的噪声频谱密度(包括由内部基准产生的噪声)如典型性能曲线部分所示。

连接到高分辨率D/A转换器的布线应能提供与RFI和EMI源的最佳隔离。消除射频辐射或拾波的关键是小回路面积。信号线和它们的回路导线应保持在一起,以便它们对任何外部磁场都有一个小的俘获截面。不建议使用钢丝缠绕结构。

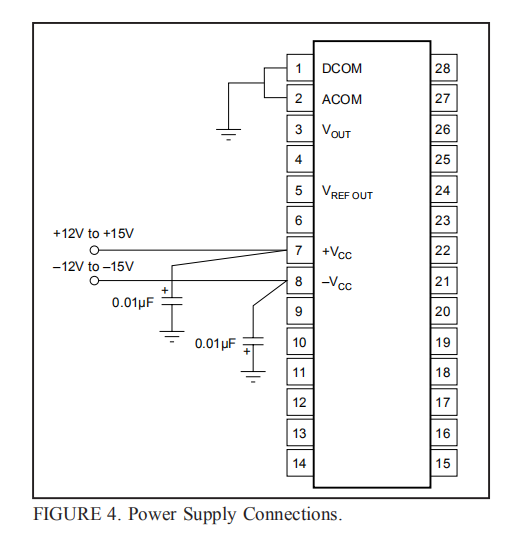

电源和参考连接

应添加电源去耦电容器,如图4所示。在–Vcc下使用1至10μF钽电容器可获得最佳性能。临界沉降时间较短的应用程序可以在–Vcc 作为下使用0.01μF以及at+Vcc。电容器应靠近包装。

DAC715有单独的模拟公共管脚和数字公共管脚。通过DCOM的电流主要是开关瞬态,幅值最高可达1mA。对于所有代码,通过ACOM的电流通常为5μA。

使用单独的模拟和数字接地平面和单个互连点,以尽量减少接地回路。模拟管脚彼此相邻,有助于将模拟信号与数字信号隔离开来。模拟信号应尽可能远离数字信号,并应以直角交叉。D/A封装周围以及模拟和电源引脚附近的固态模拟接地平面将隔离D/A和开关电流。建议将DCOM和ACOM直接连接到包下的接地层。

如果使用多个DAC715,或者如果DAC715与其他组件共享电源,则将ACOM和DCOM线路连接在一起一次(而不是在每个芯片上)可能会获得更好的结果。

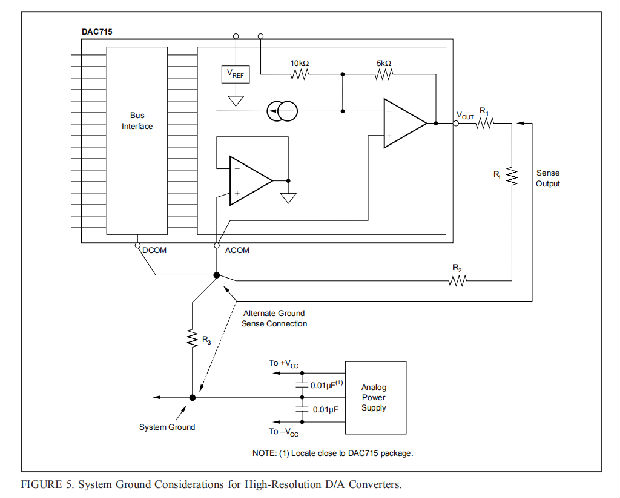

负载连接

由于VOUT和VREF OUT的参考点是ACOM引脚,因此将D/A转换器负载直接连接到ACOM引脚很重要。参考图5。

引线电阻和接触电阻用R1到R3表示。只要负载电阻RL恒定,R1只会引入增益误差,并可通过D/a增益调整或系统范围增益校准消除。如果在ACOM上检测到输出电压,则R2是RL的一部分。

在某些应用中,将负载返回到D/A转换器的ACOM引脚是不切实际的。感应系统接地点的输出电压是合理的,因为只要R3是低电阻接地层或导体,DAC715 ACOM电流没有变化。在这种情况下,您可能希望将DCOM连接到系统接地。

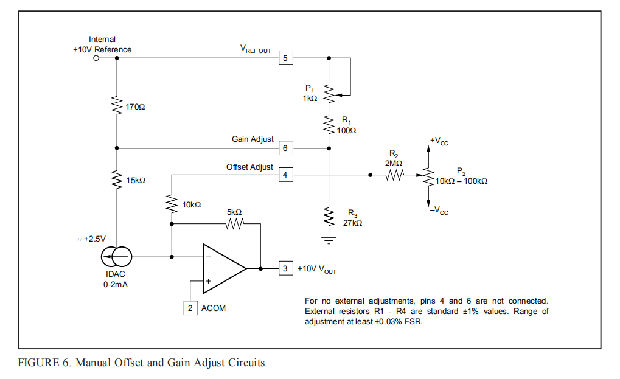

增益和偏移调整连接使用电位计

增益和偏移调整引脚提供了使用外部电位计的微调。15圈电位计提供足够的分辨率。这些微调的调整范围至少为满刻度范围的±0.3%。参考图6。

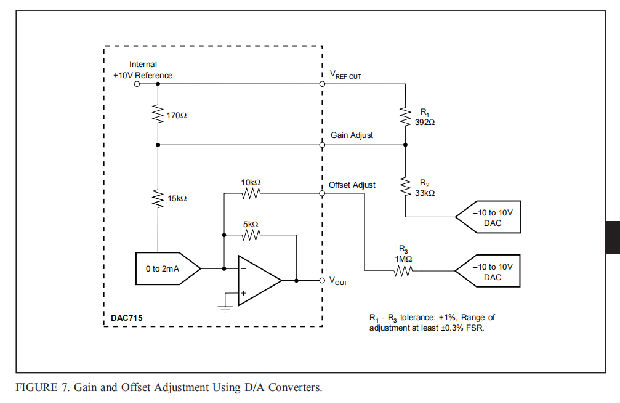

使用D/A转换器

DAC715的增益调整和偏移调整电路已经被布置成使得这些点可以容易地由外部D/A转换器驱动。参考图7。12位D/A转换器提供偏移调整分辨率和增益调整分辨率,每LSB步进30μV到50μV。

当D/A转换器输出大约为0伏的半刻度时,增益和偏移的标称值出现。

数字接口

总线接口

DAC715有一个16位双缓冲数据接口和控制线,便于连接到16位总线。双缓冲特性允许同时更新多个D/A。

A0是数据输入闩锁的启用控制。A1是D/A闩锁的启用。WR用于将数据选通到由A0和A1启用的锁存器中。参考图1的方框图和第3页的时序图。

CLR将输入数据锁存器和D/A锁存器设置为0000H(D/A输出为5V)。

单缓冲操作

为了将DAC715接口作为一个缓冲闩锁来操作,数据输入锁存器通过连接A0到DCOM来永久启用。如果A1不用于启用D/A,它也应连接到DCOM。对于这种工作模式,WR的宽度至少需要80ns,以便将数据通过数据输入锁存器传递到D/A锁存器。

透明接口

DAC715的数字接口可以通过断言AO、A1和WR低,以及CLR高而变得透明。