特征

•用于SRAM非易失性控制的电源监控和切换

•输入解码器允许控制1组或2组SRAM

•写保护控制

• 3V一次电池输入

•3.3-V操作

•系统上电复位的复位输出

•小于20 ns芯片启用传播延迟

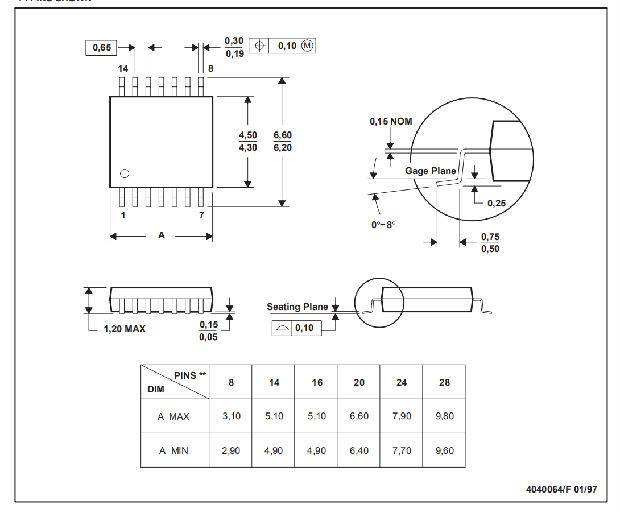

•16导联小型TSSOP封装

应用

• NVSRAM模块

•销售点系统

•传真机、打印机和复印机

•互联网设备

•服务器

•医疗器械和工业产品

说明

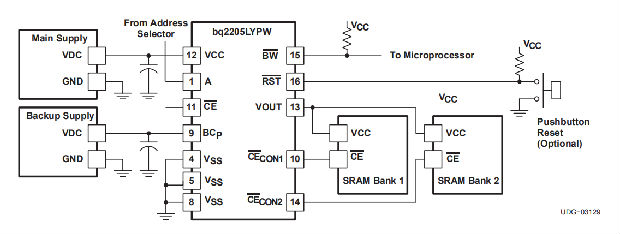

具有复位功能的CMOS bq2205 SRAM非易失性控制器提供将一组或两组标准CMOS SRAM转换成非易失性读/写存储器所需的所有功能。

精密比较器监控3.3V VCC输入是否超出公差条件。当检测到超差时,两个条件芯片使能输出被强制停用,以写保护SRAM的两个组。

当VCC衰减时,外部SRAM的电源从VCC电源切换到备用电池电源。在随后通电时,VOUT电源会自动从备用电源切换到VCC电源。外部SRAM处于写保护状态,直到电源有效状态存在。复位输出为系统提供电源故障和上电复位。在功率有效运行期间,输入解码器A选择两组SRAM中的一组。

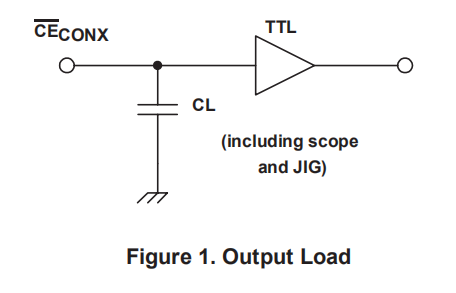

交流试验条件,输入脉冲电平0 V≤VIN≤3 V,tR=tF=5 NS。

功能描述

两组CMOS静态RAM可以使用VOUT和来自bq2205的条件芯片使能输出管脚支持电池。当电压输入VCC在电源故障期间下降时,两个经过调节的芯片使能输出CECON1和CECON2被强制非活动,独立于芯片启用输入CE。当VCC降至超出公差阈值VPFD时,此活动无条件写入保护外部SRAM。当电源继续通过VPFD时,内部开关设备将VOUT强制转换为备用能量来源:CECON1CECON2被VOUT能量源维持在高位。

在通电期间,当VCC高于备用单元输入电压源VOUT时,VOUT切换回3.3 V电源。电源达到后,输出CECON1和CECON2保持非活动状态,持续时间为tCERVPFD,独立于CE输入,允许处理器稳定。

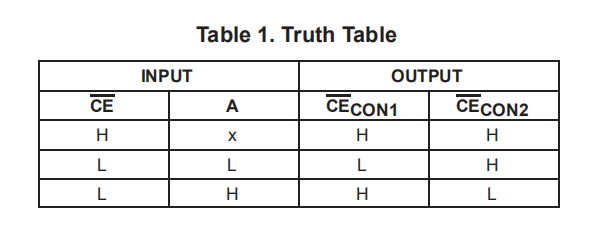

在功率有效运行期间,CE输入通过传输延迟小于tCED的两个CECONx输出之一。CE输入在两个CECONx输出引脚中的一个上输出;取决于bank select input A的电平。参见下面的真值表。

Bank-select输入A通常与一个高阶地址pin相连,这样就可以使用低密度存储设备来设计大型非易失性存储器。非挥发性和解码是通过硬件连接实现的,如应用程序图所示。

RST输出可以用作微处理器的上电复位。当RST返回非活动状态时,可以开始访问外部RAM。

备用电池输入

备用能源,BCp输入在bq2205上提供,用于外部一次电池。原电池输入设计用于接受任何3V的主电池(不可充电),通常是某种锂化学类型。

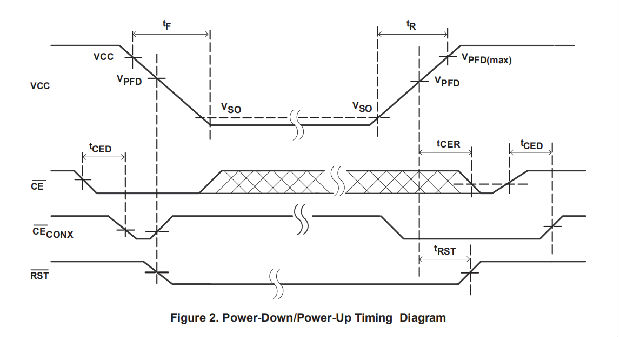

断电和加电循环

bq2205连续监控VCC是否超出公差。在电源故障期间,当VCC低于VPFD时,bq2205写保护外部SRAM。当VCC小于VPFD且BCP大于VPFD时,或当VCC小于BCP且BCP小于VPFD时,电源切换至BCP。当VCC高于VPFD时,电源为VCC。在VCC上升到VPFD以上后,写保护将持续一段时间。

外部CMOS静态RAM使用来自bq2205的VOUT和芯片启用输出引脚进行电池备份。当电压输入VCC在电源故障期间下降时,芯片启用输出CECONx被强制停用,独立于芯片启用输入CE。

当电源继续通过VPFD时,内部开关设备将VOUT强制转换为外部备用能源。CECONx由VOUT能源维持高位。

当备用电源电压高于电源电压时,备用电源切换至电压源。如果VPFD<bq2205上的BCP,则在VPFD处切换至主电源。在电源达到VPFD后,CECONx保持非活动状态一段时间,与CE输入无关,以允许处理器稳定。

上电复位

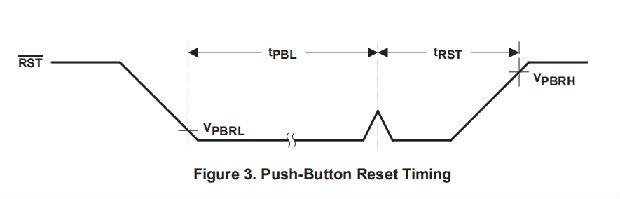

bq2205提供上电复位功能,在VCC通过VPFD后,它将RST引脚拉低,并在tRST通电时保持低电平。当BCP上的电池电压有效时,RST对于VCC=VSS仍然有效。这个如果使用按钮复位,该引脚上的上拉电阻不应超过10 kΩ。

电池电量低警告

bq2205在通电时检查蓄电池电压。电池警告比较器的阈值是VBW,并且在每次加电有效并在tCER时间后锁定后感测到低电平。锁存值显示在BW引脚,低表示电池电量低。

申请信息

PCB布局信息

要特别注意PCB布局。以下提供了一些指导原则:

*为了获得最佳性能,从输入端子到VSS的去耦电容器应尽可能靠近bq2205,信号管脚和VSS管脚的跟踪时间都很短。

*所有低电流VSS连接应与输入电源的高电流路径分开。使用单点接地技术,包括小信号接地路径和电源接地路径。

机械数据

PW(R-PDSO-G**)塑料小外形包装

注:

A、所有线性尺寸单位均为毫米。

B、 本图纸如有更改,恕不另行通知。

C、 主体尺寸不包括不超过0.15的模具飞边或突出物。

D、 属于JEDEC MO-153。