DS4520点击型号即可查看芯片规格书

特征

♦ 机械跳线和开关的可编程更换

♦ 九个NV输入/输出引脚

♦ 64字节NV用户存储器(EEPROM)

♦ I2C兼容串行接口

♦ 同一I2C总线上最多可以有8个设备多点连接

♦ 带可配置上拉的开漏输出

♦ 输出可下沉12毫安

♦ 低功耗

♦ 宽工作电压(2.7V至5.5V)

♦ 工作温度范围:-40°C至+85°C

应用

•基于RAM的多轮廓FPGA组交换

•在引导闪存之间选择

•设置ASIC配置/配置文件

•服务器

•网络存储

•路由器

•电信设备

•PC外围设备

一般说明

DS4520是一个9位非易失性(NV)I/O扩展器,具有64字节的NV用户内存,由兼容I2CTM的串行接口控制。DS4520为用户提供了硬件跳线的数字可编程替代方案以及用于控制数字逻辑节点的机械开关。此外,每个引脚的数字状态可以通过串行接口读取。每个I/O引脚可独立配置。输出为开漏式,可选择上拉。每个输出都有能力下沉到12毫安。由于该设备是NV,它在所需的状态下通电,允许它在通电时立即控制数字逻辑输入,而不必等待主机CPU启动控制。

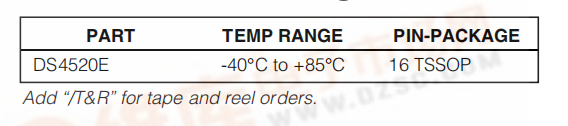

订购信息

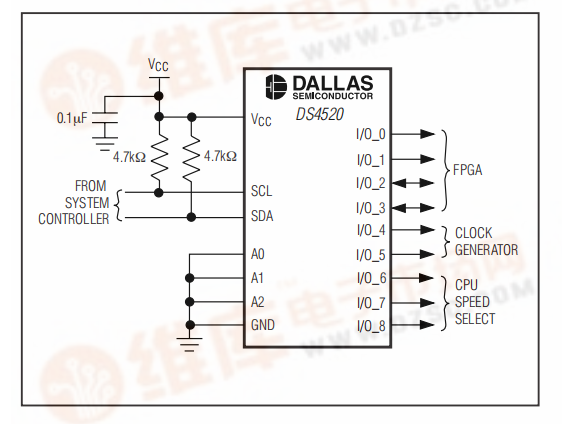

典型工作电路

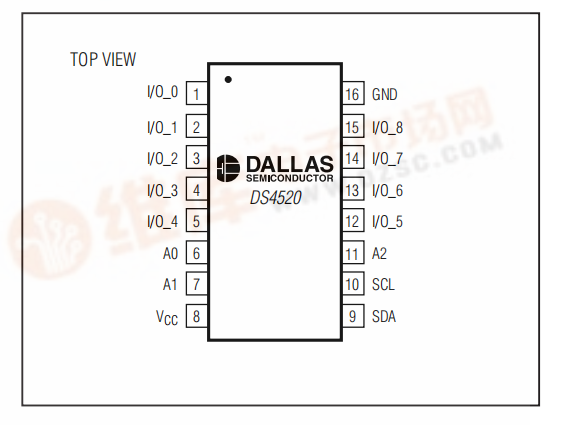

引脚配置

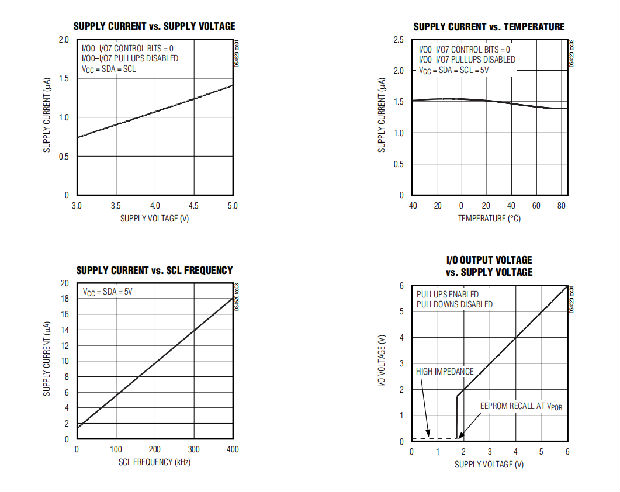

典型工作特性

(除非另有说明,否则VCC=+5.0V,TA=+25°C。)

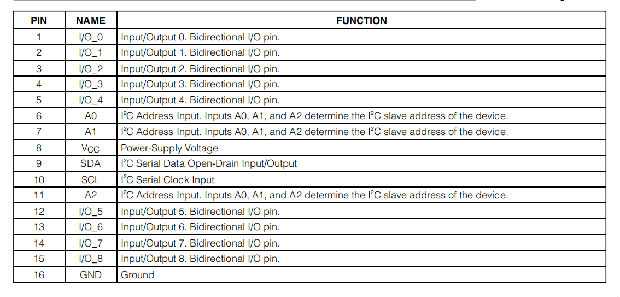

管脚说明

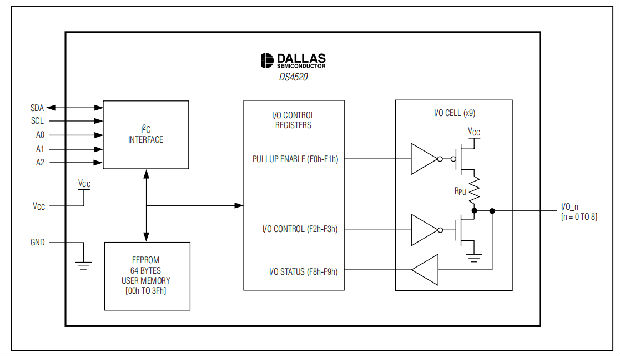

方块图

详细说明

DS4520包含9个双向、NV、输入/输出(I/O)引脚和64字节EEPROM用户存储器。I/O引脚和用户存储器可通过兼容I2C的串行总线访问。

可编程NV I/O引脚

每个可编程I/O引脚由一个输入端和一个开路集电极输出端和一个可选的内部上拉电阻器组成。要启用每个I/O引脚的上拉,请写入上拉启用寄存器(F0h和F1h)。要将输出拉低或将下拉晶体管置于高阻抗状态,请写入I/O控制寄存器(F2h和F3h)。要读取I/O引脚上的电压电平,请读取I/O状态寄存器(F8h和F9h)。要确定输出寄存器的状态,请读取I/O控制寄存器和上拉电阻器寄存器。I/O控制寄存器和上拉启用寄存器都是SRAM阴影EEPROM寄存器。可以使用配置寄存器中的SEE位禁用寄存器的EEPROM写入。这减少了写入寄存器所需的时间,并增加了在EEPROM磨损之前可以调整I/O引脚的次数。

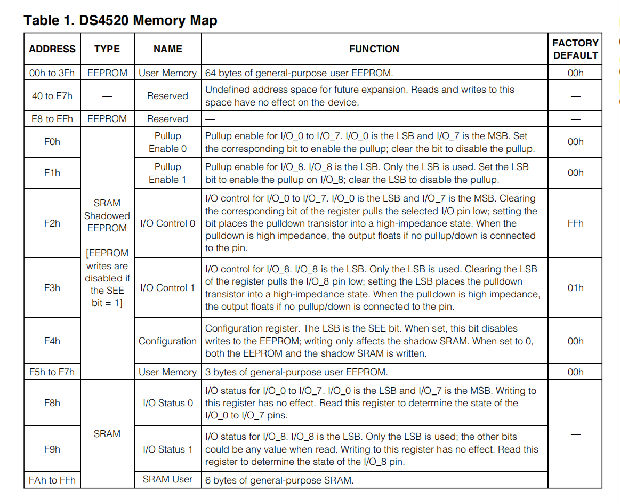

内存映射和内存类型

DS4520内存映射如表1所示。DS4520中有三种不同类型的内存:EEPROM、SRAM阴影EEPROM和SRAM。指定为EEPROM的内存位置为NV。写入这些位置将导致EEPROM写入周期,时间由tWR在AC电气特性表中指定。指定为SRAM阴影EEPROM的位置可以配置为在SEE位指定的两种模式中的一种(配置寄存器F4h的LSB)。当SEE位=0(默认值)时,存储器位置的作用类似于EEPROM。然而,当SEE=1时,写入阴影SRAM而不是EEPROM。这消除了EEPROM的写入时间tRW,以及磨损EEPROM的问题。这对于希望不断写入I/O的应用程序来说非常理想。可以为EEPROM中的I/O编程通电默认状态(SEE=0),然后一旦通电,SEE可以写入1,这样就可以在SRAM中定期更新I/O。DS4520中的最后一种内存是标准SRAM。

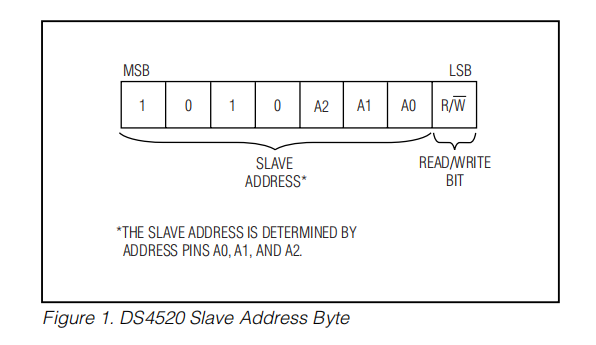

从地址和地址引脚

DS4520的从机地址由A0、A1和A2地址引脚的状态决定,如图1所示。连接到GND的地址管脚在从机地址的相应位位置产生“0”。相反,连接到VCC的地址管脚在相应的位位置产生“1”。I2C通信将在后面的部分中详细描述。

I2C串行接口说明

I2C定义

以下术语通常用于描述I2C数据传输。

主设备:主设备控制总线上的从设备。主设备产生SCL时钟脉冲、启动和停止条件。从设备:从设备根据主机的请求发送和接收数据。

总线空闲或不忙:当SDA和SCL都不活动且处于逻辑高电平状态时,停止和启动条件之间的时间。当总线空闲时,它通常会启动从设备的低功耗模式。

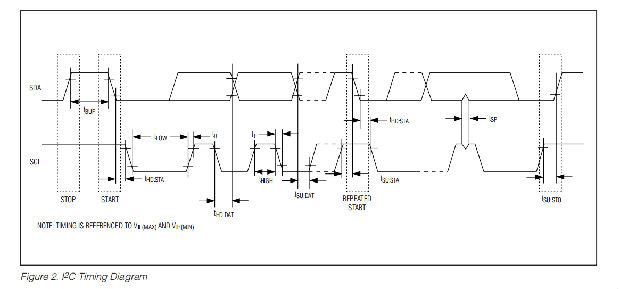

启动条件:启动条件由主机生成,以启动与从机的新数据传输。当SCL保持较高时,将SDA从高转换到低将生成启动条件。有关适用的定时,请参阅时序图。

停止条件:主机生成停止条件,以结束与从机的数据传输。当SCL保持较高时,将SDA从低转换到高将生成停止条件。有关适用的定时,请参阅时序图。

重复启动条件:主机可以在一次数据传输结束时使用一个重复的启动条件来指示它在当前数据传输之后立即启动新的数据传输。在读取操作期间,通常使用重复启动来标识特定的内存地址以开始数据传输。重复起动条件与正常起动条件相同。有关适用的定时,请参阅时序图。位写入:SDA的转换必须在SCL的低状态下发生。在SCL的整个高脉冲加上设置和保持时间要求期间,SDA上的数据必须保持有效和不变(见图2)。在SCL上升沿期间,数据被转移到设备中。

位读取:在写入操作结束时,主机必须在位读取过程中的下一个SCL上升沿之前释放SDA总线线路一段适当的设置时间(见图2)。该装置在前一个SCL脉冲的下降沿将SDA上的每一位数据移出,并且该数据位在当前SCL脉冲的上升沿有效。请记住,主机生成所有SCL时钟脉冲,包括从机读取位时。

确认(ACK和NACK):确认(ACK)或不确认(NACK)总是在字节传输期间传输的第9位。接收数据的设备(读操作期间的主设备或写操作期间的从设备)通过在第9位发送零来执行ACK。设备通过在第9位期间发送一个来执行NACK。ACK和NACK的定时(图2)与所有其他位写入相同。ACK是设备正确接收数据的确认。NACK用于终止读取序列或作为设备没有接收数据的指示。

字节写入:字节写入由8位信息从主机传输到从设备(大多数信号优先)加上从设备到主机的1位确认。由mas ter发送的8位是根据位写入定义来完成的,而确认是使用位读取定义来读取的。

字节读取:字节读取是从机到主机的8位信息传输加上从机到从机的1位ACK或NACK。使用主字节的定义,从主机传输的最重要的位(从位)是使用第一个读到的定义的重要字节。主机必须将最后一个字节读入终止通信,以便从机将SDA的控制权返回给主机。

从字节地址:I2C总线上的每个从机响应在启动条件后立即发送的从机地址字节。从地址字节包含最高有效位7位的从属地址和最低有效位的R/W位。

DS4520的从机地址由A0、A1和A2地址引脚的状态决定,如图1所示。连接到GND的地址管脚在从机地址的相应位位置产生“0”。相反,连接到VCC的地址管脚在相应的位位置产生“1”。

当R/W位为0时(例如在A0h中),主机表示它将向从机写入数据。如果R/W=1(在本例中是A1h),则主机表示它将从从机读取数据。

如果写入的从机地址不正确,DS4520假定主机正在与另一个I2C设备通信,并忽略该通信,直到发送下一个启动条件。

内存地址:在I2C写入操作期间,主机必须传输一个内存地址,以标识从设备存储数据的内存位置。内存地址总是在从地址字节之后的写入操作中传输的第二个字节。

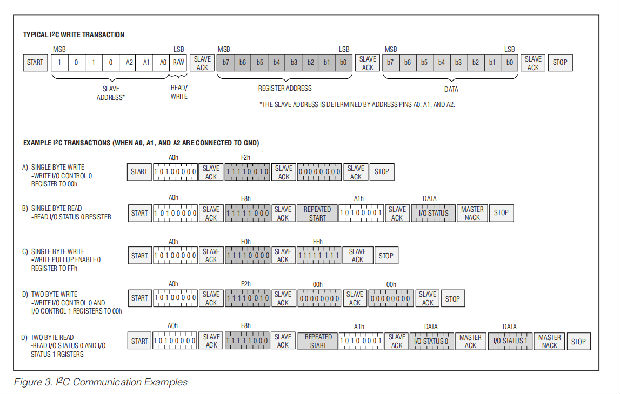

I2C通信

将单个字节写入从机:主机必须生成一个启动条件,写入从机地址字节(R/W=0),写入内存地址,写入数据字节,并生成停止条件。记住,在所有字节写入操作期间,主机必须读取从机的确认。

向从机写入多个字节:要向从机写入多个字节,主机生成一个启动条件,写入从机地址字节(R/W=0),写入内存地址,最多写入8个数据字节,并生成停止条件。

DS4520能够用一个写入事务写入最多8个字节(一页或一行)。这是由一个地址计数器内部控制的,它允许在发送每个数据字节之前将数据写入连续地址,而无需发送内存地址。地址计数器将写入限制为一个8字节页。尝试写入内存的其他页而不在页之间发送停止条件会导致地址计数器绕到当前行的开头。第一行从地址00h开始,随后的行以8的倍数开始(08h、10h、18h、20h等)。

为了防止发生地址包装,主机必须在页面末尾发送一个停止条件,然后等待总线空闲或EEPROM写入时间过去。然后主机可以生成一个新的启动条件,在继续写入数据之前,写入从地址字节(R/W=0)和下一个内存行的第一个内存地址。

确认轮询:每当EEPROM页被写入时,DS4520要求EEPROM写入时间(tW)在停止条件之后将页的内容写入EEPROM。在EEPROM写入期间,由于设备忙,设备不确认其从机地址。可以通过反复寻址DS4520来利用这种现象,这使得只要设备准备好,通信就可以继续。应答轮询的替代方法是等待最长时间tW,然后再尝试访问设备。

EEPROM写入周期:当EEPROM写入发生时,DS4520写入整个EEPROM内存页,即使页面上只有一个字节被修改。不修改页上所有8个字节的写入是有效的,不会损坏同一页上的任何其他字节。因为整个页面都是被写入的,所以即使是在事务处理期间未被修改的页面上的字节,也会受到写入周期的影响。DS4520的EEPROM写入周期在非易失性存储器特性表中指定。所示规格为最坏情况下的温度。它能够在室温下处理大约10倍的许多写操作。

从从机读取单个字节:与使用指定内存地址字节定义数据写入位置的写入操作不同,读取操作发生在内存地址计数器的当前值处。从机读取单个字节时,主机生成一个启动条件,写入R/W=1的从机地址字节,用NACK读取数据字节,以指示传输的结束,并生成停止条件。但是,由于要求主机跟踪内存地址计数器是不切实际的,因此应该使用以下方法从指定的内存位置执行读取。

操作地址的计数器

虚拟写入周期可用于将地址计数器强制设置为特定值。为此,主机生成一个启动条件,写入从机地址字节(R/W=0),写入它希望读取的内存地址,生成一个重复的启动条件,写入从地址字节(R/W=1),使用ACK或NACK(如适用)读取数据,并生成停止条件。

图3显示了一个使用重复启动条件来指定起始内存位置的读取示例。

从从机读取多个字节:读操作可用于通过一次传输读取多个字节。当从系统读取字节时,如果主机希望在终止事务之前读取另一个字节,则只需确认数据字节。在mas读入最后一个字节后,它必须NACK以指示传输的结束并生成一个停止条件。

应用程序信息

电源去耦

为了达到最佳效果,强烈建议在IC电源引脚上使用去耦电容器。去耦电容器的典型值为0.01μF和0.1μF。使用优质陶瓷表面贴装电容器,并将其安装在尽可能靠近IC的VCC和GND引脚的位置,以尽量减小引线电感。

芯片拓扑

晶体管计数:14398

基板接地