LM1972点击型号即可查看芯片规格书

一般说明

LM1972是一款数字控制的2声道78dB音频用CMOS工艺制作的衰减器。每个频道从0dB到47.5dB,衰减阶跃为0.5dB从48分贝到78分贝,静音功能减弱104分贝。对数衰减曲线可定制通过软件来适应所需的应用。μPot的性能可以通过其非常低的信噪比(THD+N)和高通道分离。每个μPot包含一个静音功能将输入信号与输出信号断开,提供最小衰减96dB。任何at tenuation设置之间的转换都是无需弹出的。LM1972的3线串行数字接口是TTL和与CMOS兼容;接收选择通道和所需的衰减级别。数据输出管脚LM1972允许将多个μpot菊花链连接在一起,减少要路由的启用和数据线的数量对于给定的应用程序。

主要规格

总谐波失真+噪声:0.003%(最大值)

频率响应:100 kHz(–3dB)(最小)

衰减范围(不包括静音):78dB(典型值)

差分衰减:?0.25dB(最大值)

信噪比(参考4 Vrms):110dB(min)

通道间隔:100dB(min)

特征

3线串行接口

菊花链能力

104dB静音衰减

弹出并单击“自由衰减更改”

应用

自动录音室混音控制台

音乐再现系统

扩声系统

电子音乐(MIDI)

个人电脑音频控制

绝对最大额定值(注2、1)

电源电压(VDD–VSS)15V

任何引脚电压VSS-0.2V至VDD+0.2V

功耗(注3)150兆瓦

静电放电耐受性(注4)2000V

结温150 303C

焊接信息

N包装(10秒)+260℉

储存温度−65°C至+150°C

工作额定值(注1)(注2)

TMIN TA TMAX公司

温度范围

TMIN≤TA≤TMAX 0○○C≤TA≤+70○○C

电源电压(VDD-VSS)4.5V至12V

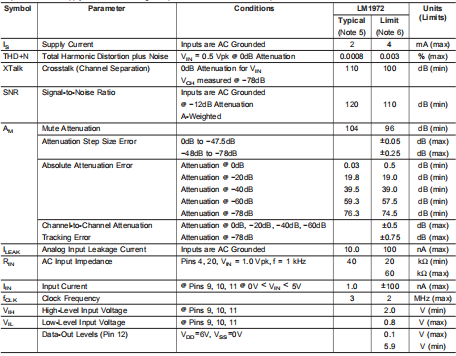

电气特性(注1)(注2)

以下规范适用于VDD=+6V、VSS=-6V、车辆识别号=5.5 Vpk和f=1 kHz的所有信道,除非另有规定

明确规定。限值适用于TA=25摄氏度。数字输入与TTL和CMOS兼容。

注1:除非另有规定,否则所有电压均根据接地引脚(1、3、5、6、14、16、19)测量。

注2:绝对最大额定值表示设备可能损坏的极限。工作额定值表示设备工作的条件,但不保证特定的性能限制。电气特性规定了在保证特定性能极限的特殊试验条件下的直流和交流电气规范。这假设设备在工作额定值范围内。没有限制的参数不保证规格然而,给定的典型值是设备性能的良好指示。

注3:最大功耗必须在高温下降额,并由TJMAX、θJA和环境温度TA决定。最大值允许的功耗为PD=(TJMAX-TA)/θJA或绝对最大额定值中给出的数值,以较低者为准。对于LM1972,TJMAX=+150摄氏度,当安装在板上时,典型的与环境热阻的连接为65°C/W。

注4:人体模型,100 pF通过1.5 kΩ电阻放电。

注5:典型值在25℃下测量,代表参数范数。

注6:限值保证为国家AOQL(平均输出质量水平)。

管脚说明

信号接地(3,19):每个输入都有自己独立的接地,GND1和GND2。

信号输入(4,20):有2个独立的信号输入,1和2。

信号输出(2,17):有2个独立的信号输出,输出1和输出2。

电源(13,15):正极电源引脚,VDD1和VDD2。

电源(7,18):负电压电源引脚,VSS1和VSS2。在单一电源配置中接地。

交流接地(1、5、6、14、16):这五个引脚没有以任何方式与模具进行物理连接(即,没有连接线)。这些引脚必须交流接地,以防止信号耦合在附近的大头针之间。应连接针脚14连接到插脚13和15,以便于布线和最佳隔离,如一个例子。

逻辑接地(8):接口的数字信号接地线路;时钟、加载/移位、数据输入和数据输出。

时钟(9):时钟输入接受TTL或CMOS电平信号。时钟输入用于将数据加载到内部移位在输入时钟波形的上升沿注册。

加载/移位(10):加载/移位输入接受TTL或CMOS电平信号。这是设备的使能管脚,当输入电压低(0V)时,所有的低数据都会被记录。

数据输入(11):数据输入接受TTL或CMOS电平信号。该引脚用于接收来自微控制器的串行数据,微控制器将被锁定并解码以改变通道的衰减水平。

数据输出(12):此引脚用于菊花链模式,其中通过同一数据线控制多个μPot。作为数据从μC被记录到链中,前面移位寄存器中的数据从数据输出引脚移位到链中的下一个μPot,如果它是链子。一旦所有的新的数据已经转移到各自的区域。

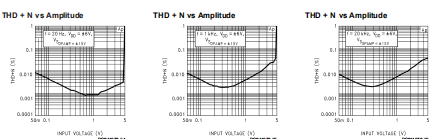

典型性能特征

应用程序信息

衰减步进方案

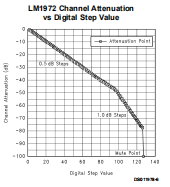

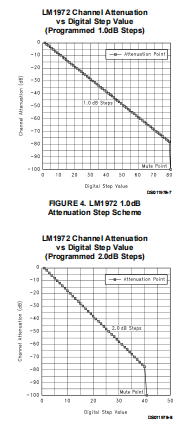

LM1972的基本衰减步进方案μPot如图3所示。这种衰减阶跃方案,但是,可以通过编程技术进行更改以适应不同的应用要求。一个这样的例子将是一个1dB的常数对数衰减方案摇摄函数的步骤如图4所示。唯一的对衰减方案定制的限制是给定的衰减水平及其相应的数据表1所示的位。设备将改变衰减仅当识别通道地址时才级别。什么时候?可识别,衰减水平将根据表1所示的数据位而改变。如图6所示,LM1972可以被配置为摇摄控制将单声道信号分为左声道和右声道。该电路可以利用基本衰减方案或被编程以提供恒定的1dB对数衰减方案如图4所示。

输入阻抗

μPot的输入阻抗在标称40千欧。消除任何不需要的直流分量在设备中传播时,通常在放置耦合盖时使用1μF。但是,如果dc与前一阶段的偏差可以忽略不计。对于性能更高的系统,首选输入耦合盖。输出阻抗μPot的输出通常在25 kΩ和35kΩ,随阶跃变化非线性变化。自从μPot由具有对数衰减的电阻梯形网络构成,输出阻抗为非线性。由于这种配置,一个μPot不能被认为是线性的电位器,但只能作为对数衰减器。应注意,由于输入阻抗大多数测量系统都不够高所需的精度。由于测量系统的低阻抗,μPot的输出将被加载向下,将导致读数不正确。防止装载从发生时起,JFET输入运算放大器应作为缓冲器/放大器。μPot的性能仅受以下因素的限制外部缓冲器/放大器的性能。

静音功能

μPot的一个主要特点是它能够将输入信号静音至104dB的衰减水平,如图3所示。这是通过物理隔离输入输出,同时输出引脚接地通过约2 kΩ。在设备通电期间获得静音功能或通过发送01111111及以上的任何二进制数据(到11111111)串行传输到设备。设备可以放置通过发送任何上面的数据。这允许设计师放置一个静音系统上的按钮,可能导致微控制器将适当的数据发送到μPot,从而使任何或所有频道。由于该功能是通过软件实现的,因此设计者在系统配置上具有很大的灵活性。

直流输入

尽管μPot被设计成用作衰减器对于音频频谱内的信号,设备能够跟踪输入直流电压。设备将跟踪DC每个供电轨上方的二极管电压下降。关于DC跟踪,需要记住的一点是μPot输出处的缓冲器,直流跟踪的分辨率取决于输出缓冲器的增益配置以及它的电源电压。还应记住输出缓冲器的电源电压不必相同作为μPot的电源电压。这样可以在直流跟踪时获得更高的分辨率。

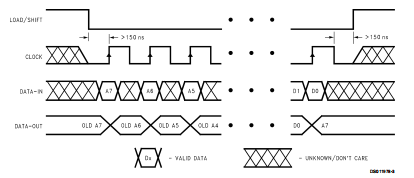

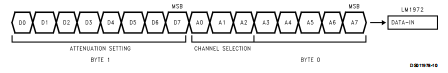

串行数据格式

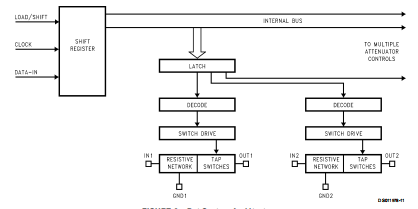

LM1972使用3线串行通信格式很容易被微控制器控制。时间安排三线制,包括数据输入、时钟和负载/移位如图2所示。图9以方块图的形式展示了数字接口如何控制抽头开关选择适当的衰减级别。如所示图2,负载/换档线应至少降低150 ns在第一个时钟脉冲的上升沿之前在每一组16个数据位的传输过程中处于低位。串行数据由8位组成,用于信道选择8位用于衰减设置。地址数据和衰减设置数据,首先发送MSB和8位地址数据在8位衰减之前发送数据。请参阅图7,以确认 mat传输过程的串行数据。

μPot系统架构

μPot的数字接口本质上是移位寄存器,其中串行数据被移入、锁定,然后被解码。作为新数据被转移到数据输入管脚中,之前的锁定的数据从数据输出引脚移出。一旦数据移入时,负载/换档线变高,锁定在新数据。然后对数据进行解码开关被激活以设置选定频道。这个过程每一个衰减变化的时间。每个通道都是最新的,仅当该通道被选作衰减器时更改或系统关机然后备份再一次。当μPot通电时,放置每个通道进入静音模式。

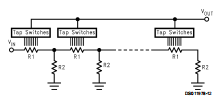

μPot梯形结构

μPot的每个通道都有自己的独立电阻lad der网络。如图8所示,梯子由构成衰减的多个R1/R2元件计划。在每个元件中都有抽头开关,选择与表1中的数据位。在图8中可以看到无论选择哪个抽头开关,而输出阻抗根据所选的分接开关而变化。

数字线路兼容性

μPot的数字接口部分与由于移位寄存器输入作用而产生的TTL或CMOS逻辑当2个二极管的阈值电压下降或大约1.4伏。

数字数据输出管脚

数据输出引脚可用于菊花链系统配置,其中将使用多个μpot。使用菊花链配置允许系统设计器使用每个链只有一个数据和一个装载/移位线,因此简化PCB跟踪布局。为了提供最高级别的通道分离并将任何信号线与数字噪声隔离数据输出引脚应通过2KΩ电阻器端接如果不使用。引脚可以保持浮动,但是,任何信号那条线上的噪音可能会耦合到相邻的线上,从而产生更高的噪音规格。

菊花链能力

由于μPot的数字接口本质上是移位寄存器,可以使用相同的数据对多个μpot进行编程以及装载/换档管路。如图11所示,对于n-μPot菊花链,有16n位需要移位和加载链子。数据加载顺序与n-μPots,因为它是一个μPot。首先,装载/换档管路低,则数据按顺序进入,同时每个μPot中的进位数据从数据输出引脚移出到链中的下一个μPot,如果它是链子。然后装载/换档管路变高;锁定将数据放入每个对应的μpot中。数据是根据地址解码(信道选择)和控制衰减水平的适当分接开关是挑选出来的。

串扰测量

如典型性能特性部分所示,通过放置一个通道上的信号并测量输出端的电平相同频率的另一个频道。重要的是确保正在测量的信号电平相同能够获得串扰的真实指示的频率。此外,为确保测量准确,测量通道的输入应通过1μF交流接地电容器。

点击和弹出

那么,为什么还需要输出缓冲区呢?有这个问题的三个答案,都很重要从系统的角度来看。在输出端使用缓冲器/放大器的第一个原因

μPot是为了确保不会听到咔哒声或砰砰声衰减设备中的阶跃变化。如果输出级使用了车载双极运算放大器,则需要有限的直流偏置电流当输出阻抗的变化。同样,这种现象是由于μPot的输出阻抗随阶跃变化和双极放大器需要有限的量直流偏压电流。作为阻抗改变了,直流偏置电流也随之改变电压“pop”。其次,μPot没有驱动能力,因此增益需要通过缓冲器来实现/非反转放大器。第三,μPot的输出需要看到防止加载和随后的眼环线性误差。JFET输入缓冲器提供高输入阻抗μPot的输出,这样就不会发生这种情况。使用JFET输入可以避免咔哒声和砰砰声缓冲器/放大器,如LF412ACN。LF412有一个高输入阻抗,具有低噪声地板和在整个音频频谱中保持低THD+N系统的信号完整性和线性度。演出系统的解决方案完全取决于质量以及JFET输入缓冲器/放大器的性能。

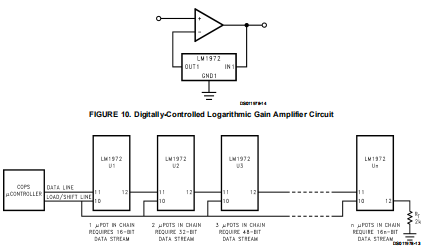

对数增益截肢器

μPot能够用于然而,如前所述,放大器的输出μPot需要看到高阻抗以保持其高性能和线性。再次加载输出将更改设备的衰减值。如所示图10,反馈回路中使用的μPot创建loga rithmic增益放大器。在这种配置中,衰减从表1中的级别,现在成为最大的增益级别可能增益值为78dB。对于大多数应用,78dB但是,由于在μPot的多功能性中,增益可以通过编程使系统的剪辑级别为从未获得。要记住的一点是在静音模式下,输入与输出断开连接。在这种配置将使放大器处于开环状态增益状态,从而导致严重的比较器动作。关心应该带着这个程序和设计电路类型。为了提供最佳性能,JFET输入应使用放大器。