ADF7021点击型号即可查看芯片规格书

解调器注意事项

2FSK前导码

2FSK的推荐前导码位模式是无直流模式(例如10101010…模式)。也可以使用具有较长游程长度约束(例如11001100…)的前导码模式,但会导致接收器中接收比特流的较长同步时间。前导码需要允许足够的比特用于接收机和CDR捕获的AGC处理。建议至少16个前导码位。当接收机使用内部AFC时,建议的最小前导码位数为48。

前导码头后面的其余字段不必使用无dc编码。对于这些字段,ADF7021可以容纳运行长度高达8位的编码方案,而不会降低性能。如果需要较长的运行长度,建议使用8B/10B或曼彻斯特编码等编码方案。

4FSK前导码和数据编码

4FSK的推荐前导码位模式是重复的00100010…位序列。这个2级重复的−3、+3、-3、+3符号序列是无dc的,并且最大化了接收机中4FSK前导码的符号定时性能和数据恢复。前导码的最小建议长度为32位(16个符号)。

构造4FSK分组的其余部分,以便通过使用数据置乱和/或以固定间隔(例如每8或16个符号之后)在发送的比特流中插入特定的dc平衡符号,发送的符号保持接近无dc特性。

2FSK相关解调器及频率误差

ADF7021有许多选项来对抗由于发射和接收晶体/TCXOs之间的不匹配而存在的频率误差。

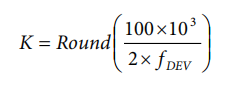

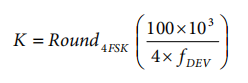

在禁用AFC的情况下,相关解调器能够容忍超过±0.4×fDEV范围的频率误差,其中fDEV是FSK频率偏差。对于较大的频率误差,通过调整K值,使相关器带宽倍增,可以将频率容限扩大到±0.8×fDEV。计算K为:

使用新的K值重新计算鉴别器的BW设置。以这种方式将相关器带宽加倍以提高频率误差容限通常会导致接收机灵敏度损失1db到2db。

相关解调器和低调制指数

2FSK中的调制指数定义为:

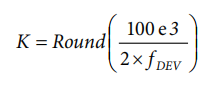

通过增加相关解调器的鉴频带宽,可以在低调制指数下最大限度地提高接收机的灵敏度性能。对于小于0.4的调制指数,建议通过如下计算K使相关器带宽加倍:

使用新的K值重新计算鉴别器。图26突出显示了在低调制指数下,通过将相关器带宽加倍,可以实现2FSK调制的改进灵敏度。

AFC操作

ADF7021还支持实时AFC环路,用于消除由于发射和接收晶体/TCXOs之间的不匹配而导致的频率误差。AFC环路使用线性鉴频块来估计频率误差。线性FSK鉴别器的输出经过滤波和平均,以消除FSK频率调制使用联合平均滤波器和包络检测器。在接收模式下,包络检测器的输出提供平均中频频率的估计。

ADF7021支持的AFC有两种方法:外部和内部。

外部AFC

这里,用户通过ADF7021串行端口读取频率信息,并将频率校正值应用于分数N合成器N分频器。

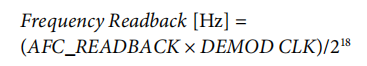

频率信息是通过读取16位有符号的AFC readback获得的,如readback Format部分所述,并且通过应用以下公式:

尽管AFC_READBACK值是一个有符号的数字,但在正常工作条件下,它是正的。在没有频率误差的情况下,频率回读值等于100 kHz的中频频率。

内部AFC

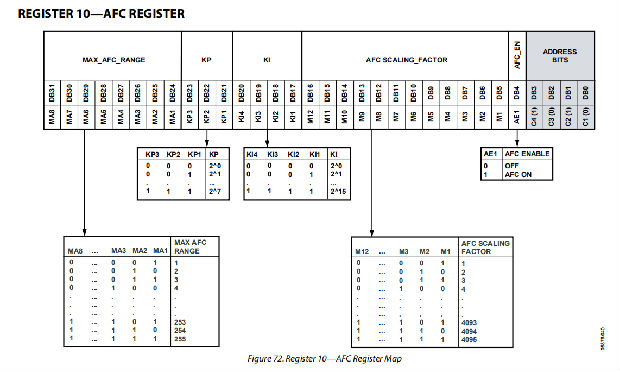

ADF7021支持实时、内部、自动频率控制回路。在这种模式下,内部控制回路自动监测频率误差,并使用内部比例积分(PI)控制回路调整合成器N分频器。

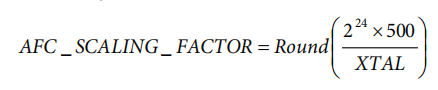

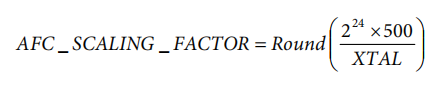

内部AFC控制回路参数控制在寄存器10中。通过将R10μDB4设置为1来激活内部AFC回路。还必须根据使用的晶体频率输入比例系数。这是在R10_DB[5:16]中设置的,可以使用:

最大AFC范围

AFC环路的最大频率校正范围可在ADF7021上编程。这是由R10_DB[24:31]设置的。最大AFC校正范围是AFC调谐范围的上下限之间的频率差。例如,如果最大AFC校正范围设置为10 kHz,则AFC可以在fLO±5 kHz范围内调整接收器LO。

然而,当RF_除以_2(R1_DB18)启用时,编程范围减半。通过将编程的最大AFC范围加倍来解释这一减半。

建议的最大AFC校正范围为≤1.5×IF滤波器带宽。如果最大频率校正范围设置为>1.5×If带宽,则If滤波器的衰减会降低AFC环路的灵敏度。

当启用AFC并且AFC校正范围接近IF滤波器带宽时,接收机的邻道抑制(ACR)性能会降低。然而,由于AFC校正范围是可编程的,用户可以权衡校正范围和ACR性能。

当使用内部或外部AFC消除AFC错误时,可以通过使用IF-BW比特(R4-DB[30:31])减少IF滤波器带宽来进一步提高接收机灵敏度。

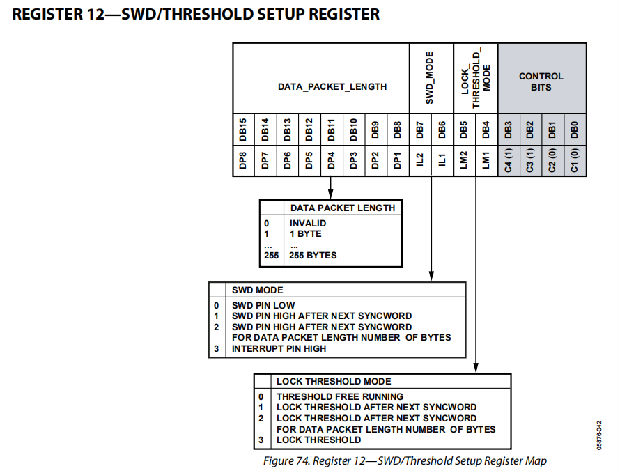

自动同步字检测(SWD)

ADF7021还支持同步或ID字段的自动检测。要激活此模式,同步(或ID)字必须预先编程到ADF7021中。在接收模式下,将该预编程字与接收的比特流进行比较。当识别出有效匹配时,ADF7021在下一个Rx时钟脉冲上断言外部SWD引脚。

此功能可用于提醒微处理器已检测到有效通道。它放宽了微处理器的计算要求,降低了总体功耗。

SWD信号还可用于通过在预先编程的字节数内保持高电平来对接收的分组进行帧化。数据包长度可以在R12_DB[8:15]中设置。

可以通过设置R12_DB[6:7]来配置SWD管脚状态。R11_DB[4:5]用于设置sync/ID字的长度,可以是12、16、20或24位长。建议值为24位,以最小化接收机中可能在恢复包的其余部分期间或当接收机输入端存在噪声/无信号时发生的假同步字检测。发射机必须先发送同步字节MSB,最后发送LSB,以确保接收机同步字节检测硬件正确对齐。

还可以编程一个误差容限参数,当多达3位的单词不正确时,该参数接受有效的匹配。

在R11_DB[6:7]中指定了误差容限值。

应用程序信息

中频滤波器带宽校准

在接收模式下每次通电时校准中频滤波器,以纠正由于过程变化导致的带宽和滤波器中心频率错误。一旦通过写入寄存器5启动自动校准,则无需外部干预。根据许多因素,例如滤波器带宽、接收信号带宽和温度变化,用户必须确定是执行粗略校准还是精细校准。有关校准设置的信息,请参阅IF Filter部分。

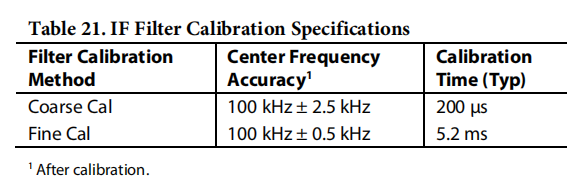

两种校准方法的性能如表21所示。

何时使用粗略校准

建议在每次接收模式通电时执行粗略校准。该校准通常需要200微秒。来自MUXOUT的滤波器校准完成信号可用于监测滤波器校准持续时间或发送校准结束信号。校准过程中不要接触ADF7021。

何时使用精细校准

在接收信号带宽非常接近IF滤波器带宽的情况下,建议在接收模式下每次单元通电时执行精细的滤波器校准。

如果:OBW+粗略校准变化>IF_FILTER_BW

其中:OBW是99%占用传输信号的带宽。粗略校准变化为2.5 kHz。

如果滤波器BW由R4_DB设置[30:31]。

来自MUXOUT的FILTER_CAL_COMPLETE信号(由R0_DB[29:31]设置)可用于监视滤波器校准持续时间或发出校准结束的信号。粗滤器校准在精滤器校准之前自动执行。

何时使用单次精细校准

在接收机在短时间内多次通电的应用中,只需要对初始接收机通电执行一次精细校准。

在初始粗略校准和精细校准之后,可以使用FILTER_CAL_read back result(参考FILTER Bandwidth calibration READBACK部分)通过串行接口读取精细校准的结果。在接收模式下的后续电源ups上,使用先前的精细滤波器校准结果手动调整滤波器。此手动调整使用IF_FILTER_adjust位(R5_DB[14:19])执行仅当接收模式下的连续不间断电源持续时间较短,在此期间温度变化不大(<15°C)时,才使用此方法。

如果过滤器随温度变化

校准时,滤波器中心频率可随温度变化而变化。如果ADF7021用于在相当长时间内保持接收模式的应用中,则用户必须考虑滤波器中心频率随温度的这种变化。这种变化通常为每10°C 0.7 kHz,这意味着如果在25°C下执行粗滤波器校准和精滤波器校准,则初始最大误差为±0.5 kHz,并且温度(-40°C和+85°C)下滤波器中心频率的最大可能变化为±4.5 kHz。总误差为±5 kHz。

如果接收信号占用的带宽远远小于If滤波器带宽,则滤波器中心频率在工作温度范围内的变化可能不是问题。或者,如果if滤波器带宽不足以容忍随温度的变化,则可以执行周期性滤波器校准,或者,可以使用片上温度传感器通过监测温度的变化来确定何时需要滤波器校准。

LNA/PA匹配

ADF7021在灵敏度、发射功率和电流消耗方面表现出最佳性能,前提是其射频输入和输出端口与天线阻抗适当匹配。对于成本敏感的应用,ADF7021配备有一个内部Rx/Tx开关,方便使用简单的组合无源PA/LNA匹配网络。或者,可以使用诸如ADG919的外部Rx/Tx开关,其产生稍有改进的接收器灵敏度和较低的发射器功耗。

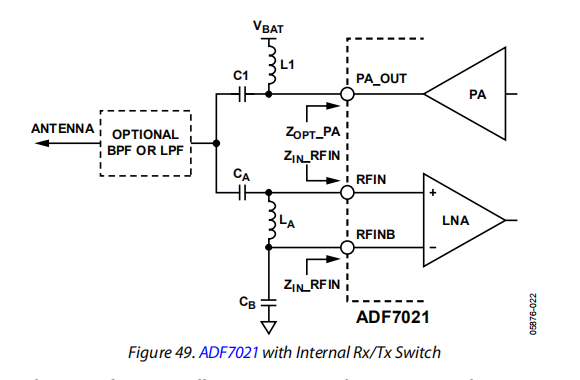

内部Rx/Tx开关

图49显示了ADF7021的配置,其中内部Rx/Tx开关与组合的LNA/PA匹配网络一起使用。这是EVALADF7021DB评估板上使用的配置。对于大多数应用来说,由内部Rx/Tx交换机引起的1db到2db的轻微性能下降是可以接受的,这允许用户利用此解决方案的成本节约潜力。组合匹配网络的设计必须考虑到Rx/Tx开关的状态,补偿网络在Tx和Rx路径中的电抗。

在达成可接受的折衷方案之前,该过程通常需要多次迭代。LNA/PA组合匹配网络的成功实现对于ADF7021来说,关键取决于PCB是否有精确的电子模型。在这种情况下,强烈建议使用合适的CAD软件包。为了避免这种努力,提供了一个小的形状因子参考设计的ADF7021,包括匹配和谐波滤波器组件。该设计是在一个2层印刷电路板,以尽量降低成本。

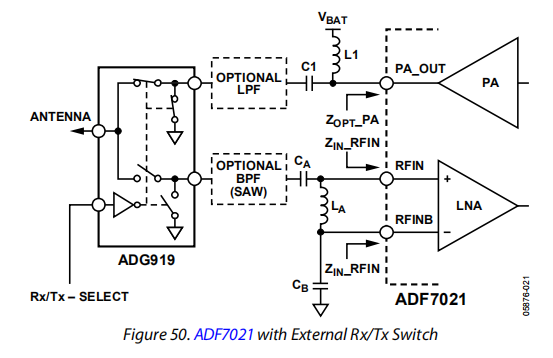

外部Rx/Tx开关

图50显示了使用外部Rx/Tx开关的配置。此配置允许独立优化发送和接收路径中的匹配和过滤网络。因此,它比使用内部Rx/Tx开关的配置更灵活,设计难度更小。PA通过电感L1偏置,而C1阻断直流电流。L1和C1一起形成匹配网络,将源阻抗转换为最佳PA负载阻抗ZOPT_PA。

ZOPT_-PA取决于各种因素,如所需的输出功率、频率范围、电源电压范围和温度范围。在an-764应用说明中,选择适当的ZOPT_-PA有助于将Tx电流消耗降至最低,该说明包含代表性条件的许多ZOPT_-PA值。但是,在某些条件下,建议通过负载拉力测量获得适当的ZOPT_PA值。

由于差分LNA输入,LNA匹配网络必须设计为提供单端到差分转换和复杂的共轭阻抗匹配。能够满足这些要求的最低组件数的网络是图50所示的配置,由两个电容器和一个电感组成。通过将匹配网络的排列理解为两个L型匹配网络,可以得到匹配网络的一阶实现。由于网络相对于地面的不对称性,必须在输入反射系数和LNA输入处的最大差分信号摆幅之间建立折衷。强烈建议使用适当的CAD软件进行优化。

根据天线配置,用户可能需要在PA输出处安装谐波滤波器,以满足适用政府法规的杂散发射要求。谐波滤波器可以以各种方式实现,例如离散LC-pi或T级滤波器。介电低通滤波器组件,例如村田制造有限公司生产的LFL18924MTC1A052(用于915MHz和868MHz频段的工作),是离散设计的一个有吸引力的替代品。通过在接收路径中添加带通滤波器,可以提高ADF7021对强带外干扰的抗扰性。除了分立设计外,由Murata制造有限公司生产的SAFCH869MAM0T00、SAFCH915MAL0N00、DCFB2869MLEJAA-TT1或DCFB3915MLDJAA-TT1等SAW或介电滤波器组件都非常适合这一用途。或者,如表14所述,可以通过选择增强的线性模式之一来提高ADF7021的阻塞性能。

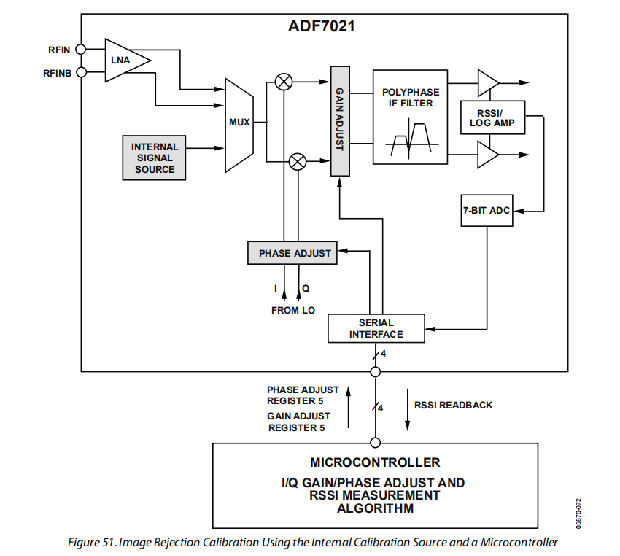

图像抑制校准

ADF7021中的图像通道低于所需信号200 kHz。多相滤波器以不对称的频率响应来抑制该图像。接收机的图像抑制性能取决于I和Q信号在幅度上的匹配程度,以及它们之间的正交匹配程度(即它们之间的距离有多接近90°)。未经校准的图像抑制性能约为29分贝(450兆赫)。但是,通过找到最佳的I/Q增益和相位调整设置,可以将此性能提高20 dB。

使用内部射频源校准

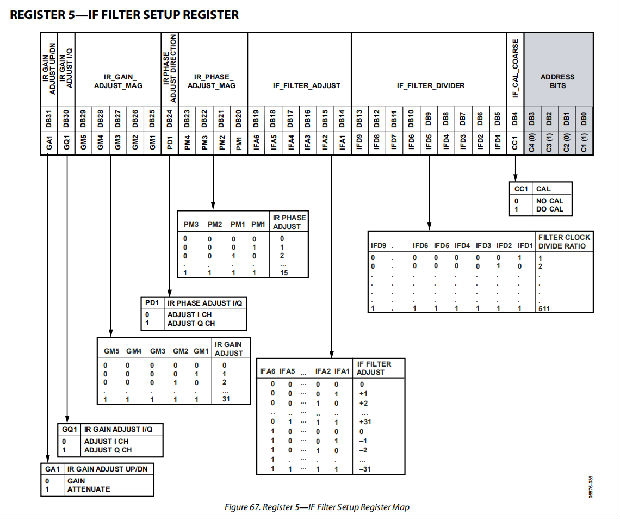

在LNA断电的情况下,芯片上产生的低电平射频音调被应用到混频器输入端。LO被调整以使音调在图像频率处下降,在该图像频率处它被IF滤波器的图像抑制衰减。然后使用RSSI readback测量该音调的功率级。调整I/Q增益和相位调整dac(R5_DB[20:31]),并重新测量RSSI。重复此过程,直到找到提供最低RSSI回读电平的增益和相位调整的最佳值,从而最大化接收机的图像抑制性能。

使用内部射频源,可用于图像校准的射频频率是可编程的,并且是参考频率的奇数倍。

使用外部射频源校准

红外校准也可以使用外部射频源来实现。红外校准程序与用于内部射频源的程序相同,只是在LNA输入端应用了射频音调。

校准程序和设置

模拟设备公司提供的红外校准算法基于一种低复杂度的二维优化算法,可以在外部微处理器或微控制器中实现。

要启用内部射频源,请将红外校准源驱动电平位(R6_DB[28:29])设置为最大电平。将LNA设置为其最小增益设置,如果使用内部电源,则禁用AGC。或者,可以使用外部射频源。

相位调整的幅度通过使用IR_phase_uadjust_umag位(R5_DB[20:23])来设置。此校正可应用于I信道或Q信道,具体取决于IR_PHASE_ADJUST_DIRECTION位(R5_DB24)的值。

I/Q增益的大小由IR_gain_uadjust_MAG比特(R5_DB[25:29])调整。此校正可应用于I或Q信道,具体取决于IR_GAIN_ADJUST_I/Q位(R5_DB30)的值,而IR_GAIN_ADJUST_UP/DN bit(R5_DB31)设置增益调整定义增益或衰减调整。

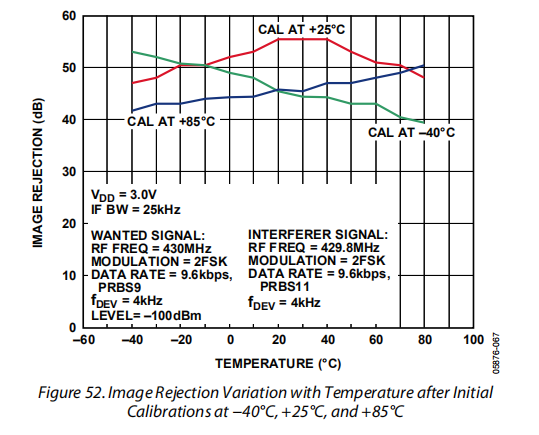

校准结果在ADF7021电源电压变化时有效。然而,温度也有一些变化。在-40℃、+25℃和+85℃下进行初始校准后,图像抑制随温度变化的典型曲线如图52所示。ADF7021上的内部温度传感器可用于确定是否需要新的红外校准。

分组结构与编码

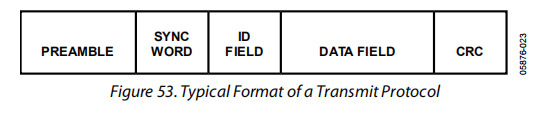

与ADF7021一起使用的建议的包结构如图53所示。

有关各种调制方案所需的前导码结构和长度的信息,请参阅接收器设置部分。

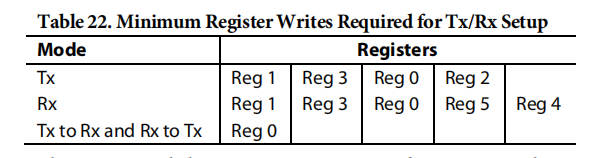

初次通电后编程

表22列出了CE升高后,在Tx或Rx模式下设置ADF7021所需的最小写入次数。还可以编写额外的寄存器以使设备适合特定的应用,例如设置同步字节检测或启用AFC。当从Tx转到Rx或反之时,用户需要切换Tx/Rx位并只写入寄存器0以将LO改变100 kHz。

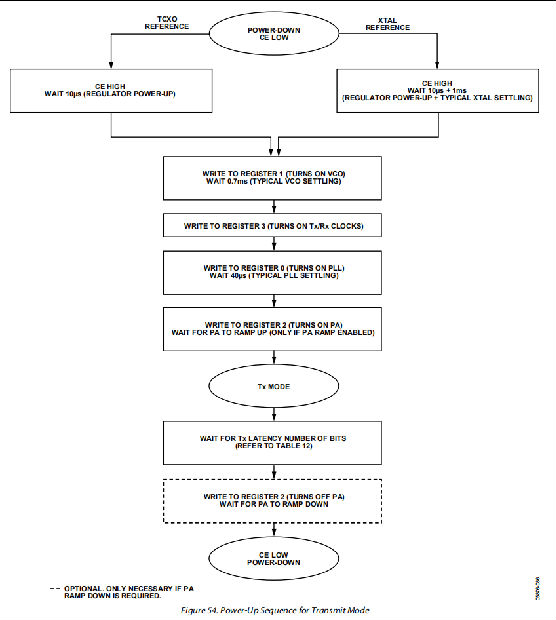

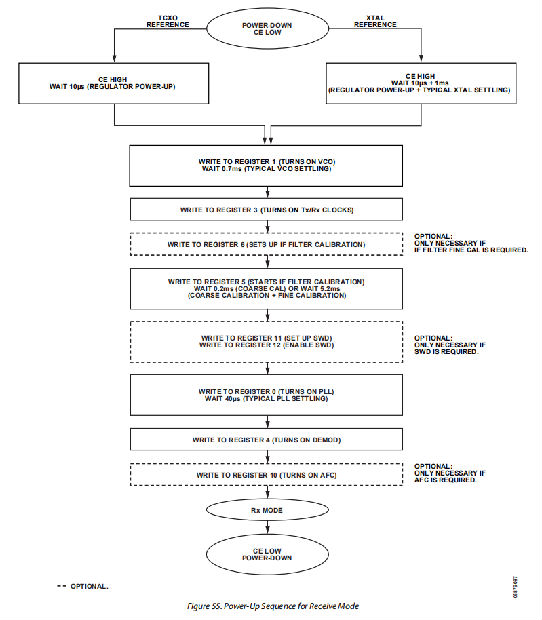

发送和接收的推荐编程序列分别如图54和图55所示。这些图显示了TCXO和XTAL引用的通电例程的差异。

应用电路

ADF7021只需要很少的外部组件就可以运行。图56显示了推荐的应用电路。请注意,为了清楚起见,省略了电源去耦和调节器电容器。

有关推荐的组件值,请参阅ADF7021评估板数据表和AN-915应用说明,可从ADF7021产品页访问。严格遵循参考设计方案,以确保窄带应用的最佳性能。

串行接口

串行接口允许用户使用三线接口(SCLK、SDATA和SLE)编程16/32位寄存器。它由一个电平移位器、32位移位寄存器和16个锁存器组成。信号必须与CMOS兼容。串行接口由调节器供电,因此当CE低时处于非活动状态。

数据首先在每个时钟(SCLK)的上升沿上进入寄存器MSB。数据被传输到SLE上升沿上的16个锁存器中的一个。目标锁存由四个控制位(C4到C1)的值决定;这四个控制位是最下面的4个lsb,DB3到DB0,如图2所示。数据也可以在SREAD pin上读取。

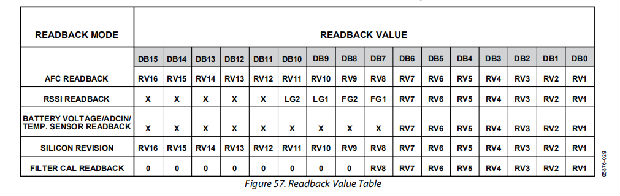

回读格式

通过将有效的控制字写入回读寄存器并启用回读位(R7_DB8=1)来启动回读操作。回读可以在控制字被SLE信号锁定后开始。读取数据时,SLE必须保持在高位。SCLK管脚上的每个活动边缘都会在SREAD管脚上连续计时回读字,如图57所示,首先从MSB开始。必须忽略闩锁操作后第一个时钟周期出现的数据。在16回读位之后需要额外的时钟周期,以将SREAD pin返回到三态。因此,每次回读需要18个总时钟周期。在18个时钟周期后,将SLE调低。

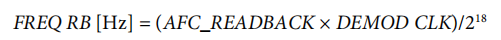

AFC回读

AFC回读仅在线性或相关解调器激活的FSK信号接收期间有效。AFC readback值被格式化为包含位RV1到位RV16的有符号16位整数,并根据以下公式缩放:

在没有频率误差的情况下,FREQ RB等于100 kHz的中频频率。注意,为了使AFC回读产生有效的结果,下转换的输入信号不能落在模拟IF滤波器的带宽之外。在低输入信号电平下,通过平均可以改善回读值的变化。

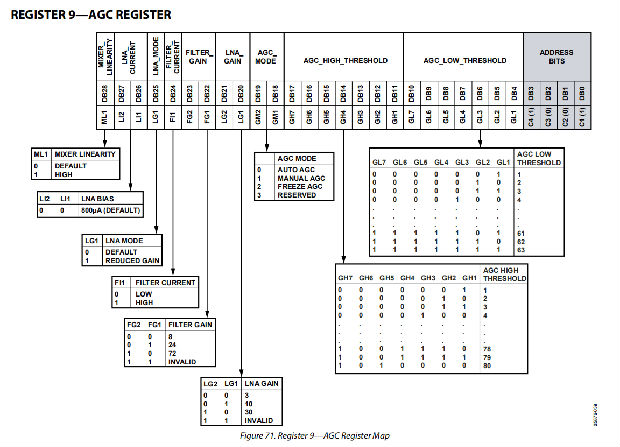

RSSI回读

回读字的格式如图57所示。它包括RSSI级信息(位RV1到位RV7)、当前滤波器增益(FG1,FG2)和当前LNA增益(LG1,LG2)设置。滤波器和LNA增益根据寄存器9-AGC寄存器部分中的定义进行编码。对于低于-100 dBm的信号电平,平均测量的RSSI值可提高精度。输入功率可以根据RSSI/AGC部分中概述的RSSI回读值来计算。

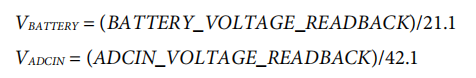

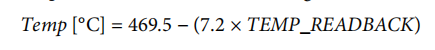

蓄电池电压/ADCIN/温度传感器读数

在针脚VDD4处测量蓄电池电压。回读信息包含在位RV1到位RV7中。这也适用于ADCIN引脚和温度传感器的电压读数。从回读信息中,可以使用:

温度可以用:

硅修正回读字在不设置任何其他寄存器的情况下有效。硅修正字用四个四重奏以BCD格式编码。产品代码(PC)由三个从位RV5扩展到位RV16的四分位编码。修订码(RC)由一个从位RV1扩展到位RV4的四重奏编码。ADF7021的产品代码读回为PC=0x210。当前修订代码读取为RC=0x4。

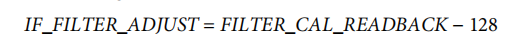

滤波器带宽校准回读

滤波器校准回读字包含在位RV1到位RV8中。此回读可用于手动调整滤波器,因此在某些情况下无需进行中频滤波器校准。手动调整值由R5_DB[14:19]编程。要根据过滤器校准读数计算手动调整,请使用以下公式:

如寄存器5-IF Filter Setup Register部分所述,将结果编程到R5_DB[14:19]。

与微控制器/DSP的接口

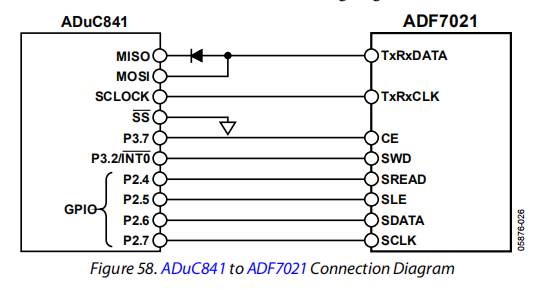

标准发送/接收数据接口

微控制器的标准发送/接收信号和配置接口如图58所示。在传输模式下,ADF7021在TxRxCLK引脚上提供数据时钟,TxRxDATA引脚用作数据输入。传输数据被记录到TxRxCLK上升沿上的ADF7021中。

在接收模式下,ADF7021在TxRxCLK引脚上提供同步数据时钟。接收数据在TxRxDATA引脚上可用。使用TxRxCLK的上升沿将接收到的数据计时到微控制器中。有关时序图,请参阅图4和图5。

在4FSK传输模式下,传输符号的MSB从TxRxCLK管脚进入数据时钟第一上升沿上的ADF7021。在4FSK接收模式下,第一个有效载荷符号的MSB在SWD之后的数据时钟的第一个负边缘上打卡,并且必须在下一个上升边缘上打卡到微控制器中。有关时序图,请参阅图6和图7。

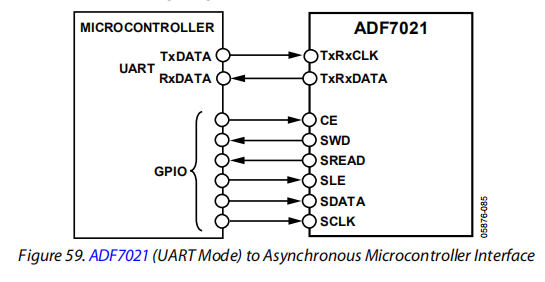

通用异步收发器模式

在UART模式下,TxRxCLK引脚被配置为在传输模式下输入传输数据。在接收模式下,接收数据在TxRxDATA引脚上可用,从而提供异步数据接口。UART模式只能与过采样2FSK一起使用。图59显示了使用ADF7021的UART模式与微控制器的可能接口。要启用此UART接口模式,请将R0_DB28设为高。图8和图9显示了UART模式的相关时序图。

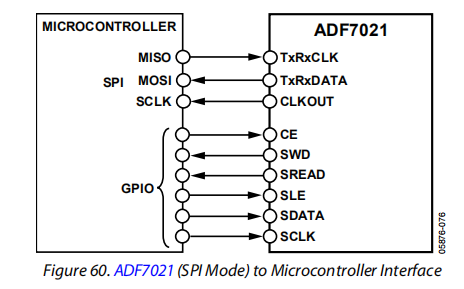

SPI模式

在SPI模式下,TxRxCLK引脚被配置为在传输模式下输入传输数据。在接收模式下,接收数据在TxRxDATA引脚上可用。CLKOUT管脚提供发送和接收模式下的数据时钟。在传输模式下,数据在时钟正边缘的ADF7021中计时。在接收模式下,TxRxDATA数据引脚由单片机在CLKOUT的正边缘进行采样。

要启用SPI接口模式,请将R0_DB28设置为高,并将R15_DB[17:19]设置为0x7。图8和图9显示了SPI模式的相关时序图,而图60显示了使用ADF7021的SPI模式的微控制器的推荐接口。

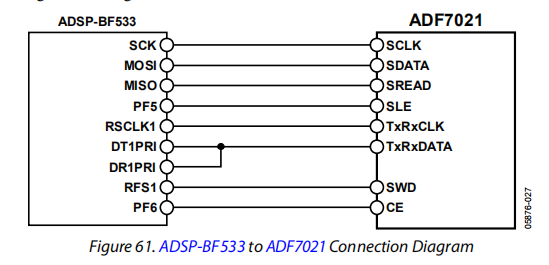

ADSP-BF533接口

图61给出了与Blackfin®ADSP-BF533接口的建议方法。

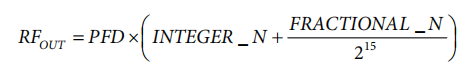

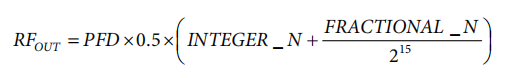

射频输出频率的计算方法如下:

对于直接输出

对于所选RF_除以_2(DB18)

在UART/SPI模式下,TxRxCLK引脚用于输入Tx数据。Rx数据在TxRxDATA引脚上可用。

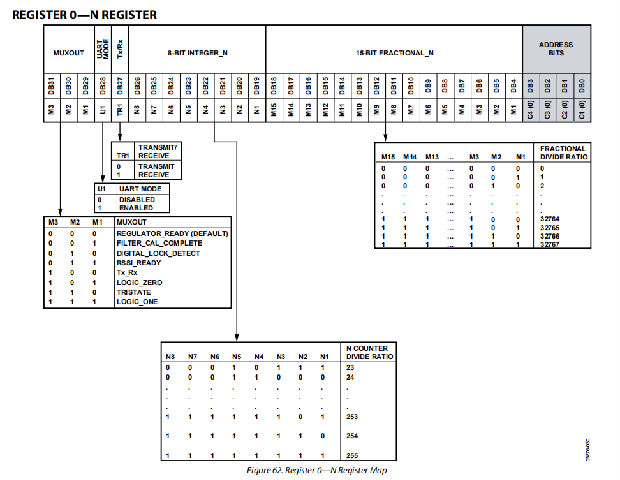

在图62中的MUXOUT图中,FILTER_CAL_COMPLETE指示粗或粗加细(如果过滤器校准已完成)。数字锁定检测指示PLL何时锁定。RSSI_READY表示RSSI信号已经稳定,可以执行RSSI回读。Tx_Rx给出该寄存器中的DB27的状态,该状态可用于控制外部Tx/Rx开关。

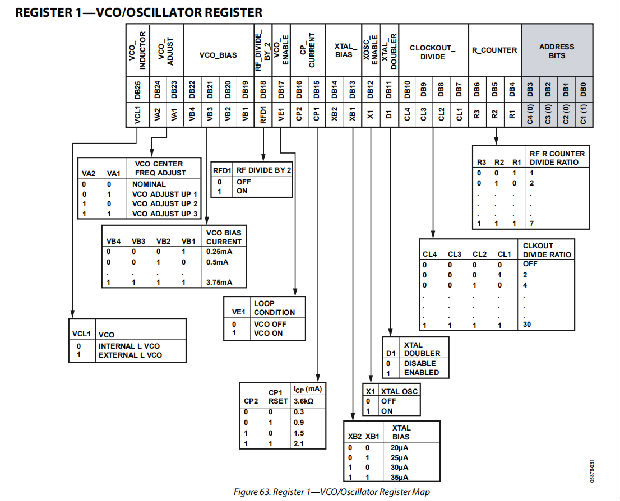

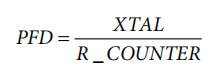

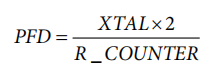

R_计数器与XTAL_双倍关系表示如下:

如果XTAL_DOUBLER=0,

如果XTAL_DOUBLER=1,

时钟除法是XTAL的向下和反向除法,可在引脚36(CLKOUT)上使用。

当使用外部晶体时,将XOSC_ENABLE设置为high。如果使用带有CMOS电平输出的外部振荡器(如TCXO)进入引脚OSC2,则将XOSC U ENABLE设置为low。如果使用具有0.8 V p-p削波正弦波输出到管脚OSC1的外部振荡器,则将XOSC U ENABLE设置为high。

根据表9设置VCO_偏置位。

VCO_调整位调整VCO操作带的中心。每个位通常将VCO频带向上调整射频工作频率的1%(如果启用了射频除以2,则为0.5%)。

将VCO_电感器设置为外部允许使用外部电感器VCO,它提供80赫兹到650兆赫的射频工作频率。如果内部电感VCO用于操作,则将该位设置为低。

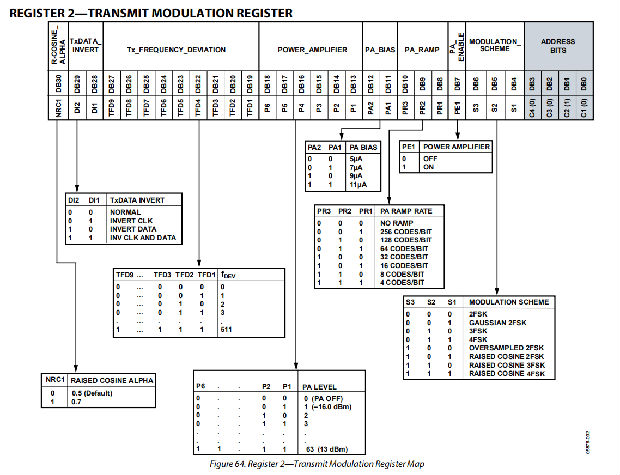

2FSK/3FSK/4FSK频率偏差表示如下:

直接输出

启用RF_除以_2(R1_DB18)

其中Tx_FREQUENCY_DEVIATION由DB[19:27]设置,PFD是PFD频率。

在4FSK的情况下,在±3×频率偏差和±1×偏差处存在音调。功率放大器(PA)以编程速率(R2_DB[8:10])缓慢上升,直到达到其编程电平DB[13:18]。如果PA是由PA_ENABLE位(DB7)启用/禁用的,则它会上下倾斜。如果由Tx/Rx位(R0_DB27)启用/禁用,则它会加速并硬关闭。

R-COSINE_ALPHA将升余弦数据滤波器的滚动因子(ALPHA)设置为0.5或0.7。默认情况下,alpha设置为0.5,但可以增加提升的余弦滤波器带宽通过使用0.7的alpha来提供不那么激进的数据过滤。

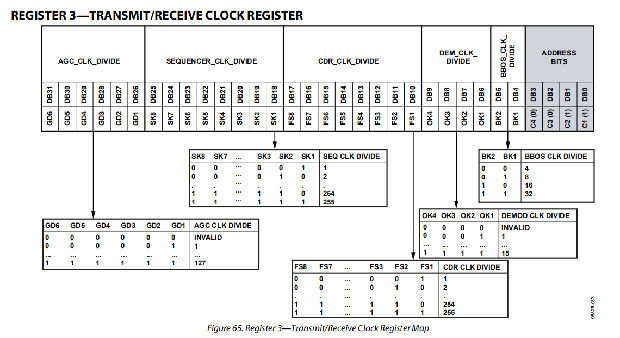

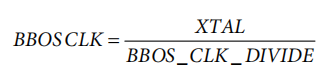

基带偏移时钟频率(BBOS CLK)必须大于1 MHz且小于2 MHz,其中

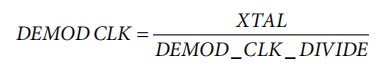

设置解调器时钟(DEMOD CLK),使2 MHz≤DEMOD CLK≤15 MHz,其中

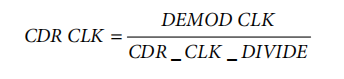

对于2FSK/3FSK,数据/时钟恢复频率(CDR CLK)需要在(32×数据速率)的2%以内。对于4FSK,CDR CLK需要在(32×符号速率)的2%以内。

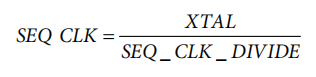

定序器时钟(SEQ CLK)将时钟提供给数字接收块。建议尽可能接近100 kHz。

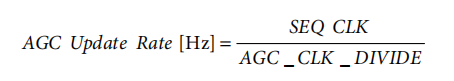

每个AGC步骤允许的结算时间由AGC更新率决定。建议设置为接近10 kHz。

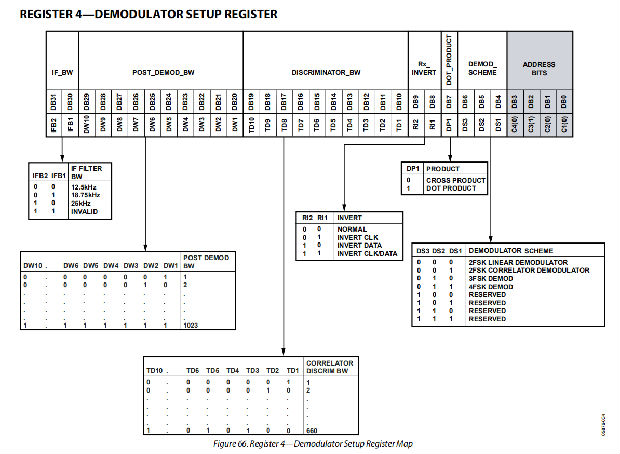

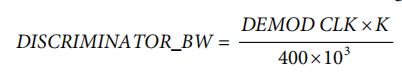

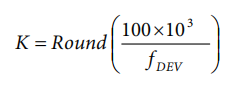

要求解鉴别器,请使用以下公式:

其中最大值=660。对于2FSK,

对于3FSK,

对于4FSK,

其中:舍入到最接近的整数。

Round4FSK四舍五入到下列整数中的最接近者:32,31、28、27、24、23、20、19、16、15、12、11、8、7、4、3。

fDEV是发射频率偏差,单位为赫兹。对于4FSK,fDEV是用于±1符号的频率偏差(即内部频率偏差)。

Rx_反转(DB[8:9])和DOT_积(DB7)需要按照表17和表18中的概述进行设置。

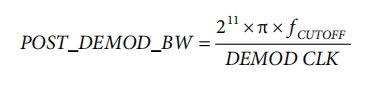

其中,后解调滤波器的截止频率(f)通常为2FSK中的数据速率的0.75倍。汇总切断后解调到最接近的整数值。在3FSK中,将其设置为等于数据速率。在4FSK中,将其设置为1.6×符号速率。

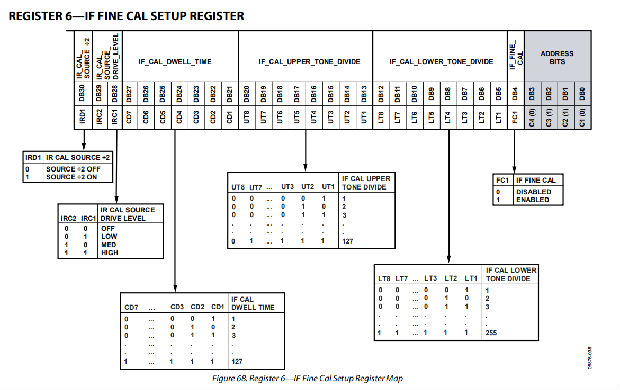

当设置了IF-CAL-u粗比特(DB4)时,执行粗IF滤波器校准。如果先前设置了If_FINE_CAL位(R6_DB4),则在粗略校准之后自动执行精细If滤波器校准。

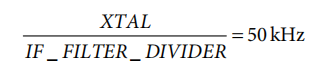

设置IF_FILTER_DIVIDER以便:

IF_FILTER_ADJUST允许将IF精细滤波器校准结果直接编程到随后的接收机电源上,从而在某些情况下节省了重新进行精细滤波器校准的需要。

DB[20:31]用于图像抑制校准。有关如何编程这些参数的详细信息,请参阅图像抑制校准部分。

通过启用IF_fine_CAL位(R6_DB4)来设置精细IF滤波器校准。只有当寄存器5被写入并且R5_DB4被设置时,才执行精细校准。

按如下方式设置精滤器校准期间使用的中频上下音调:

IF音调校准时间是在IF校准音调上花费的时间量。它取决于定序器时钟。

对于最佳实践,建议将IF音调校准时间至少设置为500μs。

精细中频滤波器校准的总时间是中频音校准时间×10。

DB[28:30]控制用于图像抑制(IR)校准的内部源。红外校准源驱动位(DB[28:29])设置源的驱动强度,而红外校准源驱动位(DB30)允许内部信号源的频率除以2。

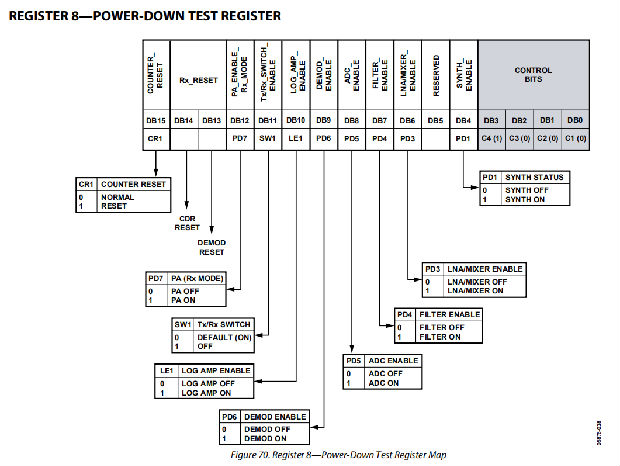

只有在Rx模式下,测量的RSSI值的回读才有效。在Rx模式下,电池电压、温度传感器或外部引脚电压的回读无效。

要在Tx模式下读取电池电压、温度传感器或外部引脚处的电压,请首先使用R8_DB8为ADC通电,因为在Tx模式下,默认情况下会将其关闭以节省电源。

对于AFC readback,使用以下公式(请参阅readback Format部分):

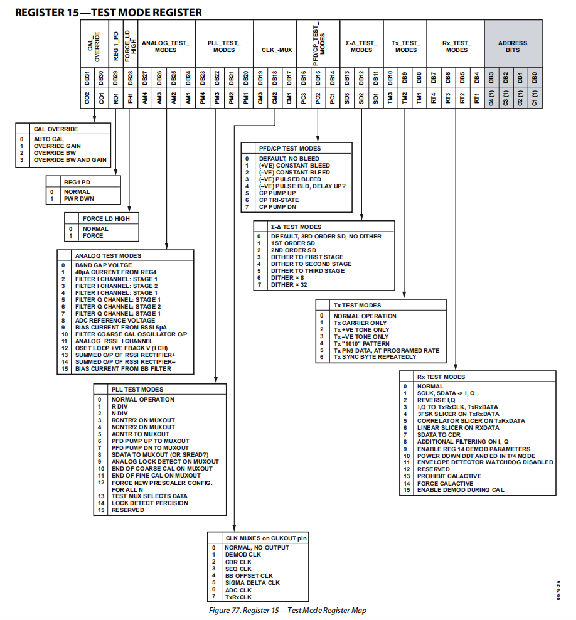

在正常工作条件下,无需写入该寄存器。

对于组合的LNA/PA匹配网络,始终将DB11设置为0,这将启用内部Tx/Rx开关。这是开机默认条件。

在接收模式下,自动增益控制在通电时默认设置为自动增益控制。默认阈值是AGC_LOW_THRESHOLD=30,AGC_HIGH_阈值=70。见RSSI/AGC部分了解详细信息。仅当需要AGC设置(默认设置除外)时,才需要对该寄存器进行编程。

AGC高和低设置之间的间隔必须大于30,以确保正确操作。

只有当LNA U模式(DB25)设置为0时,LNA增益30才可用。

AFC_标度因子可以表示为:

KI和KP的设置影响AFC的沉降时间和AFC精度。每个参数的允许范围是碘化钾>6和KP<7,

最佳AFC性能的推荐设置是KI=11和KP=4。

为了在AFC稳定时间和AFC精度之间进行权衡,可以从建议的设置(保持在允许范围内)调整KI和KP参数,以便:AFC校正范围=最大AFC范围×500赫兹

当RF_除以_2(R1_DB18)启用时,编程的AFC校正范围减半。用户通过将编程的MAX_AFC_RANGE值加倍来解释此减半。例如,对于所需的±5 kHz的校正范围,在启用RF_除以_2的情况下,将MAX_AFC_range(R10_DB[24:31])设置为20。

在AFC拉入范围内但在IF滤波器带宽之外的信号被IF滤波器衰减。结果,信号可以低于接收器的敏感点,因此,AFC无法检测到。

锁定阈值锁定信封检测器的阈值。这具有在线性解调中锁定切片器和在使用线性或相关解调时锁定AFC和AGC环路的效果。

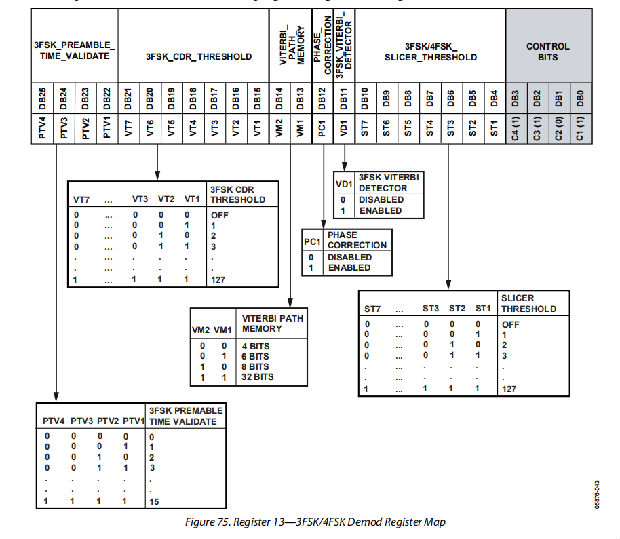

寄存器13-3FSK/4FSK解调寄存器

有关编程这些设置的信息,请参阅接收器设置部分。

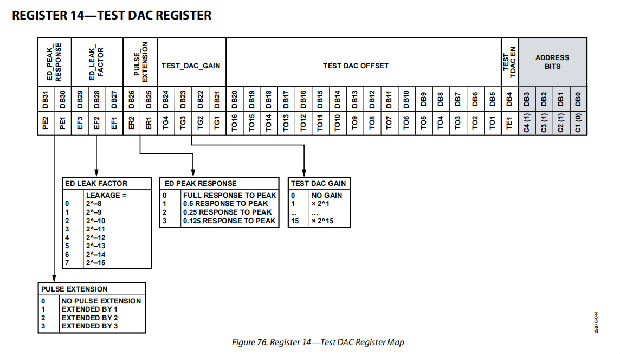

解调器调谐参数、脉冲扩展、ED_泄漏因子和ED_峰值响应只能通过将R15_DB[4:7]设置为0x9来启用。

用测试DAC实现模拟调频解调及信噪比测量

测试DAC允许后解调器滤除线性解调器和相关解调器,以便从外部观看。测试DAC还接收16位滤波器输出,并使用二阶误差反馈∑-Δ转换器将其转换为高频单位输出。可在SWD引脚上查看输出。该信号经过适当过滤后,可用于执行以下操作:

*监测FSK后解调滤波器输出的信号。这样就可以测量解调器的输出信噪比。还可以构造接收比特流的眼图来测量接收信号的质量。

*提供模拟调频解调。

当相关器和滤波器由DEMOD CLK定时时,CDR CLK对测试DAC进行计时。注意,尽管测试DAC在常规用户模式下工作,但是当CDR_CLK增加到或高于DEMOD CLK的频率时,可以获得最佳性能。当存在这种情况时,CDR块不起作用。

编程寄存器14启用测试DAC。线性和相关/解调器输出都可以复用到DAC中。

寄存器14允许从信号中移除固定偏移项(以移除ddt情况中的IF分量)。它还有一个信号增益项,允许使用DAC的最大动态范围。

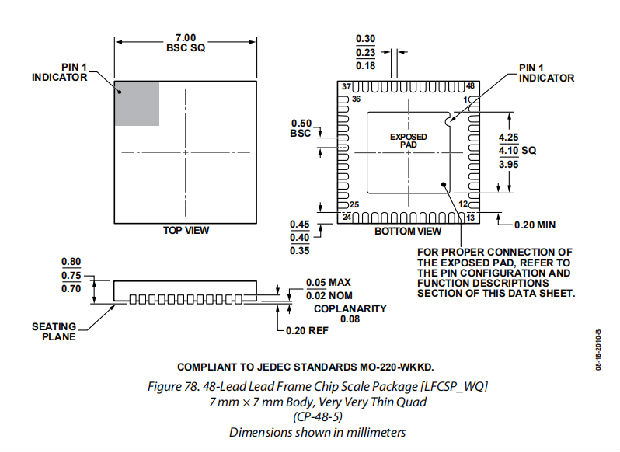

外形尺寸

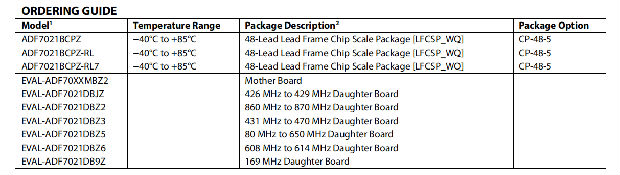

注意:Z=符合RoHS的零件。所有子板的最大订购量为3。EVAL-ADF70XXMBZ2是子板所需的母板。

[1]、特定RF频率下的最大可用PFD受最小N除以值的限制。

[2]、在VCO调谐电压为1V时测得的VCO增益。VCO增益在VCO调谐范围内变化。软件包adisimpl™ 可以用来模拟这种变化。

[3]、该值可用于计算任何工作频率的带内相位噪声。使用以下公式计算PA输出处的带内相位噪声性能:-203+10对数(fPFD)+20对数。

[4]、由设计保证。样品测试以确保符合性。

[5]、TCXO、VCXO或OCXO可以用作外部振荡器。

[6]、晶体启动时间是从芯片启用(CE)被断言到CLKOUT引脚上正确时钟频率的时间。7有关使用外部振荡器的详细信息,请参阅参考输入部分。