EL9115点击型号即可查看芯片规格书

特征

•总延迟62ns

•2ns延迟步进增量

•在±5V电源下运行

•高达122MHz带宽

•低功耗

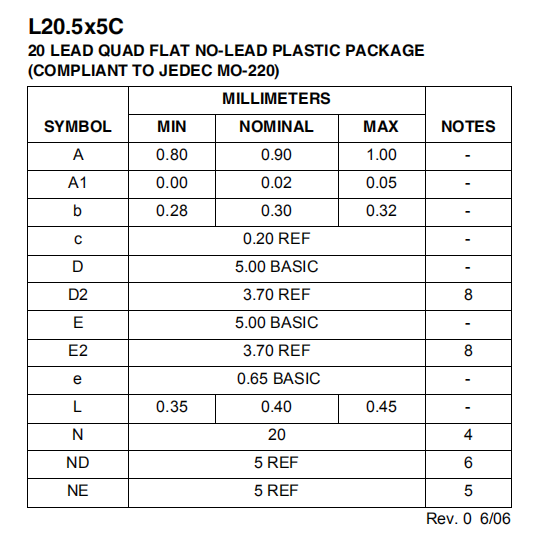

•20 Ld QFN(5毫米x 5毫米)包装

•无铅(符合RoHS)

应用

•RGB的倾斜控制

•模拟波束形成

说明

三重模拟视频延迟线

EL9115是一个三重模拟延迟线,允许任何三个信号之间的倾斜补偿。该部分非常适合补偿典型的5类电缆(每对电缆上的电气长度不同)引起的倾斜。

EL9115可以在每个信道上以2ns到62ns总延迟的步骤进行编程。

笔记:

1、 为磁带和卷盘添加“-T*”后缀。有关卷盘规格的详细信息,请参阅技术简介TB347。

2、 这些Intersil无铅塑料包装产品采用特殊的无铅材料组、模塑料/模具连接材料和100%哑光镀锡板加退火(e3端接处理,符合RoHS标准,并与SnPb和无铅焊接操作兼容)。Intersil无铅产品在满足或满足无铅峰值回流焊温度时被归类为MSL超过IPC/JEDEC J STD-020的无铅要求。

3、 有关湿度灵敏度水平(MSL),请参见EL9115的设备信息页。有关MSL的更多信息,请参阅技术简介TB363。

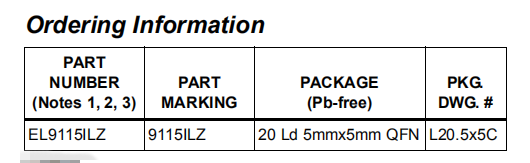

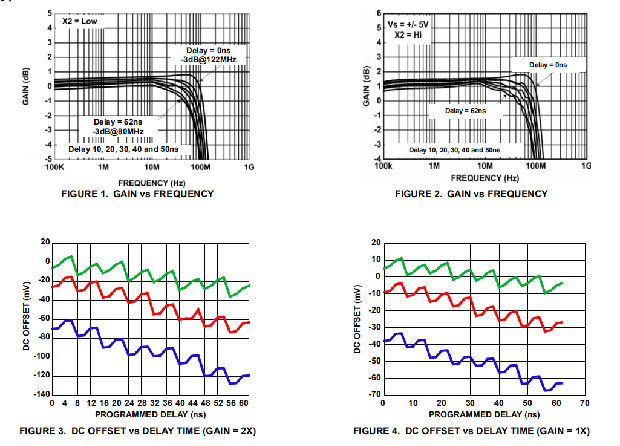

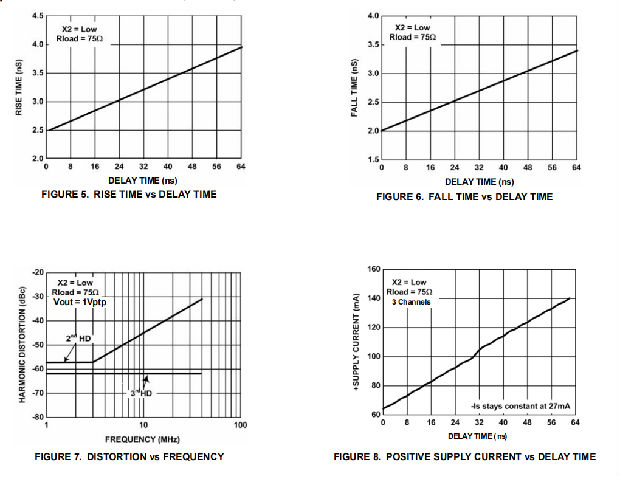

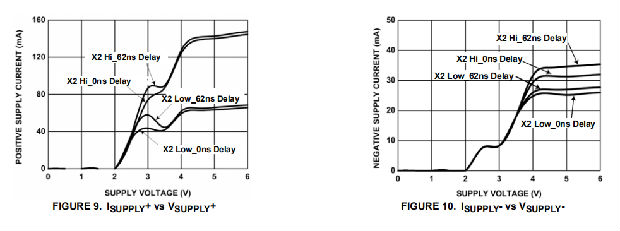

典型性能曲线

应用程序信息

EL9115是一个三重模拟延迟线接收器,允许任何三个高频信号之间的倾斜补偿。这部分补偿了典型的5类电缆引入的时间偏差,每对电缆具有不同的电长度。EL9115可以通过SPI接口以2ns到62ns的总延迟在每个信道上独立编程,同时达到80MHz以上的带宽。

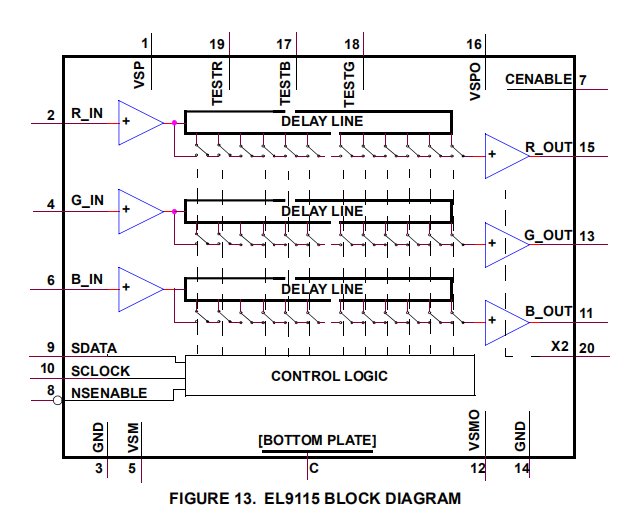

图13显示了EL9115框图。三个模拟输入是接地参考单端信号。接收到信号后,通过将滤波器块切换到信号路径中引入延迟。每个滤波器组是一个引入2ns延迟的全通滤波器。除了延时,每个滤波器组还引入了一些低通滤波。结果,信号路径的带宽从0ns延迟设置时的120MHz减少到最大延迟设置时的80MHz,如第4页“典型性能曲线”图1所示。

除了延迟,信号路径中的额外放大器还引入偏移电压。对于X2高设置,输出偏移电压可移动100毫伏,对于X2低设置,输出偏移电压可移动50毫伏。

在操作中,最好分配延迟最大的信号0ns延迟,然后增加其他信道上的延迟以使它们成行。这将导致最低的功率和失真解决方案来平衡延迟。

功耗

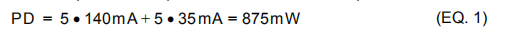

随着延迟设置的增加,额外的滤波器块打开并插入到信号路径中。每通道延迟2ns,VSP电流增加0.9mA,VSM变化不明显。在极端设置下,正电源电流可达140mA,负电源电流可达35mA。在±5V电源下工作,总功耗如式1所示:

可计算长期可靠运行所需的θJA。这是通过方程式2完成的:

其中:TJ最高结温(+135°C);TA是最高环境温度(+85°C)。

在适当布局的PCB热沉铜区,20ld封装可以达到40°C/WθJA热阻。为了分散热量,底部散热片必须焊接到PCB上。热量通过热分配器流向电路板铜,然后扩散并对流到空气中。因此,PCB铜平面成为散热器(参见TB389)。这被证明是一种非常有效的技术。一个单独的应用说明,其中详细说明了20 Ld QFN电路板的设计考虑,是可用的。

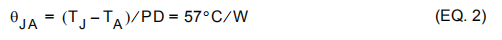

串行总线操作

在NSEnable变低后的第一个负时钟边缘,从数据中读取输入(图14)。此数据级别应为0(写入寄存器);不支持读取。读取后续负边缘上的下两个数据位,并将其解释为要填充的寄存器。Reg 01=R,02=G,03=B,00测试使用。读取接下来的五位数据并将它们发送到寄存器。在每个8位块的末尾,任何进一步的数据都被视为新词。输入的数据在进入时直接转移到最终寄存器。上电时所有寄存器的初始值为0。用户有责任发送8个时钟周期的完整模式,即使第一位设置为1。如果发送的数据少于8位,则只能通过寄存器部分移位。8的模式从NS enable变低开始,因此在NS enable突发中对每个单词进行帧化是一个很好的实践。

测试接脚

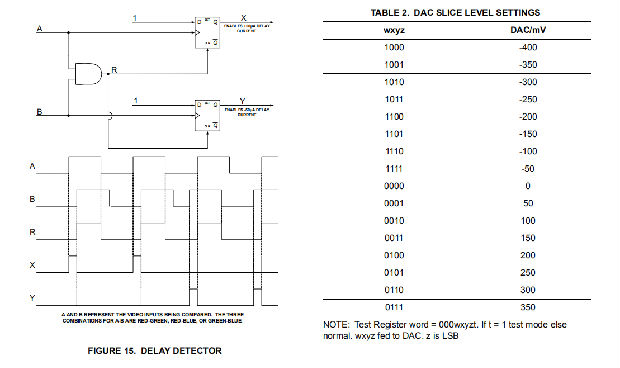

提供三个测试销(测试R、测试G、测试B)。在正常操作期间,测试引脚在输入之间重叠的时间内输出脉冲电流,如图15所示:

测试脉冲=红色输出(A),绿色输出(B)

测试脉冲=绿色输出,蓝色输出

测试脉冲=蓝色输出,红色输出

平均电流可以直接测量两条边之间的延迟。当A先于B时,电流脉冲为+50μA,输出电压上升。当B在A之前时,脉冲为-50μA。

为了使逻辑正常工作,A和B必须有一段时间的重叠,而它们是高的(不能测量比脉冲宽度长的延迟)。

通过比较视频信号与由内部DAC设置的切片级别,从视频输入中导出信号A和B。这使得可以从编码在视频顶部的类同步信号的上升沿或从专用设置信号测量延迟。输出可用于设置接收信号的正确延迟。

DAC电平由指向测试寄存器(00)的位1到4通过串行输入设置。表2显示了DAC片级位的设置。

测试模式

对于正常操作,测试寄存器的位0设置为0。如果设置为1,则设备处于测试模式。在测试模式下,DAC电压被引导到绿色通道输出,而对于红色和蓝色通道,测试输出现在是通过观察通道输入和输出之间的延迟而产生的电流脉冲。因此,它们能够测量延迟。

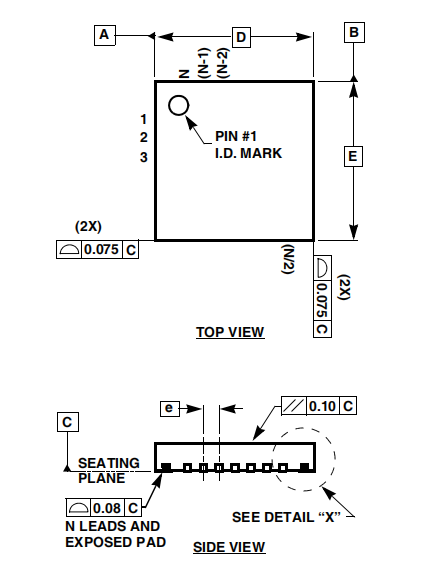

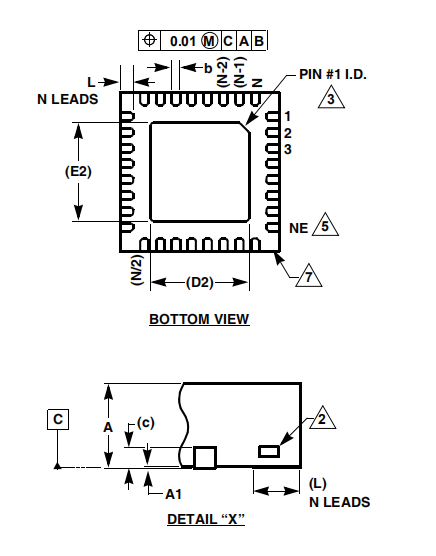

四平无铅塑料包装(QFN)

笔记:

1、 尺寸和公差符合ASME Y14.5M-1994。

2、 显示的Tiebar视图是一个非功能特性。

3、 底侧销1内径是如图所示的模垫倒角。

4、 N是设备上的终端总数。

5、 NE是封装“E”侧(或Y方向)的端子数。

6、 ND是封装“D”侧(或X方向)的端子数。ND=(N/2)-NE。

7、 端子的内端可以是正方形或圆形,半径(b/2)如图所示。

8、 如果列出了两个值,则可以使用多个公开的焊盘选项。请参阅特定于设备的数据表。

9、 MDP0046中的10个包之一。