CS5106点击型号即可查看芯片规格书

特征

*可编程固定频率

*可编程FET非重叠

*使能导线

*12V固定辅助电源控制

*欠压和过压停机

*带定时器的输出欠压保护

*主从时钟同步能力

*同步频率范围检测

*80ns脉冲宽度调制传播延迟

*20毫安5伏参考输出

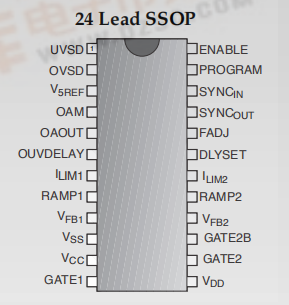

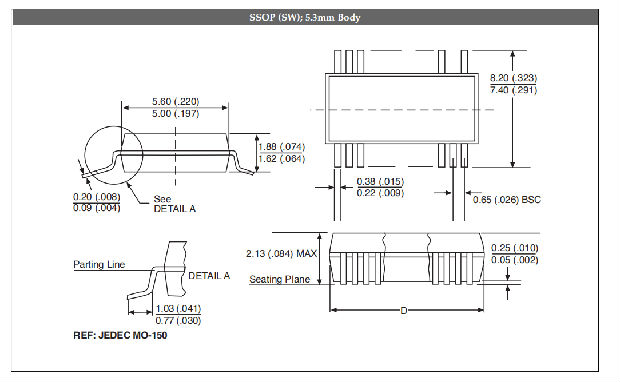

*小型24导SSOP封装

*控制性呃逆模式

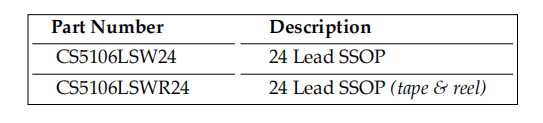

程序包选项

说明

CS5106是一个固定频率的电流模式控制器单NFET驱动器和一个双FET同步驱动器。同步驱动器可提高主等功率级的效率,单个驱动器可使设计者开发用于控制器电源和二次侧室内维护的辅助电源。此外,由于同步驱动器具有可编程的场效应晶体管(FET)非重叠,CS5106是软开关变换器拓扑的理想控制器。

CS5106是专门为隔离拓扑设计的,灵活性、减小尺寸和减少部件数量是要求。控制器包含以下内容特点:欠压停机,过压停机,可编程频率,可编程同步非重叠时间,主从时钟频率范围检测,启用,输出欠压保护定时器,20毫安5伏输出,80毫安脉冲宽度调制传播延迟,控制打嗝模式。

CS5106的连接温度和供电范围分别为-40℃~125℃和9V~16V,可在24导SSOP封装中使用。

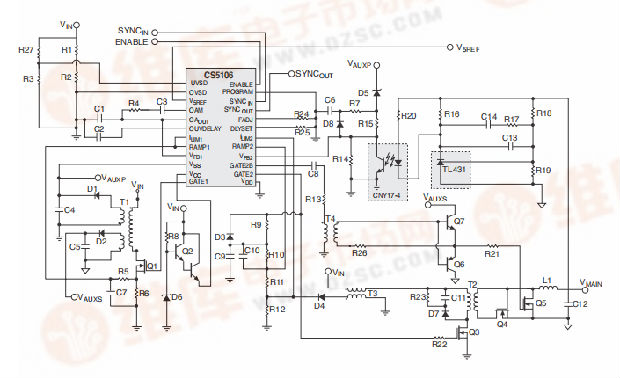

应用程序关系图

带同步整流器的48V至3.3V正激变换器

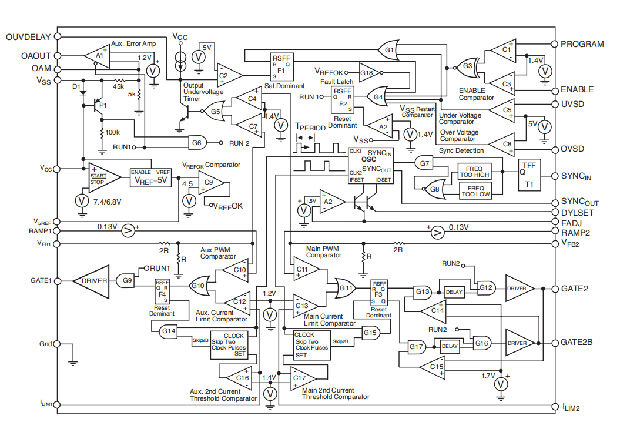

方块图

应用理论

操作理论

为集成电路供电

集成电路有一个电源、VCC和一个接地线。如果VSS用于自举电源,则VSS和VCC之间的二极管是正向偏置的,并且IC将从VSS获得其功率。内部逻辑监控电源电压VCC。在异常运行条件下,所有闸门驱动器都保持在低状态。CS5106需要1.5mA额定启动电流。

启动

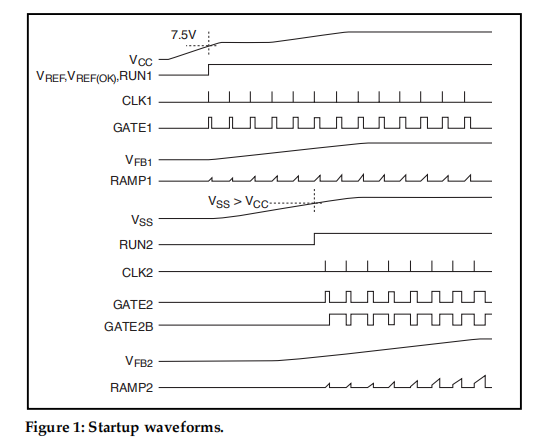

假设部件已启用且不存在过压或欠压故障。此外,假设所有辅助和主调节输出电压从0V开始。8V齐纳参考电源通常应用于VCC。当VCC超过7.5V时,5V参考电压启用,OSC开始切换。如果V5REF导线没有过度负载,使得V5REF<4.5V标称值,则VREFOK将变高,RUN1将变高,从而将GATE1从低状态释放。在释放GATE1之后,它开始根据辅助控制回路和辅助电源设置的条件进行切换,VSS开始上升。当VSS>VCC+V(D1)时,P1打开,RUN2变高,将GATE2和GATE2B从低状态释放。GATE2和GATE2B根据主控制回路设定的条件开始切换,主调节输出开始上升。参见图1中的启动波形。

软起动

辅助电源的软启动是通过在OAOUT和接地之间放置一个电容器来实现的。误差放大器的额定源电流为200A,非常适合设置辅助调节器的软启动条件。应注意确保软启动计时要求与辅助电源的任何瞬态负载要求不冲突,因为OAOUT上的大电容会减慢环路响应。此外,必须选择软启动电容器,以便在启动或重启过程中,两个输出都将在延时计时器跳闸之前进入调节状态。主电源的软启动是通过在启动时向软启动电容器C6至D5和R7充电来完成的。主电源进入调节后,C6继续充电,并由D8断开与反馈回路的连接。

电压和电流斜坡PWM比较器输入(VFB1、2和RAMP1、2导线)

C10和C11是辅助和主电源的PWM比较器。反馈电压(VFB)除以3,并与变压器一次侧电流的线性电压表示(RAMP)进行比较。当反馈比较器的输出变高时,复位信号被发送到PWM触发器,栅极驱动器被驱动到低电平。坡道导线上的130mV偏移允许驾驶员在轻载情况下进入0%的占空比。

GATE1驱动器(VFB1)的反馈电压

通常,辅助误差放大器(A1)的输出与VFB1相连。通过误差放大器负输入上的10:1电阻分压器和误差放大器正输入上的固定1.2V参考电压,将VSS输出编程为12V。

逐脉冲过流保护及打嗝模式(ILIM1,2引线)

C12和C13是辅助和主电源的逐脉冲电流限制比较器。当变压器一次侧的电流增大到电流检测电阻器上的电压超过1.2V标称值时,电流限制比较器的输出变高,并且向PWM触发器发送复位信号,栅极驱动器被驱动低。

C16和C17是第二阈值,用于辅助和主电源的逐脉冲电流限制比较器。如果变压器一次侧的电流增长如此之快,以致电流检测电压不受C12或C13的限制,并且电流检测电阻器上的电压超过1.4V,则第二阈值比较器将使延迟电路跳闸,并强制栅极驱动器级变低并在接下来的两个时钟周期内保持低电平。

欠压和过电压阈值

C5和C8是欠压和过压检测比较器。通常,这些输入通过三电阻分压器中的中间电阻连接,顶部电阻连接至车辆识别号,底部电阻连接至接地。欠压比较器具有200毫伏的内置滞后,相对于UVSD导线上的直接输入。欠压比较器的正输入为5V,过电压比较器的负输入为5V。两个比较器的输出均在(G4)处与过电流和使能输入相乘。G4的输出将输入馈送到故障锁存器(F2)。

规划和启用潜在客户

程序导线控制使能导线的极性。如果程序导程是高或浮动的,则如果使能输入是高或浮动的,则门输出将变低。如果程序导联系低,如果使能输入系低,门输出将变低。如果在将输出切换为低后启用部件,则部件将根据“启动”部分中概述的过程重新启动。

故障逻辑

如果VREF、UVSD或OVSD故障在任何时候发生,G4将重置故障锁存器(F2)。运行1变低,所有门驱动器停止切换并返回其低状态。当RUN1变低时,辅助运放(A1)的输出放电软启动电容器,并在RUN1变低时保持低。如果在OUVDELAY定时器跳闸前消除故障条件,则当VSS<1.4V时,IC将重新启动电源。如果OUVDELAY定时器跳闸,则必须重新启动电源,如下节所述。

主和输出欠压延迟定时器辅助调节输出

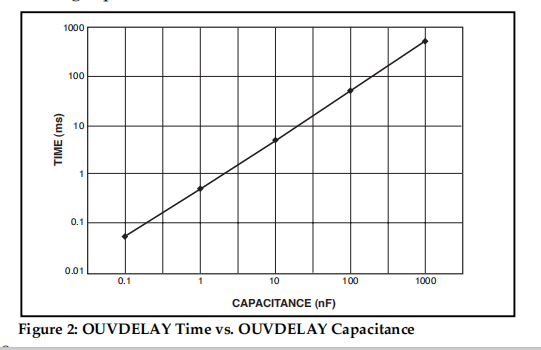

C7和C4是辅助和主电源的输出欠压监测器比较器。如果调整后的输出电压下降到其相关的VFB电压超过4.1V,则输出欠压监测器比较器将变高,并且OUV延时电容器从0V开始充电。时序关系由10A标称电流源、OUV延时电容器和C2输入端的5V故障阈值建立(见图2)。如果任何调节输出下降,并在整个充电时间内保持低电压,则会触发故障,所有栅极驱动器将进入低状态。

一旦触发此故障,只有在VSS<1.4V时,当OUVDELAY故障复位并启用或切换UVSD时,IC才会重新启动电源。要复位OUVDELAY故障,两个VFB输入必须小于4.1V。在所示的应用电路中,当RUN1停止振荡器时,OAOUT会使VFB1变低。当VAUXP放气时,VFB2降低,VFB2光隔离器不再通电。

FADJ和DLYSET领导

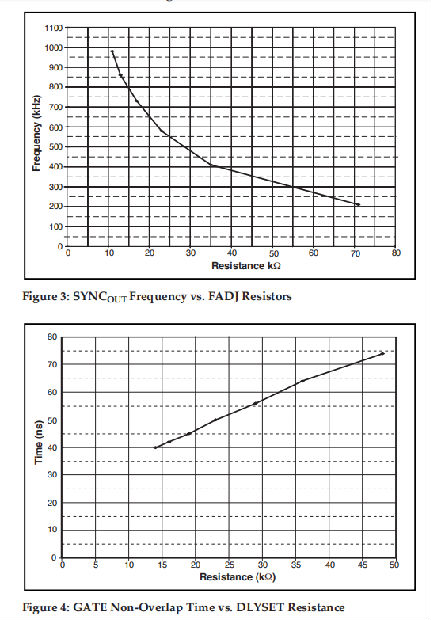

放大器A2和晶体管N3产生一个输出为FADJ的电流源跟随器。一个从FADJ到接地的外部电阻完成了回路。电阻两端的电压由一个经过缓冲、微调的精确参考电压设定。以这种方式,产生一个精确的电流,用于对内部电容器进行充电和放电,从而产生一个具有严格频率公差的振荡器。有关FADJ电阻值的选择,请参见图3。晶体管N2与N3并联,用于在从DLYSET到接地的电阻器之间产生独立的电流。该电流用于编程主PWM驱动器中的栅极非重叠延迟块。有关DLYSET电阻值的选择,请参见图4。

振荡器

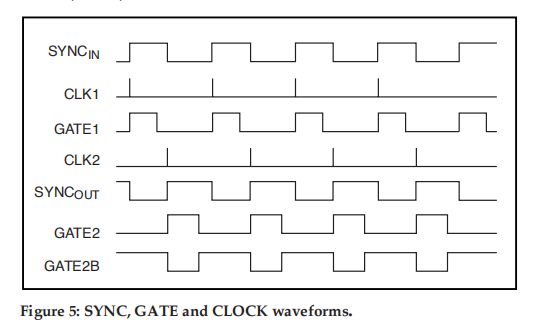

振荡器产生两个时钟信号,这两个信号相对于时间来说是180度异相。一个时钟信号为主驱动器供电,另一个为辅助驱动器供电。因为驾驶员从未同时打开,所以地面噪音和电源噪音被降至最低。时钟信号实际上是100ns脉冲峰值。这些尖峰形成了一个狭窄的驾驶员开启窗口。这个窄窗口可以防止驾驶员在时钟周期中间误开。振荡器可由外部时钟(从机)同步或驱动其他控制器(主机)的时钟。SYNC、CLK和GATE波形之间的关系见图5。

同步和同步线索

通过使用同步导线,可以将多个电源同步到一个电源。同步和同步脉冲总是相差180度。同步输入始终与主驱动器的时钟信号同步,同步输出始终与辅助驱动器的时钟信号同步。如果IC被用作从机,输入频率必须在其自身FADJ电阻器设定的编程频率的+10%,-20%范围内。如果SYNCIN导线上的频率超出内部频率+25%,-35%,则SYNCIN输入将被忽略。如果同步信号在电源处于同步操作时停止,则同步电源将停止并重新启动自由运行。当电源处于同步运行状态时,如果同步信号偏离频率规范,则同步电源将开始自由运行,而不重新启动。

坡度补偿

具有电流模式控制的DC-DC变换器需要斜坡补偿,以避免占空比大于50%时的不稳定性。在电流检测波形中添加一个斜率(或从电压波形中减去),该斜率等于电感电流下降斜率的百分比(典型值为75%)。在所示的应用图中,可以选择引导(反激)变压器电感,使占空比不超过50%,因此不需要斜坡补偿。正激变换器中的buck指示器通常选择在最大占空比为50-60%的连续传导模式下工作,并且需要斜坡补偿。斜坡补偿完成如下:每次门2打开时,R9和C9形成斜坡波形上升。C9通过D3放电到每个循环的相同水平,而不考虑占空比。选择R10和R11来控制坡度补偿量。C10为噪音和开启峰值提供过滤。要计算所需的斜率补偿,请计算buck指示器下电流和电流检测电阻器-R12处的相应电压斜率。

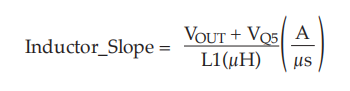

降压电感器下降坡度为:

此应用电路的电流感测电阻器处的等效下降斜率为:

在选择R9和C9以产生时间常数约为振荡器周期5倍的斜坡之后,可以选择R10和R11以使斜坡2处的电压为R12处电压的1.75。

同步整流

为了降低正激变换器的损耗,采用了同步整流。在低电压、中电流和大电流转换器中,效率的提高将是最重要的,在这些转换器中,传导损耗的提高抵消了栅极驱动的任何附加损耗。

在应用电路中,Q4由正向变压器接通和断开。Q5通过脉冲变压器T4和由Q6、Q7构成的栅极驱动器进行开关。因为Q4和Q5是通过不同类型的组件驱动的,所以必须考虑传播延迟的差异。应选择DLYSET电阻器,以避免击穿或过多的关闭时间。

门驱动能力

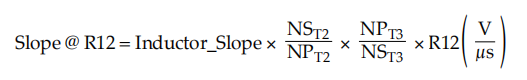

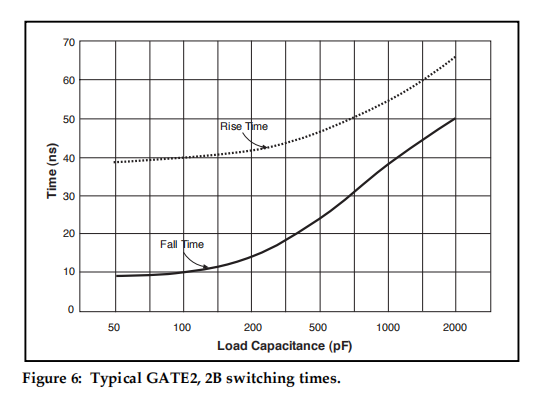

所有栅极驱动输出的额定峰值电流为0.5A。典型上升和下降时间见图6和图7。

设计注意事项

电路板应采用高频布局技术,以避免脉冲宽度抖动和高阻抗输入的误触发。应采用地平面。信号接地和电源接地应分开运行。具有高转换率或电流脉冲的电路部分应与敏感区域隔离。应根据需要使用屏蔽和去耦电容器。

应特别注意防止同步导线和周围导线之间的耦合。根据电路板布局和元件值,可能需要去耦电容器或降低电阻值,以减少FADJ和DLYSET电阻器上的噪声拾取。可能需要去耦电容器或有源上/下拉,以防止启用和程序引线的误触发。

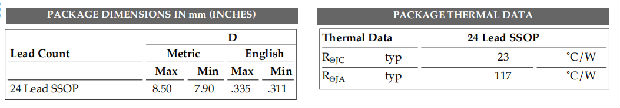

包装规格

订购信息