ADP3166点击型号即可查看芯片规格书

特征

*可选择2、3或4相操作,每相最高1兆赫

*差分感应误差超过温度±1%

*外部大功率驱动器接口的逻辑级PWM输出

*所有输出相位之间的有功电流平衡

*内置动力好冲裁支架

*视频代码更改

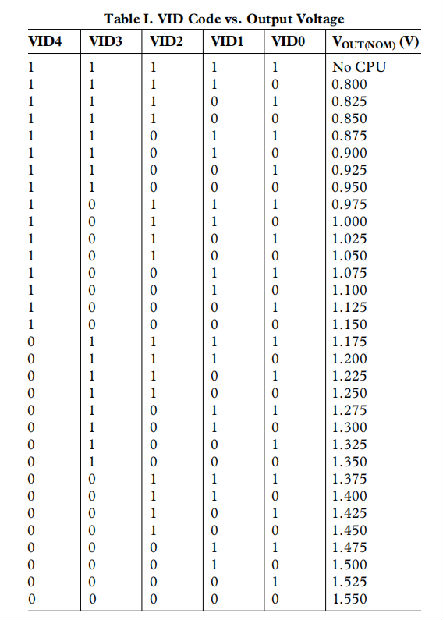

*5位数字可编程0.8 V至1.55 V输出

*可编程短路保护

*闭锁延迟

*过电压保护撬杆逻辑输出

应用

*台式电脑电源

*下一代AMD处理器

*VRM模块

一般说明

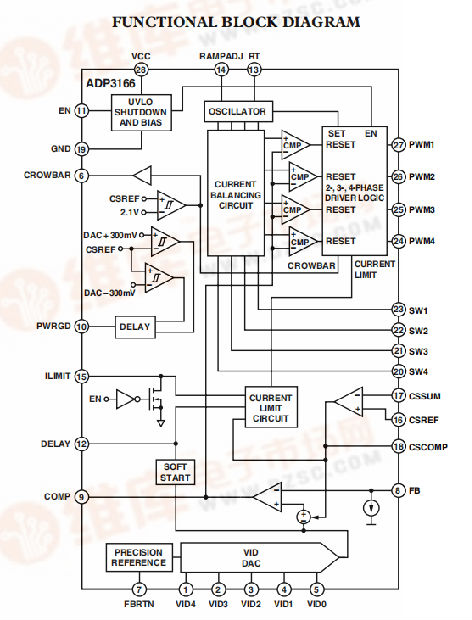

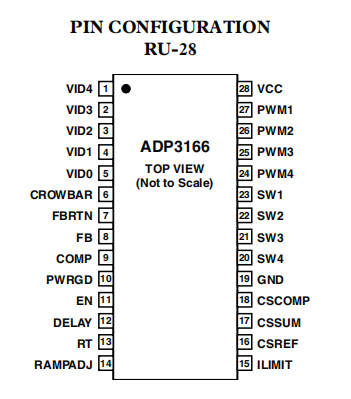

ADP3166是一种高效、多相、同步降压型开关稳压器控制器,用于将12V主电源转换为高性能AMD处理器所需的核心电源电压。它使用内部5位DAC直接从处理器读取电压识别(VID)代码,该处理器用于将输出电压设置在0.8 V和1.55 V之间。ADP3166还使用多模式PWM架构以可编程开关频率驱动逻辑级输出,该开关频率可优化VRM的大小和效率。输出信号的相位关系可以是可编程为提供2、3或4相操作,允许构造多达4个互补降压开关级。

ADP 3166包括可编程的空载偏移和斜率功能,以调整输出电压作为负载电流的函数,从而使其始终处于系统瞬态的最佳位置。ADP3166还提供精确可靠的短路保护、可调电流限制和延迟功率良好输出,可适应CPU要求的动态输出电压变化。

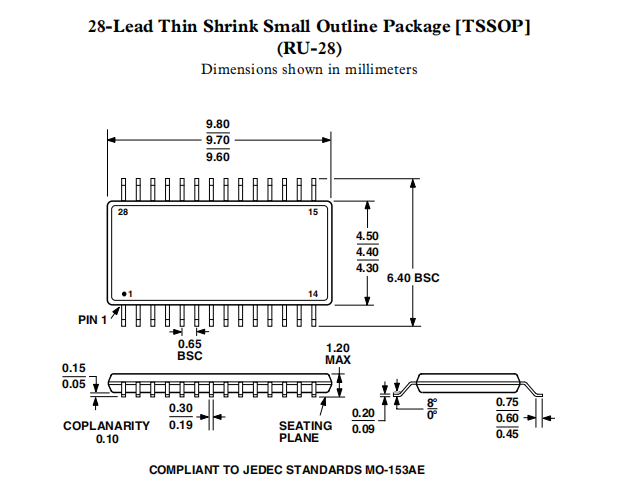

ADP 3166规定的商业温度范围为0°C至85°C,可在28铅TSSOP封装中使用。

操作理论

ADP3166结合了多模、固定频率的脉宽调制多相逻辑输出控制,用于2、3、4相同步buck-CPU核心电源转换器。内部5位VID DAC符合AMD的Hammer系列电源规范。多相操作对于产生当今微处理器所需的高电流和低电压非常重要。在单相变换器中处理高电流会对系统中的电感和mosfet等元件产生很高的热需求。

ADP3166的多模控制确保了

•平衡相位之间的电流和热量。

•在尽可能低的开关频率和输出解耦下的高速响应。

•尽量减少低频操作造成的热开关损耗。

•紧负荷线调节和精度。

•高达4相操作的高电流输出。

•利用多相抵消降低输出纹波。

•董事会布局豁免。

•由于独立的组件选择,易于使用和设计。

•操作灵活,可根据低成本或高性能定制设计。

相数

工作相位的数量及其相位关系由监控PWM输出的内部电路决定。通常,ADP 3166作为4相PWM控制器工作。接地脉冲宽度调制4引脚程序3相操作,接地脉冲宽度调制3和脉冲宽度调制4引脚程序2相操作。

当ADP 3166启用时,控制器在PWM3和PWM4上输出约550 mV的电压。内部比较器根据400毫伏的阈值检查每个引脚的电压。如果引脚接地,它将低于阈值,相位将被禁用。脉宽调制引脚的输出阻抗约为5 kΩ。连接到脉宽调制引脚的任何外部下拉电阻不应小于25 kΩ,以确保正常工作。相位检测在内部振荡器的前两个时钟周期期间进行。之后,如果PWM输出没有接地,它将在0v和5v之间切换。如果PWM输出接地,它将保持断开。

PWM输出是逻辑级设备,用于驱动外部栅极驱动器,如ADP3418。由于每个阶段都是独立监测的,因此运行接近100%的占空比是可能的。此外,对于重叠的相位,一次可以打开多个输出。

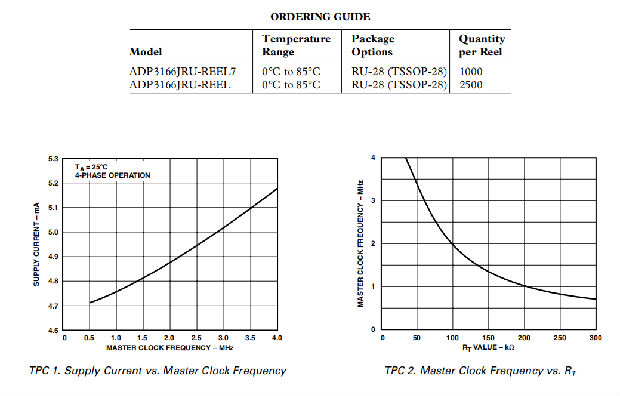

主时钟频率

ADP3166的时钟频率由一个从RT引脚接地的外部电阻设置。频率遵循TPC 1中的图表。为了确定每相的频率,时钟被使用的相数除以。如果PWM4接地,则将主时钟除以3作为剩余相位的频率。如果PWM3和PWM4接地,除以2。如果所有相位都在使用中,除以4。

输出电压差动感应

ADP 3166将差分传感与高精度VID DAC和基准以及低偏移误差放大器相结合,以在其整个工作输出电压和温度范围内保持±1%差分传感误差的最坏情况规范。输出电压在FB和FBRTN管脚之间感应。FB应该通过一个电阻器连接到调节点,通常是微处理器的远程感应引脚。FBRTN应直接连接到遥感接地点。内部VID-DAC和精度参考是参照FBRTN的,FBRTN的最小电流为100微安,以便进行精确的遥感。内部误差放大器将DAC的输出与FB引脚进行比较,以调节输出电压。

输出电流感应

ADP 3166提供了一个专用的电流检测放大器(CSA),用于监测总输出电流,以确定电压与负载电流之间的正确位置,并进行电流极限检测。在输出端感测负载电流可得到传递到负载的总平均电流,这是一种固有的比峰值电流检测或通过感测元件(如低侧MOSFET)采样电流更精确的方法。

根据系统目标的不同,可以采用多种方式配置该放大器:

•无热敏电阻输出电感ESR传感,成本最低;

•带热敏电阻的输出电感器ESR传感,通过跟踪电感器温度提高精度;

•最高精度测量用感测电阻器。

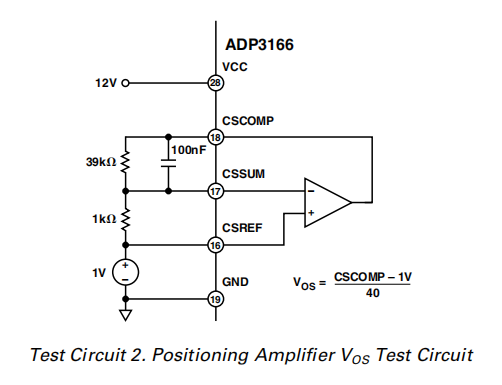

CSA的正输入连接到CSREF引脚,CSREF引脚连接到输出电压。放大器的输入通过从感测元件(例如输出电感的开关节点侧)到反向输入CSSUM的电阻相加。CSCOMP和CSSUM之间的反馈电阻设置放大器的增益,滤波器电容与该电阻并联放置。放大器的增益是可编程的,通过调节反馈电阻来设置微处理器所需的负载线。然后将当前信息作为CSREF–CSCOMP的差异给出。该差分信号在内部用于偏移用于电压定位的VID DAC,并用作电流限制比较器的差分输入。

为了为电流传感提供最佳精度,CSA被设计为具有低偏移输入电压。此外,传感增益由外部电阻确定,因此可以使其非常精确。

有源阻抗控制方式

为了控制动态输出电压降作为输出电流的函数,可以将与CSCOMP管脚处的总输出电流成比例的信号缩放为等于调节器的降阻阻抗乘以输出电流。然后使用该降电压来设置系统的输入控制电压。直接从DAC参考输入电压中减去下垂电压,以告诉误差放大器输出电压应在哪里。这与以前的实现不同,并允许增强的前馈响应。

电压控制方式

电压模式控制回路采用高增益带宽的电压模式误差放大器。正输入的控制输入电压根据表I中列出的电压通过VID 5位逻辑代码进行设置。该电压还被作为电流函数的输出电压的主动定位的下垂电压(通常称为主动电压定位)所抵消。放大器的输出是COMP管脚,它设置内部PWM斜坡的终止电压。

负输入(FB)通过一个电阻器RB连接到输出检测位置,用于检测和控制此时的输出电压。来自流过RB的FB管脚的电流源用于设置来自VID电压的空载偏移电压。空载电压相对于VID DAC为正。在FB和COMP之间的反馈网络中加入了主回路补偿。

软起动

输出电压的通电斜坡时间由一个电容器和一个电阻并联设置,从延迟引脚到接地。RC时间常数还确定电流限制锁存关闭时间,如下节所述。在UVLO或EN为逻辑低时,延迟引脚保持在地上。在达到UVLO阈值并且EN为逻辑高之后,延迟电容器被内部20μa电流源充电。输出电压跟随延迟引脚上的斜坡电压,限制浪涌电流。软启动时间取决于VID-DAC和CDLY的值,RDLY会产生次要影响。有关设置CDLY的详细信息,请参阅应用程序部分。

当达到PWRGD阈值时,软启动循环停止,延迟引脚被拉高至3v。这确保当PWRGD向系统发送输出电压良好的信号时,输出电压处于VID电压。如果EN值过低或VCC降至UVLO以下,则延迟电容器复位为接地,以准备进行另一个软启动循环。

限流短路保护

ADP3166将可编程电流限制设定值与CSCOMP引脚处电流检测放大器输出上的电压进行比较。电流限值的水平是通过从ILIMIT引脚到接地的电阻来设置的。在正常运行期间,ILIMIT上的电压为3V。通过外部电阻器的电流在内部缩放,以给出10.4mV/μa的电流极限阈值。如果CSREF和CSCOMP之间的电压差降至电流极限阈值以下,内部电流限制放大器将控制内部COMP电压,以将平均输出电流保持在极限。

达到极限后,断开延迟引脚上的3V上拉,外部延迟电容器通过外部电阻放电。比较器监测延迟电压,并在电压降到1.8V以下时关闭控制器。因此,电流限制闭锁关闭延迟时间由从3V放电到1.8V的RC时间常数设置。应用部分讨论了基于所选CDLY的RDLY的选择。

由于控制器在闩锁关闭延迟时间内继续循环相位,如果在达到1.8 V阈值之前消除短路,控制器将恢复正常工作。恢复特性取决于PWRGD的状态。如果输出电压在PWRGD窗口内,控制器恢复正常工作。但是,如果短路导致输出电压下降到PWRGD阈值以下,则启动软启动循环。

可以通过卸下VCC并将其重新应用到ADP3166,或通过短时间将EN销拉低来重置闩锁关闭功能。要禁用短路闭锁关闭功能,外部接地电阻应保持打开状态,并将一个大(大于1 MΩ)电阻从VCC连接到延迟。这可以防止延迟电容器放电,因此永远不会达到1.8V阈值。电阻器将对软启动时间产生影响,因为通过它的电流将增加到内部20微安的电流源。

在启动过程中,当输出电压低于200毫伏时,二次电流限制激活。这是必要的,因为CSCOMP的电压摆幅不能低于地面。这个二次电流限制将内部COMP电压控制到PWM比较器的2v。这将通过电流平衡电路限制低压侧mosfet的电压降。

动态电压识别

ADP3166具有在控制器运行时动态改变视频输入的功能。这允许在电源运行和向负载提供电流时改变输出电压。这通常被称为飞行视频(OTF)。VID-OTF可以在轻载或重载条件下发生。处理器通过从开始代码到结束代码的多个步骤改变VID输入来向控制器发送信号。这种变化可以是正的,也可以是负的。

当VID输入改变状态时,ADP3166检测到该改变并使DAC空白至少400 ns。这一次是为了防止在六个VID输入发生变化时,由于逻辑扭曲而产生错误代码。另外,第一个VID改变启动PWRGD消隐功能至少100微秒,以防止假PWRGD事件。每次更换视频都会重置内部计时器。

功率良好监测

功率良好比较器通过CSREF引脚监测输出电压。PWRGD管脚是一个开路漏极输出,其高电平(当连接到上拉电阻器时)表明输出电压在先前根据VID电压设置规定的标称限值内。如果输出电压超出此指定范围,PWRGD将变低。在VID-OTF事件期间,PWRGD被屏蔽100微秒,以防止在输出改变期间出现假信号。

输出撬棍

作为电源的负载和输出部件保护的一部分,当输出电压超过功率良好阈值上限时,PWM输出被驱动为低(打开低侧mosfet),CROWBAR逻辑输出变为高。如果不存在其他故障,一旦输出电压回落到技术规格范围内,撬杆动作就会释放。释放阈值约为400 mV。

打开低边mosfet会随着电感中反向电流的增加而降低输出。如果输出过电压是由于高压侧MOSFET短路引起的,则该动作电流会限制输入电源或熔断其保险丝,从而保护微处理器不受损坏。

撬杆输出可用于向外部输入撬杆或其他保护电路发送信号。

输出启用和UVLO

输入VCC必须高于UVLO阈值,EN pin必须高于其逻辑阈值,以便ADP3166开始切换。如果UVLO小于阈值或EN pin为逻辑低,则禁用ADP3166。这将使PWM输出保持在地上,使延迟电容器对地短路,并使ILIMIT引脚保持在地上。

在应用电路中,ILIMIT引脚应连接到ADP3418驱动器的OD引脚。因为ILIMIT是接地的,所以这会禁用驱动程序,以便DRVH和DRVL都接地。此特性对于防止控制器关闭时输出电容器放电非常重要。如果驱动器输出未被禁用,则由于输出电容器通过电感的大电流放电,可能会在输出上产生负电压。

应用程序信息

典型AMD K8兼容CPU应用的设计参数如下:

•输入电压(VIN)=12 V

•VID设置电压(VVID)=1.500 V

•占空比(D)=0.125

•最大静态输出电压误差(±VSERR)=±50 mV

•最大动态输出电压误差(±VDERR)=±70 mV

•控制器和纹波允许的误差电压(±VRERR)=±20 毫伏

•最大输出电流(IO)=56 A

•最大输出电流阶跃( IO)=24 A

•静态输出降阻(RO)基于:

a) 、在上输出端设置空载输出电压电压限制。

VONL=VVID+VSERR–Verr=1.530伏

b)、 低输出全负荷输出电压电压限制。

•VOFL=VVID–VSERR+Verr=1.470伏

•RO=(VONL–VOFL)/(IO)=(1.530伏–1.470伏)/(56A)=1.1 mΩ

•动态输出降阻(棒)基于:

a)、 带输出电压的输出电流阶跃到空载设置在输出动态电压上限。

VONLD=VVID+VDERR–Verr=1.550伏

b)、 负载变化前的输出电压(在IOUT= IO处)。

•VOL=VONL–( IO RO)=1.504伏

•杆=(VONLD–VOL)/(IO)=(1.550 V–1.504 V)/(24A)=1.9 mΩ

•相数(n)=3

•每相开关频率(fSW)=330 kHz

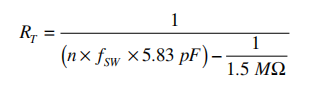

设置时钟频率

ADP3166采用固定频率控制架构。频率由外部定时电阻器(RT)设置。时钟频率和相数决定了每相的开关频率,它直接关系到开关损耗和电感、输入输出电容的大小。对于三相n=3,990 kHz的时钟频率将每个相位的开关频率fSW设置为330 kHz,这表示开关损耗和输出滤波器组件的大小之间的实际权衡。图1显示,要获得990 kHz的振荡器频率,RT的正确值为200 kΩ。或者,可以使用:

其中5.83 pF和1.5 MΩ是内部IC组件值。

为了获得良好的初始精度和频率稳定性,建议使用1%的电阻。

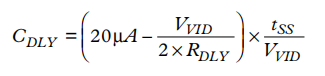

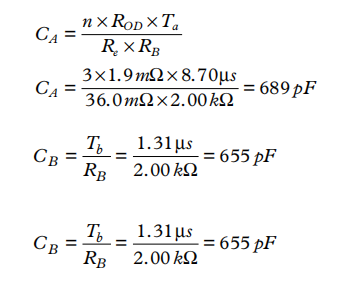

软启动和电流限制闭锁关闭延迟时间

由于软启动和电流限制闭锁-关断延迟功能共享延迟管脚,这两个参数必须一起考虑。第一步是为软启动斜坡设置CDLY。该斜坡由20μa内部电流源产生。RDLY的值将对软启动时间产生二阶影响,因为它将部分电流源沉到地上。然而,只要RDLY保持大于200kΩ,这种影响就很小。CDLY的值可以使用:

其中tSS是所需的软启动时间。假设RDLY为390kΩ,所需软启动时间为3ms,CDLY为36nf。

CCS的最接近标准值是39nf。一旦选择了CDLY,就可以使用:

如果RDLY的结果小于200 kΩ,则应通过重新计算CDLY的方程式来考虑较小的软启动时间,或者应使用较长的闭锁时间。在任何情况下都不应小于200 kΩ。在本例中,8 ms的延迟时间使得RDLY=402 kΩ。最接近的标准5%值为390 kΩ。

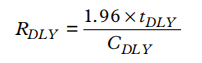

感应器选择

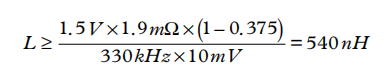

电感电感的选择决定了电感中的纹波电流。电感越小,产生的纹波电流越大,这会增加mosfet的输出纹波电压和传导损耗,但允许使用较小尺寸的电感,并且对于指定的峰-峰瞬态偏差,总输出电容较小。相反,较高的电感意味着较低的纹波电流和较低的传导损耗,但对于相同的峰-峰瞬态偏差,则需要较大的电感尺寸和较大的输出电容。在任何多相变流器中,电感峰间纹波电流的实用值小于同一电感中最大直流电流的50%。方程4显示了电感、振荡器频率和电感中峰间纹波电流之间的关系。公式5可用于根据给定的输出纹波电压确定最小电感:

求解10 mV p-p输出纹波电压产生率的方程5

如果纹波电压小于设计的纹波电压,则可以使电感变小,直到纹波值满足要求。这将允许最佳瞬态响应和最小输出解耦。

应使用尽可能小的电感器,以尽量减少输出电容器的数量。一个600毫安的电感是一个很好的起点选择,它给出了6.6 A的计算纹波电流。电感不应该饱和在22 A的峰值电流,并且应该能够处理由绕组中18.7 A的平均电流和磁芯损耗引起的功耗之和。

电感设计中的另一个重要因素是用于测量相电流的DCR。大的DCR会导致过大的功率损耗,而过小的DCR值会导致测量误差增加。一个好的规则是DCR大约是静态下垂电阻(RO)的1到1 1/2倍。

在我们的例子中,我们使用DCR为1.6 mΩ的电感器。

设计电感器

一旦电感和DCR已知,下一步要么是设计一个电感,要么是找到一个标准电感,尽可能接近达到总体设计目标。为了保证控制系统的精度,指定电感和DCR公差也很重要。使用20%的电感和8%的DCR(在室温下)是大多数制造商可以满足的合理公差。

电感器设计的首要决定是选择磁芯材料。在高频下提供低铁心损耗有多种可能性。两个例子是粉末磁芯(例如,来自Magnetics,Inc.的Kool-Mμ或微金属)和间隙软铁氧体磁芯(例如,来自Philips的3F3或3F4)。低频铁粉铁芯损耗大,特别是电感值较低、纹波电流较大时,应尽量避免。

核心几何体的最佳选择是闭环类型,例如pot核心、PQ核心、U核心和E核心或圆环体。价格和性能之间的一个很好的折衷是具有环形形状的磁芯。

输出降阻

设计要求当输出电流增大时,在CPU引脚处测量的稳压器输出电压下降。规定的电压降对应于静态输出降阻(RO)。

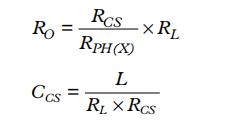

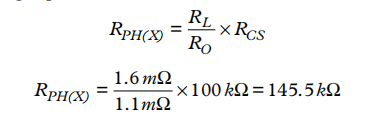

输出电流是通过将每个电感器上的电压相加,然后通过低通滤波器来测量的。这个夏季过滤器是配置了电阻RPH(X)(夏季)和RCS的CS放大器,以及CCS(过滤器)。调节器的输出电阻由以下方程式设定,其中RL是输出电感的DCR:

一个可以灵活地选择RCS或RPH(X)。最好选择RCS等于100kΩ,然后通过重新排列方程6来求解RPH(X)。

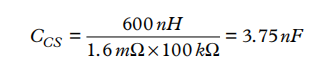

接下来,使用方程式6求解CCS:

最好在布局中有一个CCS的双重位置,以便可以并行使用标准值,以尽可能接近所需的值。对于这个例子,选择CCS作为1.5nf和2.2nf并行是一个不错的选择。为了获得最佳精度,CCS应该是10%的电容器。RPH(X)的最接近标准1%值为147 kΩ。

电感DCR温度校正

以电感的直流电阻为敏感元件,铜线为直流电阻源,需要补偿电感绕组的温度变化。幸运的是,铜有一个众所周知的温度系数(TC)为0.39%/℃。

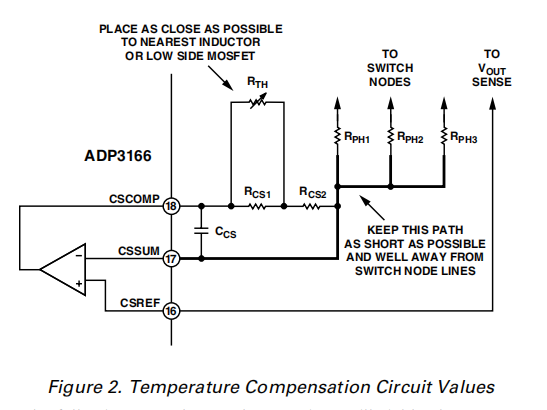

如果RCS的电阻变化与导线的电阻变化成相反和相等的百分比,它将抵消电感器DCR的温度变化。由于NTC热敏电阻的非线性特性,需要使用电阻RCS1和RCS2(见图2)将NTC线性化并产生所需的温度跟踪。

以下程序和表达式将产生用于给定RCS值的RCS1、RCS2和RTH(25°C时的热敏电阻值)的值。

1.根据类型和值选择NTC。因为我们还没有一个值,所以从一个接近RCS的热敏电阻开始。NTC的初始公差也应大于5%。

2.根据NTC的类型,找出其在两种温度下的相对电阻值。工作良好的使用温度为50°C和90°C。我们将这些电阻值称为A(A为RTH(50°C)/RTH(25°C))和B(B是RTH(90°C)/RTH(25°C))。注意,在25°C时,NTC的相对值始终为1。

3.接下来,求出每种温度所需的RCS的相对值。这是基于所需的百分比变化,我们最初将其设为0.39%/℃。我们将这些称为r1(r1为1/(1+TC(T1-25)),r2(r2为1/(1+TC(T2-25)),其中TC=0.0039,T1=50℃,T2=90℃。

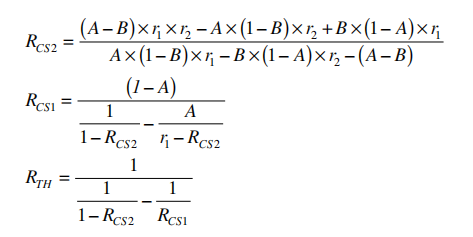

4、使用计算RCS1、RCS2和RTH的相对值:

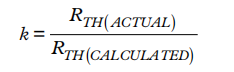

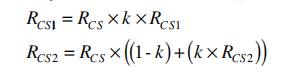

5.计算RTH=RTH RCS,然后选择可用热敏电阻的最接近值。同时,根据实际使用的热敏电阻值与计算值的比值计算缩放系数k:

6.最后,使用以下公式计算RCS1和RCS2的值:

在这个例子中,RCS被选择为100kΩ,所以我们从一个100kΩ的热敏电阻值开始。通过查看现有的0603型热敏电阻,我们发现Vishay NTHS0603N01N1003JR NTC热敏电阻的a=0.3602和B=0.09174。从中我们计算出RCS1=0.3796,RCS2=0.7195和RTH=1.0751。求解RTH得到107.51kΩ,因此我们选择100kΩ,使k=0.9302。最后,我们发现RCS1和RCS2分别为35.3kΩ和73.9kΩ。选择最接近的1%电阻值可得到35.7 kΩ和73.2 kΩ的选择。

输出偏移

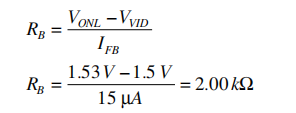

AMD的规范要求在空载情况下,调节器的标称输出电压应偏移到高于对应于VID码的标称电压的值。偏移量由从FB引脚(IFB)流出并流过RB的恒流源设定。RB的值可通过方程式11找到:

最近的标准1%电阻值为2.00 kΩ。

COUT选择

AMD通常推荐用于各种处理器和平台的调节器所需的输出解耦。还可以使用一些简单的设计准则来确定需要什么。这些指导方针的基础是在系统中同时使用大容量电容器和陶瓷电容器。

首先要根据所用电容器的数量和类型来选择陶瓷电容的总量。陶瓷的最佳位置是在插座内。其他的也可以沿着插座的外缘放置。

建议使用30至100微F的陶瓷组合值,通常由多个陶瓷电容器组成。选择陶瓷数量并计算陶瓷总电容(CZ)。

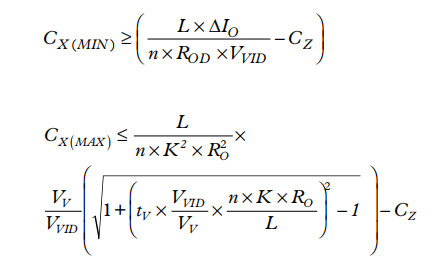

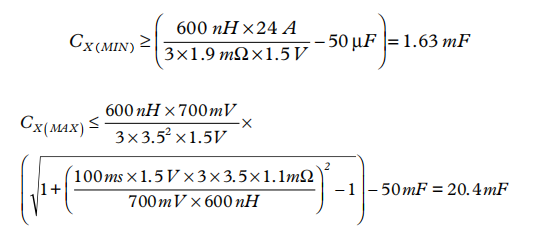

其次,当考虑输出的飞行电压步进的VID时(时间tV中的电压步进VV,误差为VERR),对总体积电容量(CX)有一个上限,并且基于满足给定最大负载步进的负载释放临界电容量的下限:

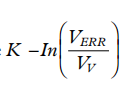

其中

为了满足这些表达式和瞬态响应的条件,大容量电容器组(RX)的ESR应小于或等于动态下垂电阻ROD。如果CX(MIN)大于CX(MAX),则系统将不满足动态视频规范,并且可能需要使用更小的电感或更多的相位(并且可能需要增加开关频率以保持输出纹波相同)。

在我们的例子中,使用了MLCC电容器的组合(CZ=50μF)。在100μs内,动态视频阶跃变化从1.5 V到0.8 V(使VV=700 mV),设置误差为3%。

体电容产额的求解:

式中K=3.5。

使用8个典型ESR为12 mΩ的820μF振荡器,每个振荡器产生CX=6.56 mF,RX=1.5 mΩ。

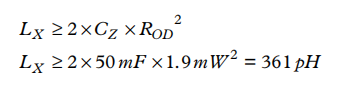

最后一次检查应确保大容量电容器(LX)的ESL足够低,以限制初始高频瞬态尖峰。这是用:

在本例中,对于8个OSCON电容器,LX为375 pH,这基本上满足了这一限制。如果选择的大容量电容器组的LX太大,则必须增加电容器的数量。

需要注意的是,对于这种多模控制技术,只要满足方程12、13和14的条件,就可以使用全陶瓷设计。

功率金氧半电晶体

在本例中,每相选择一个高压侧开关和两个低压侧开关的N通道功率mosfet。功率mosfet的主要选择参数有VGS(TH)、QG、CISS、CRSS和RDS(ON)。最小栅极驱动电压(ADP3418的电源电压)指示必须使用标准阈值或逻辑级阈值mosfet。当VGATE~10v时,建议使用逻辑电平阈值mosfet(VGS(TH)<2.5v)。

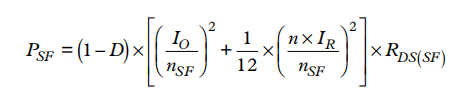

最大输出电流IO决定了低端(同步)mosfet的RDS(ON)要求。在ADP3166中,电流在相位之间是平衡的,因此每个低边MOSFET中的电流是输出电流除以MOSFET的总数(nSF)。在导通损耗占主导地位的情况下,以下表达式显示了每个同步MOSFET在每相纹波电流(IR)和平均总输出电流(IO)方面的总功耗:

知道设计的最大输出电流和允许的最大功耗,就可以找到MOSFET所需的RDS(ON)。对于D-PAK Mosfet环境温度为50℃,在120℃结温下,PSF的安全限值为1w至1.5w。因此,对于我们的例子(最大56安),我们发现RDS(SF)(每MOSFET)<10 mΩ。这个RDS(SF)也处于约120℃的结温,因此我们需要确保在进行选择时考虑到这一点。在我们的例子中,我们选择了两个下侧mosfet,每个在室温下为7 mΩ,在高温下为8.4 mΩ。

同步MOSFET的另一个重要因素是输入电容和反馈电容。反馈与输入的比率需要很小(建议小于10%),以防止当开关节点变高时同步mosfet意外开启。

此外,关闭同步MOSFET的时间不应超过MOSFET驱动器的非重叠死区时间(ADP3418的典型值为40 ns)。驱动器的输出阻抗约为2Ω,典型的MOSFET输入栅极电阻约为1Ω到2Ω,因此应坚持小于6000 pF的栅极总电容。由于有两个MOSFET并联,我们应该将每个同步MOSFET的输入电容限制在3000pf。

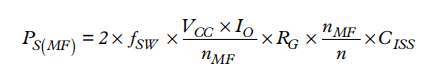

高侧(主)MOSFET必须能够处理两个主要的功耗组件:传导和开关损耗。开关损耗与主MOSFET打开和关闭所需的时间以及被开关的电流和电压有关。基于栅极驱动器阻抗和MOSFET输入电容的上升和下降时间的开关速度,以下表达式提供了每个主MOSFET的开关损耗的近似值,其中nMF是主MOSFET的总数:

这里,RG是总栅极电阻(对于ADP3418为2Ω,对于典型的高速开关mosfet为1Ω,使RG=3Ω),CISS是主电路的输入电容MOSFET。有趣的是,添加更多的mainMOSFET(nMF)并不能真正帮助每个MOSFET的开关损耗,因为额外的栅电容会减慢开关速度。降低开关损耗的最好办法是使用较低的栅电容器件。

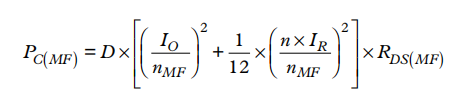

主MOSFET的传导损耗如下所示,其中RDS(MF)是MOSFET的导通电阻:

通常,对于主mosfet,需要最高速度(低CISS)器件,但这些器件通常具有较高的导通电阻。

在结合开关损耗和传导损耗时,必须选择满足总功耗(单个D-PAK约1.5w)的设备。

在我们的例子中,我们选择了一个Infineon IPD12N03L作为主MOSFET(共三个;nMF=3),CISS=1460 pF(max),RDS(MF)=14 mΩ(TJ=120℃时最大),一个Infineon IPD06N03L作为同步MOSFET(共六个;nSF=6),CISS=2370 pF(max),RDS(SF)=8.4 mΩ(TJ=120℃时最大)。同步MOSFET的CISS小于3000pf,满足了这一要求。在IO=56a和IR=6.6a时求解每个MOSFET的功耗,每个同步MOSFET的功耗为647mw,每个主MOSFET的功耗为1.26w。

考虑到每个主MOSFET与每个同步MOSFET相比通常有更多的PCB可用面积,这些数字工作得很好。

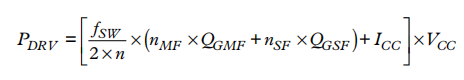

最后要看的是驱动程序中每个阶段的功耗。这最好用MOSFET的QG来描述,并由下面给出,其中QGMF是每个主MOSFET的总栅极电荷,QGSF是每个同步MOSFET的总栅极电荷:

还显示了驱动器的待机损耗因数(ICC VCC)。对于ADP3418,最大耗散应小于400兆瓦。在我们的例子中,当ICC=7毫安,QGMF=22.8毫安,QGSF=34.3毫安时,我们发现每个驱动器中有265毫瓦,低于400毫瓦的损耗极限。有关更多详细信息,请参阅ADP3418数据表。

斜坡电阻选择

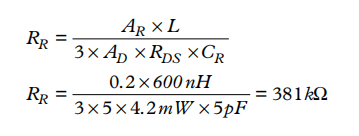

斜坡电阻器(RR)用于设置内部PWM斜坡的大小。选择该电阻值是为了提供热平衡、稳定性和瞬态响应的最佳组合。以下表达式用于确定最佳值:

其中AR是内部斜坡放大器增益,AD是电流平衡放大器增益,RDS是总的低边MOSFET导通电阻,CR是内部斜坡电容值。最接近的标准1%电阻值为383 kΩ。

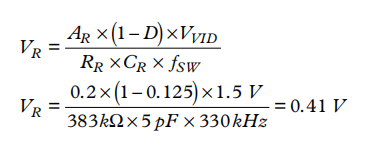

内部匝道电压大小可以使用:

内部斜坡的大小可以变大或变小。如果它变大,稳定性和瞬态响应会提高,但热平衡会降低。相反,如果斜坡变小,热平衡将在牺牲瞬态响应和稳定性的情况下得到改善。方程式19分母中的因子3设置了一个斜坡大小,为良好的稳定性、瞬态响应和热平衡提供了最佳平衡。

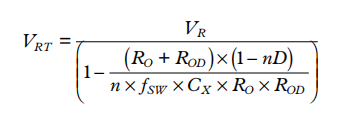

压缩机销斜坡

由于电压下降和输出电压下降,压缩机引脚上有一个斜坡信号。该斜坡幅度增加到内部斜坡,以在脉宽调制输入处产生以下整体斜坡信号。

在本例中,发现整个斜坡信号为0.48 V。

电流限制设定值

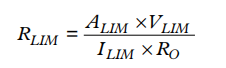

要选择电流极限设定值,我们需要找到RLIM的电阻值。ADP 3166的电流极限阈值设置为3 V源(VLIM)穿过RLIM,增益为10.4 mV/μa(ALIM)。可以使用以下方法找到RLIM:

当RLIM值大于500kΩ时,电流极限可能低于预期,因此需要对RLIM进行一些调整。这里,ILIM是电源输出的平均电流限制。在我们的例子中,为ILIM选择75a,我们发现RLIM是378kΩ,为此我们选择374kΩ作为最接近的1%值。

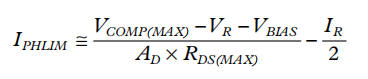

前面描述的每相电流限值由以下内容确定:

对于ADP3166,最大COMP电压(VCOMP(MAX))为3.3v,COMP引脚偏置电压(V bias)为1.2v,电流平衡放大器增益(AD)为5。使用0.48 V的VR和4.2 mΩ的RDS(最大值)(150°C时的低侧电阻),我们发现每相限值为74 a。

这个限制可以通过改变斜坡电压VR来调整。但请确保每相限值不低于每相平均电流(ILIM/n)。

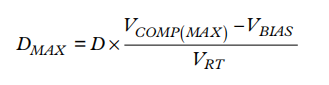

每个阶段的初始占空比限值也由以下因素确定:

对于本例,最大占空比为0.55。

反馈回路补偿设计

ADP3166的优化补偿允许调节器输出对负载变化的最佳响应。确定最佳补偿的基础是使调节器和输出解耦显示为在尽可能宽的频率范围内(包括直流)优化的输出阻抗,并等于下垂电阻(RO和ROD)。通过输出阻抗,输出电压将与负载电流成比例地响应;这确保了最佳输出位置,并允许输出解耦最小化。

采用ADP3166的多模反馈结构,需要设置反馈补偿,使变换器的输出阻抗与输出解耦并联工作,才能达到这一目的。输出电感和去耦电容(输出滤波器)产生了几个极点和零点,需要补偿。

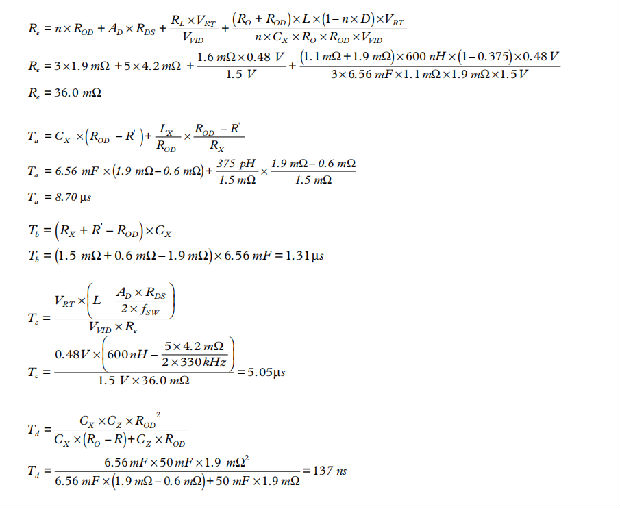

第一步是计算系统中所有极点和零点的时间常数:

其中,对于ADP3166,R'是来自块体的PCB电阻陶瓷电容器,其中RDS为总低压侧每相MOSFET导通电阻。在这个例子中,AD是5,VRT等于0.48 V,R'约为0.6 mΩ(假设为4层主板),对于8个OSCON电容器,LX的pH值为375。

电压反馈上的三型补偿器足以输出滤波器的适当补偿。那些表达以下是设计的最佳起点;可能需要进行一些调整,以考虑PCB和组件寄生效应。

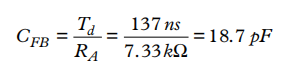

然后可以使用以下方法求解补偿值:

为这些组件选择最接近的标准值会产生:CA=680 pF,RA=7.32 kΩ,CB=680 pF,CFB=18 pF。

图3显示了使用补偿值的典型瞬态响应。

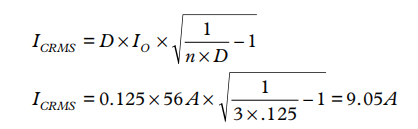

CIN选择和输入电流di/dt降低在连续电感电流模式下高边MOSFET是一个近似方波的占空比比值等于n VOUT/VIN,振幅为最大输出电流。为了防止大的电压瞬变适用于最大均方根电流的低ESR输入电容器必须使用。最大均方根电容电流由:

注意,电容器制造商的纹波电流额定值为通常只基于2000小时的生命。因此,建议进一步降低电容器的额定值,或选择额定温度高于要求的电容器。多个电容器可以并联放置,以满足设计中的尺寸或高度要求。在本例中,输入电容器组由三个2200μF、16 V Nichicon电容器组成,每个电容器的纹波电流额定值为3.5 a。

为了将输入电流di/dt降低到低于建议的最大值0.1 A/μs,应在转换器和sup-ply总线之间插入一个附加的小电感(L>1μH@15 A)。该电感器还充当转换器和主电源之间的滤波器。

ADP3166的调谐程序

1、基于从设计电子表格计算的补偿值构建电路。

2、将直流负载连接到电路上,将其打开,并检查其工作情况。同时检查空载和满载时的抖动。

直流负载线设置

3、测量空载时的输出电压(VNL)。确认其在公差范围内。

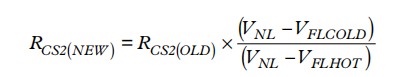

4、测量满载冷态(VFLCOLD)下的输出电压。让电路板在满载状态下设置约10分钟,然后测量输出(VFLHOT)。如果变化超过几毫伏,使用公式35和37调整RCS1和RCS2。

5、重复步骤4,直到冷电压和热电压测量值保持不变。

6、用5 A步测量从空载到满载的输出电压。计算每个变化的载重线坡度,然后对其进行平均,得到总载重线坡度(ROMEAS)。

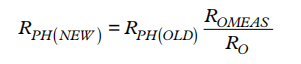

7、如果ROMEAS从RO关闭超过0.05 mΩ,使用公式36调整RPH值:

8、重复步骤6和7检查载重线,必要时重复调整。

9、完成直流载重线调整后,在其余步骤中不要更改RPH、RCS1、RCS2或RTH。

10、用示波器测量空载和满载时的输出纹波,并确保其在规定范围内。

交流载重线设置

11、从电路中移除直流负载并连接动态负载。

12、将示波器连接到输出电压,并将其设置为直流耦合,时间刻度为100微秒/分。

13、在1 kHz和50%占空比下,将动态负载设置为大约24 a的瞬态阶跃。

14、测量输出波形(可能需要使用示波器上的直流偏移量来查看波形)。尝试使用100 mV/div或更精细的垂直刻度。

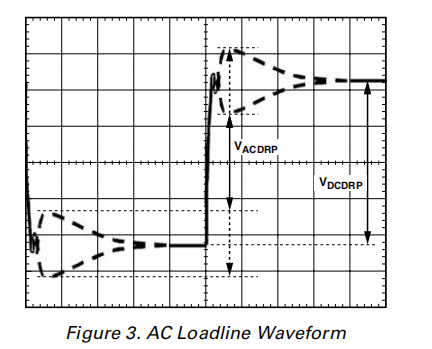

15、波形应该类似于图3。使用水平光标测量VACDRP和VDCDRP,如图所示。不要测量步骤后立即发生的下冲或过冲。

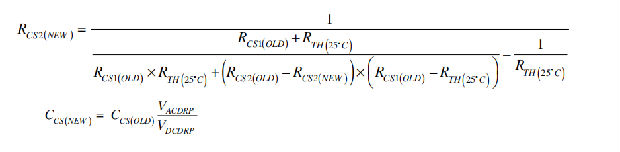

16、如果VACDRP和VDCDRP相差超过几毫伏,使用以下方法调整CCS。由于可用的标准电容值有限,因此可能需要并联不同的值以获得正确的值。(在布局中为两个电容器设置位置是个好主意。)

17、重复步骤11至13,必要时重复调整。一旦完成,不要在程序的其余部分更改CCS。

18、将动态加载步长设置为最大步长(不要使用大于所需步长的步长),并验证输出波形是否为方形(表示VACDRP和VDCDRP相等)。

初始瞬态整定

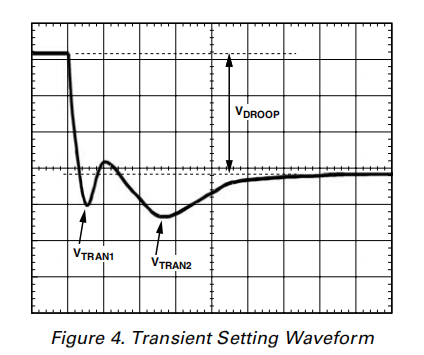

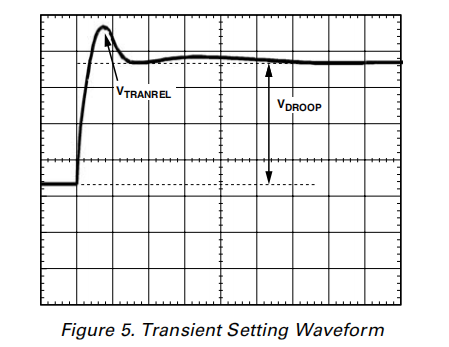

19、在动态负载仍设置为最大步长的情况下,将范围时间刻度扩展到2微秒/分到5微秒/分。波形可能有两个过冲和一个小过冲(见图5)。这里,VDROOP是最终所需的静态值。

20、如果过冲大于期望值,请尝试按此顺序进行以下调整(注意:如果这些调整不改变响应,则受输出解耦的限制)。每次进行更改时检查输出响应以及交换节点(以确保其仍然稳定)。

a、使斜坡电阻增大25%(RRAMP)。

b、对于VTRAN1,增加CB或开关频率。

c、对于VTRAN2,增加RA,减少CA 25%。

21、对于负载释放(见图5),如果VTRANREL大于VTRAN1(见图4),则没有足够的输出电容。要么需要更多的电容,要么需要使电感值更小(如果电感发生变化,则需要重新开始使用电子表格和本调整指南进行设计)。

布局和零部件放置

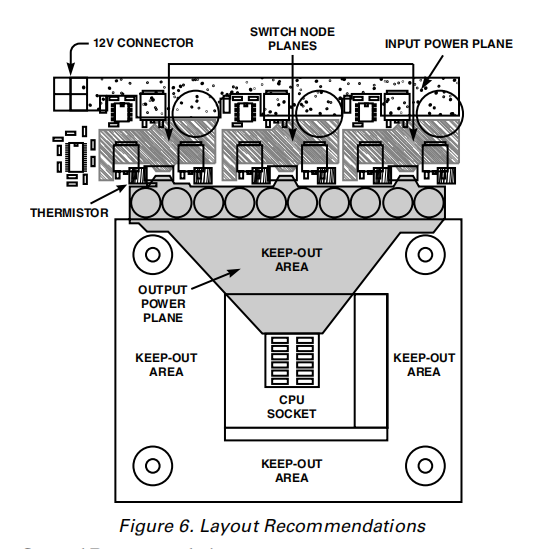

为使PC系统中的开关调节器达到最佳性能,建议采用以下指南。关键的布局问题如图6所示。

一般性建议

•为了获得良好的效果,建议至少使用四层印刷电路板。这应允许所需的多功能性,用于控制电路互连和优化布置,电源平面用于接地,输入和输出功率,以及在剩余的功率传输电流路径中的宽互连轨迹。请记住,在室温下,每平方单位1盎司铜痕的电阻约为0.53 mΩ。•当高电流必须在PCB层之间布线时,应充分使用过孔来创建多个平行电流路径,以便将这些电流路径引入的电阻和电感最小化,并且不超过过孔电流额定值。

•如果关键信号线(包括ADP3166的输出电压检测线)必须穿过电源电路,最好在这些信号线和电源电路的轨迹之间插入一个信号接地平面。这起到了屏蔽作用,以减少信号中的噪声注入,同时降低信号接地的噪声。•应在ADP3166周围和下方使用模拟接地平面,以参考与控制器相关的组件。该平面应与最近的输出去耦电容器接地相连,且不应与任何其他电源电路相连,以防止电源电流流入其中。

•ADP 3166周围的部件应靠近控制器,并留有短痕迹。最重要的记录道是FB和CSSUM引脚,以保持短距离和远离其他记录道。有关CSSUM节点布局的更多详细信息,请参阅图6。

•输出电容器应尽可能靠近接收电源的负载(或连接器)(例如微处理器芯)。如果负载是分布的,电容器也应该是分布的,并且通常与负载趋向于更动态的地方成比例。•避免越过开关电源路径回路上的任何信号线,如下所述。

电源电路

•开关电源路径应在PCB上布线,以包含尽可能短的长度,以最小化电路板中的辐射开关噪声能量(即EMI)和传导损耗。如果不采取适当的预防措施,通常会导致整个PC系统的EMI问题以及功率转换器控制电路中的噪声操作问题。开关电源路径是电流路径通过输入电容器和功率mosfet形成的回路,包括所有互连的PCB轨迹和平面。在这条线路中,使用短而宽的互连线路尤为重要,原因有两个:它使开关回路中的电感最小化,从而导致高能量振铃;它以最小的电压损失满足高电流需求。

•无论何时将功率耗散元件(如功率MOSFET)焊接到PCB上,建议直接在安装板上及其周围自由使用过孔。两个重要的原因是通过过孔的电流额定值提高,以及从过孔延伸到PCB的另一侧的热性能提高,在那里,一个平面可以更容易地将热量传递到空气中。制作一个镜像的任何垫被用来热沉在印刷电路板的另一边的mosfet,以实现对电路板周围空气的最佳散热。为了进一步提高热性能,应使用尽可能大的焊盘面积。

•输出功率路径也应包括短距离。输出功率路径由通过电感、输出电容器和负载的电流路径形成。

•为了最好地抑制电磁干扰,应使用固体电源接地平面作为所有电源部件下完全延伸的内层之一。

信号电路

•输出电压在FB引脚和FBRTN引脚之间感应和调节,FBRTN引脚连接到负载的信号接地。为避免感应信号中的差模噪声拾取,回路面积应较小。因此,FB和FBRTN记录道应在电源接地平面顶部彼此相邻地路由回控制器。•来自开关节点的反馈轨迹应尽可能靠近电感器。CSREF信号应连接到离控制器最近的电感的输出电压。

外形尺寸