WM8782点击型号即可查看芯片规格书

说明

WM8782是一款高性能、低成本的立体声音响为可记录媒体应用程序设计的ADC。

该设备提供立体声线路电平输入和两个控制输入管脚(格式,IWL),允许操作三种行业标准模式的音频接口。一个内部运算放大器集成在芯片前端适应大于1Vrms的模拟输入信号。

该装置还有一个高通滤波器,用于去除残余物直流偏移。

WM8782提供主模式或从模式时钟方案。

控制输入引脚M/S用于允许从模式操作或主模式操作。根据采样率,立体声24位多位sigma-delta ADC用于128x、64x或32x过采样。数字音频输出16-24位的字长和采样率支持8kHz到192kHz。

设备是硬件控制的设备在一个20-SSOP的包裹里。

特征

•信噪比102dB('A'加权@48kHz)

•THD-90分贝(at-1分贝)

•采样频率:8–192kHz

•主从时钟模式

•系统时钟(MCLK):128fs、192fs、256fs、384fs、512fs,768英尺

•音频数据接口模式

-16-24位I2S、 16-24位左对齐,16-24位右对齐

•电源电压

-模拟2.7至5.5V

-数字核心:2.7V至3.6V

•20针SSOP封装

应用

•可录制DVD播放机

•个人录像机

•机顶盒

•录音室音频处理设备

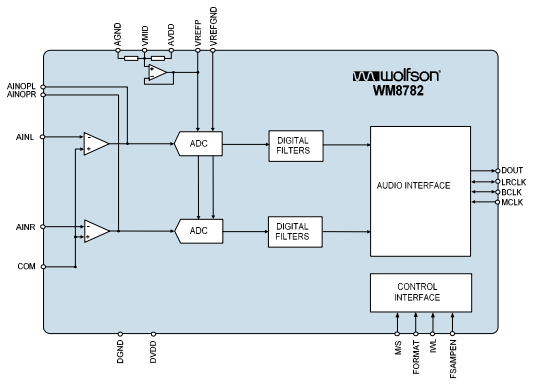

方块图

设备描述

导言

WM8782是一款24位立体声ADC,专为DVD等高要求的录音应用而设计录音机、录音室混音器、PVR和AV放大器。WM8782由立体声线路电平输入组成,然后是sigma-delta调制器和数字滤波。

该设备提供立体声线路电平输入和两个控制输入引脚(格式,IWL),以允许以三种行业标准模式(左对齐、右对齐或I2)操作音频接口S) 是的。

芯片前端集成了一个内部运算放大器,以适应模拟输入信号大于1Vrms。该装置还具有高通滤波器以去除残余的直流偏移。

WM8782提供主模式或从模式时钟方案。控制输入引脚M/S用于允许从模式或主模式操作。WM8782支持从128fs到768fs和16-24位数字音频输出字长。从8kHz到192kHz的采样率为支持,根据采样率。

线路输入通过运算放大器内部偏置到VMID。

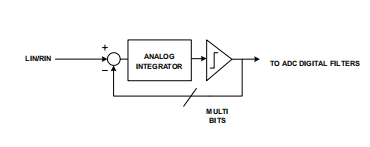

模数转换器WM8782使用多位过采样sigma-delta ADC。ADC的单通道是如图所示,多位过采样Sigma-Delta ADC示意图

多位过采样Sigma-Delta ADC原理图多比特反馈和高过采样率的使用减少了抖动和高频率噪声。

在AVDD=5.0伏时,ADC满标度输入为1.0V rms。任何大于满标度的电压都会可能会使ADC过载并导致失真。注意满标度输入具有线性关系与AVDD。内部运放和适当的电阻可以用来减少信号更大在到达ADC之前超过1Vrms。

ADC滤波器执行真正的24位信号处理,以转换原始的多位过采样数据从ADC到数字音频接口上输出的正确采样频率。

模数转换器数字滤波器ADC数字滤波器包含数字高通滤波器。高通滤波器响应在数字滤波器特性。高通滤波器的工作消除了出现在音频信号上。

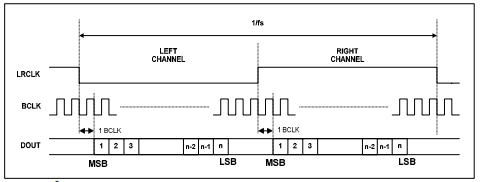

音频数据格式

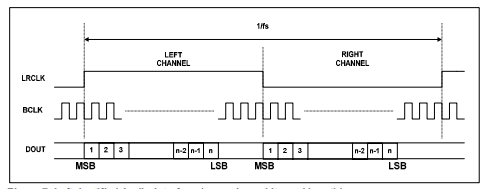

在左对齐模式下,在LRCLK之后的BCLK的第一个上升沿上可以使用MSB过渡。然后按顺序发送LSB之前的其他位。根据字长,BCLK频率和采样率,在每个LRCLK转换之前可能有未使用的BCLK循环。

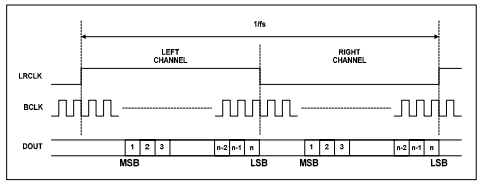

图左对齐音频接口(假定n位字长)在右对齐模式下,在LRCLK之前的BCLK的最后一个上升沿上可以使用LSB过渡。所有其他位在(MSB优先)之前传输。根据字长,BCLK频率和采样率,在每次LRCLK转换后可能有未使用的BCLK循环。

图右对齐音频接口(假定n位字长)

S模式下,MSB在LRCLK转换后的BCLK的第二上升沿上可用。然后按顺序发送LSB之前的其他位。根据字长,BCLK频率和采样率,一个采样的LSB和下一个的MSB。

图S对正音频接口(假定n位字长)

主时钟和音频采样率

在典型的数字音频系统中,只有一个中央时钟源产生参考时钟所有音频数据处理都是同步的。这个时钟通常被称为音频系统的主时钟(MCLK)。外部主系统时钟可通过MCLK直接应用输入引脚。在一个有许多可能的参考时钟源的系统中建议使用抖动最低的时钟源来优化ADC。

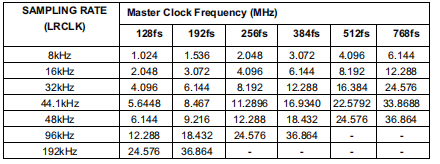

主时钟用于操作数字滤波器和噪声整形电路。WM8782支持128fs、192fs、256fs、384fs、512fs和768fs的主时钟,其中fs是音频采样频率(LRCLK)。在从属模式下,WM8782自动检测音频样本速度。在主模式下,为速率256fs生成LRCLK,除非用户将其更改为128fs使用FSAMPEN pin=z(见下表7)。BCLK也在主模式下生成。

对于256fs,BCLK=MCLK/4;对于128fs,BCLK=MCLK/2。

表显示了不同采样率下的常见MCLK频率

主时钟频率选择

在从模式下,WM8782有一个主检测电路,自动确定主时钟频率与采样率之间的关系(在+/-32系统内时钟)。如果存在大于32个时钟的错误,接口会将自身设置为可用的最高速率(768英尺)。每个LRCLK必须有固定数量的mclk,尽管WM8782允许这些时钟上的相位变化或抖动。

WM8782可以在8kHz到192kHz的采样率下工作。WM8782使用sigma delta在6.144MHz的固定频率下工作的调制器(48kHz时128 x LRCLK过采样采样率)。为了设备的正确操作和最佳性能,用户必须设置适当的ADC调制器采样率启用。在主模式和从模式下建议对于96kHz用户将FSAMPEN设置为1,对于192kHz用户将FSAMPEN设置为z主模式192kHz,要求将FSAMPEN设置为z。

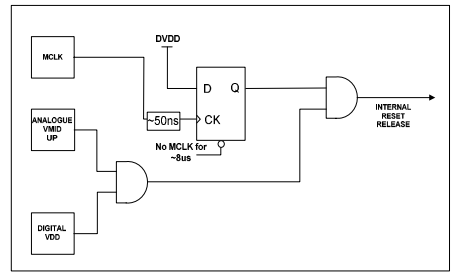

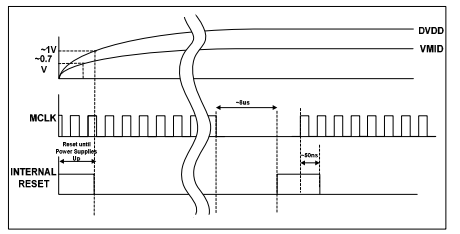

上电复位

WM8782具有内部通电复位电路。在通电或打开电源。在内部重置被移除之前,DOUT被强制为零。

10上电复位图

上电复位定时

应用程序信息

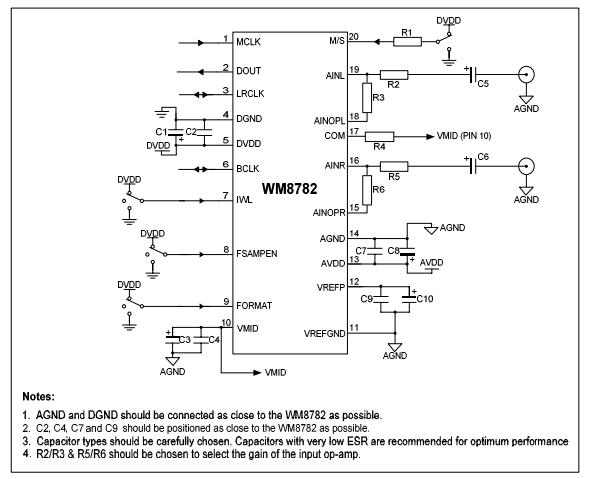

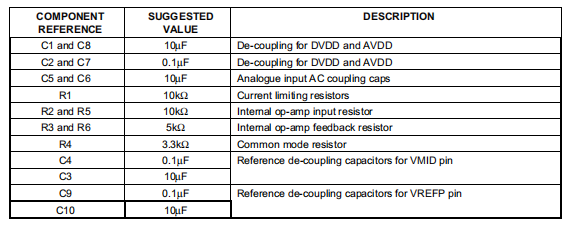

推荐的外部组件

外部组件图

推荐的外部组件值

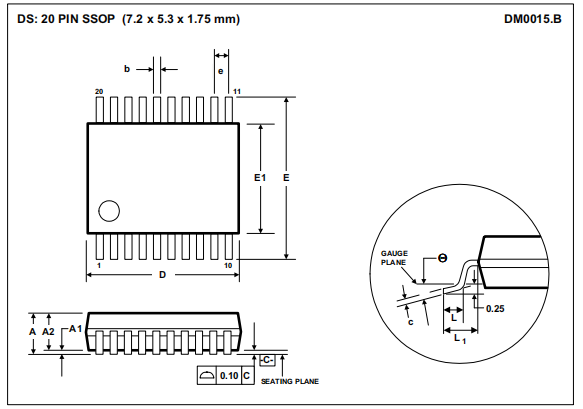

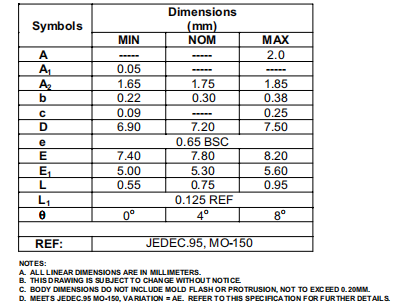

包装尺寸

重要通知

Wolfson Microelectronics plc(WM)保留对其产品进行更改或停止任何产品或未经通知的服务,并建议客户在放置之前获取最新版本的相关信息以进行验证命令,所依赖的信息是最新的。所有产品均按WM销售条款和条件销售在订单确认时提供,包括与保证、专利侵权和限制有关的责任。

WM保证其产品的性能符合WM在销售时适用的规范标准保修。在WM认为有必要支持的范围内,使用测试和其他质量控制技术这个保证。不必对每个设备的所有参数进行特定测试,除非政府要求。

为了将与客户应用相关的风险降到最低,必须使用适当的设计和操作保护措施由客户尽量减少固有或程序性危害。Wolfson产品未被授权作为关键产品使用未经公司高管明确书面批准的生命支持设备或系统中的组件。生活支撑装置或系统是指用于外科植入体内的装置或系统,或支撑或维持生命,并且当按照所提供的使用说明正确使用时,其无法执行,可以合理预期会对用户造成重大伤害。关键部件是生命支持的任何部件不能正常运行的装置或系统,可能导致生命支持装置或或影响其安全性或有效性。

WM对应用程序协助或客户产品设计不承担任何责任。WM不保证也不代表任何明示或默示的许可,是根据任何专利权、版权、面具作品权或其他知识产权授予的WM的财产权,涵盖或涉及任何组合、机器或过程,在这些组合、机器或过程中,这些产品或服务可能被使用或被使用。WM发布任何第三方产品或服务的信息不构成WM的批准、许可、保证或背书。

只有在没有更改和随附所有相关保证、条件、限制和通知。本文件的陈述或复制更改后的信息将使为相关WM产品或服务提供的所有保证无效,是不公平和欺骗性的商业惯例,WM不对任何此类使用负责。

转售WM的产品或服务,声明与WM规定的参数不同或不同产品或服务使相关WM产品或服务的所有明示和暗示保证无效,是不公平的,并且具有欺骗性的商业行为,WM不对任何此类使用负责。