ADSP-21469点击型号即可查看芯片规格书

相关信号链

信号链是一系列信号调节电子元件,它们接收输入(从采样实时现象或从存储数据中获取的数据),并将链的一部分的输出提供给下一部分。信号链通常用于信号处理应用中,以收集和处理数据或应用基于实时现象分析的系统控制。有关此术语和相关主题的更多信息,请参阅维基百科中的“信号链”条目或模拟设备网站上的EE术语表。

模拟设备通过提供设计为能够很好地协同工作的信号处理组件来简化信号处理系统的开发。查看特定应用程序和相关组件之间关系的工具可在网站上找到。

实验室网站(/Signal Chains)电路中的“应用信号链”页面提供:

•各种电路类型和应用的信号链图形电路框图;

•从每个链中的组件向下钻取到选择指南和应用程序信息;

•采用最佳实践设计技术的参考设计。

总功耗

本节中的信息应增加ADSP-214xx SHARC处理器(EE-348)的估计功率。总功耗由两部分组成:

1. 内部功耗还包括两个组件:

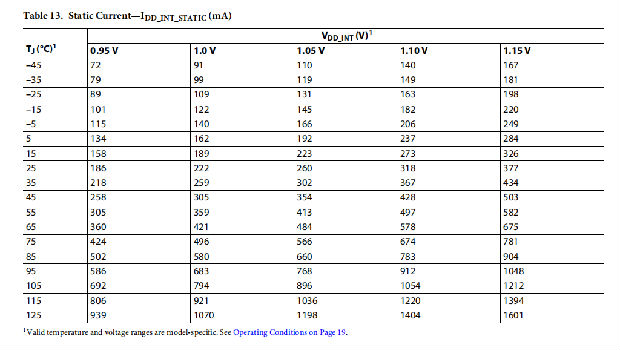

•泄漏产生的静态电流。表13显示了静态电流消耗(IDD_INT_static)作为结温(TJ)和芯电压(VDD_INT)的函数。

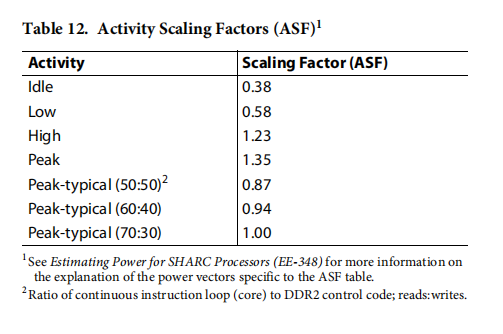

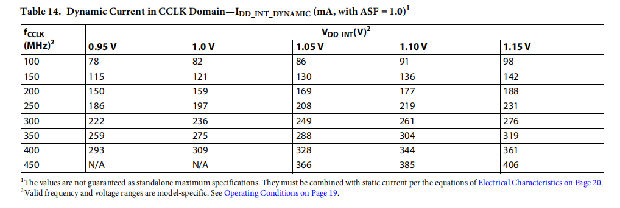

•由于晶体管开关特性和处理器的活动水平而产生的动态电流(IDD_INT_Dynamic)。活动级别由活动缩放因子(ASF)反映,ASF表示在处理器核心上运行的应用程序代码的活动级别,具有不同级别的外围和外部端口活动(表12)。动态电流消耗是通过选择与用户应用最接近的ASF,然后将其乘以动态电流消耗来计算的(表14)。

2. 外部功耗是由外部引脚的开关活动引起的。

绝对最大额定值

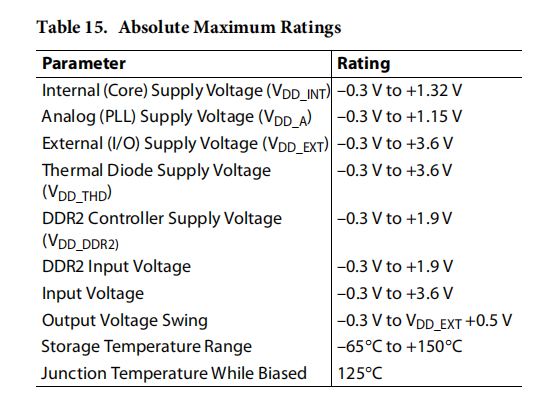

应力大于表15中列出的应力可能导致设备永久损坏。这些只是应力额定值;设备的功能操作这些或任何其他条件大于本规范操作章节中所示的条件并不意味着。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

包信息

图4和表16中显示的信息提供了有关处理器的包品牌的详细信息。有关产品可用性的完整列表,请参阅第74页的订购指南。

定时规格

使用给定的精确计时信息。不要试图从其他的加减运算中得到参数。虽然加法或减法会对单个设备产生有意义的结果,但本数据表中给出的值反映了统计变化和最坏情况。因此,添加参数以获得更长的时间是没有意义的。

在以下部分中,切换特性指定处理器如何更改其信号。处理器外部的电路必须设计为与这些信号特性兼容。开关特性描述了处理器在给定的环境下会做什么。使用开关特性来确保连接到处理器(如存储器)的设备的任何定时要求得到满足。

在以下各节中,时序要求适用于由处理器外部电路控制的信号,例如用于读取操作的数据输入。时序要求保证处理器与其他设备一起正常工作。

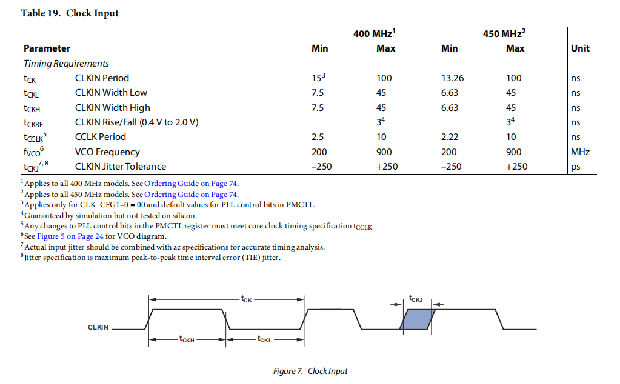

核心时钟要求

处理器的内部时钟(CLKIN的倍数)为内部存储器、处理器核心和串行端口定时提供时钟信号。在复位期间,用CLK U CFG1–0引脚编程处理器的内部时钟频率和外部(CLKIN)时钟频率之间的比率。

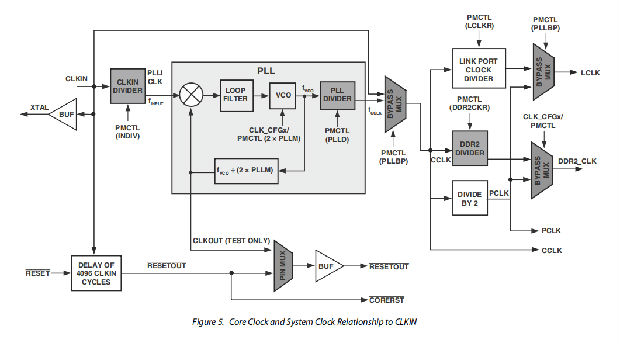

处理器的内部时钟切换频率高于系统输入时钟(CLKIN)。为了产生内部时钟,处理器使用内部锁相环(PLL,见图5)。这种基于PLL的时钟最小化了系统时钟(CLKIN)信号和处理器内部时钟之间的偏差。

压控振荡器

在应用设计中,PLL倍增值的选择应确保VCO频率不超过表19中规定的fVCO。

•如果输入分配器未启用(INDIV=0),则CLKIN和PLLM的乘积不得超过表19中fVCO(max)的1/2。

•如果输入分配器启用(INDIV=1),则CLKIN和PLLM的乘积不得超过表19中的fVCO(max)。

VCO频率计算如下:

式中:fVCO=VCO输出PLLM=在PMCTL寄存器中编程的倍增值。

在复位过程中,PLLM值由硬件中使用CLK_CFG管脚选择的比率导出。

PLLD=基于PMCTL寄存器上编程的PLLD值的除法器值2、4、8或16。重置期间,该值为2。

fINPUT=PLL的输入频率当输入分配器被禁用时,fINPUT=CLKIN,或当输入分配器启用时,fINPUT=CLKIN2

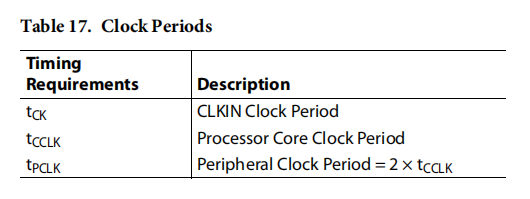

注意时钟周期的定义,时钟周期是CLKIN的函数,适当的比率控制如和表17所示。所有外围设备的定时规范都是根据tPCLK定义的。有关每个外围设备的定时信息,请参阅外围设备特定部分。

图5显示了与外部振荡器或晶体的核心到核心的关系。阴影分频器/乘法器块表示哪里可以使用电源管理控制寄存器(PMCTL)通过硬件或软件设置时钟比率。有关详细信息,请参阅ADSP-214xx SHARC处理器硬件参考。

通电顺序

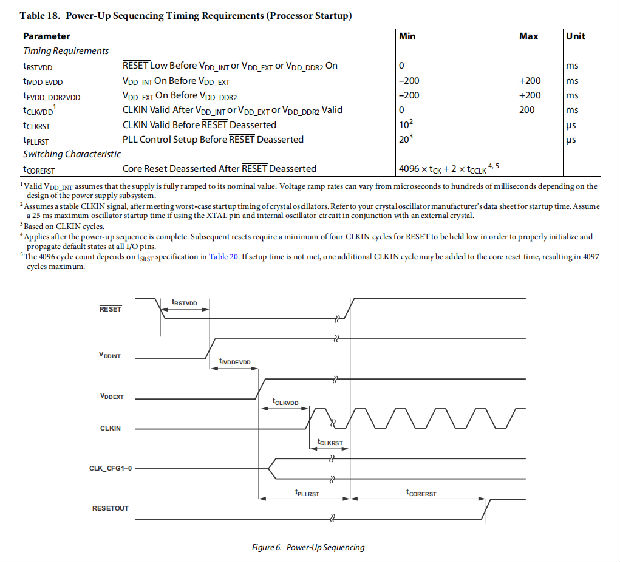

处理器启动的时间要求见表18。虽然在VDD_EXT、VDD_DDR2和VDD_INT之间不需要特定的通电顺序,但系统设计应考虑一些因素。

•在另一个电源开始之前,不应长时间(大于200 ms)通电加强。

•如果VDD_INT电源在VDD_EXT、任何管脚之后接通,例如RESETOUT和RESET,实际上可能会在VDD_INT rail通电之前暂时驱动。

在板上共享这些信号的系统必须确定是否有任何问题需要基于这种行为来解决。

注意,在通电过程中,当VDD_INT电源在VDD_EXT之后接通时,可以观察到三态泄漏电流上拉、下拉顺序的泄漏电流任何管脚,即使该管脚仅为输入(例如复位管脚),直到VDD_INT rail通电。

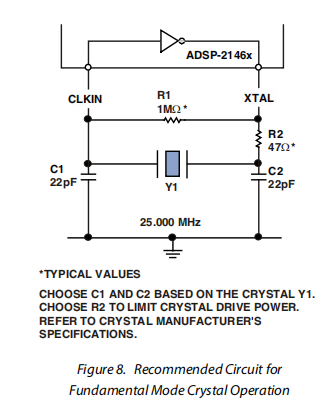

时钟输入

时钟信号

处理器可以使用外部时钟或晶体。参见表10中的CLKIN引脚说明。程序可以通过将必要的组件连接到CLKIN和XTAL来配置处理器以使用其内部时钟生成器。图8显示了在基本模式下工作的晶体所使用的组件连接。请注意,时钟速率是使用25 MHz晶体和16:1的PLL倍频比实现的(CCLK:CLKIN实现400 MHz的时钟速率)。

为了达到全核心时钟速率,程序需要在PMCTL寄存器中配置乘法器位。

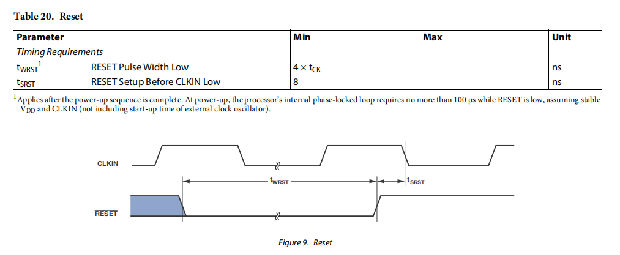

重置

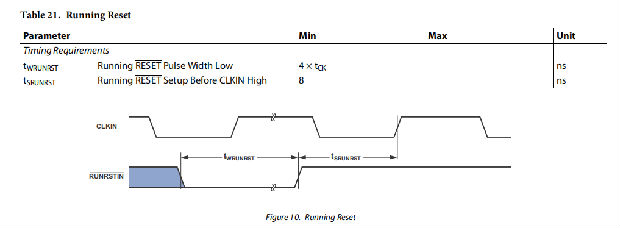

运行复位

当配置为RUNRSTIN时,以下计时规范适用于RESETOUT/RUNRSTIN管脚。

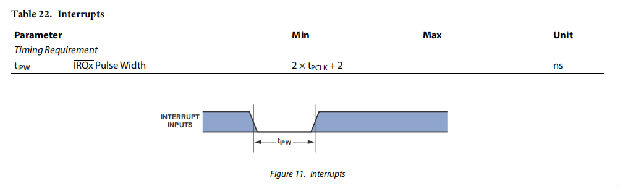

中断

以下计时规范适用于标志0,FLAG1和FLAG2引脚配置为IRQ0时,IRQ1和IRQ2中断,以及DAI_P20–1和DPI_P14–1管脚(当它们配置为中断时)。

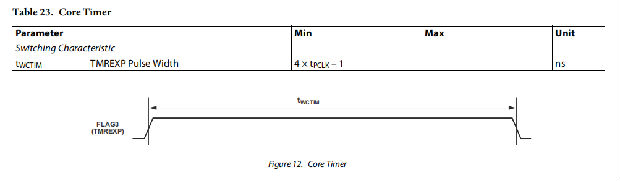

核心计时器

当FLAG3配置为核心计时器(TMREXP)时,以下计时规范适用于它。

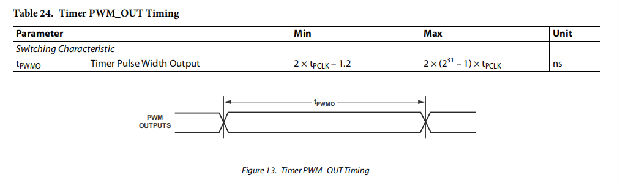

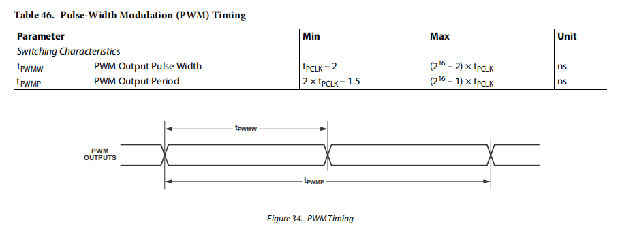

定时器脉冲宽度调制输出周期定时

以下计时规范适用于计时器0和定时器1处于PWM输出(脉冲宽度调制)模式。定时器信号通过DPI SRU路由到DPI_P14–1引脚。因此,下面提供的正时规范在DPI_P14–1引脚处有效。

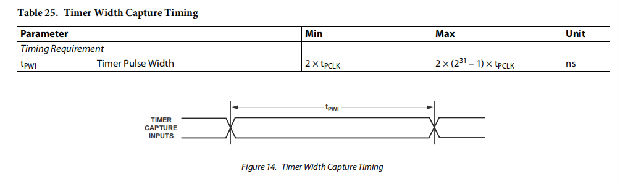

定时器定时

以下定时规范适用于WDTH U CAP(脉冲宽度计数和捕获)模式下的定时器0和定时器1。

定时器信号通过SRU被路由到DPI_P14–1引脚。因此,下面提供的正时规范在DPI_P14–1引脚处有效。

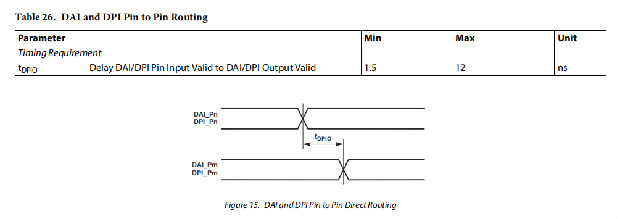

针对针直接布线(DAI和DPI)

仅用于直接管脚连接(例如DAI_PB01_I到DAI_PB02_O)。

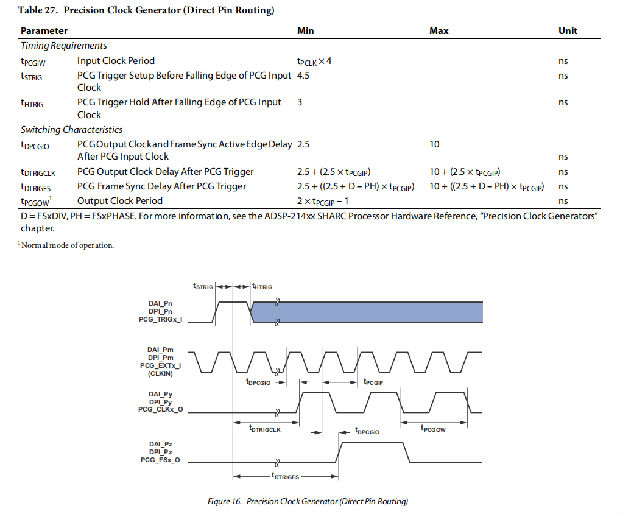

精密时钟发生器(直接管脚布线)

只有当SRU被配置成精密时钟发生器(PCG)直接从DAI管脚(通过管脚缓冲器)接收其输入并将其输出直接发送到DAI管脚时,该定时才有效。对于其他情况,PCG输入和输出没有直接路由到DAI管脚/从DAI管脚(通过管脚缓冲器)没有可用的定时数据。所有定时参数和开关特性均适用于外部DAI引脚(DAI_P01–DAI_P20)。

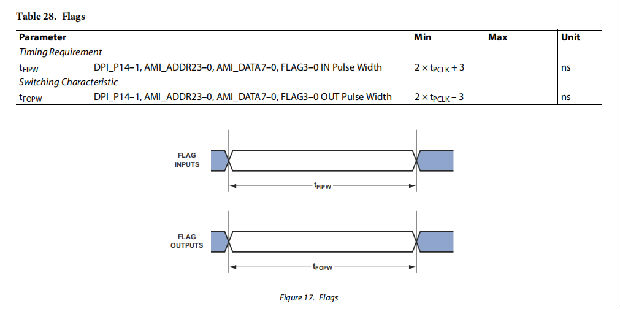

Flags

下面提供的计时规范适用于当配置为标志时,AMI-ADDR23-0和AMI-DATA7-0。有关标志使用的更多信息,请参见第14页的表10。

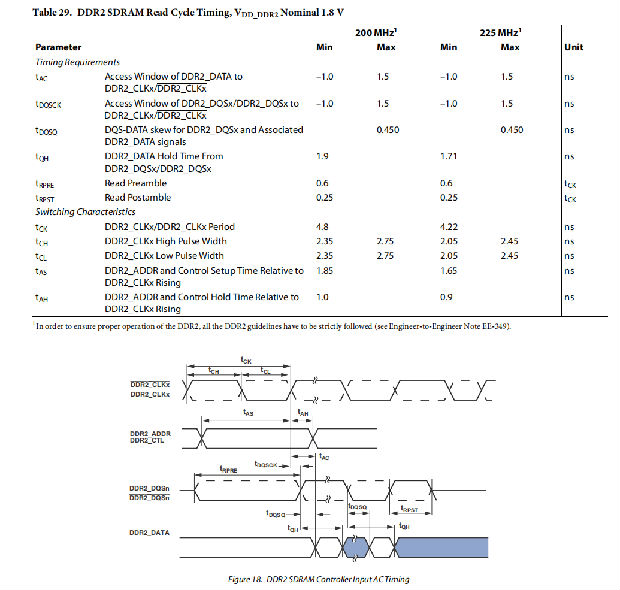

DDR2 SDRAM读取周期计时

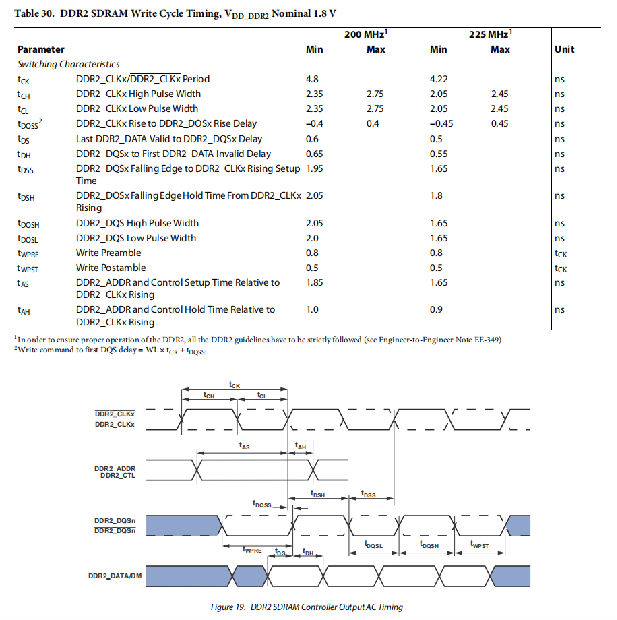

DDR2 SDRAM写入周期计时

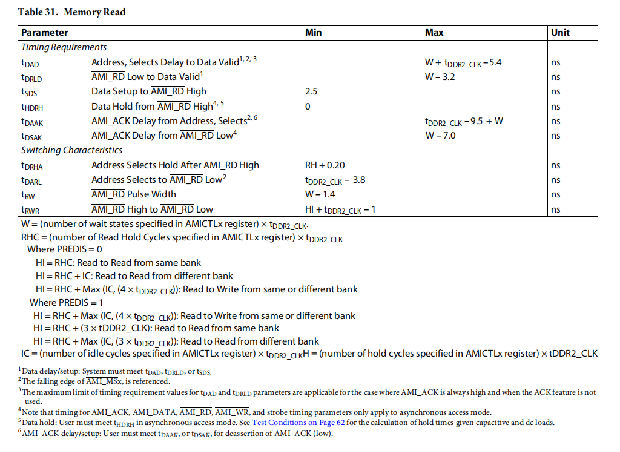

AMI读取

将这些规范用于异步接口-瑞斯。注意,AMI-ACK、AMI-DATA、AMI-RD的计时,AMI_WR和选通时序参数仅适用于异步访问模式。

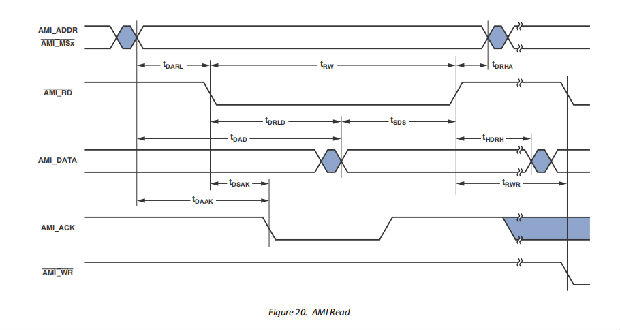

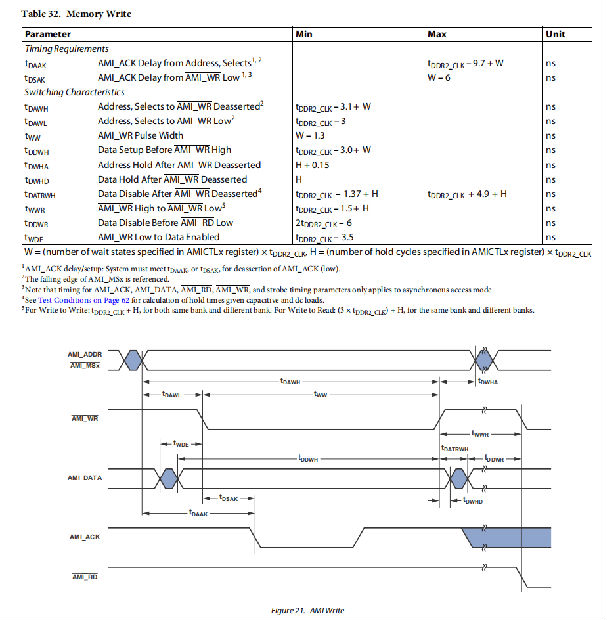

AMI写入

将这些规范用于异步接口-瑞斯。注意,AMI-ACK、AMI-DATA、AMI-RD的计时,AMI_WR和选通时序参数仅适用于异步访问模式。

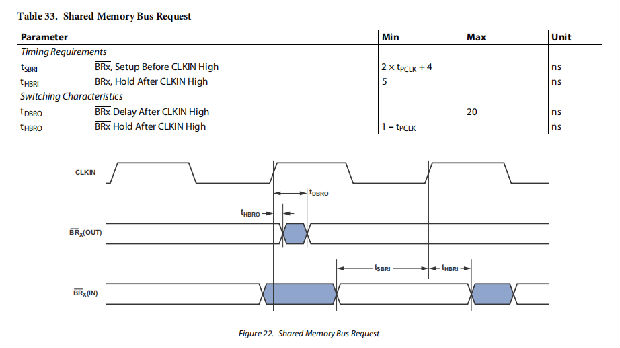

共享内存总线请求

使用这些规范在处理器(BRx)之间传递总线主控。

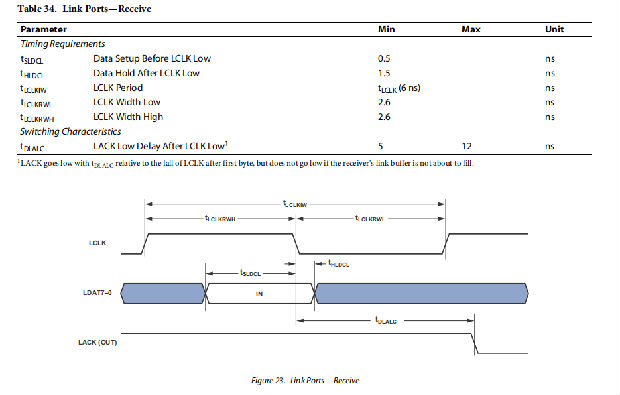

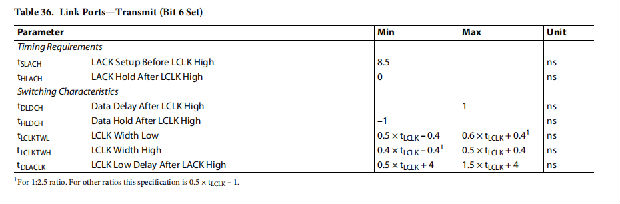

链接端口

为了确定LDATA和LCLK之间的传输路径长度差中可以引入的最大允许偏差,需要计算链路接收器的数据设置和相对于链路时钟的保持。设置倾斜是最大值相对于LCLK,LDATA中可能引入的延迟:(设置偏差=tLCLKTWH min–tDLDCH–tSLDCL)。Hold skew是LCLK中相对于LDATA可以引入的最大延迟:(Hold skew=tLCLKTWL min–tHLDCH–tHLDCL)。

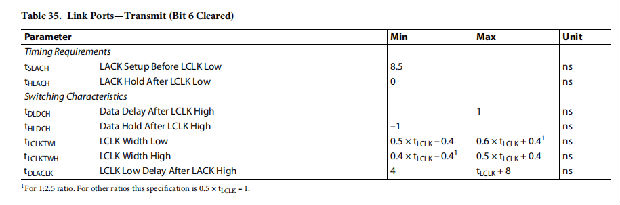

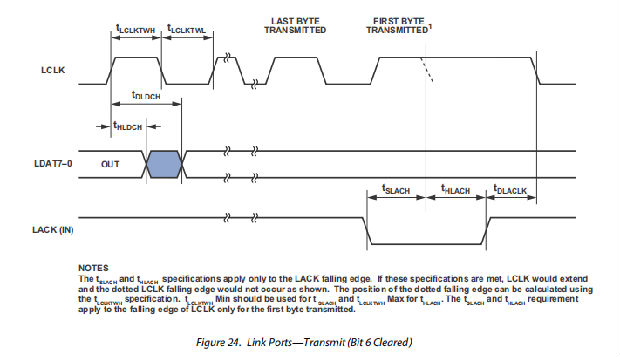

当LSYNC_EN位(LCTLx寄存器中的位6)被清除时,表35中的数据和图24中的定时信息适用。

当设置LSYNC_EN位(LCTLx寄存器中的位6)时,表36中的数据和图25中的定时信息适用。

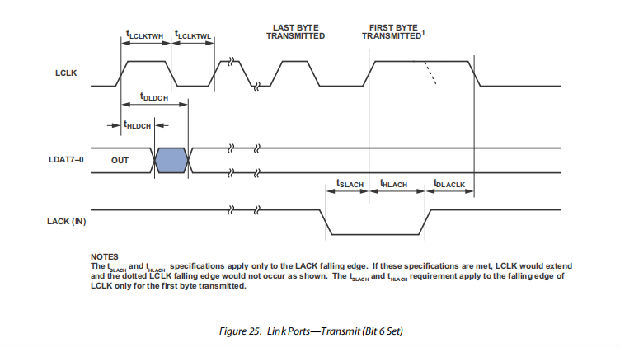

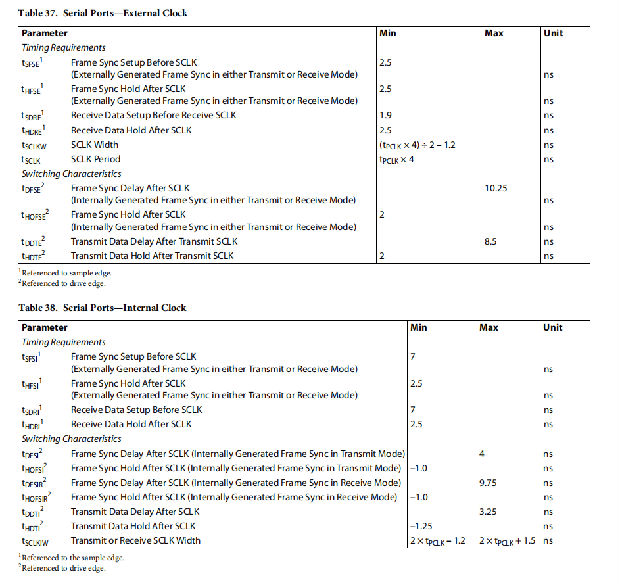

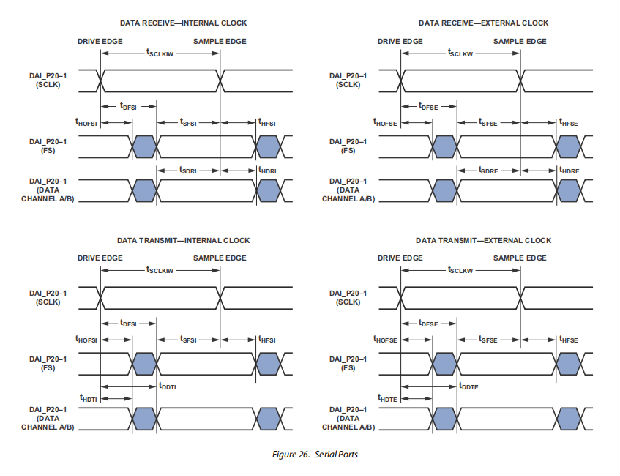

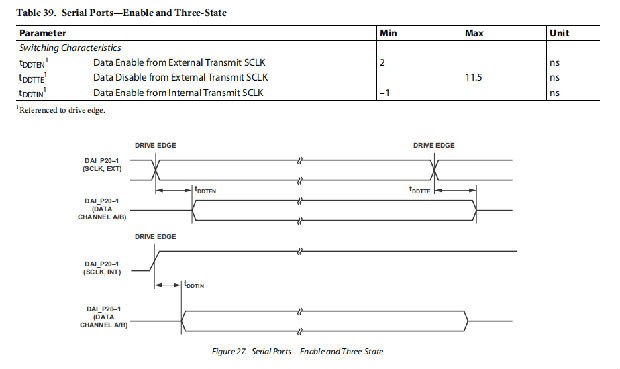

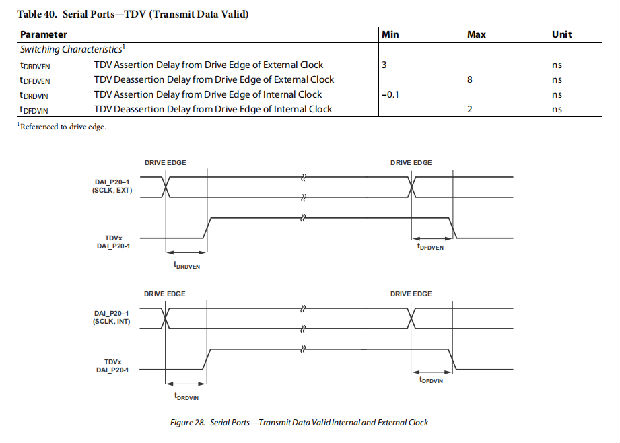

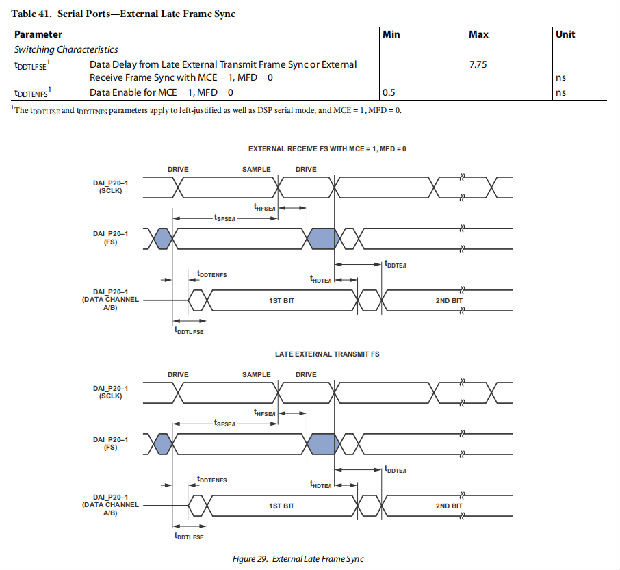

串行端口

在从发射机模式和主接收机模式下,最大串行端口频率为fPCLK/8。要确定两个设备之间是否可以以时钟速度n进行通信,必须确认以下规范:1)帧同步延迟和帧同步设置和保持,2)数据延迟和数据设置和保持,以及3)串行时钟(SCLK)宽度。

串行端口信号使用SRU路由到DAI_P20–1引脚。因此,下面提供的正时规范在DAIúU P20–1引脚上有效。在图26中,SCLK的上升沿或下降沿(外部或内部)可以用作活动采样边。

SPORTx_TDV_O输出信号(布线单元)在运动多声道模式下激活。在传输时隙期间(使用有源信道选择寄存器启用)SPORTx_TDV_O用于与外部设备通信。

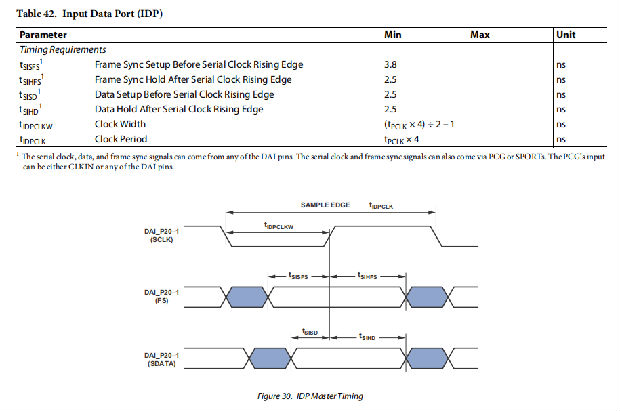

输入数据端口(IDP)

表42给出了IDP的定时要求。IDP信号使用SRU路由到DAI_P20–1管脚。因此,下面提供的正时规范在DAIúU P20–1引脚上有效。

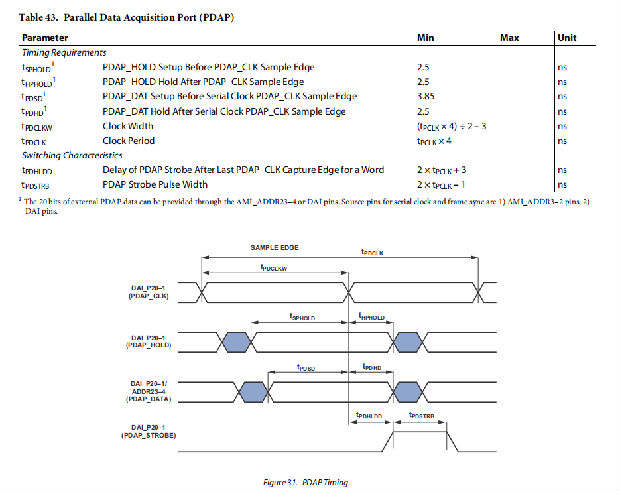

并行数据采集端口(PDAP)

PDAP的时间要求见表43。PDAP是IDP的信道0的并行模式操作。

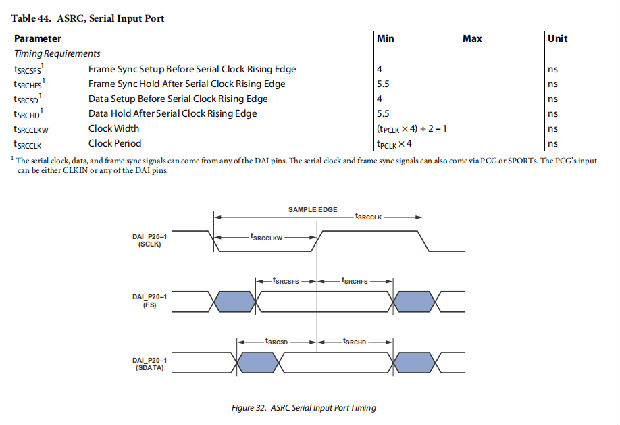

采样率转换器串行输入端口

ASRC输入信号使用SRU从DAIúU P20–1引脚路由。因此,表44中提供的定时规格在DAIúU P20–1引脚处有效。

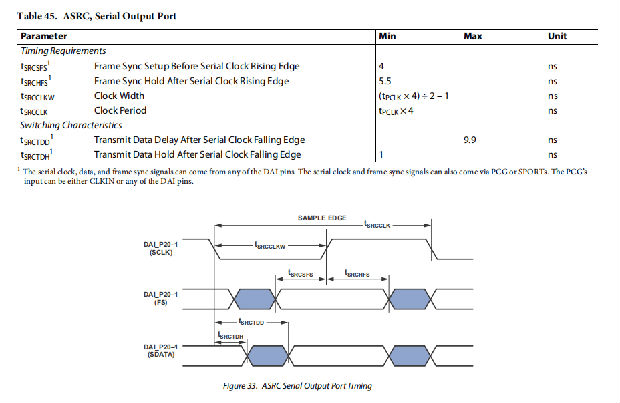

采样率转换器串行输出端口

对于串行输出端口,帧同步是一个输入,它应该满足与输出端口上的串行时钟有关的设置和保持时间。串行数据输出有一个保持时间和关于串行时钟的延迟规范。注意,串行时钟上升沿是采样沿,下降沿是驱动器沿。

脉冲宽度调制(PWM)发生器

当AMI-ADDR23–8引脚配置为PWM时,以下计时规范适用。

S/PDIF发射机

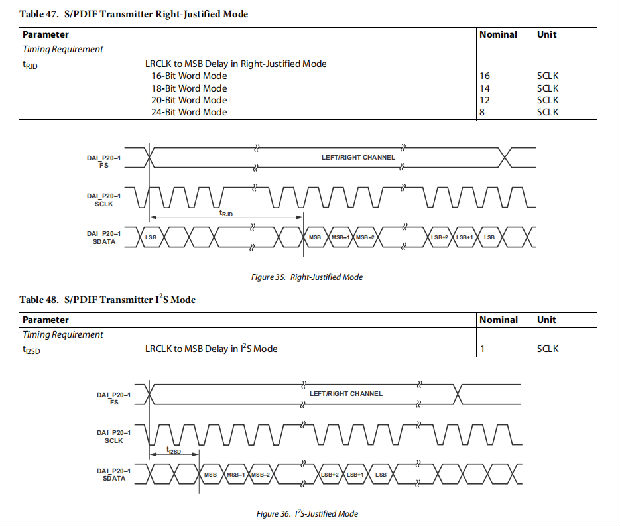

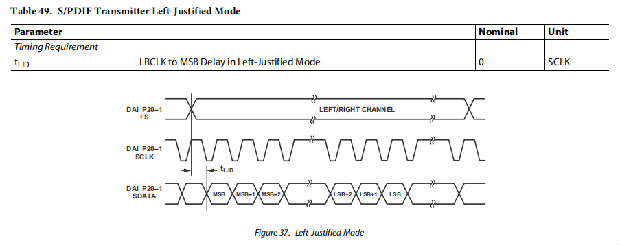

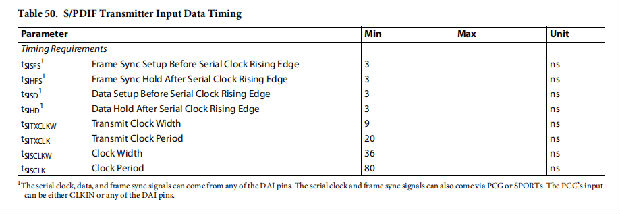

输入到S/PDIF发射机的串行数据可以格式化为左对齐、I2S或右对齐,字宽为16、18、20或24位。以下各节为发射机提供定时。

S/PDIF发射机串行输入波形

图35显示了右对齐模式。左声道的LRCLK为高,右声道的LRCLK为低。数据在串行时钟上升沿有效。可以看出,在24位输出模式下,MSB最小延迟,在16位输出模式下,MSB最大延迟。

一种LRCLK转换,当每个LRCLK周期有64个串行时钟周期时,数据的LSB将右对齐到下一个LRCLK转换。

图36显示了默认的I2S调整模式。左声道的LRCLK低,右声道的LRCLK高。数据在串行时钟上升沿有效。MSB左对齐为LRCLK转换,但有延迟。

图37显示了左对齐模式。左声道的LRCLK为高,右声道的LRCLK为低。数据在串行时钟上升沿有效。MSB左对齐为LRCLK转换,没有延迟。

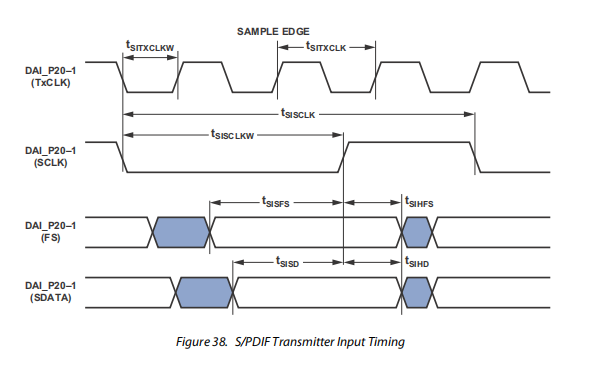

S/PDIF发射机输入数据定时

S/PDIF发射机的定时要求见表50。使用SRU将输入信号路由至DAI_P20–1引脚。因此,下面提供的正时规范在DAIúU P20–1引脚上有效。

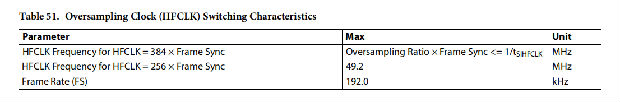

过采样时钟(HFCLK)开关特性

S/PDIF发射机具有过采样时钟。这个HFCLK输入被分解以产生双相时钟。

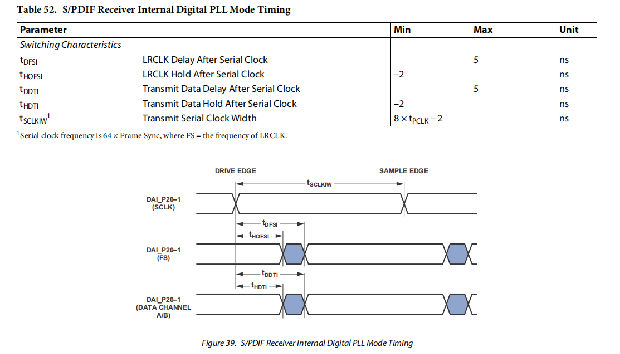

S/PDIF接收机

以下部分描述与S/PDIF接收器相关的定时。

内部数字锁相环模式

在内部数字锁相环模式下,内部PLL(数字PLL)产生512×FS时钟。

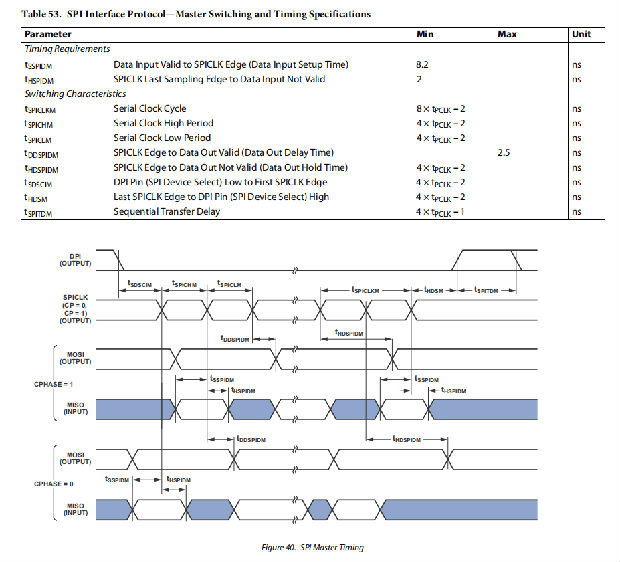

SPI接口主机

处理器包含两个SPI端口。主设备和辅助设备都只能通过DPI使用。表53和表54中提供的定时适用于两者。

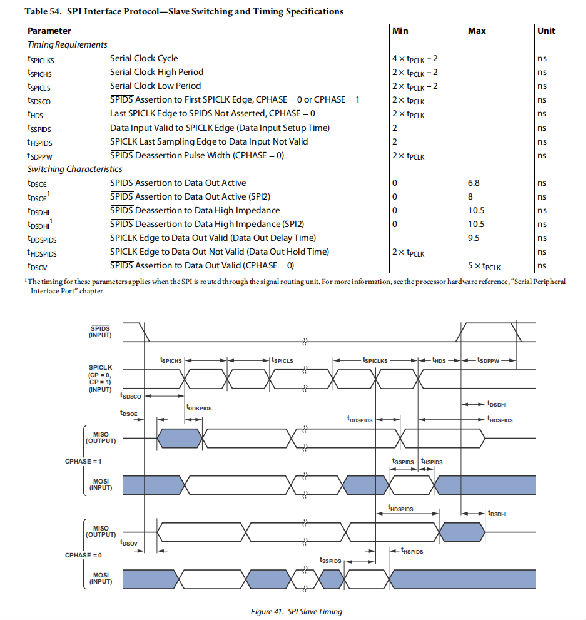

SPI接口从机

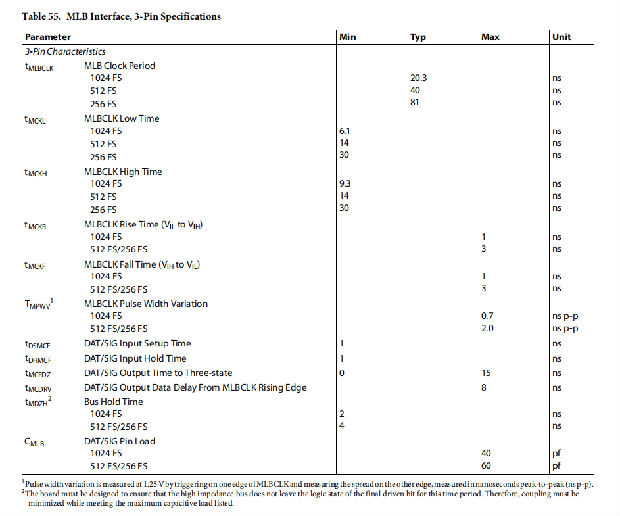

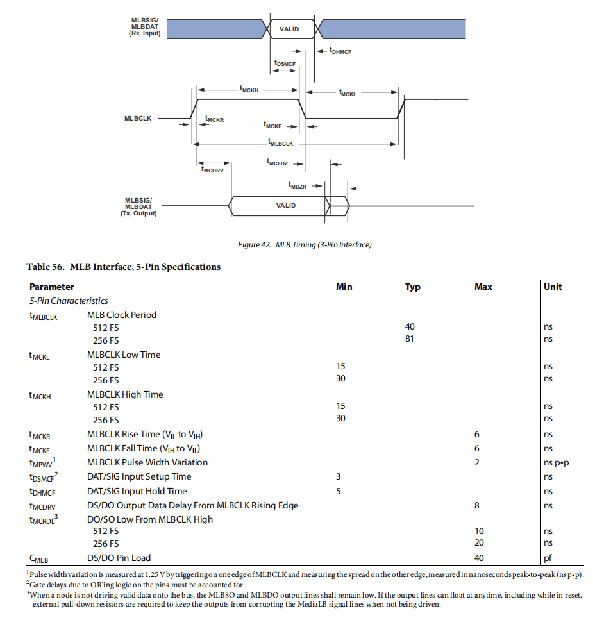

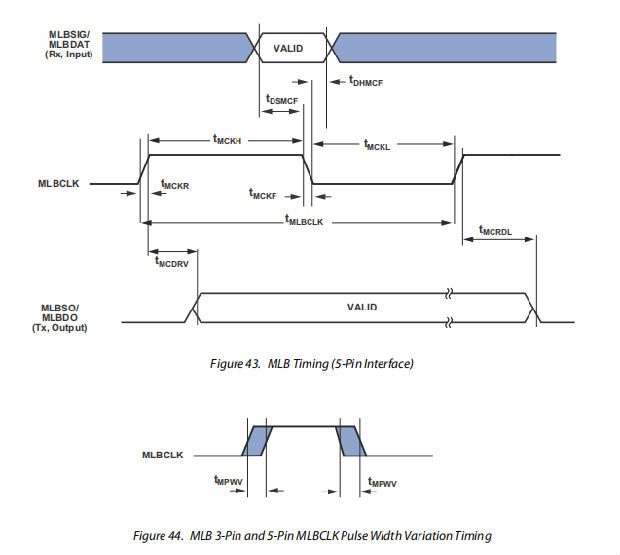

媒体本地总线

除非另有规定,否则给出的所有数字适用于所有速度模式(3针为1024 FS、512 FS和256 FS;5针为512 FS和256 FS)。

通用异步收发器(UART)端口接收和发送定时

有关UART端口接收和发送操作的信息,请参阅ADSP-214xx SHARC硬件参考手册。

2线接口(TWI)-接收和发送定时

有关TWI接收和发送操作的信息,请参阅ADSP-214xx SHARC硬件参考手册。

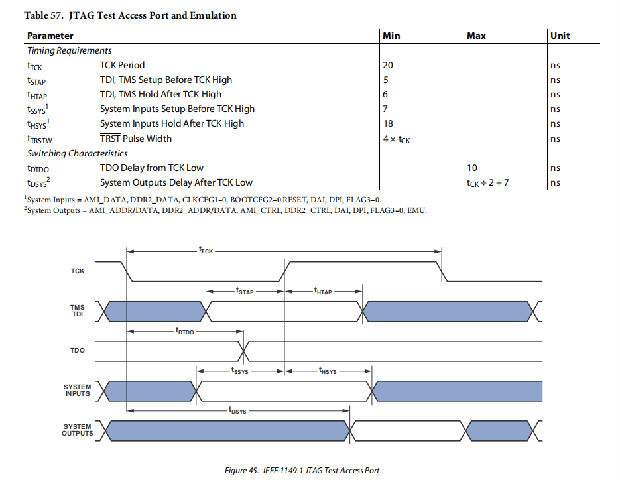

JTAG测试访问端口及仿真

试验条件

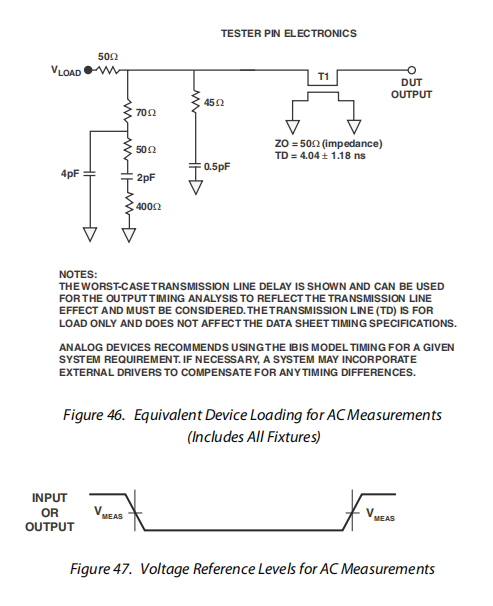

交流信号规格(定时参数)见第27页表20至第61页表57。这些包括输出禁用时间、输出启用时间和电容负载。SHARC的定时规范适用于图46中的电压参考电平。

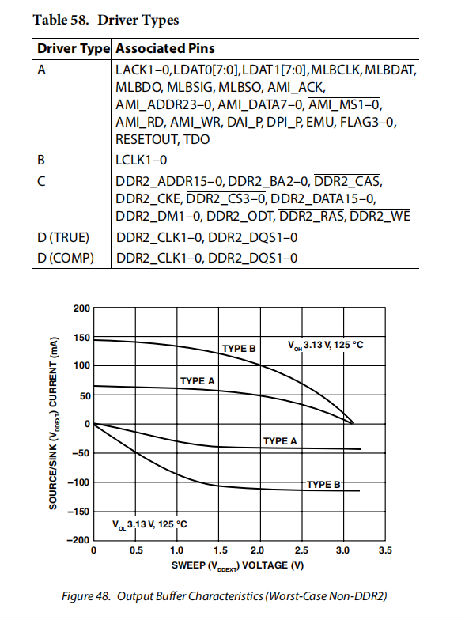

如图47所示,当信号穿过VMEAS电平时,对信号进行定时测量。在第一个信号到达VMEAS和第二个信号到达VMEAS之间测量所有延迟(纳秒)。对于非DDR管脚,VMEAS的值为1.5 V,对于DDR管脚,VMEAS的值为0.9 V。

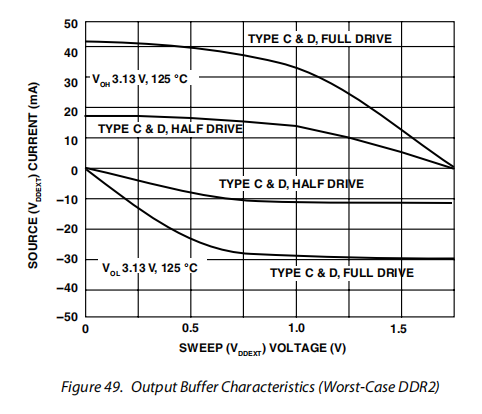

输出驱动电流

图48和图49显示了处理器输出驱动器的典型I-V特性,表58显示了与每个驱动器相关联的管脚。这些曲线表示输出驱动器的电流驱动能力与输出电压的函数关系。

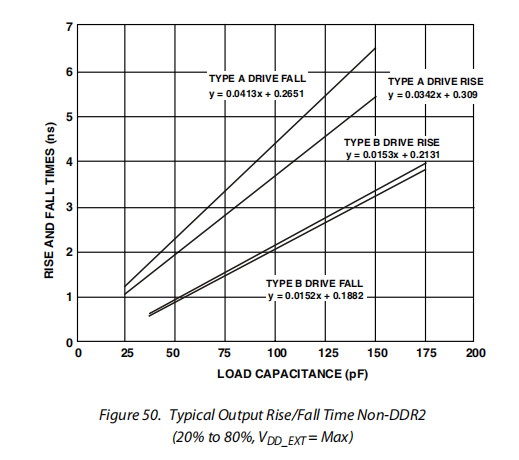

电容性负载

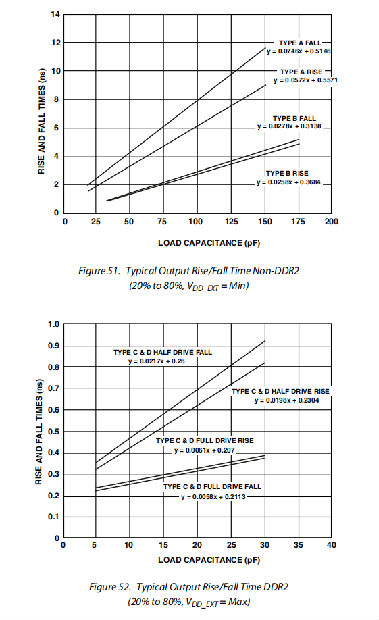

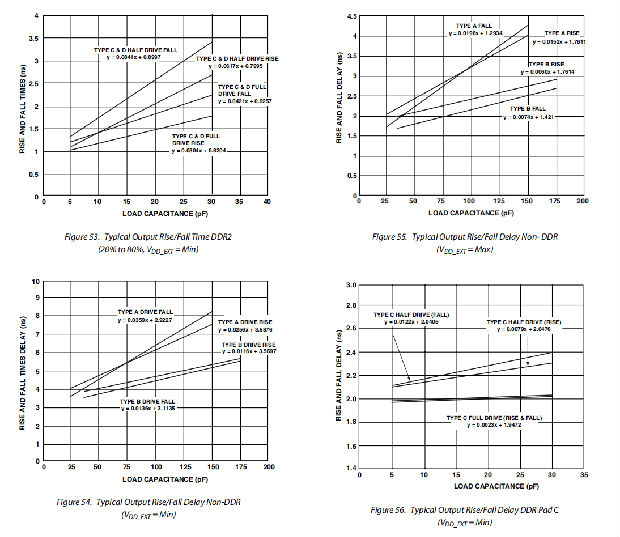

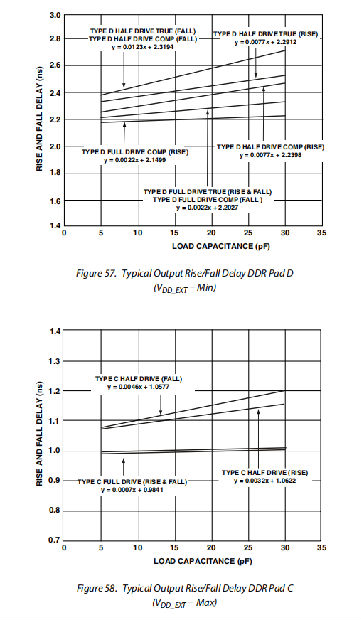

输出延迟和保持基于标准电容负载:所有引脚上的30 pF(见表58)。图54到图59以图形方式显示了输出延迟和保持是如何随负载电容而变化的。图50至图59的图形在典型输出延迟与负载电容和典型输出上升时间(20%至80%,V=Min)与负载电容的所示范围之外可能不是线性的。

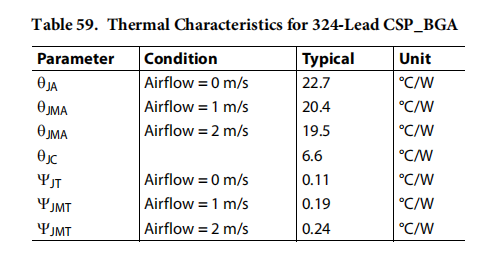

热特性

处理器的性能在第19页操作条件中规定的温度范围内。

表59气流测量符合JEDEC标准JESD51-2和JESD51-6,连接板测量符合JESD51-8。测试板设计符合JEDEC标准JESD51-7(CSP_BGA)。接头到外壳的测量符合MIL-STD-883。所有测量均使用2S2P JEDEC测试板。

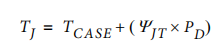

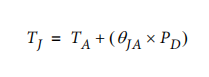

要在应用程序PCB上确定设备的连接温度,请使用:

式中:TJ=结温(℃);TCASE=在包装顶部中心测量的外壳温度(℃);JT=连接至顶部(包装)的特性参数是表59中的典型值。PD=功耗;θJA的值用于包比较和PCB设计考虑。θJA可用于TJ的一阶近似,公式如下:

式中:TA=环境温度°C。

当需要外部散热器时,提供的值θ用于封装比较和PCB设计考虑。

θ的值用于封装比较和PCB设计考虑。注意,表59中提供的热特性值是模型值。

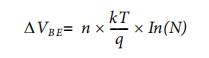

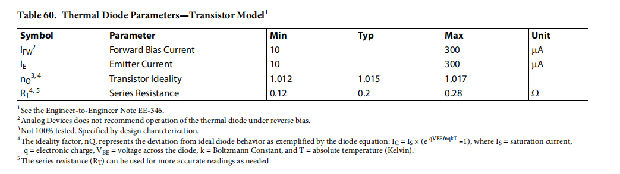

热二极管

处理器采用热二极管来监测模具温度。热二极管是一个接地集电极PNP双极结晶体管(BJT)。THD_P管脚连接到发射极,THD_M管脚连接到晶体管的底座。外部温度传感器(如ADM 1021A或LM86或其他)可以使用这些引脚来读取芯片的模具温度。

外部温度传感器采用的技术是测量热二极管在两种不同电流下工作时VBE的变化。如下式所示:

式中:n=接近1的乘法因子,取决于过程变化

k=玻尔兹曼常数

T=温度(℃)

q=电子的电荷

N=两个电流的比率

对于常用的温度传感器芯片,这两种电流通常在10μA到300μA之间。

表60包含使用晶体管型号的热二极管规格。注意,测量的理想因素已经考虑到β()的影响变化。

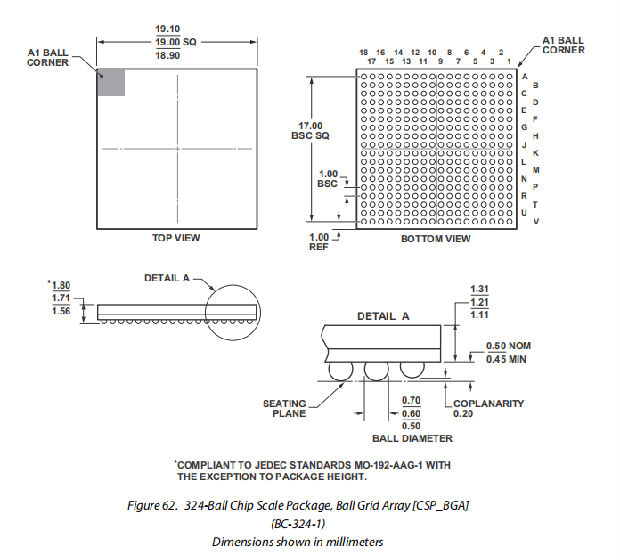

外形尺寸

处理器提供19毫米x 19毫米CSP_BGA无铅封装。

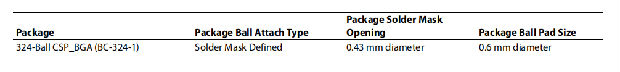

表面贴装设计

下表为PCB设计的辅助工具。有关工业标准设计建议,请参阅IPC-7351《表面安装设计的一般要求》和《地面模式标准》。

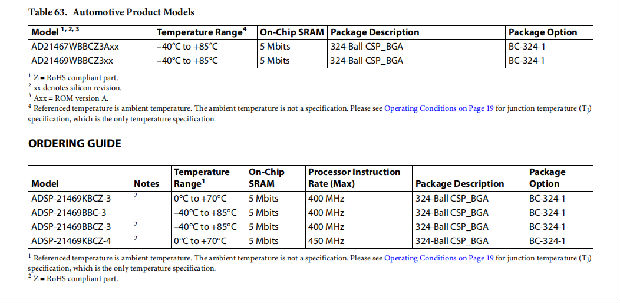

汽车产品

ADSP-21467W和ADSP-21469W型号提供控制制造,以支持汽车应用的质量和可靠性要求。注意,汽车模型可能有不同于商业模型的规格,设计者应仔细审查本数据表的规格部分。请联系您当地的ADI客户代表以获取特定的产品订购信息,并获取这些型号的特定汽车可靠性报告。