THS8200点击型号即可查看芯片规格书

说明

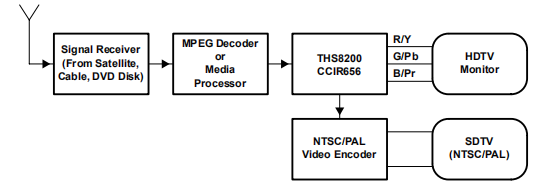

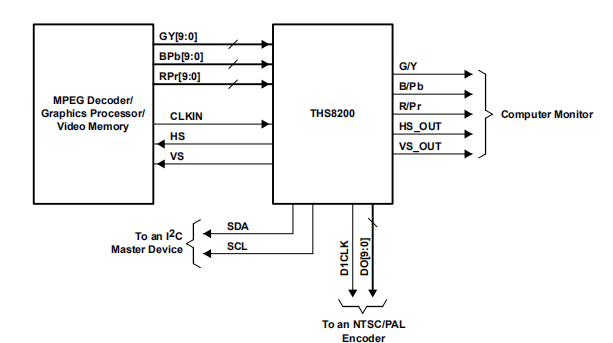

THS8200是一个完整的视频后端D/a解决方案,适用于DVD播放器、个人视频录像机和机顶盒,或任何需要将数字分量视频信号转换为模拟域的系统。

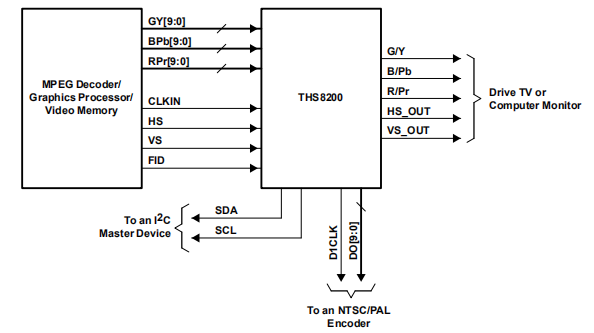

THS8200可以接受多种数字输入格式,包括4:4:4和4:2:2格式,通过3×10位、2×10位或1×10位接口。设备通过专用的Hsync/Vsync输入或通过从视频流中的嵌入式sync(SAV/EAV)代码提取同步信息来同步到传入的视频数据。或者,当被配置为生成PC图形输出时,THS8200还提供主定时模式,其中它从外部(存储器)源请求视频数据。

THS8200包含一个显示定时生成器,它可以完全为所有标准和非标准视频格式编程,最大支持像素时钟为205 MSPS。因此,该设备支持所有组件视频和PC图形(VESA)格式。颜色空间转换包括一个完全可编程的3×3矩阵运算。所有视频格式,高达HDTV 1080I和720P格式,也可以在内部2×过采样。过采样缓解了DAC后面对尖锐外部模拟重建滤波器的需求,改善了视频特性。

输出符合范围可通过外部调节电阻器设置,有两种设置可供选择,以便在不改变硬件的情况下适应分量视频/PC图形(700 mV)和复合视频(1.3 V)输出。视频数据上的内部可编程剪辑/移位/乘法功能可确保标准兼容的视频输出范围,适用于全10位或精简的ITU-R.BT601类型的视频输入。为了避免视频范围缩放后的非线性,dac内部采用11位分辨率。此外,具有可编程幅度的双电平或三电平同步(为了同时支持700/300 mV和714/286 mV视频/同步比)可以仅插入绿色/luma信道,也可以插入所有三个输出信道。此同步插入是从DAC中的其他电流源生成的,这样整个DAC分辨率对于视频范围仍然可用。这将为视频数据保留DAC 11位动态范围的100%。

THS8200可选地支持嵌入在输入视频流中的辅助数据的通过,或者可以根据CGMS数据规范将辅助数据插入到525P模拟组件输出中1.2特点

三个11位205-MSPS D/A转换器,集成双电平/三电平同步插入

支持所有ATSC视频格式(包括1080P)和PC图形格式(75 Hz时最高支持UXGA)

输入

灵活的10/15/16/20/24/30位数字视频输入接口,支持4:4:4或4:2:2采样的YCbCr或RGB数据通过Hsync、Vsync专用输入或根据ITU-R.BT601(SDTV)或SMPTE274M/SMPTE296M(HDTV)提取嵌入式SAV/EAV码进行视频同步与DVI 1.0(带HDCP)接收器的无胶接口。可根据EIA-861规范通过DVI格式接收视频,并通过单独同步或嵌入式复合同步转换为YPbPr/RGB组件格式

视频处理

可编程的剪辑/移位/倍增功能,用于全范围或ITU-R.BT601视频范围输入数据操作

每个模拟输出通道上的可编程数字精细增益控制器,用于精确通道匹配和可编程白平衡控制

内置4:2:2至4:4:4视频插值滤波器

内置2×过采样SDTV/HDTV插值滤波器,改善视频频率特性

全可编程数字彩色空间转换电路

全可编程显示定时发生器,提供所有SDTV和HDTV复合同步定时格式,渐进式和交错式

完全可编程的Hsync/Vsync输出

垂直消隐间隔(VBI)覆盖或数据传递,实现VBI数据透明度

可编程CGMS数据生成和插入

输出

数字

–ITU-R BT.656数字视频输出端口

模拟

–软件可切换700 mV/1.3 V兼容输出DAC在37.5Ω负载下的模拟元件输出

–可编程视频/同步比(7:3或10:4)

–可编程视频底座

总则

内置视频彩条测试图案生成器

快速模式IC控制接口2

可配置主/从计时模式

–配置模式允许设备充当从视频帧缓冲区请求数据的主计时源。或者,该设备可以从属于外部定时主机。(主模式仅适用于PC图形输出模式)。

DAC和芯片断电模式

低功率1.8/3.3 V操作

80针PowerPAD塑料四片式封装,散热效率高,物理尺寸小

应用

DVD播放器

数字电视/互动电视/互联网机顶盒

个人录像机

高清电视显示或投影系统

数字视频系统

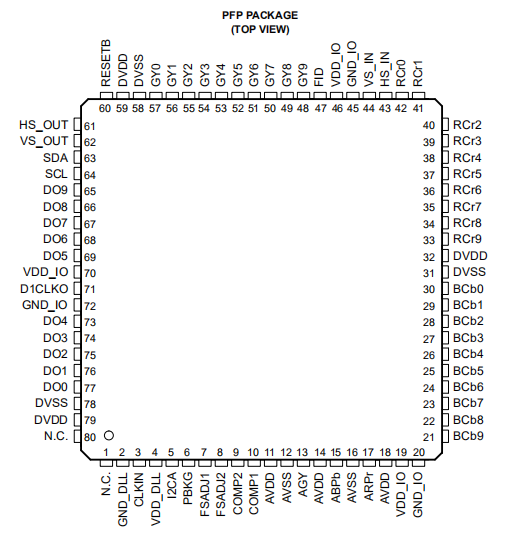

终端说明

THS8200功能概述

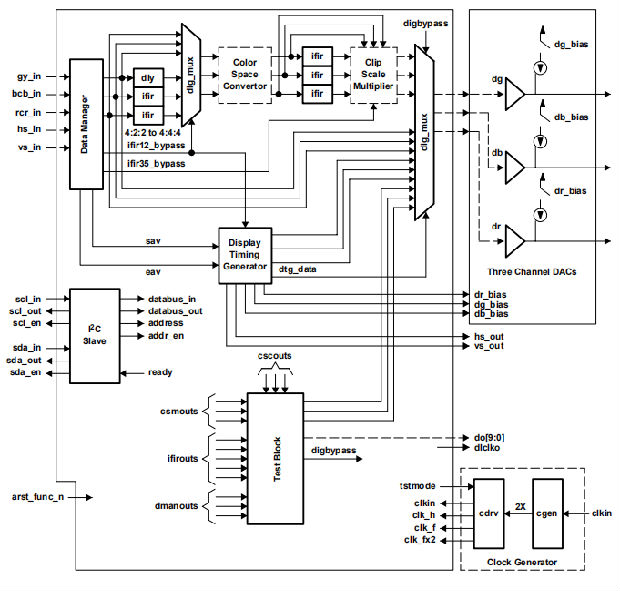

功能框图

数据管理器(DMAN)

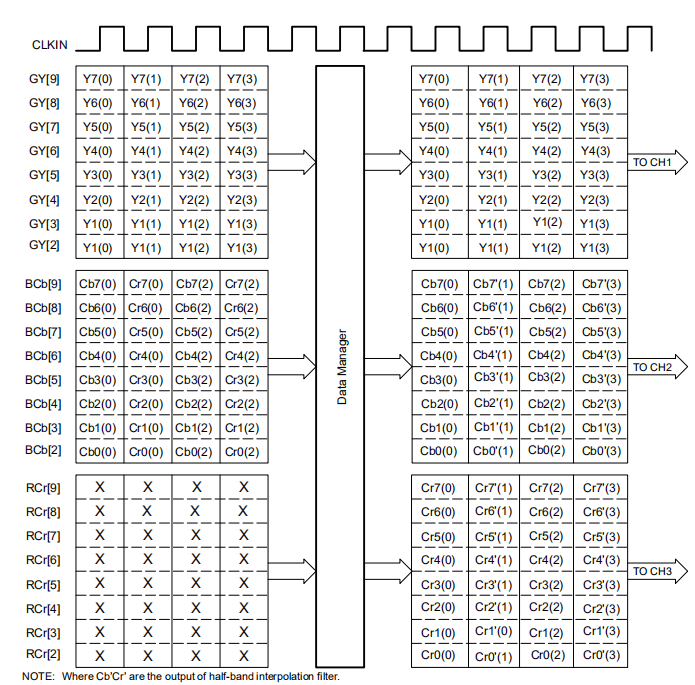

数据管理器是将芯片输入总线上显示的选定输入视频数据格式转换为内部10位三通道表示的块。支持的输入格式包括带有嵌入式同步代码的10/8位ITU-R.BT656、带有外部同步的15-/16或24-/30位RGB、带有嵌入式同步代码的20-/16位SMPTE274M/296M以及带有外部同步的20-/16位YCbCr 4:2:2。用户可以选择包括4:2:2到4:4:4

3–1个

颜色数据路径上的插值。当选择具有嵌入式同步的格式时,DMAN还从ITU-R.BT656(SDTV)或SMPTE274M/296M(HDTV)数据流中提取H(H sync)、V(Vsync)、F(FieldID)标识符,用于DTG的内部同步。或者,设备与HS_-IN、VS_-IN、FID输入同步。

插值有限脉冲响应滤波器(IFIR)

采用插值FIR对输入数据进行2×上采样。在THS82000中有五个IFIRs。前两个仅在输入数据采用4:2:2格式转换为两个色差通道上的4:4:4内部表示时使用。最后三个ifir用于在启用2×视频插值的情况下将所有三个通道上的内部数据向dac进行上采样。通过对视频数据进行2倍过采样,放宽了DAC输出端对模拟重建滤波器的要求,从而可以用较少的分量来构建,从而改善了整体视频特性(较小的群延迟变化)。通过编程适当的IC寄存器,可以绕过或切换所有的ifir。所有IFIRs的系数都是固定的。

颜色空间转换(CSC)

颜色空间转换器块用于将一种颜色空间中的输入视频数据转换为在另一种颜色空间中输出视频数据(例如,RGB到YCbCr,反之亦然)。该模块包含一个3×3矩阵乘法器/加法器和一个3×1加法器。所有乘法器和加法器系数都可以通过IC接口编程,以支持对视频数据的任何线性矩阵+偏移操作。

剪辑/移位/乘法器(CSM)

clip shift multiply块可选地在编程的低/高代码处剪辑输入代码范围,向下移动输入视频数据,并将输入乘以0–1.999范围内的可编程系数。这允许在输入码范围减小的情况下操作,如ITU-R.BT601建议中所规定的。每个通道都可以独立编程,以适应三个输入通道中每个通道的不同数字范围。例如,对于标准视频信号,Y通道的数字输入范围为64–940,而其他两个通道的输入范围为64–960。所有三个通道的DAC输出范围必须为0–700 mV,因此通常情况下,对应于1 LSB的模拟电压必须改变,以考虑不同的数字输入。这可能会导致匹配错误。因此,在THS8200中,DAC LSB不改变;相反,LSB转换是通过将数字输入缩放到DAC的全部输入范围来完成的。此外,CSM输出为11位宽,并被发送到11位DACs。额外的分辨率位解决了缩放过程中引入的非线性问题。可以关闭剪裁功能,以允许超白/超黑偏移。

数字多路复用器(DIGMUX)

DACs前面的多路复用器可以在1×或2×像素时钟速率的视频信号之间进行选择。它还用于切换显示定时生成器(DTG)块生成的消隐/同步电平数据和测试模式数据(例如,色条、IC控制的DAC电平)或在垂直消隐期间执行数据插入(CGMS)。

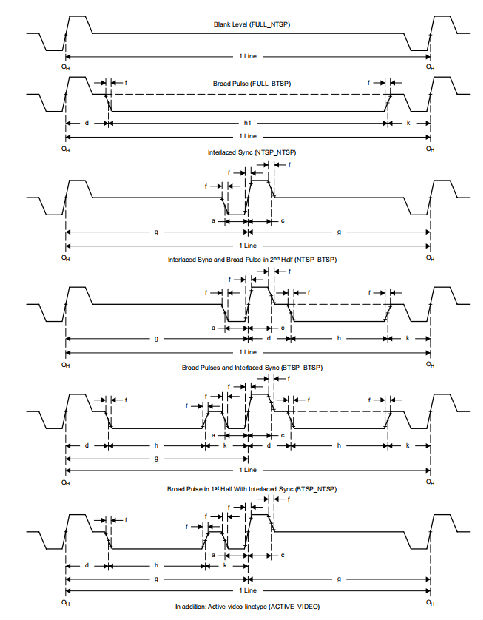

显示定时发生器(DTG

显示定时发生器负责生成正确的帧格式,包括所有同步、均衡和锯齿脉冲。在主定时模式下,DTG与外部同步输入(从专用设备终端HS-In、VS-In和FID)同步,或者与由DMAN模式选择的从输入数据流提取的标识符同步。在主定时模式下,DTG基于外部应用的像素时钟输入生成所需的字段/帧格式。

当活动数据没有被传送到DACs时,即在水平/垂直消隐间隔期间,DTG生成用于消隐、同步电平和其他电平偏移的正确数字字,例如前锯齿脉冲和后锯齿脉冲以及均衡脉冲。

水平计时,以及负同步和正同步、HDTV宽脉冲和SDTV前后均衡和锯齿脉冲的幅度,都是可编程IC来适应,例如,两者的产生2

3-2个

符合EIA.770-1(10:4视频/同步比)和EIA.770-2(7:3视频/同步比)的模拟分量视频输出,并支持非标准视频计时格式。

除了或作为插入在绿色/luma信道或所有模拟输出上的复合同步的替代,输出视频定时也可以通过专用Hsync/Vsync输出信号进行。Hsync和Vsync输出的位置、持续时间和极性是完全可编程的,以便支持例如在图片帧内的活动视频窗口的居中。

DTG还控制DIGMUX块中的数据多路复用器。DIGMUX可编程为仅在活动视频线路上传送设备输入数据(在消隐间隔期间插入DTG生成的消隐电平)。或者,DTG也可以在一些VBI行期间传递设备输入数据(输入流中的辅助数据在一些VBI行上透明地传递)。最后,设备还可以生成自己的辅助数据,并根据525P视频格式的CGMS数据格式将其插入模拟输出。

时钟发生器(CGEN)

时钟发生器是一个基于模拟延迟锁定环(DLL)的电路,从CLKIN输入提供2×时钟。CDRV块使用2×时钟进行2×视频插值。有些视频格式还需要1/2速率时钟,用于4:2:2到4:4:4的转换。

时钟驱动器(CDRV)

时钟驱动块生成所有的片上时钟。它的输入是来自数字逻辑的控制信号、原始CLKIN和来自CGEN的2×时钟。输出包括半速率时钟、全速率时钟和2×全速率时钟。时钟用于可选的片内插值处理:4:2:2到4:4:4插值和1×到2×视频过采样。

IC主机接口(I2CSLAVE)2

IC接口控制和编程内部IC寄存器。THS8200集成电路接口实现支持快速集成电路规范(SCL:400khz),并允许寄存器的写入和读取。自动递增寻址功能简化了块寄存器编程。集成电路接口在CLKIN上没有时钟的情况下工作。22222

试块(TST)

测试块控制THS8200的所有测试功能。除了制造测试模式外,该块还包含多个用户测试模式,包括DAC内部渐变生成器和75%SMPTE视频色条生成器。

3.1.10 D/A转换器(DAC)

THS8200包含三个DAC,工作速度高达205 MSPS,内部分辨率为11位。每个DAC包含一个集成视频同步插入器。同步是通过附加的电流源电路插入的,无论是在绿色/luma(Y)通道上还是在所有的DAC输出通道上,以符合用户(EIA,sync-on-G/Y)和专业(SMPTE,sync-on-all)标准。

DAC速度支持所有ATSC格式,包括1080P,以及所有PC图形(VESA)格式,最高支持75赫兹(202.5毫秒/秒)的UXGA。

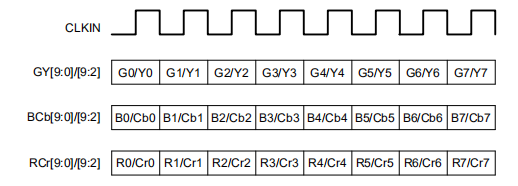

输入接口格式

下图定义了每个输入模式的输入视频格式,由数据寄存器设置选择。视频数据总是记录在CLKIN的上升沿。注意:对于使用10位输入总线的8位操作,只连接所用每个输入总线的8个MSBs,并将2个lsb连接到地。

24/30位RGB或YCbCr数据格式

20位YCbCr 4:2:2

CLKIN等于1×像素时钟。像素时钟等于Y输入的速率,并且是该输入格式中的另外两个信道的速率的2倍,其中Cb和Cr被复用到同一输入总线上。

20-/16位YCbCr 4:2:2数据格式(显示16位操作)

当在该模式中使用专用定时时,HS-in的第一激活周期(即,第一CLKIN上升沿看到HS-in激活)与接收CbCr样本的总线上在该时钟周期期间假设存在的Cb颜色分量之间存在固定关系。在这种模式下使用嵌入式定时时,SAV/EAV结构还根据HDTV的SMPTE274M/296M明确地定义CbCr序列。

注:图中显示了每10位输入总线仅使用8位时的情况。

10位YCbCr 4:2:2(ITU模式)

CLKIN等于像素时钟的2倍,因为所有组件都在一个10位总线上以4个多序列进行多路复用:CbYCrY。因此,像素时钟(即Y输入速率)是CLKIN的1/2,Cb和Cr速率是CLKIN的1/4。

当在该模式中使用专用定时时,HS-in的第一激活周期(即,第一CLKIN上升沿看到HS激活)与输入总线上该时钟周期中假设存在的Cb颜色分量之间存在固定关系。当在该模式中使用嵌入式定时时,SAV/EAV结构还根据ITU-R.BT656(用于625I和525I)和SMPTE293M(用于525P)明确地定义CbCr序列。•16位RGB 4:4:4

CLKIN等于像素时钟的1倍。此格式仅在VESA模式下受支持,并且可用于不需要每个颜色组件的完整8位分辨率的PC图形应用程序。

时钟发生器(CGEN)/时钟驱动器(CDRV)

时钟生成器/时钟驱动块生成4:2:2到4:4:4和2×视频过采样的所有片上时钟。DMAN设置控制输入数据是4:2:2还是4:4:4采样,以及是否使用30位、20位或10位接口。此选择影响假定存在于CLKIN上的时钟输入频率。

1×像素时钟。4: 应绕过2:2到4:4:4插值。可选2×过采样可用于像素时钟高达80 MHz的格式。30位4:4:4:

1×像素时钟。4: 2:2到4:4:4插值应切换到,可用于像素时钟高达150 MHz的格式。可选2×过采样,可用于像素时钟高达80 MHz的格式。20位4:2:2:

1/2×像素时钟。4: 2:2到4:4:4插值应切换到,可用于像素时钟高达150 MHz的格式。可选2×过采样可用于像素时钟高达80 MHz的格式。10位4:2:2(ITU):

内部DLL(延迟锁定环)产生更高的时钟频率。当使用一个或两个内插/过采样级时,用户应根据CLK中出现的频率对输入频率范围选择寄存器dll_freq_sel进行编程。

到4:4:4级被切换或旁路,这取决于数据ifir12旁路寄存器的设置(仅在色度通道上进行插值)。此功能应仅与YCbCr 4:2:2输入一起使用。THS8200可以根据CSC设置执行到RGB的颜色空间转换。dtg2_rgbmode_on寄存器应设置为与DAC输出的颜色空间表示相对应。

根据数据ifir35_旁路寄存器的设置,2×过采样级被切换或旁路。

当时钟频率超过80mhz时,用户不应启用2×过采样级,对于更高的PC图形格式和1080P HDTV也是如此。在这种情况下,应使用vesa_clk寄存器绕过DLL,以禁用2×频率生成。如该寄存器的详细寄存器映射描述中所述,在该模式下仍然可以支持20位4:2:2输入(例如,对于1080P)。

存在由DLL旁路寄存器启用的DLL的第二个旁路模式操作。当该旁路模式激活时,CLKIN输入假定为2×像素频率。此模式仅用于测试目的,因为它与支持的输入格式表中的任何模式都不对应。

颜色空间转换(CSC)

THS8200包含一个完全可编程的3×3乘法/加法和3×1加法器块,可切换为所有视频格式,最高像素时钟频率为150 MHz。因此,颜色空间转换可用于所有数字电视模式,包括1080P和VESA模式,在75赫兹(135 MSPS)时最高可达SXGA。该操作在可选的4:2:2到4:4:4转换之后完成,因此在可选的2×视频过采样之前对1×像素时钟视频数据执行。CSC块可以根据寄存器CSC_bypass的设置来切换或旁路。

3×3乘/加的9个浮点乘法器系数中的每一个都表示为6位有符号二进制整数部分和10位小数部分的组合。整数部分是以MSB为符号位的有符号大小表示。小数部分是幅度表示;请参见以下示例。

寄存器命名法为:csc<r,g,b><i,f>c<1,2,3>,其中:

<r,g,b>确定哪个输入通道乘以该系数(r=红色/Cr,g=绿色/Y,b=蓝色/Cb输入)

<i,f>表示系数的整数(i)或小数(f)部分

<1,2,3>标识颜色空间转换器的输出通道:1=Yd/Gd,2=Cb/Bd,3=Cr/Rd

对于偏移量值,需要在单个偏移寄存器中编程所需数字偏移量的1/4值,因此512(偏移量超过视频范围的1/2)的典型偏移量需要在偏移量<1,2,3>寄存器中编程128个十进制值,其中<1,2,3>再次定义受影响的输出信道,具有类似的约定如前所示。

可以切换饱和逻辑,以避免在使用csc uof_cntl寄存器进行颜色空间转换后,结果出现过流和下流。

接下来我们将展示一个如何编程CSC的示例。这也解释了数字数据格式。

CSC配置示例:HDTV RGB到HDTV YCbCr

RGB到YCbCr转换的公式为:

Yd=0.2126*Rd+0.7152*Gd+0.0722*Bd

断路器=–0.1172*Rd–0.3942*Gd+0.5114*Bd+512

Cr=0.5114*Rd-0.4646*Gd-0.0468*Bd+512

要将通道1(Y)的红色系数编程为0.2126,必须执行以下操作:

1. 认识到这是一个正值,所以整数部分的符号位是0。(csc_ric1的位5=0)

2. 注意,系数中没有整数部分(位4–位0=00000)。

3. 分数部分的二进制表示可以直接由分数部分的二进制等价物乘以1024(0.2126×1024=217.7)构造,四舍五入到最近的整数(218),并表示为二进制10位数(0011010)。

剪辑/缩放/倍增(CSM)

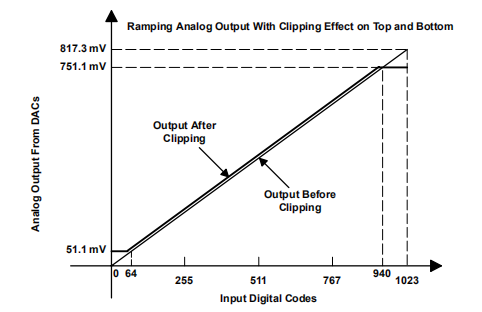

如果根据ITU或SMPTE标准进行采样,则对视频数据的编码范围有限制。换句话说,完整的10位范围[0:1023]不用于表示视频像素。例如,通常64位小数是允许表示视频信号的最低代码,并且对应于消隐级别。与Y类似,通常最大代码是940十进制。超出此范围的偏移可能是数字视频处理的结果。

THS8200可以通过两种方式之一来处理这种瞬时偏移:将输入代码限制为可编程的最大/最小值,或者允许发生这种偏移。

根据所选择的方法,用户可以放大CSM中的视频数据,以确保在使用限制时使用DAC的满标度动态范围以获得最佳性能。或者,当该限幅被禁用时,可以由DAC在模拟输出信号中输出码范围之外的瞬时偏移(允许模拟输出中的超白/黑)。

CSM块允许用户使用这种减少的摆动输入视频代码来指定THS8200的行为。它由以下部分组成:

1. 输入视频数据在高限和低限时的一种可选剪辑,在高限和低限时,每个通道的限值是可单独编程的

2. 输入视频数据的向下移位,其中移位量是每个通道单独可编程的

3. 视频数据的倍增(幅度缩放)功能,其中倍增系数是每个通道单独可编程的。

4.5.1剪裁

视频输入数据的剪辑(限制)可以通过对csm-gy、rcr、bcb-clip-on寄存器进行编程,在高端和/或低端选择性地打开或关闭。高/低限幅值可以使用寄存器csm_clip_<gy,rcr,bcb><high,low>对每个通道进行编程。

显示了截取ITU-R.BT601采样视频信号的典型情况。

限幅对模拟输出的影响

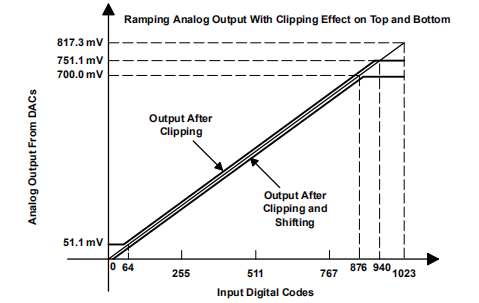

移位

接下来,视频数据可以在可编程量上向下移动。通过编程csm_shiftúgy,rcr,bcb>来设置每个通道上用于移动输入视频数据的代码数。输入视频数据的移位可以在CSM内向下移动超过0..255个代码。

移位对截断模拟输出的影响

DAC的模拟输出,前提是[64..940]输入上的满标度视频范围与分量视频的正常700 mV范围相对应。此满标度范围由选定的FSADJ满标度设置(寄存器数据)设置。

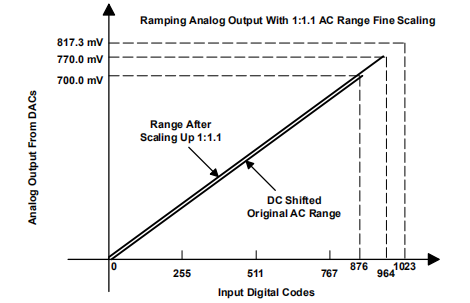

倍增

当10位范围不能完全用于视频时,我们可以缩放输入的视频数据以使用DAC的全部10位动态范围。应注意不要在缩放后使可用范围过大/过小。

这种倍增控制有两个目的:

使用完整的10位DAC范围进行缩小范围的输入

每个通道单独的精细增益控制,以补偿增益误差并提供白平衡控制

缩放模拟视频输出的效果

移位的模拟斜坡输出。可以计算乘法因子,将该输出范围扩展到DAC的全部10位范围。请注意,可以使用寄存器csm_mult_<gy、rcr、bcb>为每个通道单独编程该缩放。乘法的范围是0..1.999,编码为二进制加权的11位值,因此:csm_mult_<gy,rcr,bcb>=(所需刻度(0到1.999)/1.999)×2047

注意,该方法允许将每个信道上不同的输入码范围缩放到相同的满标度DAC输出符合性,这是ITU-R.BT601采样信号所要求的,其中Y视频数据在范围[64..940]中表示,并且两个Cb、Cr色差信道都在范围[64..960]内编码。所有三个通道都需要产生700毫伏的标称模拟输出符合性。在模拟域和数字CSM控制中,结合FSADJ同时调节所有DAC通道的满标度电流,可以对DAC输出幅度控制(包括通道匹配)进行不同的权衡。

正如在显示定时发生器(第4.7节)中所讨论的,在消隐、正负同步、前后均衡和锯齿脉冲期间,用户还控制DAC输出电平。因此,使用CSM和DTG编程的组合,可以容纳许多视频标准,包括那些需要视频空白到黑色级别设置的标准,以及不同的视频/同步比率(例如,10:4或7:3)。

最后,使用FSADJ1或FSADJ2终端的可选择满标度调整,可以在两个模拟输出符合性设置之间切换,而无需硬件更改。

物理上,CSM输出在内部表示为11位值,以在缩放后在10位级别上改善DAC线性。每个DAC内部的分辨率为11位。

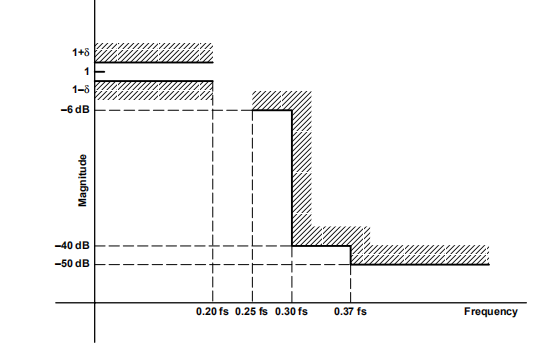

插值有限脉冲响应滤波器(IFIR)

为了缓解模拟域DAC后重构滤波器的要求,充分利用THS8200中DAC的高速性能,集成了2×数字上采样插值滤波器模块。

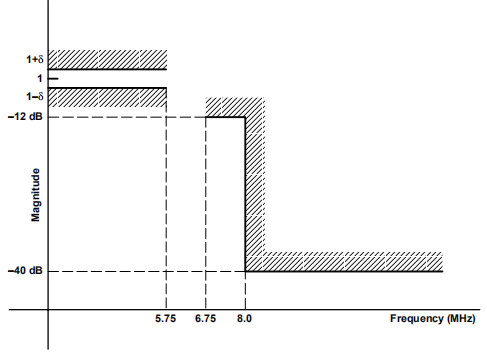

HDTV(SMPTE274M/296M标准)和SDTV(ITU-R.BT601标准)的YRGB和CbCr滤波要求。

注:δ=0.05db。对于1080I和720P HDTV格式,fs=74.25 MSPS。

基于SMPTE296M/274M的P和P滤波器要求

注:δ=0.05db。

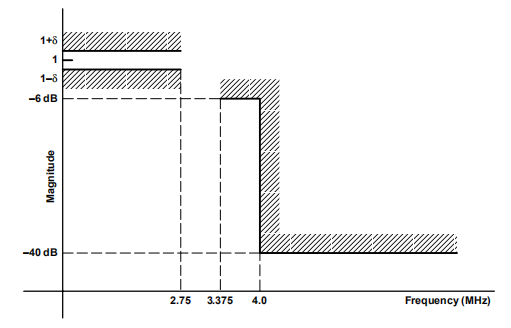

基于ITU-R.BT601的Y和RGB滤波器要求

注:δ=0.05dB

基于ITU-R.BT601的Cb和Cr滤波器要求

插值滤波器的频率和相位响应。显示了使用THS8200中的有限字长系数的实际响应。SDTV/HDTV模式和4:2:2至4:4:4插值(2个滤波器,每个Cb和Cr通道一个,在DMAN上选择4:2:2输入模式以插值1/2至1×像素时钟速率的色度时切换)以及2×视频过采样(3个滤波器,每个DAC通道一个,切换)都使用相同的滤波器特性当2×插值被激活时)。

显示定时发生器(DTG)

功能概述

THS8200可以生成专用的Hsync/Vsync/FieldID视频同步输出,以及在G/Y或所有模拟输出信道上插入的复合同步。两种类型的输出同步可以同时使用,并且可以独立编程。同步模式是完全可编程的,以适应所有标准的VESA(PC图形)和ATSC(DTV)格式以及非标准格式。

为了生成输出视频定时,设备配置为HDTV、SDTV或VESA模式(dtg1_模式寄存器)。根据所选的DTG模式,有多种线型可用于生成完整的视频帧格式。水平和垂直同步的时间和位置、水平和垂直消隐间隔的位置、以及在垂直消隐间隔内的均衡脉冲、前锯齿脉冲和后锯齿脉冲的结构、位置和宽度是用户可编程的。

DTG确定:

帧格式/字段格式(像素数/行、行数/字段1、行数/字段2、字段数/帧=1表示逐行或2表示隔行格式)及其与输入数据源的同步-寄存器:dtg1_total_pixels、dtg1_linecnt、dtg1_frame_size、dtg1_field_size

在从机模式下,无论是HS-in、VS-in、FID(专用同步输入)用于输入视频同步,还是从嵌入式SAV/EAV码中提取视频定时,以及视频帧相对于这些同步信号的相对位置

–寄存器:dtg2嵌入式定时,dtg2高速,dtg2高速

输入信号的输入/输出方向(主/从模式)和极性

HS_-IN、VS_-IN和FID信号

–寄存器:dtg2_hs_pol、dtg2_vs_pol、dtg2_fid_pol

输出信号的位置、宽度和极性

–寄存器:dtg2长度,dtg2长度,dtg2长度1,dtg2长度1,dtg2长度2,dtg2长度2,dtg2长度2,dtg2长度输出pol,dtg2长度输出pol

DTG内的磁场反转

–寄存器:dtg1_field_flip

活动视频窗口:水平消隐间隔的宽度和位置,垂直消隐间隔的宽度和位置

–寄存器:dtg2_bp<n>、dtg2_线型<n>和dtg1_spec_x寄存器,见DTG线型概述(第4.7.3节)。

复合同步格式:水平线定时包括锯齿、隔行同步和垂直消隐间隔中每行上的宽脉冲、垂直同步宽度

–寄存器:dtg1 U模式、dtg1 U规格<a、b、c、d、d1、e、g、h、i、k、k1>

复合同步插入的行为:仅插入G/Y通道,或插入所有通道,或不插入复合同步;插入的负同步和正同步的振幅,垂直消隐间隔期间所有锯齿脉冲和宽脉冲的振幅

–寄存器:dtg1_<y,cbcr>_sync_high,dtg1_<y,cbcr>_sync_low

DAC在消隐期间的输出振幅,以及在垂直消隐间隔内的线路的活动视频部分(不包含垂直同步、锯齿或宽脉冲)期间是否通过视频数据-寄存器:dtg1<y、cbcr>_blank、dtg1_pass_through

色条测试图案的每个色条的宽度

–寄存器:dtg1_vesa_cbar_大小

功能描述

用户应使用当前视频格式的正确参数对DTG进行编程。DTG包含一个测线和一个像素计数器,以及一个状态机,用于确定要为模拟输出的每条测线输出用户定义的测线波形。像素计数器水平计数,直至每行的像素总数,编程为“dtg1_total_pixels”。行计数器在第一个字段中计数最多为“dtg1_field_size”行,并在总帧(field1+field2)中继续计数最多为“dtg1_frame_size”行。

电流场由奇偶场ID信号导出,奇偶场ID信号在Vsync周期开始时采样。内部FID信号的源可以是到FID终端的信号,也可以是从相应终端上的相对Hsync/Vsync对齐(由“dtg2-FID-de-cntl”和当前DTG模式(VESA对SDTV/HDTV)选择)内部导出的。有关详细信息,请参阅“dtg2_fid_de_cntl”的寄存器映射说明。根据EIA-861规范,从Hsync/Vsync输入校准中导出FID。在Hsync/Vsync转换不对中实现了一个公差。当Vsync跃迁的活动边缘在Hsync的活动边缘的正负63个时钟周期内发生时,两个信号都被解释为对齐,这表示字段1。由于这个定时窗口,内部FieldID信号在Vsync周期开始之前生成。由于在Vsync周期开始时对信号进行内部采样以确定当前场,因此场的解释是相反的。使用“字段翻转”寄存器通过字段反转来更正此错误。

如果视频格式是渐进式的,则只存在field1,不需要FID信号。但是,只有在检测到字段1条件时,即在Vsync周期开始时检测到FID低时,DTG才会启动。因此,在渐进式视频格式的情况下,当使用具有外部FID输入的设备时,用户必须确保保持FID终端低电平。

正确的DTG同步还需要编程的Hsync和Vsync输入极性是正确的。由于Hsync、Vsync的极性会因不同的VESA PC格式而改变,因此该设备内置了检测输入同步极性的支持。这是通过比较Hsync high('misc_ppl')的宽度与总行长('dtg2_pixel_cnt')来实现的,以导出Hsync占空比及其极性。一旦检测到,用户可以对检测到的输入极性进行编程,以实现DTG输入同步(“dtg2_hs_pol”)——设备不会自动设置该极性。使用寄存器'misc_lpf'、'dtg2_line_cnt'和'dtg2_vs_pol'进行Vsync极性检测的过程类似。

DTG同步可分为三个功能:

DTG如何与内部水平和垂直计数器同步内部同步:

水平和垂直计数器如何与HS_-IN/VS_-IN/FID或SAV/EAV信号同步源同步:

输出定时HS_OUT、VS_OUT和复合同步输出如何与DTG和水平和垂直计数器同步输出同步:

DTG基于一个状态机,该状态机可以生成一组行类型,这些行类型可以覆盖DAC输入上的值。DTG输出被DIGMUX多路复用到数据路径中。选定的视频格式预设设置,或在dtg1 U模式下选择通用模式时的编程(线型、断点)表,确定为特定行生成的线型,以及该DTG输出用于覆盖正常DAC输入的位置。在内部,存在固定数量的预配置行类型,用户可以从中进行选择。

此外,对于每一组线路类型(我们将看到下一个可能有两组不同的线路类型),用户可以编程每个预定义偏移的水平持续时间(负同步、正同步、后廊、前廊、宽脉冲、隔行同步等)以及振幅(例如负同步振幅、正同步振幅,空白振幅)。

dtg1 U模式的设置决定:

0H基准(DTG的水平复位)在SDTV和HDTV之间不同。内部同步:

可用的输出同步线路类型取决于这些模式。用户可以为每个模式从许多预定义的线型中进行选择。在每种模式下,用户都可以对线路上的计时进行编程。但是,某些计时是由选定的DTG U模式硬编码的(例如,同步的上升/下降时间不同;请参阅DTG线路类型概述,第4.7.3节),并且并非所有的线路类型都可以在每个DTG模式中选择(例如,HDTV允许三级同步,而SDTV只允许生成两级负同步)。输出同步:

预定义的DTG视频格式(预设)

虽然DTG可以灵活地生成各种视频输出格式及其同步信号,但最常见的视频格式具有字段和帧大小以及(线型、断点)设置的预定义设置。

选择视频格式预设时,仍需要对线型的水平计时进行编程。预置只修复(行类型,断点)表。

内部同步

DTG的像素和行计数器由内部信号重置。在从机模式(THS820从机至外部视频输入源)中,这些信号来自嵌入式SAV/EAV代码或专用Hsync/Vsync/FID输入。在主模式下,这些计数器处于自由运行状态,THS8200根据编程的场/帧参数生成HS_-In/VS_-In信号。主模式仅适用于渐进式扫描VESA模式。主模式下不生成FID。

用户可以通过编程输入延迟寄存器,在水平和垂直方向上延迟DTG的0参考。在物理上,水平和垂直DTG启动值都会改变。其效果是,当从专用输入或嵌入式SAV/EAV代码接收到垂直或水平同步时,输出帧从位置(x,y)开始。这确保了,例如,输出视频帧可以在显示器上居中。

基于DTG的0-参考,生成线类型,DIGMUX将在每种线类型的视频输入和DTG输出之间进行选择。不同线路类型的所有水平计时都是可编程的,包括视为活动视频的视频线路部分。SDTV或HDTV模式下所有可用线路类型的完整概述见第4.7.3节。

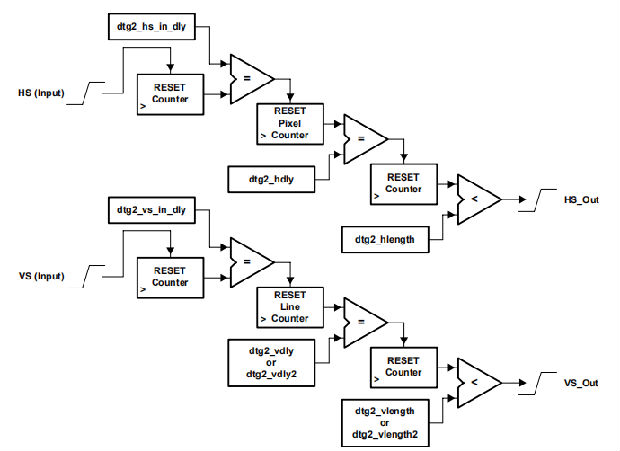

此外,可以生成Hsync/Vsync输出,并与THS8200 DAC输出同步。这些输出在宽度、位置和极性上是可编程的,基于水平/垂直像素计数器,因此独立于DTG基准。这确保插入DAC输出的复合同步输出和专用Hsync/Vsync输出之间可以独立同步。由于其可编程性,这些输出信号也可用于其他目的;例如,Vsync可编程为VBI期间激活的信号。

在从模式下内部像素和行计数器如何与内部HS和VS信号同步。HS和VS是从HS-IN、VS-IN或从输入视频数据中的嵌入式SAV/EAV代码导出的内部信号。由于DTG的0参考由这些计数器确定,因此dtg2-vs-in-ly和dtg2-hs-in-ly寄存器设置影响hs-OUT、vs-OUT和复合同步输出定时。另一方面,dtg2_vdly<1,2>和dtg2_hdly设置仅影响HS_OUT和VS_OUT,因为它们位于像素计数器的下游。同样,dtg2长度和dtg2长度<1,2>仅影响这些专用同步输出信号。

THS8200 DTG VS/HS输出生成

注意,两组独立的延迟寄存器允许在从机模式下容纳不同的输入定时参考。当设备配置为主模式时,延迟寄存器可以补偿不同的外部(帧存储器)同步要求。

输出同步:复合同步

复合同步是由一个编程序列(线型,断点)组合生成的,可以是用户编程(通用模式)或预置(预置模式)。线路类型用可编程的振幅和定时来确定DAC输出处的波形形状。

在每一行上,在DTG的水平参考点处,DTG决定在何处开始/停止DTG生成的数据以及在何处传递输入的视频数据。例如,在活动视频线期间,可以将辅助数据嵌入线的活动视频部分之外的数字流中,我们可能希望将其转换为模拟数据。或者,在非活动视频线期间(通常将插入预定义的线类型),可能需要在该线的活动视频部分期间传递辅助数据。

在G/Y和BPb、RPr信道之间,正、负同步偏移和负锯齿、前后均衡以及宽脉冲的幅度是独立可编程的。因此,同步插入只能在G/Y输出或所有DAC输出上编程。

为了限制选择行类型的选择位数,并且由于我们可以定义一组SDTV和HDTV视频模式互斥的行类型,有两种DTG视频模式:SDTV和HDTV。第三种DTG模式(VESA)不使用行类型/断点状态机,只生成Hsync/Vsync输出。

输出同步:Hsync/Vsync输出

这些是HS_OUT和VS_OUT信号,其宽度、位置和极性可在所有DTG模式下编程。

DTG线型概述

HDTV模式

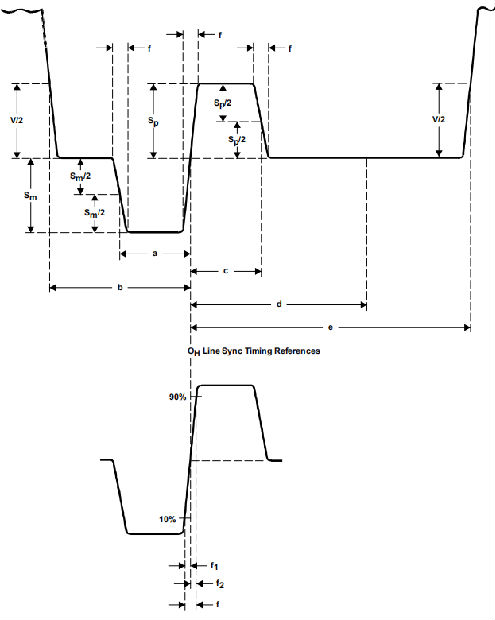

当在dtg1 U模式(预设或通用)中选择HDTV模式时,在每条视频线的开始处的模拟输出端插入三级同步。负偏移和正偏移期间的振幅是可编程的,以及两个偏移的水平定时参数(宽度、位置)。

VBI中负向空白和空白向正偏移的转换时间固定为2T,生成4T负向正偏移的三电平同步。线型在寄存器dtg2_linetype<n>中编程,并由DTG从与寄存器dtg2_breakpoint<n>中编程的线号相对应的垂直字段/帧位置输出,直到到达下一个断点寄存器中列出的线号。

DTG覆盖输入的视频数据,除非下面为特定的行类型指定。

水平计时对应于dtg1_spec_<x>寄存器。注意f规格是固定的。

三电平线路同步信号波形

A转换

THS8200包含3个DAC,内部分辨率为11位,最大速度为205 MSPS。这允许操作所有(H)DTV格式,包括1080P和PC图形格式,最高可达75赫兹UXGA。

可以使用数据调整寄存器在两个满标度范围之间选择DAC输出符合性。DIGMUX在非视频线路类型期间选择DTG输出数据,除非dtg1_passthrough处于活动状态:在这种情况下,视频输入数据仍在某些线路类型的活动视频部分期间传递,如DTG线路类型第4.7.3节所述。

ths820支持RGB或YPbPr颜色空间中的输出。使用RGB输出时,需要设置寄存器上的dtg2_RGB_mode_。在这种情况下,将偏移量添加到所有DAC输出信道,以便为负同步提供净空。名义上,消隐电平为350mV,700mV摆动向上延伸。因此,峰值白色对应于1.05 V。当在该寄存器上选择YPbPr模式时,偏移量仅添加到Y通道输出;Pb和Pr输出的视频范围从0到700 mV,0 V对应于内部DAC输入代码0(注意,由于CSM块,这可能对应于另一个设备输入代码)。因此,Cb和Cr色度差信道被假定为偏移二进制编码,而不是2s补码。

最后,DTG模式确定DIGMUX是否切换来自DTG的输出数据。例如,在VESA模式下,dac始终由视频输入总线驱动。在SDTV或HDTV模式下,当DTG覆盖视频输入总线时,DAC在这段时间内输出的实际幅度电平是用户通过dtg1迴、cbcr迴、dtg1迴、cbcr迴、dtg1迴、cbcr迴和dtg1迴、cbcr迴高寄存器进行编程的。

接下来我们将概述一些可以从THS8200生成的模拟分量视频输出格式。

无同步信号插入的RGB输出/通用应用DAC

在此模式下,任何模拟输出上都不会插入同步信号。生成用于输出视频同步的HS_OUT和VS_OUT信号。此模式通常用于计算机图形视频输出。

软件可选择两级满标度输出。对于视频应用,标称电压水平为0.7 V和1.305 V。

对于分量视频应用,标称电压电平为0.7v;NTSC/PAL复合视频显示器使用1.305v。对于复合视频应用,数字视频流必须在外部数字NTSC/PAL编码器中编码。THS8200仅将数字复合信号转换为模拟复合视频。图4-39显示了无同步插入的模拟输出。

当THS8200在此模式下编程时,由于对DAC输入码的线性响应,它也可以用作通用DAC。可选地,可以绕过CSM块以避免对设备输入代码进行任何处理。

SMPTE兼容的RGB输出,同步信号插入G(绿色)通道

在此模式下,将三电平(HDTV模式)/双电平(SDTV模式)同步信号插入G频道。标称模拟输出电压范围(从同步尖端到活动视频的峰值)为0.0 V到1.050 V。在活动视频期间,峰值到峰值交流值(动态范围)为700 mV(从350 mV到1050 mV)。所有三个通道上的空白电平对应于底部代码64,并且为350 mV。图4-41和图4-42示出了模拟视频输出信号,包括插入三电平或二电平同步脉冲的G通道的输出,以及R和B通道的输出。在R和B通道的同步期间未插入同步信号。

或者,通过适当地编程同步幅度电平,可以在THS8200上的所有三个信道上插入同步。在没有插入同步的通道上,空白电平保持在350 mV直流电平。

R、G和B通道上的活动视频代码范围为64到940。根据定义,代码64对应于空白电平输出,代码940对应于峰值模拟输出。此区域之外的输入代码可以由THS8200剪裁,也可以通过,具体取决于CSM设置。当通过时,用户应确保如果会出现瞬时高输出代码,则不会在DAC输出符合性范围之外超速驱动DAC输出。

测试功能

当设备使用VESA_colorbars register设置配置为VESA模式时,用户可以激活75%SMPTE色条测试模式。每个色条的宽度可以使用dtg1_vesa_cbar_大小寄存器进行编程。

dac前面的数字逻辑可以完全绕过,dac可以通过激活dac i2c cntl寄存器,通过IC接口编程的电平直接驱动。在这种情况下,dac<n>cntl寄存器设置dac输入代码。快速或慢速斜坡信号可以在内部生成,并使用tst_fast ramp和tst_slowramp寄存器发送到DACs。这对于静态DAC线性测试是有用的。

或者,当tst_digbypass寄存器被激活以全速测试时,输入总线可以直接驱动DAC。

在Y Cb Cr模式下,可以通过编程tstòY delay寄存器来改变Y信道相对于Cb和Cr信道的延迟。

最后,还有一个数字输出端口,其数据按照ITU-R.BT656编码。这是原始输入总线在任何THS8200内部处理之前的环路,因此仅当以10位ITU-R BT.656格式提供对THS8200的输入时才提供标准数据。此输出总线可用于连接到单独的NTSC/PAL视频编码器。data_clk656_on寄存器激活该总线上的时钟输出,data_tristate656寄存器禁用输出总线。建议在不使用时禁用此输出。

断电

THS8200实现两种断电模式:dac_pwdn关闭dac通道,但保持所有数字逻辑活动;芯片_pwdn关闭除IC接口外的数字逻辑。激活两个寄存器可强制关闭除IC接口外的所有模拟/数字电源。

CGMS插入

THS8200可以在垂直消隐间隔内嵌入数据,根据EIA-805数据插入标准进行编码。CGMS是EIA-805标准的一个实现,该标准定义了分量视频接口(CVI)视频信号中的数据插入。

THS8200支持在525P格式的每帧的第41行插入CGMS数据。数据仅插入Y通道;Pb和Pr通道保持在空白级别。CGMS数据插入是通过激活CGMS_en寄存器并对CGMS_报头和CGMS_有效载荷寄存器进行适当编程来实现的。用户需要以正确的格式对报头和有效载荷数据进行编程,因为在插入到模拟DAC输出之前没有进行额外的数据编码。THS8200仅对编程数据执行播放功能。CGMS编码块假设使用完整的10位视频范围,以确定EIA-805规定的逻辑1位的峰值白幅度的70%。CSM不影响CGMS数据插入的幅度。

CGMS按照EIA 770标准在第41行插入,用于SDTV的渐进式格式显示。该行可插入14位,由6位报头和8位有效载荷组成。用户可以直接将这些位编程到相应的THS8200寄存器中。应注意根据CGMS语义格式化此数据;请参考原始标准来确定报头/有效负载数据编程。为了避免无效数据的传输,只有当子地址最高的CGMS寄存器在CGMS处于活动状态时,才会更新传输的数据。

可在THS8200的1×或2×内插视频模式中插入CGMS。虽然EIA-805允许插入的数据在每一帧上改变,并且还允许将跨越多条线的数据包(因此也允许多个帧,因为只有一条线/帧用于插入),但是THS8200不支持多行数据插入,因为CGMS不需要它。

IC接口2

THS8200包含一个只支持从机的IC接口,该接口支持写和读。寄存器映射显示哪些寄存器支持读/写(R/W),哪些寄存器是只读的(R)。该设备支持正常和快速IC模式(SCL高达400 kHz)。当CLKIN上没有接收到输入时钟时,IC接口也可以工作。

为了区分写操作和读操作,设备在不同的设备地址寻址。有一个自动内部子地址递增计数器,在一次写入/读取操作期间,有效地写入/读取寄存器映射中的多个字节。此外,IC设备地址的bit1取决于I2CA pin的设置,如下所示:

如果地址选择引脚I2CA=0,则

–写入地址为40h(0100 0000)

–读取地址为41h(0100 0001)

如果地址选择引脚I2CA=1,则

–写入地址为42h(0100 0010)

–读取地址为43h(0100 0011)

IC接口支持快速,即SCL高达400 kHz。

系统控制(子地址0x02–0x03)

版本(7:0):设备版本

{版本0x02(7..0)}[0000 0000]

用户可以读取该寄存器,找出系统中的THS8200版本。

vesa_clk:时钟模式选择

{芯片控制0x03(7)}[0]

0 :正常运行

1 :除半速率时钟外,所有时钟都相同,并且将绕过DLL。这在VESA模式下用于支持直接的205兆赫输入时钟。没有内部2×插值可用。此模式应用于需要大于80 MSPS像素时钟的所有格式,因为用于2×时钟生成的内部DLL仅指定为高达80 MSPS。

如果需要允许例如148mhz 20位输入(1080P),半速率时钟仍在内部生成。

动态链接库旁路:

动态链接库旁路

{芯片控制0x03(6)}

[0]

0 :DLL用于生成时钟;使用内部生成的2×时钟进行正常操作。当设备时钟输入上有1×时钟可用,并且内部需要1×或2×DAC操作时(通过寄存器数据ifir35旁路选择),大多数视频格式应选择此模式

1 已绕过:DLL以生成时钟。在这种情况下,CLKIN管脚上的时钟输入直接用作2×时钟,而不是DLL内部生成的信号。此模式仅用于测试目的。

vesa_色条:色条测试图案

{芯片控制0x03(5)}[0]

0 :正常运行

1 :设备生成色条图案;忽略外部视频输入。色条图案仅在VESA PC图形模式下支持,设备配置为主模式(芯片=1)。

dll_freq_sel:dll频率范围选择

{芯片控制0x03(4)}[0]

设置DLL 2×时钟生成的频率范围。DLL不应在大于80mhz时使用。在这种情况下,应启用vesa_clk寄存器。因此,2×视频插值不适用于大于80mhz像素时钟的格式。

0 :高频范围:40–80 MHz像素时钟

1 :低频范围:10–40 MHz像素时钟

dac_pwdn:dac断电

{芯片控制0x03(3)}[0]

0 :正常运行

1 :DAC进入断电状态。

芯片:芯片断电

{芯片控制0x03(2)}[0]

0 :正常运行

1 :除IC外所有数字逻辑断电2

芯片:芯片模式选择

{芯片控制0x03(1)}[0]

0 :从模式。设备与输入的视频同步信号同步,可以嵌入ITU-R.BT656接口,也可以从专用定时信号接收。

1 :主模式。设备请求视频数据并根据编程的帧/场格式向外部(存储器)设备生成视频输入定时信号。只有当DTG在VESA模式(PC图形信号)下工作时,主模式才可用。

arst_func_n:芯片软件复位

{芯片控制0x03(0)}[1]

0 :功能块进入复位状态。IC寄存器保留值。2

注:在输入视频从输入总线断开并重新连接后(例如,在视频格式更改后),用户需要发出软件重置,以便将内部显示定时生成器正确同步到输入视频源。

1 :正常运行

5.1.2颜色空间转换控制(子地址0x04–0x19)

数字格式:

有符号大小:MSB是符号位,其余位是大小的二进制表示。这不是2s补码符号。

幅值:幅值的二进制表示

csc_ric1(5:0):R/Cr输入信道-G/Y输出信道系数,整数部分

{csc_r11 0x04(7:2)}[00 0000]

系数的6位整数部分,与R/Cr输入相乘,以产生G/Y输出(有符号量值格式)

csc_rfc1(9:0):R/Cr输入通道–G/Y输出通道,小数部分

{csc_r11 0x04(1:0)和csc_r12 0x05(7:0)}[00 0000 0000]

与R/Cr输入相乘的系数的10位小数部分,以产生G/Y输出(幅度格式)

csc_ric2(5:0):R/Cr输入通道–B/Cb输出通道,整数部分

{csc\u r21 0x06(7:2)}[00万]

系数的6位整数部分,与R/Cr输入相乘,以产生B/Cb输出(有符号大小格式)

csc_rfc2(9:0):R/Cr输入通道–B/Cb输出通道,部分

{csc r21 0x06(1:0)和csc r22 0x07(7:0)}[00 0000 0000]

与R/Cr输入相乘的系数的10位小数部分,以产生B/Cb输出(幅度格式)

csc_ric3(5:0):R/Cr输入通道–R/Cr输出通道,整数部分

{csc_r31 0x08(7:2)}[000000]

系数的6位整数部分,与R/Cr输入相乘,以产生R/Cr输出(有符号量值格式)

csc_rfc3(9:0):R/Cr输入通道–R/Cr输出通道,部分

{csc r31 0x08(1:0)和csc r32 0x09(7:0)}[00 0000 0000]

与R/Cr输入相乘的系数的10位小数部分,以产生R/Cr输出(幅度格式)

csc_gic1(5:0):G/Y输入通道–G/Y输出通道,整数部分

{csc_g11 0x0A(7:2)}[00 0000]

与R/Cr输入相乘的系数的6位小数部分,以产生R/Cr输出(幅度格式)

csc_gfc1(9:0):G/Y输入通道–G/Y输出通道,小数部分

{csc_g11 0x0A(1:0)和csc_g12 0x0B(7:0)}[00 0000 0000]

与G/Y输入相乘的系数的10位小数部分,以产生G/Y输出(幅度格式)

csc U gic2(5:0):G/Y输入通道–B/Cb输出通道,整数部分

{csc_g21 0x0C(7:2)}[00 0000]

系数的6位整数部分,与G/Y输入相乘,以产生G/Y输出(幅度格式)csc_gfc2(9:0):G/Y输入通道–B/Cb输出通道,小数部分{csc_g21 0x0C(1:0)和csc_g22 0x0D(7:0)}[00 0000 0000]

与G/Y输入相乘的系数的10位小数部分,以产生B/Cb输出(幅度格式)csc_gic3(5:0):G/Y输入通道-R/Cr输出通道,整数部分{csc_g31 0x0E(7:2)}[00万]

系数的6位整数部分,与G/Y输入相乘,以产生R/Cr输出(有符号量值格式)cscúgfc3(9:0)G/Y输入通道-R/Cr输出通道,部分

{csc_g31 0x0E(1:0)和csc_g32 0x0F(7:0)}[00 0000 0000]与G/Y输入相乘的系数的10位小数部分,以产生R/Cr输出(幅度格式)

csc_bic1(5:0):B/Cb输入通道-G/Y输出通道,整数部分{csc_b11 0x10(7:2)}[00 0000]

系数的6位整数部分,与B/Cb输入相乘,以产生G/Y输出(有符号大小格式)

csc_bfc1(9:0):B/Cb输入通道–G/Y输出通道,小数部分{csc_b11 0x10(1:0)和csc_b12 0x11(7:0)}[00 0000 0000]

系数的10位小数部分,与B/Cb输入相乘,以产生G/Y输出(幅度格式)

csc_bic2(5:0):B/Cb输入通道-B/Cb输出通道,整数部分{csc_b21 0x12(7:2)}[00万]

系数的6位整数部分,与B/Cb输入相乘,以产生B/Cb输出(有符号大小格式)

csc_bfc2(9:0):B/Cb输入通道–B/Cb输出通道,部分{csc_b21 0x12(1:0)和csc_b22 0x13(7:0)}[00 0000 0000]

与B/Cb输入相乘的系数的10位小数部分,以产生B/Cb输出(幅度格式)

csc_bic3(5:0):B/Cb输入通道–R/Cr输出通道,整数部分{csc_b31 0x14(7:2)}[00万]

系数的6位整数部分,与B/Cb输入相乘,以产生R/Cr输出(有符号量值格式)

csc_bfc3(9:0):B/Cb输入通道-R/Cr输出通道,部分{csc_b31 0x14(1:0)和csc_b32 0x15(7:0)}[00 0000 0000]

系数的10位小数部分,与B/Cb输入相乘,以产生R/Cr输出(幅度格式)

csc U偏移量1(9:0):DAC信道1偏移量

{csc_offs1 0x16(7:0)和csc_offs12 0x17(7:6)}[00 0000 0000]用于G/Y输出的偏移值(有符号量值格式)

csc U偏移量2(9:0):DAC信道2偏移量

{csc_offs12 0x17(5:0)和csc_offs23 0x18(7:4)}[00 0000 0000]用于B/Cb输出的偏移值(有符号量值格式)

csc U偏移量3(9:0):DAC信道3偏移量{csc_offs23 0x18(3:0)和csc_offs3 0x19(7:2)}[00 0000 0000]R/Cr输出的偏移值(符号大小格式)csc_旁路:csc块的旁路{csc_offs3 0x19(1)}

0 :未绕过颜色空间转换(CSC)

1 :CSC旁路csc_uof_cntl:csc块的欠/溢出控制{csc_offs3 0x19(1)}[0]彩空间转换器上的过/下流保护逻辑控制0:Under-/overflow protection关闭1:Under-/overflow protection打开3测试控制(子地址0x1A–0x1B)tst_digbypass:旁路至DAC输入{tst_cntl1 0x1A(7)}[0]

0 :正常运行;非旁路

1 :数字逻辑旁路,直接从输入总线控制DACtst_offset:DAC偏移的旁路{tst_cntl1 0x1A(6)}[0]

0 :正常运行;逻辑未绕过

1 :无论模式或dtg U状态如何,编程偏移始终添加到DAC代码中。

tst_delay(1:0):Y延迟路径控制{tst_cntl2 0x1B(7:6)}[00]

在YCbCr模式期间调整Y通道的延迟。快速斜坡:DAC测试控制,快速斜坡{tst_cntl2 0x1B(1)}[0]0 :正常运行

1 :DAC以2×时钟速率输出斜坡。

tst_slow ramp:DAC测试控制,慢速斜坡{tst_cntl2 0x1B(0)}[0]0 :正常运行

1 :DAC以2×时钟速率除以64000输出斜坡。此模式的优先级高于tst_fastramp设置的优先级。

5显示定时发电机控制,第1部分(子地址0x1D–0x3C)

dtg1 U y U空白(9:0):y通道空白电平振幅控制{dtg1_y_sync_msb 0x23(5:4)和dtg1_y_sync1_lsb 0x1D(7:0)}[10 0000 0000 0000]设置y通道的消隐电平的振

dtg1_y_sync_low(9:0):y通道低同步电平幅度控制

{dtg1同步msb 0x23(3:2)和dtg1同步lsb 0x1E(7:0)}[00 0000 0000]

设置Y通道的负同步和均衡/锯齿/宽脉冲的振幅。dtg1_y_sync_high(9:0):y通道高同步电平幅度控制{dtg1_y_sync_msb 0x23(1:0)和dtg1_y_sync3_lsb 0x1F(7:0)}[11 0000 0000]设置y通道正同步的幅度。

dtg1 U cbcr U空白(9:0):Cb/Cr通道空白电平振幅控制{dtg1_Cb Cr_sync_msb 0x24(5:4)和dtg1_cbcr_sync1_lsb 0x20(7:0)}[10 0000 0000 0000]设置Cb和Cr信道的消隐电平的幅度。

dtg1_cbcr_sync_low(9:0):Cb/Cr通道低同步电平幅度控制{dtg1_cbcr_sync_msb 0x24(3:2)和dtg1_cbcr_sync2_lsb 0x21(7:0)}[00 0000 0000]

设置Cb和Cr通道的负同步和均衡/锯齿/宽脉冲的振幅

dtg1_cbcr_sync_high(9:0):Cb/Cr通道高同步电平幅度控制{dtg1_Cb Cr_sync_msb 0x24(1:0)和dtg1_cbcr_sync3_lsb 0x22(7:0)}[11 0000 0000]设置Cb和Cr信道的正同步幅度

dtg1 U规格a(7:0):负同步宽度{dtg1_spec_a 0x25(7:0)}[0010 1100]=[44d]

三电平(HDTV模式)或二电平(SDTV模式)同步负偏移宽度

dtg1_spec_b(7:0):活动视频结束到0H{dtg1 U规格b 0x26(7:0)}[0101 1000]=[88d]

从活动视频结束到负同步开始(SDTV模式)或到三级同步负向正转换(HDTV模式)的距离。

dtg1_spec_c(7:0):正同步宽度(HDTV)/均衡脉冲(SDTV)宽度{dtg1_spec_c 0x27(7:0)}[0010 1100]=[44d]

三电平正偏移宽度(HDTV模式)。均衡脉冲宽度(SDTV模式)。

dtg1_spec_d(8:0):同步到活动视频(SDTV)/同步到宽脉冲(HDTV)

{dtg1_spec_deh_msb 0x2B(7)和dtg1_spec_d_lsb 0x28(7:0)}[0 1000 0100]=[132d]

从Hsync前缘到活动视频开始的距离(SDTV模式)或从三电平同步的负向正转换到宽脉冲开始的距离(HDTV模式)

dtg1_spec_d1(7:0):中心均衡脉冲到活动视频(SDTV){dtg1_spec_d1 0x29(7:0)}[0000 0000]

线中心均衡脉冲到活动视频的距离(SDTV模式)

dtg1_spec_e(8:0):同步到活动视频(HDTV)/彩条启动(VESA)

{dtg1_spec_deh_msb 0x2B(6)和dtg1_spec_e_lsb 0x2A(7:0)}[0 1100 0000]=[192d]

三电平同步从负向正转换到活动视频开始的距离(HDTV模式)。如果在VESA模式下激活颜色条,则此参数指定颜色条相对于水平同步的开始位置。

dtg1_spec_h(9:0):宽脉冲持续时间(SDTV)

{dtg1_spec_deh_msb 0x2B(1:0)和dtg1_spec_h_lsb 0x2C(7:0)}[00 0000 0000]宽脉冲持续时间(SDTV模式)。

dtg1_spec_i(11:0):全线宽脉冲持续时间(SDTV)

{dtg1戋U规格i戋U msb 0x2D(3:0)和dtg1戋U规格i戋U lsb 0x2E(7:0)}[0000 0000 0000]全线宽脉冲持续时间(SDTV模式)

dtg1_spec_k(10:0):活动视频结束同步(SDTV)/宽脉冲结束同步(HDTV)

{dtg1_spec_k_msb 0x30(2:0)和dtg1_spec_k_lsb 0x2F(7:0)}[000 0101 1000]=[88d]

从活动视频结束到同步前沿(SDTV)的距离,或从宽脉冲结束到三电平同步(HDTV)的负向正转换的距离

dtg1_spec_k1(7:0):线对中心均衡脉冲(SDTV)上半段活动视频结束{dtg1 U规格k1 0x31(7:0)}[00000000]

SDTV线型有源滤波器上半行距有源视频端到中心均衡脉冲的距离

dtg1 U规格(11:0):线路长度的1/2(SDTV){dtg1_spec_g_msb 0x33(3:0)和dtg1_spec_g_lsb 0x32(7:0)}[0000 0101 1000]=[88d]一半的行长度。仅用于计算SDTV线路类型

dtg1_总像素(12:0):每行总像素(SDTV/HDTV/VESA){dtg1_total_pixels_msb 0x34(4:0)和dtg1_total_pixels_lsb 0x35(7:0)}[0 0101 0010 0000]=[1312d]每行的像素总数。用于所有DTG模式dtg1_field_flip:FID/F极性选择{dtg1_fieldflip_linecnt_msb 0x36(7)}[0]

0 :当接收到FID信号或F位上的0时,DTG在活动VS边缘初始化为field1。

1 :当接收到FID信号或F位上的1时,DTG在活动VS边缘初始化为field1。

dtg1_linecnt(10:0):DTG起始行号{dtg1_fieldflip_linecnt_msb 0x36(2:0)和dtg1_linecnt_lsb 0x37(7:0)}[000 0000 0001]

设置断言Vsync输入或V位时DTG的起始行号(垂直显示控件)

DTG开/关{dtg1_模式0x38(7)}[1]

0 :DTG输出保持为DTG_y_空值

1 :DTG打开DTG通过:DTG通过{dtg1_模式0x38(4)}[0]

0 :某些线路类型期间视频数据被阻止

1 :在某些行类型期间传递的视频数据

视频与计算机图形应用

THS8200是一种高度集成和灵活的通用模拟组件视频/图形发生器,可用于任何需要视频/图形信号D/a转换的应用。

在典型的视频应用(例如DVD播放器、机顶盒)中,THS8200从MPEG解码器或媒体处理器引擎接收其输入,并将信号转换为模拟域,从而为所选格式生成正确的定时/帧格式。

它的ITU-R.BT656输出端口可用于连接NTSC/PAL视频编码器,如德州仪器TVP6000,用于常规的复合/S视频输出。

请注意,由于DAC速度的额定值高达205 MSPS,所有流行的SDTV和HDTV格式(包括1080I和720P)都支持1×和2×插值模式。1080P以1×速率支持。

典型视频应用

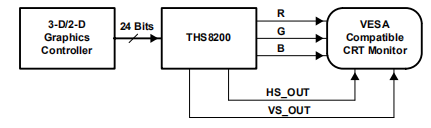

由于其可编程的Hsync/Vsync输出、对RGB以及YCbCr颜色空间的片上支持以及其内部颜色空间转换电路,以及205 MSPS的DAC运算速度,所有的PC图形格式都得到了支持,在75 Hz时可达UXGA。视频插值现在被忽略,因此完整的205 MSPS可用于1×像素时钟

计算机图形学应用

DVI到模拟YPbPr/RGB应用

与DVI接收器一起,该设备形成双芯片解决方案,使用嵌入式复合同步或单独的Hsync、Vsync将通过DVI接口发送的视频或图形格式转换为模拟RGB或YPbPr格式。THS8200使用其数据输入总线和HS_-IN和VS_-IN终端无胶连接到DVI接收器。TI-DVI 1.0(带HDCP)接收机提供在活动视频窗口期间高的数据启用(DE)信号。THS8200可配置为在其FID终端上解释该数据元素信号,以自动插入用户可编程

在其模拟输出上处于活动视频窗口外的消隐电平振幅;此消隐电平可以正确定位为RGB或YPbPr模拟输出。用户可以选择在THS8200中执行颜色空间转换,并通过设备的CSM块调整偏移和增益范围。

当通过DVI发送(隔行)视频时,EIA-861规范描述了一种从Hsync和Vsync信号的相对对准中导出DVI1.0(带HDCP)接收器不能直接获得的fieldID信号的方法。可以将THS8200配置为根据本规范从Hsync/Vsync对准中在内部获得正确的偶数/奇数字段标识,而不是在其FID输入端子上使用FieldID信号。这避免了在DVI应用程序中需要额外的粘合逻辑。

主/从计时模式

在从计时模式下,THS8200输出显示计时与视频数据源同步。显示定时输出信号基于输入同步信号,或馈送到专用Hsync、Vsync和FieldID(HS-IN、VS-IN和FID)输入终端上的设备,或基于嵌入在输入视频数据中的SAV/EAV代码。

THS8200从机运行方式在主定时模式下,THS8200产生两组输出同步信号

HS_-IN和VS_-IN现在成为视频源的输出信号(未使用FID)

HS_-OUT和VS_-OUT仍输出信号至显示设备

其目的是THS8200从需要外部定时的源(例如视频存储器)请求视频数据

HS8200主运行方式