AD5544点击型号即可查看芯片规格书

AD5554点击型号即可查看芯片规格书

特征

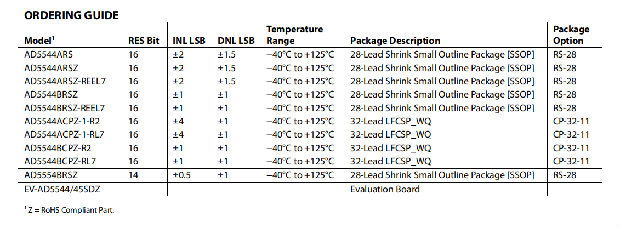

AD5544电话:16位分辨率;入口为±1 LSB(B级);AD5554电话:14位分辨率;最小有效位±0.5(B级);2毫安满标度电流±20%,VREF=±10 V;0.9μs沉淀时间至±0.1%;12兆赫倍频带宽中刻度故障-1 nV秒;中刻度或零刻度重置;4个独立的4象限乘法参考输入;SPI兼容,3线接口;双缓冲寄存器启用;多通道同时切换;内部通电复位;温度范围:-40°C至+125°C;紧凑型28导SSOP和32导LFCSP。

应用

自动测试设备;仪表数字控制校准。

一般说明

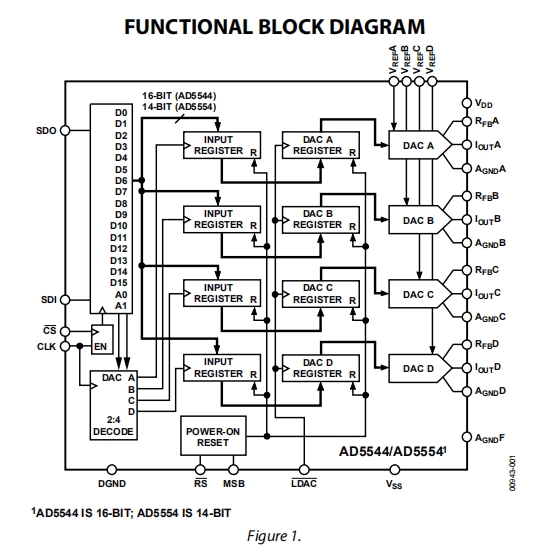

AD5544/AD5554四位、16-/14位、电流输出、数模转换器(DAC)设计为在2.7 V至5.5 V电源范围内工作。

外加外部参考输入电压(Vx)决定满标度输出电流。集成反馈电阻(R)提供温度跟踪,全尺寸电压输出时,结合外部I-to-V精密放大器。

双缓冲串行数据接口提供高速,3线,使用串行数据的SPI和微控制器兼容输入(SDI)、芯片选择(CS)和时钟(CLK)信号。此外,当使用多个包时,串行数据输出引脚(SDO)允许菊花链。一个普通的、电平敏感的、负载DAC选通(LDAC)输入允许从先前加载的输入寄存器同时更新所有DAC输出。此外,内部上电复位在系统接通时将输出电压强制为0。

MSB pin允许系统重置断言(RS)在MSB=0时将所有寄存器强制为零代码,或在MSB=1时强制为半刻度代码。

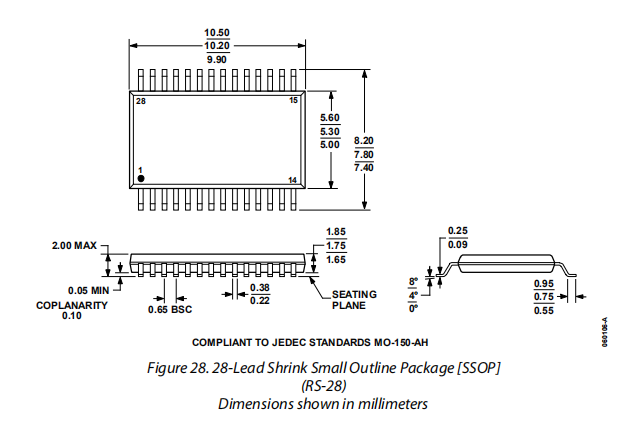

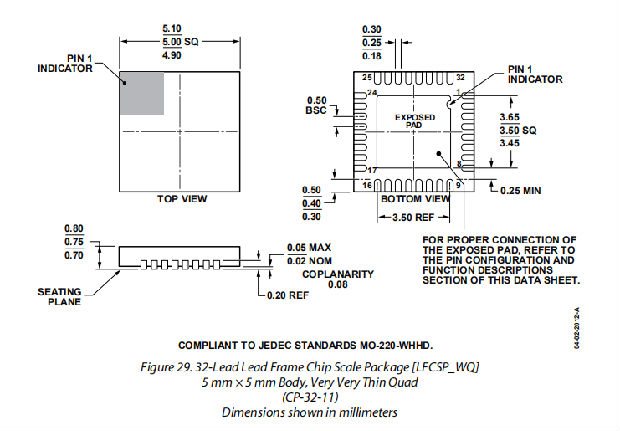

AD5544封装在紧凑型28引线SSOP和32引线LFCSP中。AD5554封装在紧凑型28引线SSOP中。

EV-AD5544/45SDZ可用于评估DAC性能。有关详细信息,请参阅《UG-285评估板用户指南》。

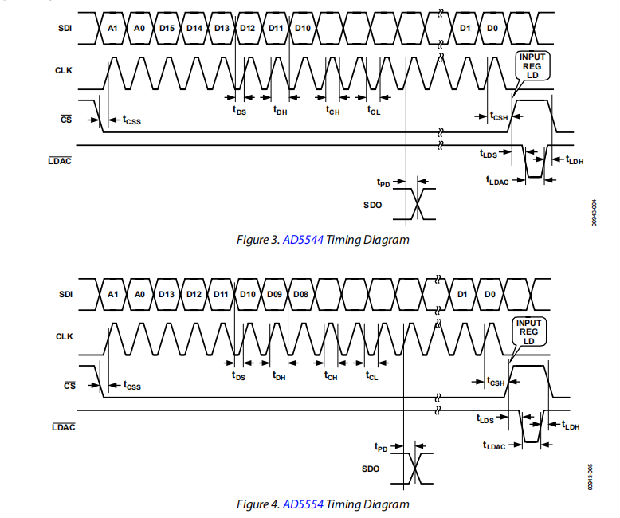

时序图

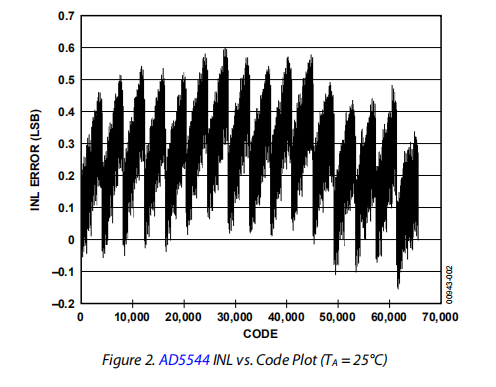

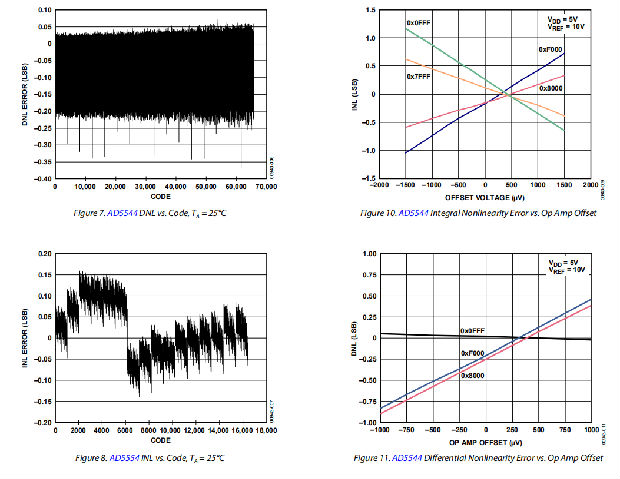

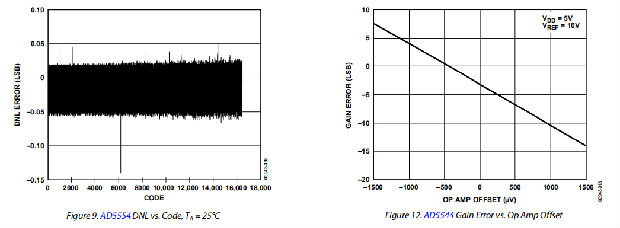

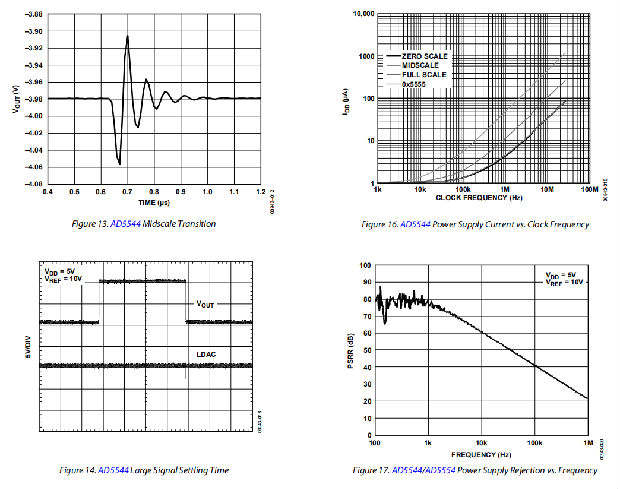

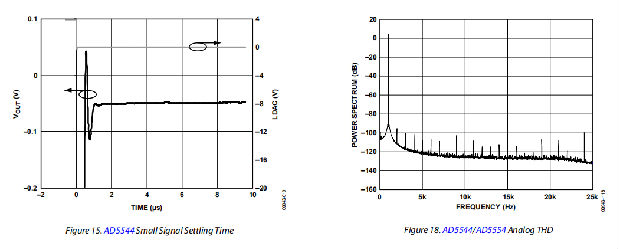

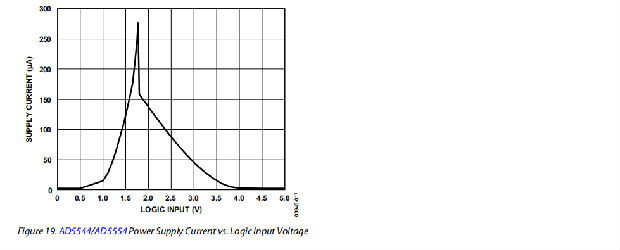

典型性能特征

操作理论

AD5544和AD5554分别包含四个16位和14位电流输出DAC。每个DAC都有自己独立的乘法参考输入。AD5544和AD5554都使用一个3线、SPI兼容的串行数据接口,带有可配置的半标度异步RS引脚(MSB=1)或零点刻度(MSB=0)预设。此外,一个LDAC选通电路可以实现4通道同步更新,以实现硬件同步输出电压的变化。

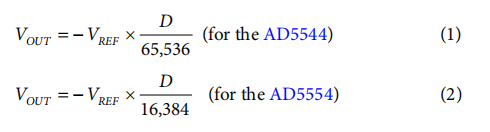

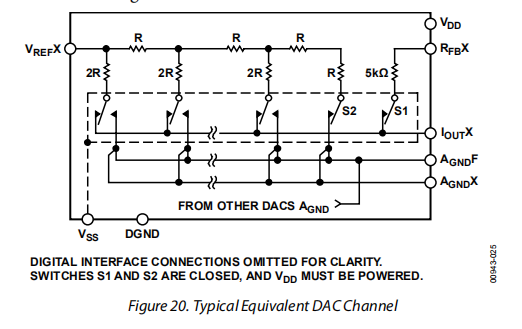

数模转换器(DAC)

每个部分包含四个电流转向R-R梯形DAC。图20显示了典型的等效DAC。每个DAC包含一个匹配的反馈电阻,用于外部I-to-V转换器放大器。Rx引脚连接到外部放大器的输出端。Ix端子连接到外部放大器的反向输入。Ax引脚应与加载点连接,要求完全16位精度。这些数模转换器设计用于在负参考电压和正参考电压下工作。

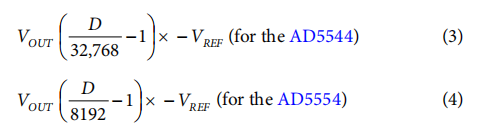

V电源引脚仅用于逻辑驱动DAC开关的开和关。注意,匹配开关与内部5 kΩ反馈电阻器串联使用。如果用户试图测量R的值,则必须对V施加功率以实现连续性。在高温应用期间,额外的V偏压管脚用于保护基板,将每10°C增加一倍的零刻度泄漏电流降至最低。DAC输出电压由V和以下方程式中的数字数据(D)确定:

注意,输出极性与直流参考电压的V极性相反。

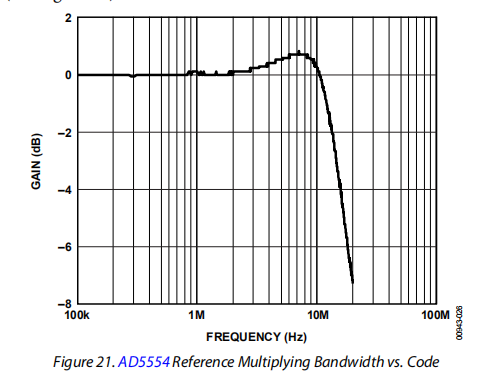

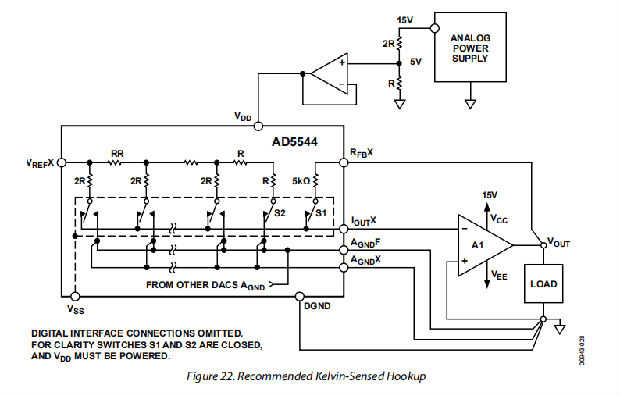

这些数模转换器也被设计用来容纳交流参考输入信号。AD5544和AD5554都能在-15 V到+15 V的范围内调节输入参考电压。参考电压输入显示恒定的标称输入电阻为5 kΩ±30%。另一方面,IA、IB、IC和ID DAC输出依赖于代码,并产生各种输出电阻和电容。外部放大器的选择应考虑AD5544/AD5554在放大器的反向输入节点上产生的阻抗变化。反馈电阻与DAC梯形电阻并联,控制输出电压噪声。对于倍增模式应用,可能需要外部反馈补偿电容器C,以提供基准输入电压阶跃变化的临界阻尼输出响应。图21显示了使用分别连接在AD5544和AD5554的Ix和Rx端子上的23pf外部反馈电容器在各种衰减设置下的增益与频率性能。为了保持良好的模拟性能,建议电源绕过0.01μF,并与1μF并联。在这种情况下,应使用具有低纹波电压能力的清洁电源。开关电源由于具有较高的纹波电压和PSS频率依赖特性,通常不适合这种应用。最好从系统模拟电源电压导出AD5544/AD5554的电源。不要使用数字电源(见图22)。

串行数据接口

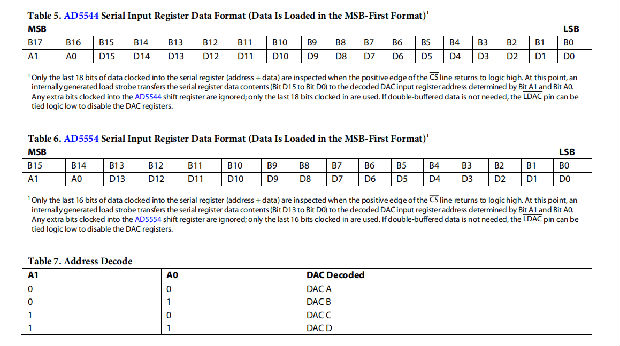

AD5544/AD5554使用3线(CS、SDI、CLK)SPI兼容串行数据接口。AD5544/AD5554的串行数据分别以18位和16位数据字格式被时钟送入串行输入寄存器。首先加载MSB位。表5定义AD5544的18个数据字位,表6定义AD5554的16个数据字位。根据接口定时规范(见表1和表2)中规定的数据设置和数据保持时间要求,将数据放在SDI引脚上,并在CLK正时钟边缘的寄存器中计时。

只有当CS芯片选择引脚处于低激活状态时,才能对数据进行时钟输入。对于AD5544,当CS引脚返回逻辑高状态时,只有最后18位进入串行寄存器;额外的数据位被忽略。对于AD5554,当CS引脚返回逻辑高状态。因为大多数微控制器以8位字节输出串行数据,所以三个右对齐的数据字节可以写入AD5544。在第一字节、第二字节和第三字节传输之间保持CS行低位将导致串行寄存器更新成功。

类似地,两个右对齐的数据字节可以写入AD5554。在第一个字节和第二个字节之间保持CS行低位会导致串行寄存器更新成功。

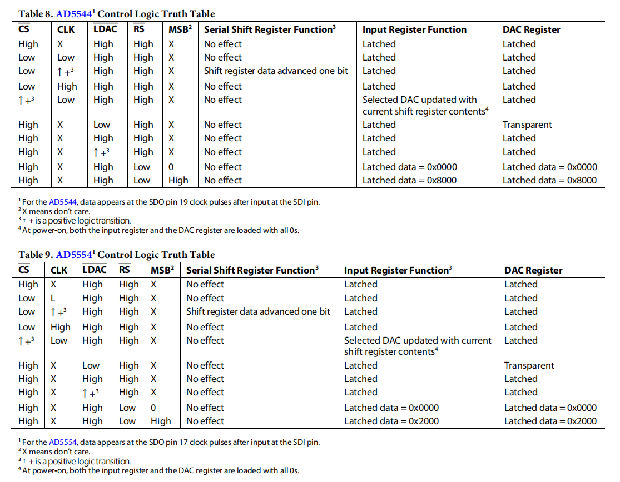

当数据在移位寄存器中正确对齐时,CS的正边缘启动新数据到目标DAC寄存器的传输,由地址位A1和地址位A0的解码确定。对于AD5544,表5、表7、表8和图3定义了软件串行接口的特性。

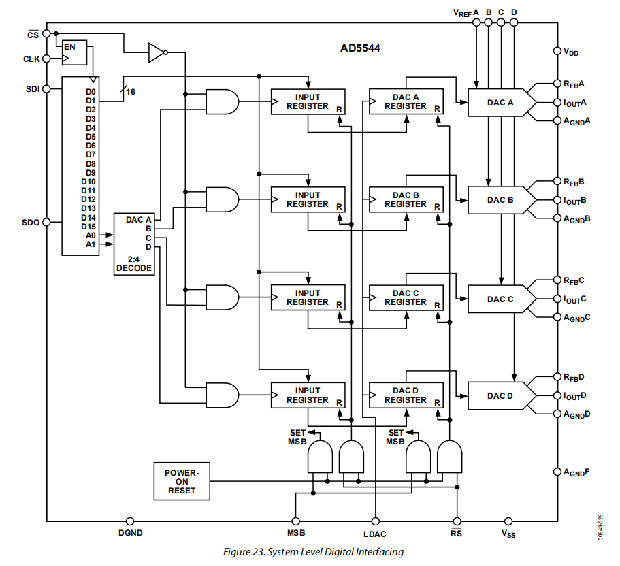

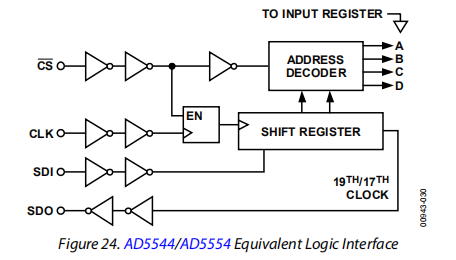

对于AD5554,表6、表7、表9和图4定义了软件串行接口的特性。图23和图24显示了AD5544关键数字控制管脚的等效逻辑接口。AD5554具有类似的配置,只是它有14个数据位。另外两个引脚,RS和MSB,提供了对预置功能和DAC寄存器加载的硬件控制。如果不需要这些功能,RS引脚可以绑定到逻辑高。异步输入RS pin将所有输入和DAC寄存器强制为零代码状态(MSB=0)或半刻度状态(MSB=1)。

上电复位

当V电源打开时,内部复位选通将所有输入和DAC寄存器强制到零代码状态或半刻度状态,具体取决于MSB引脚电压。V电源应具有平滑的正斜坡,且不会下垂,以获得一致的结果,特别是在V=1.5 V至2.3 V的区域。V电源对上电复位性能没有影响。DAC寄存器数据保持在零刻度或半刻度设置,直到发生有效的串行寄存器数据加载。

ESD保护电路

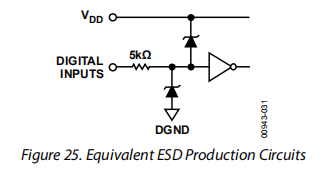

所有的逻辑输入管脚都包含反向偏置的ESD保护齐纳二极管,它们连接到地(DGND)和V上,如图25所示。

供电顺序

作为标准做法,建议在进行任何参考之前,对V、V和接地进行通电。理想的通电顺序如下:Ax、DGND、V、V、Vx和数字输入。不一致的通电顺序可能会升高参考电流,但一旦V和V通电,设备将恢复正常工作。

布局和电源旁路

最好采用紧凑、最小引线长度的布局设计。通向输入端的导线应尽可能直接,导线长度最小。接地路径应具有低电阻和低电感。

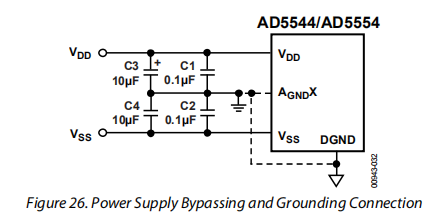

同样,为了获得最佳的稳定性,最好使用高质量电容器绕过电源。应使用0.01μF至0.1μF的片状或片状陶瓷电容器绕过设备的电源线。低ESR 1μF至10μF钽或电解电容器也应在V下使用,以最小化任何瞬态干扰,并过滤任何低频纹波(见图26)。由于电源抑制比(PSRR)随频率的降低,用户不应为V应用开关调节器。

接地

AD5544/AD5554的DGND和Ax管脚用作数字和模拟接地参考。为了将数字地面反弹降到最低,DGND终端应远程连接到模拟地面的一个点上(见图26)。

应用程序信息

AD5544/AD5554本质上是两象限乘法DAC。也就是说,它们可以很容易地设置为单极输出操作。满标度输出极性与参考输入电压成反比。

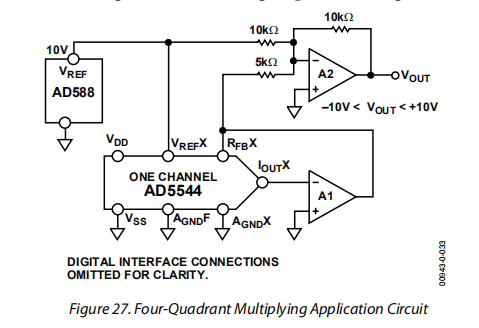

在某些应用中,可能需要产生全四象限乘法能力或双极性输出摆幅。使用配置为求和放大器的附加外部放大器(A2)很容易实现(见图27)。

在该电路中,第一和第二放大器(A1和A2)提供2的总增益,该总增益将输出电压跨距增加到20v。使用与参考电压偏移10v的外部放大器偏置可产生完整的四象限乘法电路。该电路的传输方程表明,当输入数据(D)从代码0(V=-10 V)增加到中刻度(V=0 V)到满刻度(V=10 V)时,会产生负输出电压和正输出电压。

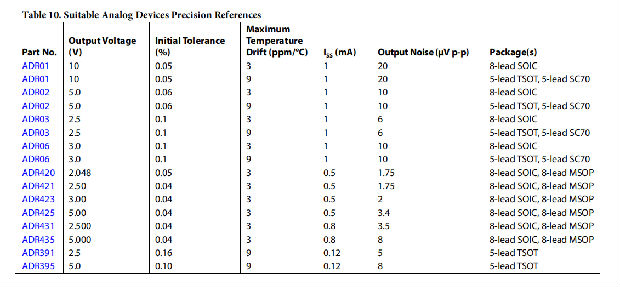

参考选择

选择与AD55xx系列电流输出DAC一起使用的基准时,注意基准的输出电压、温度系数规格。选择一个低输出温度系数的精密参考,使误差源最小化。表10列出了可从Analog Devices,Inc.获得的适用于此范围电流输出DAC的一些参考资料。

放大器选择

电流转向模式的主要要求是具有低输入偏置电流和低输入偏置电压的放大器。由于DAC的码相关输出电阻,运算放大器的输入偏置电压乘以电路的可变增益。由于放大器的输入偏移电压,两个相邻数字部分之间的噪声增益的变化会导致输出电压的阶跃变化。这种输出电压变化叠加在两个代码之间的期望输出变化上,并产生差分线性误差,如果误差足够大,则可能导致DAC非单调。

运算放大器的输入偏置电流也在电压输出处产生偏移,这是因为反馈电阻R中的偏置电流。

运算放大器的共模抑制在电压开关电路中很重要,因为它在电路的电压输出端产生一个与码相关的误差。

如果DAC开关是由真正的宽带、低阻抗源(V和AGND)驱动的,它们很快就会稳定下来。因此,电压开关DAC电路的转换速率和稳定时间在很大程度上取决于输出运放。为了在这种配置中获得最小的稳定时间,在DAC的V节点(本应用中的电压输出节点)处最小化电容。这是通过使用低输入电容缓冲放大器和仔细的电路板设计完成的。

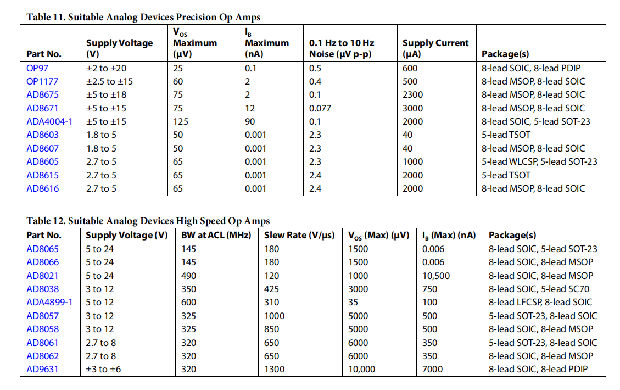

如表11和表12所列,模拟设备为精密直流和交流应用提供了广泛的放大器。

外形尺寸