ISO1540点击型号即可查看芯片规格书

特征

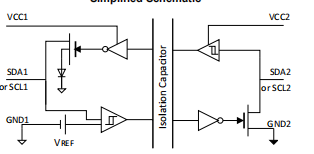

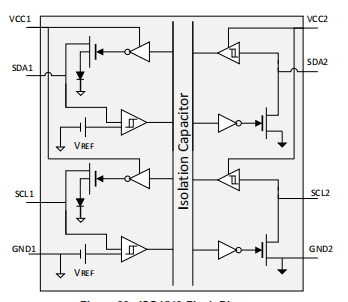

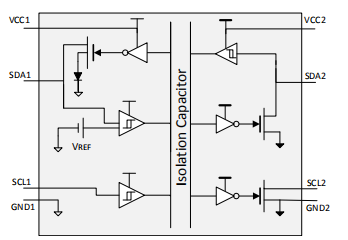

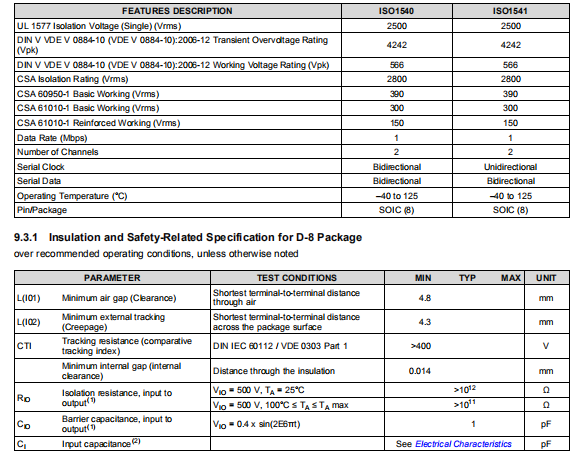

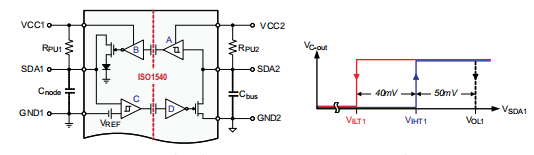

描述ISO1540和ISO1541设备是低功耗的,1隔离双向,I2C兼容,与I2C通信接口兼容的双向隔离器。这些设备有它们的逻辑输入和支持高达1兆赫的操作输出缓冲区,由TI的电容隔离分离使用二氧化硅(二氧化硅)屏障的3-V至5.5-V电源范围技术。3.5毫安1侧和35侧的开漏输出-当与隔离电源一起使用时,这些mA设备可阻断高压、隔离接地和2侧汇电流能力防止噪声电流进入当地地面–40°C至+125°C工作温度,干扰或损坏敏感电路。±50千伏/微秒瞬态抗扰度(典型值)此隔离技术提供功能,所有插脚上的4千伏HBM ESD保护;性能、尺寸和功耗与光耦合器相比,8千伏总线引脚的优势。这个安全和监管批准ISO154和ISO1541设备使隔离的I2C接口将按照DIN V VDE V 0884-10小尺寸因数在–4242-VPK隔离内实现(VDE V 0884-10):2006年12月–2500-V根据UL 1577,ISO154有两个隔离的双向通道RMS隔离1分钟对于时钟和数据线,而ISO1541具有–CSA部件验收通知5A、IEC双向数据和单向时钟信道。60950-1和IEC 61010-1终端设备ISO1541适用于标准单主,而ISO1540是理想的适合多-–CQC基本绝缘符合GB4943.1-2011主应用。隔离双向通信是通过抵消隔离I侧1低电平输出电压值大于2C总线因此,SMBus和PMBus接口防止了内部逻辑锁存,否则会开放式排水网络采用标准数字隔离器。

电机控制系统设备信息(1)

电池管理零件号包装本体尺寸(标称)I2C水平位移

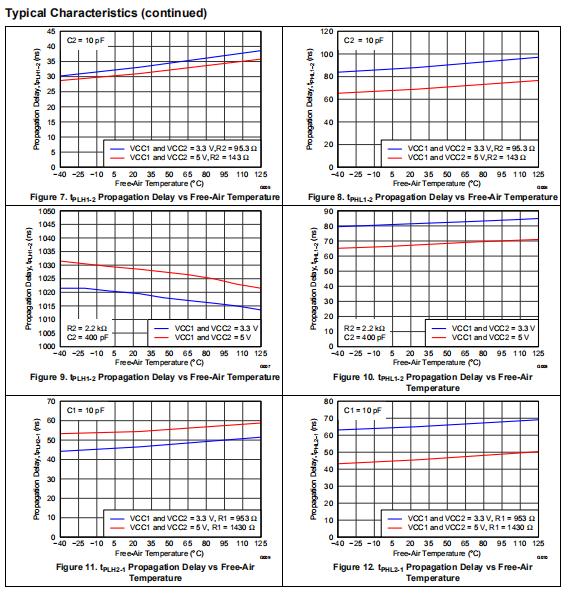

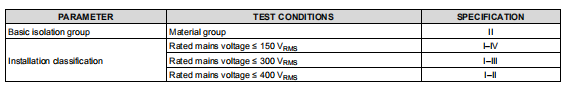

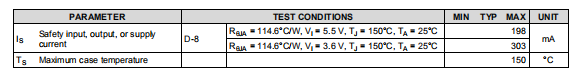

电气特性

超过推荐的操作条件,除非另有说明

(1) 此参数不适用于ISO1541 SCL1线,因为它是单向的。

(2) ΔVOIT1=第1卷–第1卷。这表示低电平输出电压和高电平输入电压之间的最小差用于防止双向通信中可能存在的永久锁存状态的阈值。

(3) 任何一侧的VCC电压低于最小值都将确保设备锁定。两个VCC电压都大于最大值防止设备锁定。

I2C总线由于使用简单而被广泛应用。这辆公共汽车由两根电线组成支持主从之间双向数据传输的通信总线。主人或处理器控制总线,特别是串行时钟(SCL)线路。数据在主机和通过串行数据(SDA)线从机。此数据可以以四种速度传输:标准模式(0到100kbps)、快速模式(0到400 kbps)、快速模式增强(0到1 Mbps)和高速模式(0到3.4 Mbps)。最多的普通速度是标准和快速模式。I2C总线以双向半双工模式工作,而标准数字隔离器是单向的设备。为了有效地利用一种技术支持另一种技术,需要外部电路将双向总线分为两个单向信号路径,而不引入有效传播延迟。这些器件的逻辑输入和输出缓冲区被TI的电容隔离技术隔开使用二氧化硅(二氧化硅)屏障。当与隔离电源一起使用时,这些设备会阻塞高压,隔离接地,防止噪声电流进入本地接地,干扰或损坏敏感电路。

ISO设备使一个完整的隔离I?C接口能够在一个小的外形尺寸内实现以下特点:

1) 屏障每侧的所有插脚连接在一起,形成一个2端设备。

(2) 从输入引脚到接地测量。

安全限制旨在防止输入或输出电路发生故障时对隔离屏障造成潜在损坏。I/O的故障会导致对地或电源的低电阻,并且在没有电流限制的情况下,会消散足够的功率使模具过热并损坏隔离屏障,可能导致二次系统失败。

安全极限约束是绝对最大值中规定的绝对最大结温评级。安装在应用中的装置的功耗和结对空气的热阻抗硬件决定结温。假设结对空气的热阻信息是安装在高K测试板上的铅表面贴装封装设备的信息。权力是建议的最大输入电压乘以电流。结温就是环境温度温度加上功率乘以结对空气的热阻。

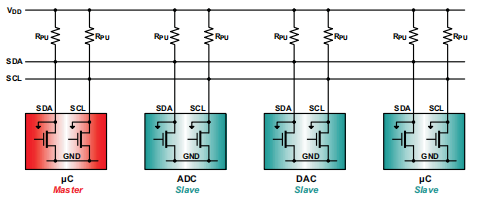

内部集成电路(I2C)总线是一个单端、多主、2线总线,用于高效的内部集成电路半双工通信模式。I2C采用开放式漏极技术,需要连接串行数据(SDA)和串行时钟(SCL)两条线路通过电阻器连接到VDD(见图25)。当让线路接地时,将线路接地视为逻辑零浮点运算是一种逻辑运算。这被用作通道访问方法。当SCL为低,SCL高时的转换表示启动和停止条件。典型电源电压为3.3 V和5五、 尽管允许使用电压较高或较低的系统。

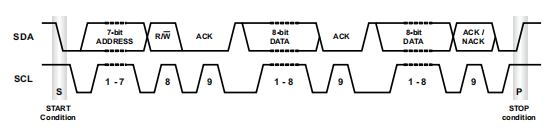

I2C通信使用带有16个保留地址的7位地址空间,因此理论上最大值为112节点可以在同一总线上通信。然而,在实践中,节点的数量受指定的,总线总电容为400 pF,将通信距离限制在几米以内。ISO1540和ISO1541的指定信令速率为100kbps(标准模式),400kbps(快速模式),1 Mbps(快速模式增强)。总线对节点有两个角色:主节点和从节点。主节点发出时钟、从节点地址以及启动和结束数据事务。从节点接收时钟和地址并响应请求那里。图26显示了主设备和从设备之间的典型数据传输。

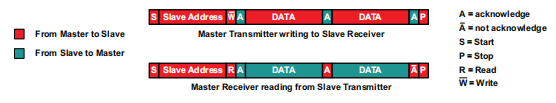

主服务器通过创建一个启动条件来启动一个事务,然后是从服务器的7位地址希望与沟通。后面跟着一个读/写位,表示主机是否希望写入(0)或从(1)从机读取。然后,主服务器释放SDA线路,以允许从服务器确认收到数据。从机通过在9号的整个高时间内将SDA拉低以应答位(ACK)响应SCL上的时钟脉冲,之后主机继续处于发送或接收模式(根据R/W位发送),而从机继续处于互补模式(分别为接收或发送)。首先发送地址和8位数据字节的最高有效位(MSB)。起始位由SCL高时SDA由高到低的转变。停止条件是由SDA从低到高的转换创建的而SCL高。如果主服务器写入从服务器,它会重复发送一个字节,从服务器发送一个ACK位。在这种情况下主设备处于主传输模式,从设备处于从接收模式。如果主服务器从从服务器读取数据,它会重复地从从服务器接收一个字节,同时确认(ACK)接收除最后一个字节以外的每个字节(见图27)。在这种情况下,主机处于主机接收模式,并且从机处于从机传输模式。主机用一个停止位来结束传输,或者可以发送另一个开始位来保持总线控制进一步转移。

当写入从机时,主机主要在发送模式下工作,只有在从从属服务器接收应答。从机读取数据时,主机以发送模式启动,发送后变为接收模式对从机的读请求(R/W位=1)。从机继续处于互补模式,直到交易。请注意,主机通过不确认(NACK)接收到的最后一个字节来结束读取序列。这个过程重置从状态机,并允许主机发送停止命令。

为了隔离双向信号路径(SDA或SCL),ISO1540在内部将双向线分成两条单向信号线,每个信号线通过单通道数字隔离器隔离。各通道输出采用开放式漏极,以符合I2C的开放式漏极技术。ISO154的1侧连接低电容I2C节点,而2侧设计用于连接高达400 pF的满载I2C总线电容。

乍一看,内部缓冲器的布置表明一个容易闭锁的闭合信号回路。但是,通过实现输出缓冲区(B),该输出缓冲区的输出低电平由二极管升高,从而断开该环路降到大约0.75 V,输入缓冲器(C)由一个具有规定滞后的比较器组成。这个比较器的上下输入阈值然后区分0.4V的适当低电位由SDA1直接驱动的最大值和B的缓冲输出低电平。图29显示了I2C隔离器ISO1540在SDA1和SDA2的一辆重载公共汽车。

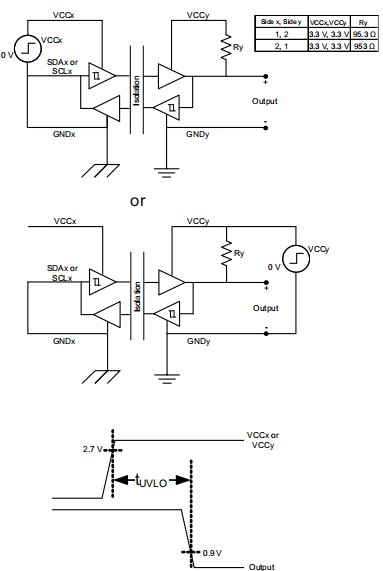

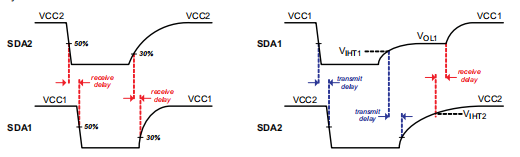

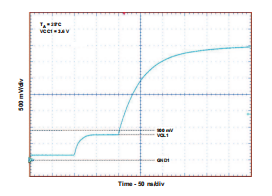

当I2C总线驱动SDA2低时,SDA1在接收路径中经过一定的延迟后跟随。它的产量低VOL1=0.75v的缓冲输出,足够低,施密特触发器输入用最低输入低电压VIL=0.9V,3V电源水平。一旦SDA2被释放,其电压电位随着RPU2形成的时间常数向VCC2方向增加以及CBU。在接收延迟之后,SDA1被释放,并随着时间常数向VCC1上升RPU1×中海油。由于时间常数显著降低,SDA1可能在SDA2到达之前到达VCC1VCC2电位。

当主驱动器SDA1低时,SDA2在传输方向上经过一定的延迟后跟随。当SDA2转动时低它也会导致缓冲区B的输出变低,但在较高的0.75 V电平。不能观察到这个水平立即被主人的低层覆盖。但是,当主控释放SDA1时,其电压电位升高,首先必须通过上输入比较器VIHT1释放SDA2的阈值。然后SDA1进一步增加,直到到达缓冲区VOL1的输出电平=0.75 V,由接收路径保持。比较器C调高后,释放SDA2传输方向延迟后。它需要另一个接收延迟,直到B的输出变高并完全释放SDA1向VCC1电位移动。

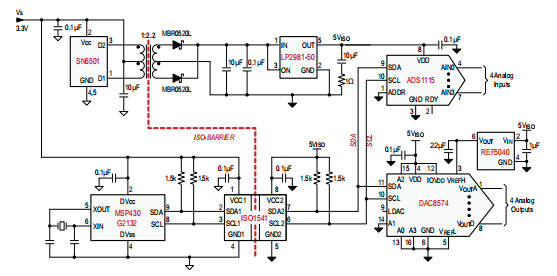

10.2典型应用

在图30中,超低功耗微控制器MSP430G2132控制配置的I2C数据流量模拟输入和输出的数据和转换结果。低功耗数据转换器构建模拟与传感器和执行器的接口。ISO1541提供了不同接地之间的必要隔离系统控制器、遥感器和执行器电路防止接地回路电流否则可能会伪造获得的数据。整个电路由一个3.3伏电源供电。小功率推挽转换器SN6501驱动中心抽头变压器,其输出经整流和线性调节,为数据提供稳定的5伏电源转换器

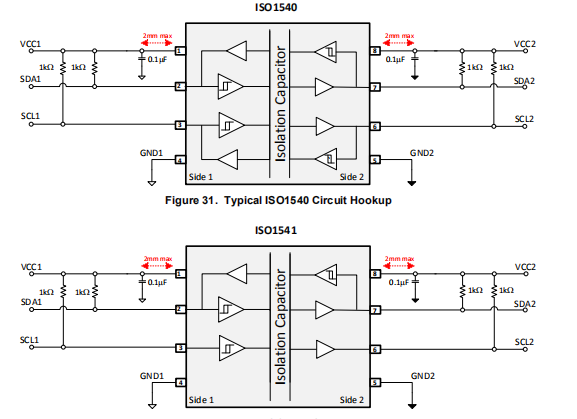

建议的电源电压(VCC1和VCC2)必须在3 V到5.5 V之间。建议去耦VCC1至GND1和VCC2至GND2之间需要0.1-μF的电容器,以保护电源电压瞬变并确保在所有数据速率下可靠运行0.1-μF的电源电容器必须尽可能靠近电源引脚。

推荐的电容器位置必须最大为2毫米,远离输入和输出电源引脚(VCC1和VCC2)。输入SDA1和SCL1线路上允许的最大负载≤40pf,输出SDA2和SCL2线路上允许的最大负载≤400磅力。VCC1的输入SDA1和SCL1线路上的最小上拉电阻的选择必须使输入电流消耗小于等于3.5毫安。必须在VCC2的输入SDA2和SCL2线上选择最小上拉电阻输出电流小于等于35ma。输入线上的最大上拉电阻(SDA1和SCL1)至VCC1和输出线(SDA1和SCL1)至VCC2将取决于负载和上升时间要求在各自的线路上。

为确保在所有数据速率和电源电压下可靠运行,TI建议在输入和输出电源引脚(VCC1和VCC2)。电容器应尽可能靠近电源引脚可能的。如果应用程序中只有一个一次侧电源可用,则可以在变压器驱动器(如TI的SN6501)的帮助下为二次侧生成。为了这样应用、详细的电源设计和变压器选择建议见SN6501数据表(SLLSEA0)。

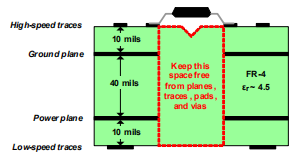

完成低EMI PCB设计至少需要四层(见图34)。层叠应按以下顺序(从上到下):高速信号层、地平面、电源平面和低频

信号层。在顶层布线高速记录道,避免了过孔的使用(以及过孔的引入感应)并允许隔离器与发射机和接收机电路之间的干净互连数据链路的。在高速信号层旁边放置一个实心接地平面,为传输线相互连接,为回流提供了一个极好的低电感路径。将电源平面放置在接地板旁边,产生额外的高频旁路电容大约100 pF/in2。•在底层路由较慢的速度控制信号,使这些信号链路具有更大的灵活性通常有足够的裕度来承受不连续性,如过孔。如果需要额外的电源电压平面或信号层,则将第二个电源或接地平面系统添加到使其保持对称的堆栈。这样可以使堆栈在机械上保持稳定并防止其翘曲。还有每个电力系统的电源和接地平面可以放在一起,从而增加高频旁路电容明显。

对于工作在150 Mbps以下(或上升和下降时间大于1 ns)的数字电路板,迹线长度为高达10英寸,使用标准的FR-4环氧玻璃作为PCB材料。FR-4(阻燃剂4)符合保险商实验室UL94-V0的要求,由于其高频时介电损耗低,吸湿性小,强度和刚度大,具有自熄燃烧特性