AD7734点击型号即可查看芯片规格书

特征

高分辨率模数转换器(ADC);24位无缺码;±0.0025%非线性;为快速通道切换而优化;500Hz时18位p-p分辨率(21位有效)2 kHz时16位p-p分辨率(19位有效);15 kHz时14位p-p分辨率(18位有效);片上每通道系统校准;4个单端模拟输入;输入范围+5 V,±5 V,+10 V,±10 V过电压容限;高达±16.5 V,不影响相邻通道;最大绝对电压不超过±50 V;三线串行接口;大豆分离蛋白™,MICROWIRE和DSP兼容;逻辑输入施密特触发器;单电源操作;5V模拟电源;3V或5V数字电源包:28导TSSOP。

应用

可编程逻辑控制器/集散控制系统;多路复用应用程序;过程控制工业仪表。

一般说明

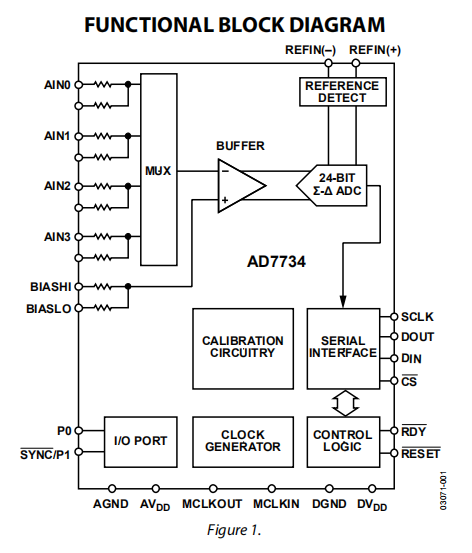

AD7734是一款高精度、高吞吐量的模拟前端。真正的16位p-p分辨率是可以实现的,总转换时间为500μs(2 kHz信道切换),这使得它非常适合高分辨率复用应用。

该设备可以通过一个简单的数字接口进行配置,该接口允许用户将噪声性能与高达15.4khz的数据吞吐量进行平衡。

模拟前端具有四个单端输入通道,单极或真双极输入范围为±10 V,同时从一个+5 V模拟电源运行。该装置具有超量程和超量程检测能力,在不降低相邻通道性能的情况下,可接受±16.5 V的模拟输入过电压。

差分参考输入具有“无参考”检测能力。ADC还支持每通道系统校准选项。数字串行接口可以配置为3线操作,与微控制器和数字信号处理器兼容。所有接口输入均由施密特触发。

该设备规定在-40°C至+105°C的扩展工业温度范围内运行。

AD7734系列中的其他设备是AD7732和AD7738。

AD7732与AD7734类似,但其模拟前端具有两个全差分输入通道。

AD7738模拟前端可配置为四个全差分或八个单端输入通道,具有0.625 V至2.5 V双极/单极输入范围,接受200 mV至AVDD–300 mV的共模输入电压。AD7738多路复用器输出在外部固定,允许用户在应用于ADC之前实现可编程增益或信号调节。

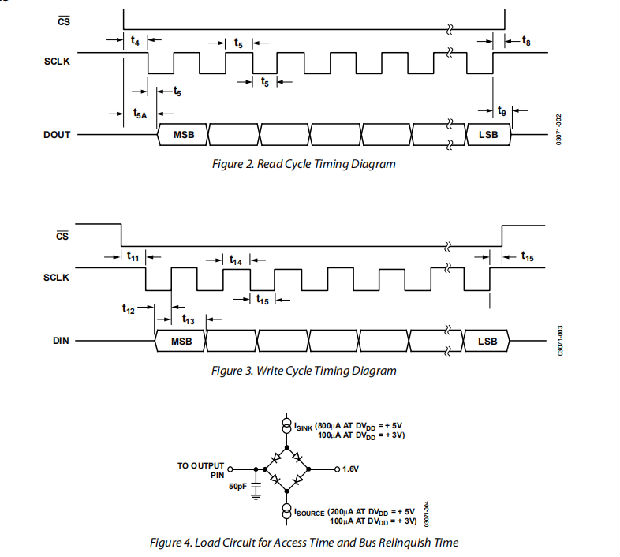

时序图

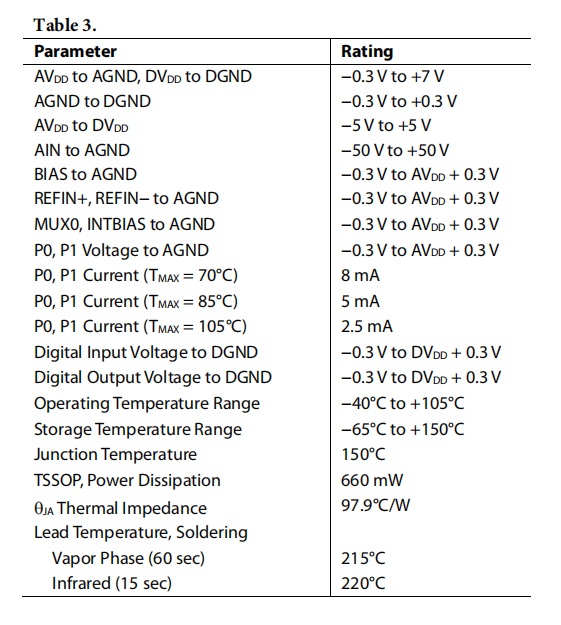

绝对最大额定值

TA=25°C,除非另有说明。

大于或等于绝对最大额定值的应力可能会对产品造成永久性损坏。这仅是一个应力等级;不暗示产品在本规范操作部分所述条件或以上任何其他条件下的功能运行。超过最大运行条件的长时间运行可能会影响产品的可靠性。

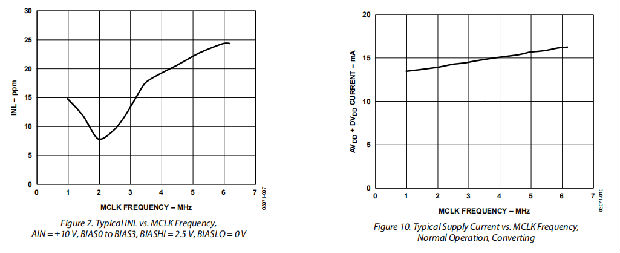

典型性能特征

输出噪声和分辨率规范

AD7734可以在启用或禁用斩波的情况下工作,允许对ADC进行编程以优化吞吐量速率和信道切换时间或优化偏移漂移性能。下面列出了这两种主要工作模式的噪声表,用于选择输出速率和稳定时间。

AD7734噪声性能取决于选定的斩波模式、滤波器字(FW)值和选定的模拟输入范围。AD7734噪声不会随MCLK频率而显著变化。

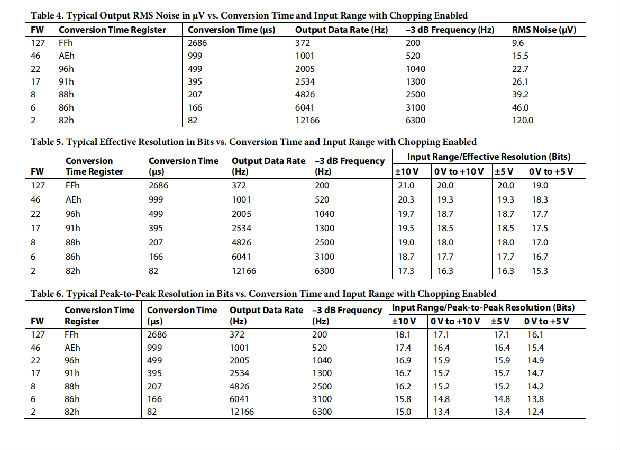

已启用斩波

第一种模式,其中AD7734配置为启用斩波(斩波=1),以较低的输出速率提供非常低的噪声。表4至表6分别显示了-3db频率和典型性能与信道转换时间和等效输出数据速率的关系。

表4显示了典型的输出均方根噪声。表5显示了基于均方根噪声的典型有效分辨率。表6显示了典型的输出峰间分辨率,表示在6∑限制内不会出现代码闪烁的值。峰间分辨率不是基于均方根噪声计算的,而是基于峰间噪声计算的。

这些典型数字是在模拟输入电压设置为0V和MCLK=6.144MHz的连续转换模式下采集的4096个数据样本产生的。通过信道转换时间寄存器选择转换时间。

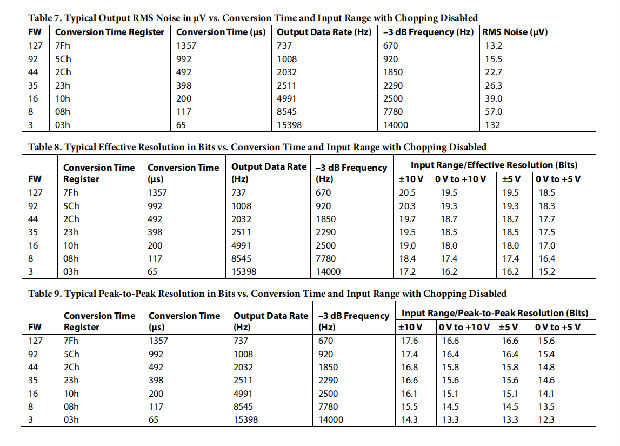

切断已禁用

第二种模式,其中AD7734配置有禁用斩波(斩波=0),提供更快的转换时间同时仍然保持高分辨率。表7至表9显示与信道相比,-3db频率和典型性能转换时间和等效输出数据速率。表7显示了典型的输出均方根噪声。表8显示了基于均方根噪声的典型有效分辨率。表9显示典型的输出峰间分辨率,表示在6∑限制内不会出现代码闪烁的值。这个峰间分辨率不是基于均方根噪声计算的但在峰到峰的噪音中。

这些典型数字是由4096个数据样本生成的用模拟输入在连续转换模式下获取电压设为0 V,MCLK=6.144 MHz。转换通过信道转换时间寄存器选择时间。

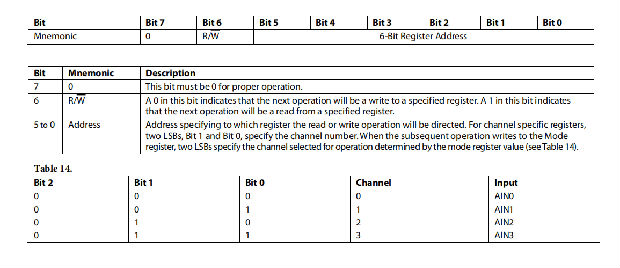

注册访问

AD7734可通过一系列寄存器进行配置。其中一些配置和控制一般的AD7734功能,而其他则针对每个通道。寄存器数据宽度从8位到24位不等。所有寄存器都是通过通信寄存器访问的,也就是说,与AD7734的任何通信都必须以对通信寄存器的写操作开始,指定随后将读取或写入哪个寄存器。

通信寄存器

8位,只写寄存器,地址00h

与设备的所有通信必须以对通信寄存器的写入操作开始。写入的数据通信寄存器确定随后的操作将是读或写操作,并将此操作定向到哪个寄存器。数字接口默认期望在通电后、复位后或对所选寄存器的后续读写操作完成后对通信寄存器进行写操作。如果接口序列丢失,则可以通过使用DIN高和CS低写入至少32个串行时钟周期来重置设备。(注意,在这种情况下,所有部分,包括调制器、滤波器、接口和所有寄存器都会复位。)在连续读取模式下或在模式寄存器组中使用转储位和“24/16”位读取32位或更多位时,请记住保持数据低。

I/O端口寄存器

8位,读/写寄存器,地址01h,默认值30h+数字输入值×40h

此寄存器中的位用于配置和访问AD7734上的数字I/O端口。

测试寄存器

24位,读/写寄存器,地址03h

此寄存器用于在制造过程中测试设备。用户不得更改此寄存器的默认配置。

ADC状态寄存器

8位,只读寄存器,地址04h,默认值00h

在转换模式中,寄存器位反映单个信道的状态。当转换完成时,相应的信道数据寄存器被更新,相应的RDY位被设置为1。

当信道数据寄存器被读取时,相应的位被重置为0。当没有发生读取操作并且下一次转换的结果被更新到信道数据寄存器时,该位也被重置为0。写入模式寄存器会将所有位重置为0。

在校准模式下,当校准进行时,所有寄存器位重置为0;校准完成时,所有寄存器位设置为1。

RDY引脚输出与由I/O端口寄存器中的RDYFN位定义的ADC状态寄存器的内容相关。RDY0位对应于通道0,RDY1位对应于通道1,依此类推。

校验和寄存器

16位,读/写寄存器,地址05h

该寄存器在AN-626应用说明e AD7732/AD7734/AD7738/AD7739 C中有说明。使用thhecksum寄存器。

ADC零刻度校准寄存器

24位,读/写寄存器,地址06h,默认值800000h

寄存器保存ADC零刻度校准系数。此寄存器中的值与ADC满标度校准寄存器中的值以及相应的信道零标度和信道满标度校准寄存器中的值一起使用,以数字方式缩放所有信道的转换结果。此寄存器中的值在执行ADC零刻度自校准后自动更新。只有在空闲模式下才能写入此寄存器(有关详细信息,请参阅校准部分)。

ADC满标度寄存器

24位,读/写寄存器,地址07h,默认值800000h此寄存器保存ADC满标度系数。建议用户不要更改此寄存器的默认配置。

信道数据寄存器

16位/24位,只读寄存器,地址08h–0Bh,默认宽度16位,默认值8000h

这些寄存器包含对应于每个模拟输入通道的最新转换结果。16位或24位数据宽度可以通过在模式寄存器中设置24/16位来配置。结果更新时,通道状态寄存器中的相关RDY位变高。一旦开始读取数据寄存器,RDY位将返回低位。RDY可以将pin配置为指示任何通道何时有未读数据,或等待所有启用的通道都有未读数据。如果在更新新结果时正在执行任何通道数据寄存器读取操作,则不会更新数据寄存器。这样可以避免数据损坏。读取状态寄存器可以与在转储模式下读取数据寄存器相关联。读取状态寄存器总是与在连续读取模式下读取数据寄存器相关联(有关详细信息,请参阅数字接口说明部分)。

通道零刻度校准寄存器

24位,读/写寄存器,地址10h–13h,默认值800000h

这些寄存器保存特定的信道零标度校准系数。这些寄存器中的值与相应信道满标度校准寄存器、ADC零标度校准寄存器和ADC满标度寄存器中的值一起使用,以数字方式缩放特定信道转换结果。此寄存器中的值在执行信道零刻度系统校准后自动更新。

信道零刻度校准寄存器的格式为符号位和22位无符号值。只有在空闲模式下才能写入此寄存器(有关详细信息,请参阅校准部分)。

通道满标度校准寄存器

24位,读/写寄存器,地址18h–1Bh,默认值200000h

这些寄存器保存特定的信道满标度校准系数。这些寄存器中的值与对应通道零点刻度校准寄存器、ADC零点刻度校准寄存器和ADC满刻度寄存器中的值,以数字方式缩放特定通道转换结果。此寄存器中的值在执行通道满标度系统校准后自动更新。只有在空闲模式下才能写入此寄存器(有关详细信息,请参阅校准部分)。

信道状态寄存器

8位,只读寄存器,地址20h–23h,默认值20h×通道号

这些寄存器包含单独的信道状态信息和一些一般的AD7734状态信息。读取状态寄存器可以与在转储模式下读取数据寄存器相关联。读取状态寄存器始终与在连续读取模式下读取数据寄存器相关联(有关更多详细信息,请参阅数字接口说明部分)。

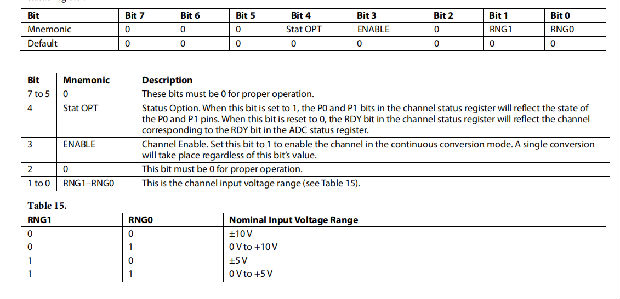

通道设置寄存器

8位,读/写寄存器,地址28h–2Bh,默认值00h

这些寄存器用于配置所选通道,配置其输入电压范围,并设置相应的通道状态寄存器。

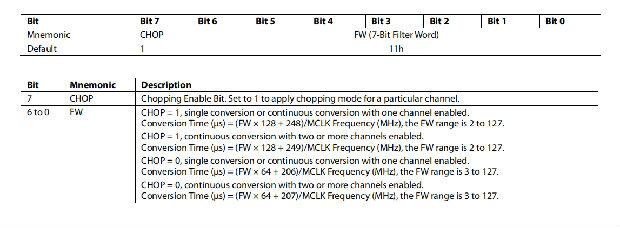

信道转换时间寄存器

8位,读/写寄存器,地址30h–33h,默认值91h

转换时间寄存器启用或禁用斩波,并为特定信道配置数字滤波器。此寄存器值影响ADC的转换时间、频率响应和噪声性能。

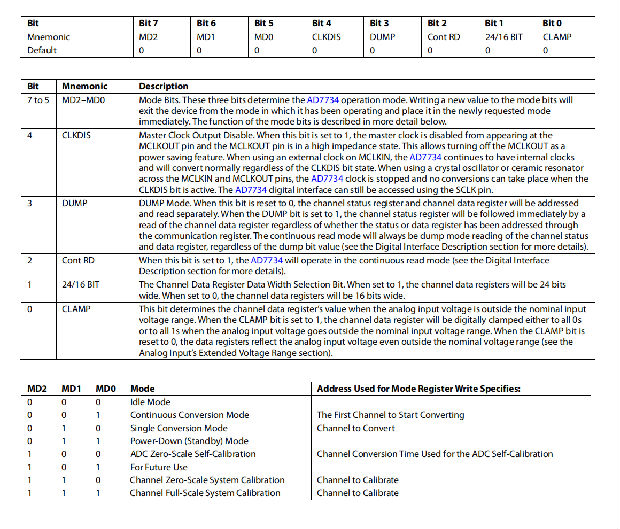

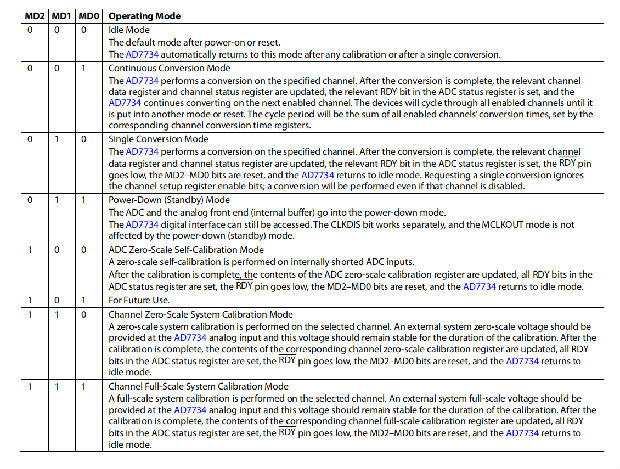

模式寄存器

8位,读/写寄存器,地址38h–3Bh,默认值00h

模式寄存器配置设备并确定其工作模式。写入模式寄存器将清除ADC状态寄存器,将RDY引脚设置为逻辑高电平,退出所有当前操作,并启动由模式位指定的模式。

AD7734只包含一个模式寄存器。地址的两个lsb用于写入模式寄存器,以指定为由MD2到MD0位确定的操作选择的通道。只能使用地址38h读取模式寄存器。

数字接口描述

硬件

AD7734串行接口可以连接到主机设备通过串行接口有几种不同的方式。CS引脚可用于选择AD7734作为以下几种之一连接到主机串行接口的电路。当CS高时,AD7734忽略SCLK和DIN信号以及DOUT引脚进入高阻抗状态。当CS信号不是使用时,将CS引脚连接到DGND。

RDY管脚可以被轮询为高到低转换或可以驱动主机设备中断输入以指示AD7734已完成选定的操作和/或新的AD7734的数据可用。主机系统也可以在将给定命令写入阅读前的设备。或者,AD7734状态可以是民意测验。当系统中没有使用RDY管脚时,它应该保持开路。(请注意,RDY pin始终是主动数字输出。它从不进入高阻抗状态。)复位引脚可用于复位AD7734。如果没有使用时,将此插针连接到DVD。

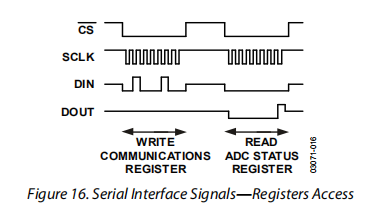

AD7734接口可以简化为两条线将DIN和DOUT引脚连接到单个双向数据线。此2线配置中的第二个信号是SCLK信号。主机系统应更改数据线参考AD7734正时技术规格的方向(见表2中的公共汽车放弃时间)。AD7734不能在2线串行接口中以连续读取模式运行配置。

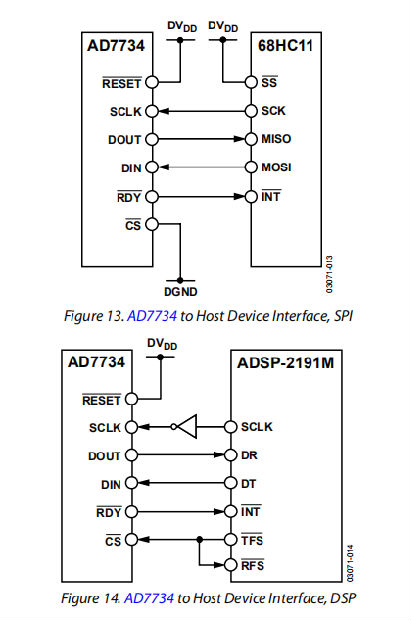

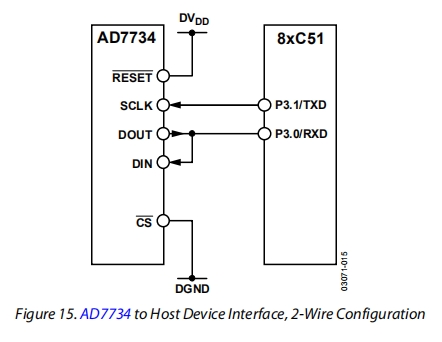

所有的数字接口输入都是施密特触发的;因此,AD7734接口具有更高的抗噪性和can通过光耦容易地与主机系统隔离。图13,图14和图15概述了一些可能的主机设备接口:不使用CS信号的SPI(图13),一个数字信号处理器接口(图14)和2线配置(图15)。

重置

AD7734可以通过复位引脚或通过向AD7734串行接口写入复位序列来复位。

复位序列为N×0+32×1,可以是面向字节接口中的数据序列00h+FFh+FFh+FFh+FFh+FFh。AD7734还具有通电复位功能,跳闸点为2V,通电后进入定义的默认状态。

系统设计人员有责任防止对AD7734进行不必要的写入操作。当SCLK上出现虚假时钟而CS引脚较低时,可能会发生不需要的写入操作。需要注意的是,在系统通电时,如果AD7734接口信号是浮动的或未定义的,则设备可能会无意中配置为未知状态。这可以通过在系统配置的第一步中启动硬件重置事件或32个1的重置序列来轻松克服。

访问AD7734寄存器

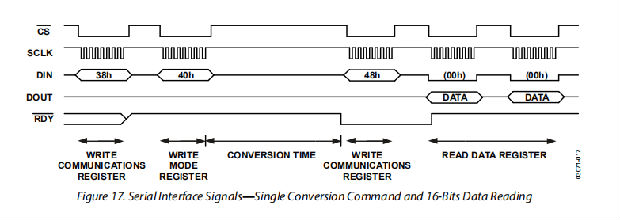

所有到设备的通信从对通信寄存器的写操作开始,然后读或写地址寄存器。

在同时读写接口(如SPI)中,读取数据时向AD7734写入0。

图16显示了ADC状态寄存器的AD7734接口读取序列。

单次转换和读取数据

写入模式寄存器时,ADC状态字节被清除,RDY引脚变高,而不管其先前的状态如何。当将单个转换命令写入模式寄存器时,ADC在由模式寄存器的地址选择的信道上启动转换。转换完成后,更新数据寄存器,将模式寄存器更改为空闲模式,设置相关的RDY位,并引脚变低。当读取相关通道数据寄存器时,RDY位被重置,RDY引脚返回高位。

图17显示数字接口信号在通道0上执行单个转换,等待RDY引脚变低,并读取通道0数据寄存器。

转储模式

当模式寄存器中的转储位设置为1时,信道状态寄存器将通过信道数据寄存器的读取立即被读取,而不管状态或数据寄存器是否已通过通信寄存器寻址。在转储模式下读取24位数据时,DIN引脚不应高;否则,AD7734将被重置。

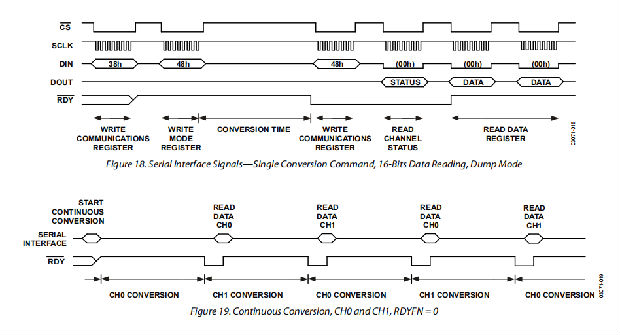

图18显示数字接口信号在通道0上执行单个转换,等待RDY引脚变低,并在转储模式下读取通道0状态寄存器和数据寄存器。

连续转换模式

写入模式寄存器时,ADC状态字节被清除,RDY引脚变高,而不管其先前的状态如何。当连续转换命令写入模式寄存器时,ADC在由模式寄存器的地址选择的信道上开始转换。

转换完成后,更新相关信道数据寄存器和信道状态寄存器,设置ADC状态寄存器中的相关RDY位,并且AD7734继续在下一个启用的信道上进行转换。设备将循环通过所有启用的通道,直到进入另一个模式或重置。周期周期将是所有启用信道的转换时间之和,由相应的信道转换时间寄存器设置。

当读取相关信道数据寄存器时,RDY位被重置。RDY管脚的行为取决于I/O端口寄存器中的RDYFN位。当RDYFN位为0时,当任何通道有未读数据时,RDY管脚变低。当RDYFN位设置为1时,只有当所有启用的通道都有未读数据时,RDY pin才会变低。

如果在新的ADC转换完成之前尚未读取ADC转换结果,则新结果将覆盖前一个结果。相关的RDY位变低,RDY管脚变高至少163 MCLK个周期(约26.5微秒),指示何时更新数据寄存器,以及先前的转换数据丢失。

如果在ADC转换完成时读取数据寄存器,则不会使用新结果更新数据寄存器(以避免数据损坏),并且新的转换数据将丢失。

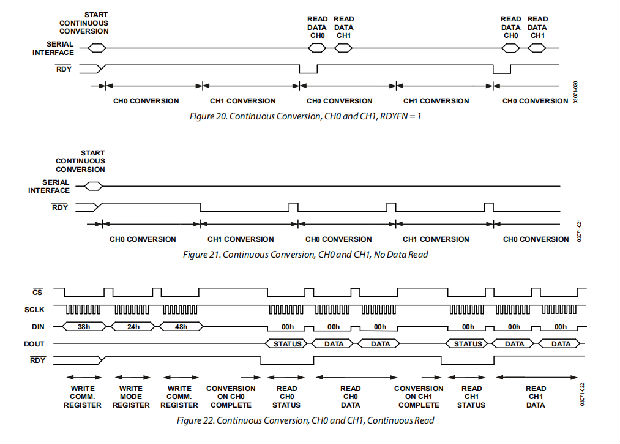

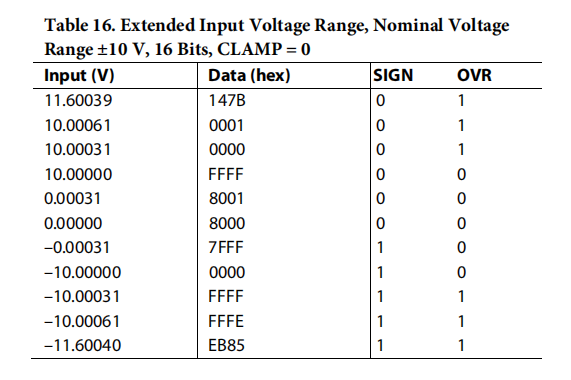

图19显示了数字接口信号在通道0和1启用且RDYFN位设置为0的连续转换模式下的序列。RDY引脚变低,每次转换后读取数据寄存器。图20显示了一个类似的序列,但RDYFN位设置为1。RDY引脚变低,在所有转换完成后读取所有数据寄存器。图21显示了没有从AD7734读取数据时的RDY管脚。

连续读取(连续转换)模式

当模式寄存器中的Cont RD位被设置时,对通信寄存器的第一次写入48h开始连续读取模式。如图22所示,对设备的后续访问顺序地读取最后完成的转换的信道状态和数据寄存器,而不需要对通信寄存器进行任何进一步的配置。

注意,在进入连续读取模式时,应设置模式寄存器中的连续转换位。

注意,连续读取模式是信道状态和数据寄存器的转储模式读取,与转储位值无关。使用通道状态寄存器中的通道位来检查/识别哪个通道数据实际上被移出。

请注意,正在读取最后完成的转换结果。因此,I/O端口寄存器中的RDYFN位应为0,并且在完成下一次转换之前,应始终开始读取结果。

只要当CS引脚低时,DIN引脚低;因此,在连续读取模式下读取时,向AD7734写入0。要退出连续读取模式,请在读取完成后将DIN pin高置至少100 ns。(向AD7734写入80h以退出连续读取。)

使DIN pin高不改变模式寄存器中的Cont RD位。因此,48h的下一次写入再次启动连续读取模式。要完全停止连续读取模式,请写入模式寄存器以清除Cont RD位。

电路说明

AD7734是一个∑-ΔADC,用于测量工业过程控制、仪表和PLC系统中的宽动态范围、低频信号。

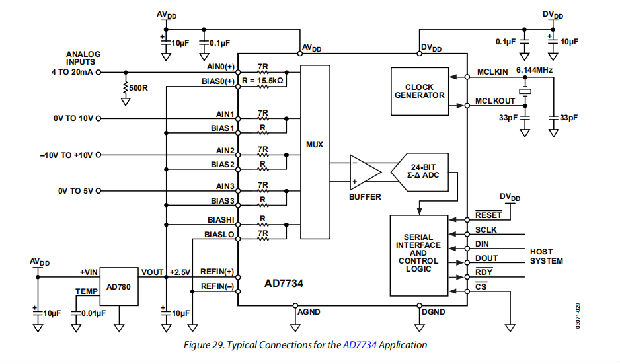

它包含薄膜电阻分压器、多路复用器、输入缓冲器、a∑-Δ(或电荷平衡)ADC、数字滤波器、时钟振荡器、数字I/O端口和串行通信接口。

模拟前端

AD7734具有四个单端模拟输入。onchip薄膜电阻分压器允许将±10 V、±5 V、0 V至+10 V和0 V至+5 V输入信号直接连接到模拟输入引脚。

电阻分压器输入级之后是多路复用器,然后是一个宽带、快速稳定的时间差分输入缓冲器,能够驱动高速∑-Δ调制器的动态负载。

在正常电路配置中,BIAS0至BIAS3和BIASHI引脚连接至2.5 V(参考)电压源,BIASLO引脚连接至0 V。这确保内部输入缓冲器所看到的差分信号在绝对/共模范围内(AGND+200 mV至AV–300 mV)。

AD7734 AIN电压应在规定的标称(高达±10 V)输入范围内,否则信道性能可能降低(请参阅模拟输入的扩展电压范围部分)。

如果偏置管脚处于正常配置,则高达±16.5 V的AIN管脚绝对电压不会降低相邻通道的性能。AIN绝对电压超过±16.5 V会导致电流流过位于薄膜电阻器后面的内部保护二极管,相邻通道可能会受到影响。

AIN引脚具有过电压容限。但是,绝对不能超过±50 V的最大AIN电压。

注意,信道状态寄存器中的OVR位是从转换结果数字生成的,表示∑-Δ调制器(标称)超量程。OVR位不表示超过AIN引脚绝对电压限制。

图23显示了AD7734模拟输入内部结构。

模拟量输入的扩展电压范围

AD7734输出数据代码范围对应于标称输入电压范围。ADC在标称输入电压范围外工作,但性能可能会降低。设计∑-Δ调制器的目的是完全覆盖±11.6v的模拟输入电压;在此范围之外,性能可能下降得更快。相邻通道不受高达±16.5 V模拟输入电压的影响(图8)。

当模式寄存器中的钳位设置为1时,当模拟输入电压超出标称输入电压范围时,信道数据寄存器将被数字钳位为全部0或全部1。

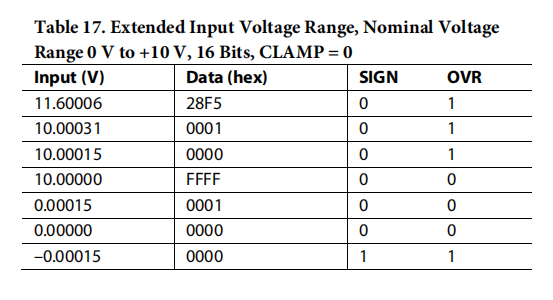

如表16和表17所示,当钳位=0时,数据反映的模拟输入电压超出标称电压范围。在这种情况下,应将信道状态寄存器中的符号和OVR位与数据寄存器值一起考虑,以解码实际转换结果。

注意,信道状态寄存器中的OVR位是从转换结果数字生成的,表示∑-Δ调制器(标称)超量程。OVR位不表示超过了AIN引脚的绝对电压限制。

切碎

在启用斩波的情况下,多路复用器反复反转ADC输入。然后,将每个输出数据结果计算为两个转换的平均值,第一个转换为正,第二个转换为负偏移项。这有效地消除了输入缓冲器和∑-Δ调制器的任何偏移误差。

然而,斩波仅应用于输入电阻分压级之后;因此,斩波不能消除由电阻引起的偏移误差和漂移。图24显示了启用斩波的信道信号链。

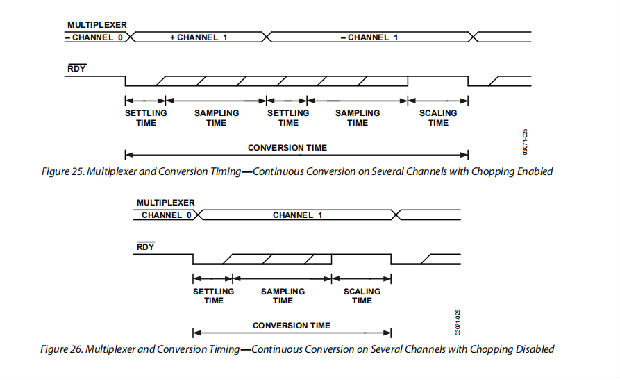

多路复用器、转换和数据输出定时

指定的转换时间包括一个或两个沉降和采样周期以及缩放时间。

在启用斩波的情况下(图25),转换周期以43 MCLK周期或44 MCLK周期(6.144 MHz MCLK约7微秒)的稳定时间开始,以允许跟随多路复用器的电路稳定。然后∑-Δ调制器对模拟信号进行采样,数字滤波器处理数字数据流。采样时间取决于FW,也就是说,取决于信道转换时间寄存器的内容。在另一个42 MCLK周期(约6.8微秒)的稳定之后,使用反向(斩波)模拟输入信号重复采样时间。然后,在163 MCLK周期(约26.5微秒)的缩放时间内,对来自数字滤波器的两个结果进行平均,使用校准寄存器缩放,并写入信道数据寄存器。

在禁用斩波的情况下(图26),只有一个采样时间,在此之前的稳定时间为43 MCLK个周期或44 MCLK个周期,随后的缩放时间为163 MCLK个周期。

多路复用器

RDY管脚在缩放时间内变高,而不管其以前的状态如何。相关的RDY位设置在ADC状态寄存器和通道状态寄存器中,并且当通道数据寄存器更新并且通道转换周期结束时,RDY引脚变低。如果处于连续转换模式,设备将在下一个启用的通道上自动继续转换循环。

注意,每个通道可以独立配置转换时间和斩波模式。整个周期和有效的每通道数据速率取决于所有启用的通道设置。

∑-ΔADC

AD7734核心由电荷平衡∑-Δ调制器和数字滤波器组成。该架构经过优化,可实现快速、完全固定的转换。这允许在保持固有的良好线性度、高分辨率和低噪声的同时进行快速的信道间切换。

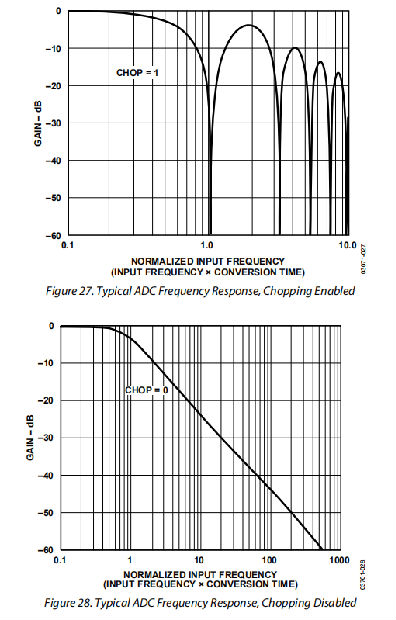

频率响应

Δ调制器的工作频率为MCLK频率的1/2,这实际上是采样频率。因此,奈奎斯特频率是MCLK频率的四分之一。数字滤波器与调制器一起具有一阶低通滤波器的频率响应。-3db点接近1/通道转换时间的频率。滚降为-20db/dec,直至奈奎斯特频率。如果启用斩波,则通过斩波对输入信号重新采样。因此,总体频率响应特征是接近频率1/信道转换时间。顶部的包络线同样是-20db/dec的ADC响应。

典型的频率响应曲线如图27和图28所示。曲线图被标准化为1/通道转换时间。

电压参考输入

AD7734有一个差分参考输入,REF IN(+)和参考输入(-)。这些输入的共模范围是从AGND到AV。指定操作的标称差动参考电压为2.5 V。两个参考输入均具有动态负载。因此,参考输入应连接到低阻抗参考电压源。外部电阻/电容组合可能会导致设备上的增益误差。

表4至表9中列出的输出噪声性能适用于0 V的模拟输入,且不受参考上噪声的影响。要在整个输入范围内获得与噪声表中所示相同的噪声性能,AD7734需要一个低噪声参考源。如果感兴趣带宽中的参考噪声过大,则会降低AD7734的性能。

AD7734的推荐参考电压源包括AD780、ADR421、REF43和REF192。注意,在典型连接中,如果向模拟输入端施加正电压,则电压基准必须能够通过内部电阻器吸收从偏压管脚流出的电流。AD780符合这一要求。如果应用中使用的电压基准不能吸收电流,则应将一个外部电阻器(5 kΩ)并联至REFIN引脚。

参考检测

AD7734包括芯片电路,用于检测设备是否具有用于转换的有效参考。如果REFIN(+)和REFIN(-)引脚之间的电压低于NOREF触发电压(典型值为0.5 V),并且AD7734正在执行转换,则设置信道状态寄存器中的NOREF位。

I/O端口

AD7734 P0引脚可用作通用数字输入/输出引脚。P1管脚(SYNC/P1)可以用作通用数字I/O管脚,或用于将AD7734与系统中的其他设备同步。当I/O端口寄存器中的同步位设置为同步引脚低,AD7734不处理任何转换。

如果处于单转换模式,则为连续转换模式,或任何校准模式,AD7734等待,直到同步引脚变高,然后开始操作。这允许转换从已知的时间点开始,即同步管脚。

数字P0和P1电压参考模拟电源。当配置为输入时,管脚应绑在高位或低位。

校准

AD7734提供了零标度自校准、零标度和满标度系统校准功能,可以有效地将偏移误差和增益误差降低到噪声的量级。每次转换后,在将ADC转换结果写入数据寄存器之前,使用ADC校准寄存器和相关信道校准寄存器对其进行缩放。

对于单极范围:

数据=((ADC结果–ADC ZS校准。注册号:

ADC FS注册/200000h–Ch.ZS校准。注册号:

Ch.FS校准。适用于双极范围的reg./200000h:

数据=((ADC结果–ADC ZS校准。注册号:

ADC FS注册/400000h+800000h–Ch.ZS校准。注册)

×Ch.FS校准。注册时间:200000小时

其中ADC结果在0到ffffff h的范围内。

注意,信道零刻度校准寄存器具有符号位和22位信道偏移值的格式。

强烈建议用户不要更改ADC满标度寄存器。

要开始任何校准,请将相关模式位写入AD7734模式寄存器。校准完成后,更新相应校准寄存器的内容,ADC状态寄存器中的所有RDY位都已设置,同步引脚变低,AD7734恢复到空闲模式。校准持续时间与所选通道上配置的转换时间相同。较长的转换时间会产生较少的噪声并产生更精确的校准;因此,至少使用默认的转换时间来启动任何校准。

ADC零标度自校准

ADC零标度自校准可以减少斩波禁用模式下的偏移误差。如果在一个温度后重复改变,它也可以减少偏置漂移误差在斩波禁用模式。

在内部短路的ADC输入上执行零刻度自校准。所选通道上的负模拟输入端子用于设置ADC零刻度校准共模。因此,应将所选差分对的负极端子或单端信道配置上的AINCOM驱动至适当的共模电压。

强烈建议ADC零标度校准寄存器仅作为零标度自校准的一部分进行更新。

每通道系统校准

如果使用每通道系统校准,应按以下顺序启动:通道零刻度系统校准,然后是通道满刻度系统校准。

系统校准受ADC零刻度和满刻度校准寄存器的影响。因此,如果系统中同时使用自校准和系统校准,则应首先执行ADC满标度自校准,然后执行系统校准循环。

在执行系统校准时,必须将完全固定的系统零标度电压信号或系统满标度电压信号连接到选定的通道模拟输入。

每个通道校准寄存器可以读取、存储或修改并写回AD7734。注意,当写入校准寄存器时,AD7734必须处于空闲模式。注意,在规定的校准范围之外,可以进行校准,但性能可能会降低(见表1中的系统校准参数)。

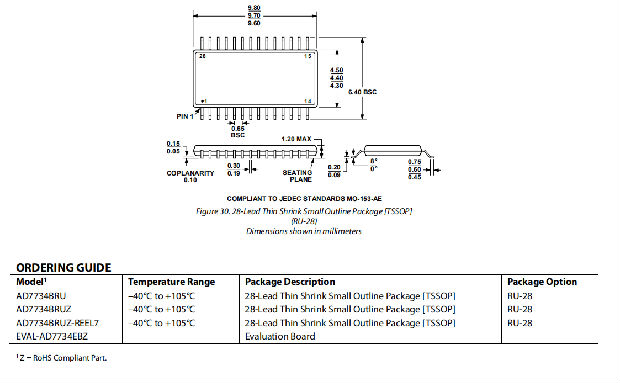

外形尺寸