AD9600点击型号即可查看芯片规格书

信号监测器

信号监视块提供关于ADC正在数字化的信号的附加信息。信号监视器计算rms输入幅度、峰值幅度和/或幅度超过特定阈值的采样数。同时,这些函数可用于深入了解信号特性,并估计输入信号的峰值/平均比甚至互补累积分布函数(CCDF)曲线的形状。该信息可用于驱动AGC环路,以在存在真实信号的情况下优化ADC的范围。

通过使用SPI端口或信号监视器SPORT输出将寄存器0x116读回寄存器0x11B,可以从部件获得信号监视器结果值。通过信号监视器控制寄存器(地址0x112)的两个信号监视器模式位来设置SPI可访问信号监视器寄存器的输出内容。两个ADC通道必须配置为相同的信号监视器模式。为每个ADC通道提供单独的SPI可访问的20位信号监视器结果(SMR)寄存器(地址0x116到地址0x11B)。信号监视器功能的任何组合也可以通过串行运动接口输出给用户。使用信号监视器运动控制寄存器(地址0x111)中的峰值检波器输出启用、有效值幅度输出启用和阈值交叉输出启用位启用这些输出。

对于每个信号监视器测量,可编程信号监视器周期寄存器(SMPR)控制测量的持续时间。该周期被编程为位于地址0x113、地址0x114和地址0x115的24位信号监视器周期寄存器中的输入时钟周期数。该寄存器可编程为128个样本到1678(200)万个样本。

由于a dc的dc偏移量可以显著大于感兴趣的信号(影响来自信号监视器的结果),因此在测量功率之前,作为信号监视器块的一部分包括dc校正电路以使dc偏移量为零。

峰值检波器模式

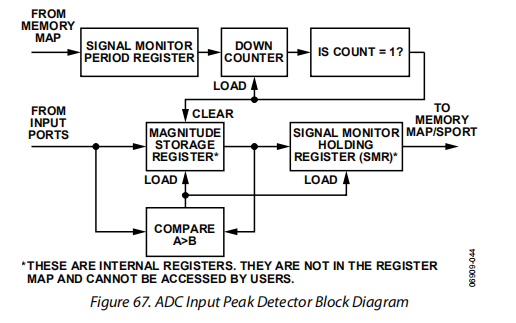

输入端口信号的幅度在可编程周期(由SMPR确定)内被监视,以给出检测到的峰值。通过在信号监视器控制寄存器(地址0x112)的信号监视器模式位中编程逻辑1或在信号监视器运动控制寄存器(地址0x111)中设置峰值检测器输出启用位来启用此功能。激活此模式前,必须对24位SMPR进行编程。

启用此模式后,SMPR中的值将加载到监视器周期计时器中,并开始倒计时。将输入信号的幅度与内部峰值电平保持寄存器中的值(用户不可访问)进行比较,并且将两个值中的较大者更新为当前峰值电平。将峰值保持寄存器中的初始值设置为当前ADC输入信号量,并且继续进行比较,直到监视周期计时器达到计数1。

当监视器周期计时器达到计数1时,峰值电平保持寄存器中的13位值被传输到信号监视器保持寄存器(用户无法访问),并且可以通过SPI端口读取或通过运动串行接口输出。用SMPR中的值重新加载监视器周期计时器,并重新启动倒计时。此外,峰值保持寄存器中的值被重置为第一输入样本的大小,并且先前解释的比较和更新过程继续。

图67是峰值检测器逻辑的框图。SMR寄存器包含由峰值检测器逻辑检测到的峰值的绝对幅度。

RMS/MS幅度模式

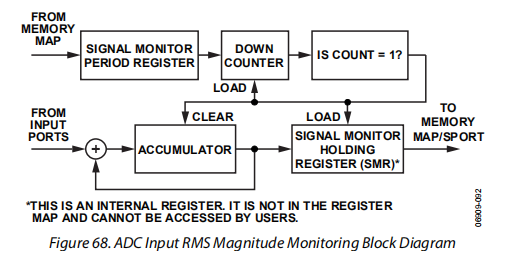

在此模式下,输入端口信号的均方根(rms)或均方根(ms)幅度在可编程周期(由SMPR确定)内积分(通过添加累加器)以给出输入信号的均方根或ms幅度。此模式通过在信号监视器控制寄存器(地址0x112)的信号监视器模式位中编程逻辑0或通过在信号监视器运动控制寄存器(地址0x111)中设置rms幅度输出启用位来设置。在激活此模式之前,必须对表示执行集成的周期的24位SMPR进行编程。

启用rms/ms幅度模式后,将SMPR中的值加载到监视器周期计时器中,并立即开始倒计时。每个输入样本都被转换为浮点格式和平方。然后将其转换为11位定点格式并添加到24位累加器的内容中。集成将继续,直到监视器周期计时器达到计数1。

当监视器周期计时器达到计数1时,累加器中的值的平方根被获取并传输(经过一些格式化后)到信号监视器保持寄存器,该寄存器可以通过SPI端口读取或通过SPORT串行端口输出。用SMPR中的值重新加载监视器周期计时器,并重新启动倒计时。此外,累加器的值被重置为第一输入样本信号功率,并且累加器继续与随后的输入样本一起进行。

图68说明了均方根值监测逻辑。

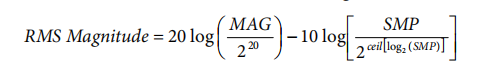

对于有效值幅度模式,信号监视器结果(SMR)寄存器中的值是20位定点数。以下公式可用于根据寄存器中的MAG值确定以分贝满标度(dBFS)为单位的rms值:

其中,如果信号监视周期(SMP)是2的幂,则方程中的第二项变为0。

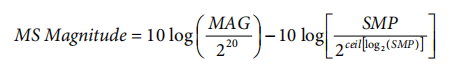

对于ms-magnitude模式,SMR中的值是20位固定点编号。以下公式可用于根据寄存器中的MAG值确定ms幅度(分贝满标度(dBFS)):

其中,如果SMP是2的幂,则方程中的第二项变为0。

越限模式

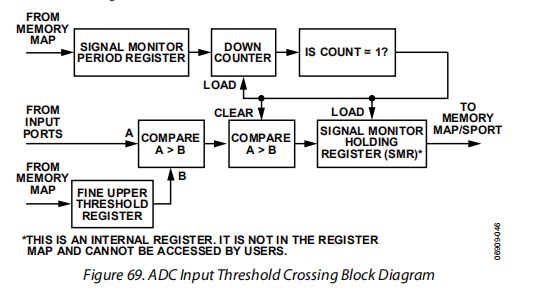

在阈值交叉操作模式中,输入端口信号的幅度在可编程时段(由SMPR确定)内被监视,以计数其穿过某个可编程阈值的次数。此模式通过在信号监视器控制寄存器(地址0x112)的信号监视器模式位中编程逻辑1x(其中x是不关心的位)或通过在信号监视器运动控制寄存器(地址0x111)中设置阈值交叉输出启用位来设置。在激活此模式之前,用户需要为每个单独的输入端口编程24位信号监视器周期寄存器(地址0x113到地址0x115)和13位精细上阈值寄存器(地址0x106和地址0x107)。同样的高阈值寄存器用于信号监测和增益控制(见ADC超量程和增益控制部分)。

进入此模式后,将SMPR中的值加载到监视器周期计时器中并开始倒计时。在每个输入时钟周期上,将输入信号的幅度与先前编程的精细阈值上限寄存器进行比较。如果输入信号的幅度大于精细上限阈值寄存器中设置的值,则内部计数寄存器中的值(用户不可访问)递增1。

内部计数寄存器的初始值设置为0。此值的比较和递增将继续,直到监视周期计时器达到计数1为止。

当监视器周期计时器达到计数1时,内部计数寄存器中的值被传输到信号监视器保持寄存器(用户不可访问),该寄存器可通过SPI端口读取或通过运动串行端口输出。

用SMPR中的值重新加载监视器周期计时器,并重新启动倒计时。内部计数寄存器也被清除为值0。图69说明了阈值交叉逻辑。SMR寄存器中的值是大于精细上限阈值寄存器的采样数。

附加控制位

为了在信号监视过程中增加灵活性,在信号监视控制寄存器(地址0x112)中提供了两个控制位。它们是信号监测使能位和复功率计算模式使能位。

信号监视器启用位

位于寄存器0x112的位0中的信号监视器启用位启用信号监视器块的操作。如果在特定应用中不需要信号监视器功能,则应清除此位(默认)以节省电源。

复功率计算模式使能位

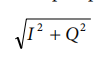

设置此位时,部件假设通道A正在数字化I数据,通道B正在数字化复杂输入信号的Q数据(或反之亦然)。在此模式下,报告的功率等于

如果信号监视器模式位设置为00,则该结果显示在信号监视器直流值通道A寄存器(地址0x10D和地址0x10E)中。信号监视器DC值信道B寄存器(地址0x10F和地址0x110)继续计算信道B值。

直流校正

由于a dc的dc偏移量可以明显大于被测量的信号,因此在测量功率之前包括dc校正电路以使dc偏移量为零。直流校正电路也可以切换到主信号路径,但如果a dc正在数字化具有显著直流内容的时变信号(例如GSM),则这可能不合适。

直流校正带宽

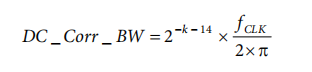

直流校正电路是一个高通滤波器,具有可编程带宽(在125毫秒/秒时范围在0.15赫兹和1.2千赫之间)。通过写入位于寄存器0x10C的4位dc校正带宽寄存器,位[5:2]来控制带宽。

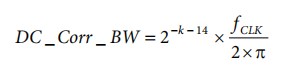

以下公式可用于计算直流校正电路的带宽值:

其中:k是在寄存器0x10C中编程的4位值,位[5:2](0到13之间的值对k有效;编程14或15提供与编程13相同的结果)。

fCLK是以赫兹为单位的AD9600 ADC采样率。

直流校正回读

当前的直流校正值可以在寄存器0x10D和寄存器0x10E(通道A)和寄存器0x10F以及寄存器0x110(通道B)中读取。直流校正值是一个10位值,可以跨越ADC的整个输入范围。

直流校正冻结

设置dc校正冻结位(寄存器0x10C的位6)使dc校正停止在其当前状态,并继续使用最后更新的值作为dc校正值。清除此位将重新启动dc校正并将当前计算值添加到数据中。

直流校正启用位

寄存器0x10C的设置位0(SM使能位的dc校正)启用dc校正以用于信号监视器计算。寄存器0x10C的设置位1(信号路径启用位的直流校正)使得计算出的直流校正值被添加到输出数据信号路径。

运动输出信号监视器

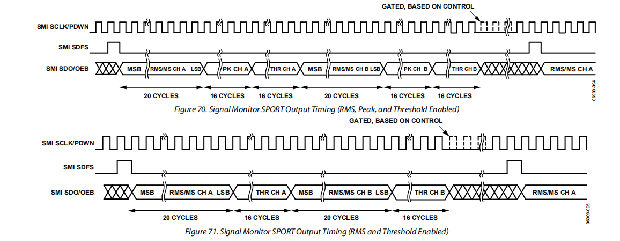

SPORT是一个带有三个输出引脚的串行接口:SMI SCLK(运动时钟)、SMI SDF(运动帧同步)和SMI SDO(运动数据)。运动是主控,驱动芯片上的所有三个运动输出引脚。

SMI症状自评量表

数据和帧同步在SMI SCLK的正边缘上驱动。SMI SCLK有三种可能的波特率:1/2、1/4或1/8 ADC时钟率,基于运动控制。此外,通过使用SPORT SMI SCLK sleep位,当信号监视器块不发送任何数据时,SMI SCLK可以被选通以保持低电平。当不需要SMI SCLK时,使用此位禁用它可以减少返回信号路径中的耦合错误。然而,这样做的缺点是分散时钟的频率内容;如果需要,可以使SMI SCLK保持启用状态以简化频率规划。

SMI SDF

SMI SDFS是串行数据帧同步。它定义了帧的开始。一个运动帧包含来自两个数据路径的数据。数据路径A中的数据在帧同步之后发送,然后是数据路径B中的数据。

SMI SDO

SMI SDO是块的串行数据输出。数据被发送MSB在SMI SDFS之后的第一个正边上。每个数据输出块包括一个或多个均方根值,峰值电平中每个数据路径的值和阈值交叉值命令。如果启用,则发送数据,首先是rms,然后是峰值值和阈值交叉值,如图70所示。

内建自测试(BIST)和输出测试

AD9600包括内置的测试功能,可以验证每个通道的完整性,并便于板级调试。包括一个BIST特性,用于验证AD9600的数字数据路径的完整性。还提供了各种输出测试选项,以便在AD9600的输出上放置可预测的值。

内置自检(BIST)

BIST是对所选AD9600信号路径的数字部分的彻底测试。启用时,测试从内部伪随机噪声(PN)源通过数字数据路径运行,从ADC块输出开始。BIST序列运行512个周期,然后停止。通道A或通道B的BIST签名值放在寄存器0x24和寄存器0x25中。如果选择一个通道,其BIST签名将写入两个寄存器。如果选择了两个通道,则两个通道的结果将被异或并放入BIST签名寄存器中。

在测试过程中,输出没有断开;因此,可以在运行时观察到PN序列。PN序列可以根据寄存器0x0E第2位中编程的值,从其最后一个值继续或从头开始。BIST签名结果根据信道配置而变化。

输出测试模式

输出测试选项如表22所示。当输出测试模式被启用时,ADC的模拟部分与数字后端块断开连接,测试模式通过输出格式化块运行。有些测试模式受输出格式的约束,有些则不受输出格式的约束。PN序列测试的种子值可以通过设置测试模式寄存器(地址0x0D)的位4或位5来强制使生成器保持在重置模式。这些测试可以在有或没有模拟信号的情况下进行(如果存在,则忽略模拟信号),但它们确实需要一个编码时钟。有关更多信息,请参阅AN-877应用说明,通过SPI与高速ADC接口。

通道/芯片同步

AD9600有一个同步输入,它为用户提供了灵活的同步选项来同步内部块。时钟分频器同步特性有助于保证多个adc之间的同步采样时钟。也可以使用SYNC输入来同步信号监视器块,从而允许在特定时间段内测量输入信号的特性。输入时钟分配器可以在同步信号的一次出现或每次出现时同步。信号监视器块在每个同步输入信号上同步。

同步输入在内部与样本时钟同步;但是,为了确保多个部分之间没有定时不确定性,同步输入信号应在外部与输入时钟信号同步,满足表5所示的设置和保持时间。同步输入应使用单端CMOS型信号驱动。

串行端口接口(SPI)

AD9600SPI允许用户通过ADC内部提供的结构化寄存器空间为特定功能或操作配置转换器。这可以根据应用程序为用户提供额外的灵活性和自定义。地址通过串行端口访问,可以通过端口写入或读取。内存被组织成字节,可以进一步划分为字段,这些字段记录在内存映射部分。有关详细的操作信息,请参阅AN-877应用说明,通过SPI连接到高速ADC。

使用SPI的配置

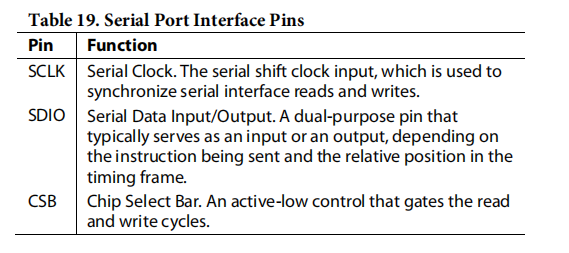

定义SPI的管脚有三个:SCLK、SDIO和CSB(见表19)。SCLK引脚用于同步ADC之间的读写数据。SDIO引脚是一个双用途引脚,允许数据发送到内部ADC内存映射寄存器并从中读取。CSB pin是一个activelow控件,用于启用或禁用读写循环。

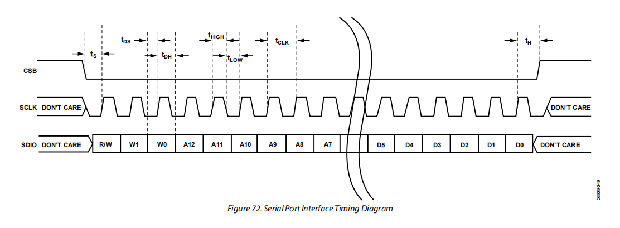

CSB的下降沿和SCLK的上升沿共同决定了帧的开始。串行定时及其定义的示例可以在图72和表5中找到。

其他涉及CSB的模式也可用。CSB可以无限期地保持低位,这将永久启用设备;这称为流式传输。CSB可以在字节之间高挂起,以允许额外的外部计时。当CSB连接到高电平时,SPI功能被置于高阻抗模式。此模式打开SPI管脚的任何辅助功能。

在指令阶段,发送16位指令。数据遵循指令阶段,其长度由W0和W1位确定。W0和W1表示要为读或写传输的数据字节数。W1:W0+1表示的值是要传输的字节数。

所有数据都由8位字组成。多字节串行数据传输帧中第一个字节的第一位指示是发出读取命令还是写入命令。这允许串行数据输入/输出(SDIO)管脚将输入方向更改为输出方向。

除了字长之外,指令阶段还确定串行帧是读还是写操作,从而允许串行端口用于对芯片进行编程和读取片上存储器的内容。如果指令是回读操作,则执行回读会导致SDIO引脚在串行帧中的适当点从输入改变到输出。

数据可以以MSB first模式或LSB first模式发送。MSB first mode是开机时的默认模式,可以通过SPI端口配置寄存器(地址0x00)进行更改。有关此功能和其他功能的更多信息,请参阅AN-877应用说明,通过SPI连接到高速ADC。

硬件接口

表19中描述的管脚构成用户编程设备和AD9600串行端口之间的物理接口。使用SPI接口时,SCLK引脚和CSB引脚用作输入。SDIO管脚是双向的,在写入阶段作为输入,在回读期间作为输出。

SPI接口足够灵活,可以由FPGAs或微控制器控制。一种SPI配置方法在AN-812应用说明,基于微控制器的串行端口接口(SPI)引导电路中详细描述。

SPI端口不应在需要转换器完全动态性能的期间处于活动状态。由于SCLK、CSB和SDIO信号通常与ADC时钟异步,这些信号的噪声会降低转换器性能。如果车载SPI总线用于其他设备,则可能需要在该总线和AD9600之间提供缓冲区,以防止这些信号在关键采样期间在转换器输入处转换。

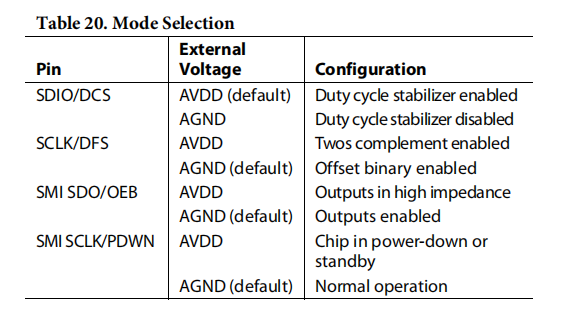

当不使用SPI接口时,有些管脚具有双重功能。当在设备通电期间将插脚绑在AVDD或接地上时,它们与特定功能相关。操作理论部分描述了AD9600支持的可捆绑功能。

不带SPI的配置

在不与SPI控制寄存器接口的应用程序中,SDIO/DCS管脚、SCLK/DFS管脚、SMI SDO/OEB管脚和SMI SCLK/PDWN管脚用作独立的CMOScompatible控制管脚。当设备通电时,假设用户打算将管脚用作占空比稳定器、输出数据格式、输出启用和断电特性控制的静态控制线。在此模式下,CSB芯片选择应连接到AVDD,这将禁用串行端口接口。

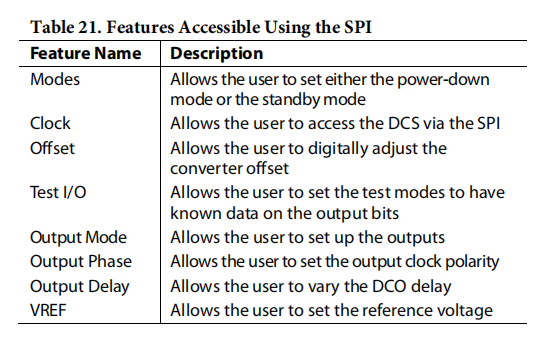

SPI可访问功能

表21简要说明了许多模拟设备(包括高速ADC,包括AD9600)上可用的、可通过SPI访问的一般特性。这些特性在AN-877应用说明中详细描述,通过SPI与高速adc接口。在存储器映射寄存器描述中描述了AD9600部件的特定功能章节。

内存映射

读取内存映射表

内存映射寄存器表(表22)中的每一行有八个位位置。内存映射分为四个部分:芯片配置寄存器(地址0x00到地址0x02)、通道索引和传输寄存器(地址0x05和地址0xFF)、ADC功能寄存器(地址0x08到地址0x25)和数字特性控制寄存器(地址0x100到地址0x11B)。

内存映射的最左边的列表示寄存器地址号,默认值显示在最右边的第二列中。(MSB)位7列是给定的默认十六进制值的开头。例如,地址0x18(VREF选择寄存器)的默认值为0xC0,这意味着位7=1,位6=1,其余位为0。此设置是默认的参考选择设置。默认值使用2.0 V峰间参考电压。有关此功能和其他功能的更多信息,请参阅AN-877应用说明,通过SPI连接到高速ADC。本应用说明详细说明了由寄存器0x00控制到寄存器0xFF的功能。其余寄存器(从寄存器0x100到寄存器0x11B)记录在内存映射寄存器描述部分。

开放位置

此设备当前不支持表22中未包含的所有地址和位位置。有效地址位置的未使用位应使用0写入。仅当地址位置的一部分打开时(例如,地址0x18)才需要写入这些位置。如果整个地址位置处于打开状态(例如,地址0x13),则不应写入此地址位置。

默认值

当AD9600从复位中出来时,关键寄存器将加载默认值。寄存器的默认值在内存映射寄存器表(表22)中给出。

逻辑电平

逻辑级术语解释如下:

•“Bit is set”与“Bit is set to Logic 1”同义,或“正在为位编写逻辑1。”

•“Clear a bit”与“bit is set to Logic 0”同义,或“正在为位写入逻辑0。”

转移寄存器映射

地址0x08到地址0x18被隐藏。写入这些地址不会影响部分操作,直到通过将0x01写入地址0xFF并设置传输位发出传输命令。这允许在设置传输位(寄存器0xFF的位0)时在内部和同时更新这些寄存器。内部更新在设置传输位和位自动清除时发生。

通道专用寄存器

一些通道设置功能,如信号监视器阈值,可以为每个通道单独编程。在这些情况下,通道地址位置在每个通道的内部重复。这些寄存器在表22中被指定为本地寄存器,并且可以通过在寄存器0x05中设置适当的通道A或通道B位来访问。如果两个位都已设置,则后续写入会影响两个通道的寄存器。在读取周期中,只有通道a或通道B应设置为读取两个寄存器中的一个。如果两个位都在SPI读取周期中设置,则部件返回通道A的值。

另一方面,表22中被指定为全局寄存器的寄存器影响通道之间不允许独立设置的整个部分或通道特性。寄存器0x05中的设置不影响全局寄存器。

内存映射

此设备当前不支持表22中未包含的所有地址和位位置。

内存映射寄存器描述

有关寄存器0x00控制到寄存器0xFF的功能的信息,请参阅应用说明AN-877,通过SPI与高速ADC接口。

同步控制(寄存器0x100)

位7-信号监视器同步启用

位7启用从外部同步输入到信号监视器块的同步脉冲。当第7位和第0位都高时,同步信号通过。这是连续同步模式。

位[6:3]-保留

位2时钟除法器,仅限下次同步

如果主同步启用位(地址0x100[0])高且时钟分割器同步启用位(地址0x100[1])高,则时钟分割器下一个仅同步位(地址0x100[2])允许时钟分割器同步到其接收的第一个同步脉冲,而忽略其余的同步脉冲。时钟分配器同步启用位(地址0x100[1])在同步后重置。

位1时钟分配器同步启用

位1将同步脉冲选通至时钟分配器。当位1和位0都高时,同步信号被传递。这是连续同步模式。

位0主同步启用

位0必须高才能启用同步功能。

快速检测控制(寄存器0x104)位[7:4]-保留

Bits[3:1]-快速检测模式选择

这些位根据表14设置快速检测输出管脚的模式。

位0-快速检测启用

位0用于启用快速检测输出管脚。当快速检测输出引脚被禁用时,输出进入高阻抗状态。在LVDS模式下,当快速检测输出管脚交错时,只有当两个通道都关闭(断电/待机/输出禁用)时,输出才会变为高Z。如果只有一个通道被关闭(断电/待机/输出被禁用),快速检测输出引脚会重复激活通道的数据。

粗上限阈值(寄存器0x105)

位[7:3]-保留

位[2:0]-粗阈值上限

这些位设置了断言粗阈值上限指示所需的级别(见表18)。

精细上限阈值(寄存器0x106和寄存器0x107)

寄存器0x106,位[7:0]-精细上阈值[7:0]

寄存器0x107,位[7:5]-保留

寄存器0x107,位[4:0]-精细上阈值[12:8]

这些寄存器提供精细的上限阈值。该13位值与来自ADC块的10位幅度相比较。如果ADC幅度超过此阈值,则设置输出指示器。

精细下限阈值(寄存器0x108和寄存器0x109)

寄存器0x108,位[7:0]-精细下限阈值[7:0]

寄存器0x109,位[7:5]-保留

寄存器0x109,位[4:0]-精细下限阈值[12:8]

这些寄存器提供了一个很好的下限阈值。该13位值与来自ADC块的10位幅度相比较。如果ADC幅度小于此阈值,则设置F_LT指示器。

增加增益保持时间(寄存器0x10A和寄存器0x10B)

寄存器0x10A,位[7:0]-增加增益保持时间[7:0]

寄存器0x10B,位[7:0]-增加增益保持时间[15:8]

这些寄存器用ADC时钟周期中的驻留时间进行编程。在确认增益增加(IG)指示灯之前,信号必须低于精细下限阈值。

信号监视器直流校正控制(寄存器0x10C)

位7—保留

位6-DC校正冻结

当位6被设置为高时,dc校正不更新到信号监视器块;因此,块继续保持其计算的最后dc值。

位[5:2]-直流校正带宽

这些位设置功率监视器直流校正功能的平均时间。该4位字根据以下等式设置校正块的带宽:

其中:k是在寄存器0x10C中编程的4位值,位[5:2](0到13之间的值对k有效;编程14或15提供与编程13相同的结果)。

fCLK是以赫兹为单位的AD9600 ADC采样率。

位1—信号通路启用的直流校正

将位1设置为高将使直流测量块的输出与信号路径中的数据相加,以从信号路径中消除直流偏移。

用于信号监视器启用的位0-DC校正

位0启用信号监视器块中的直流校正功能。直流校正是一种平均功能,信号监视器可以使用它来消除信号中的直流偏移。从测量中移除此直流电可以获得更精确的读数。

信号监测器直流值通道A(寄存器0x10D和寄存器0x10E)

寄存器0x10D,位[7:0]-直流值通道A[7:0]

寄存器0x10E,位[7:6]-保留

寄存器0x10E,位[5:0]-直流值通道A[13:8]

这些只读寄存器保存由信道A的信号监视器计算的最新dc偏移值。

信号监视器直流值通道B(寄存器0x10F和寄存器0x110)

寄存器0x10F位[7:0]-直流值通道B[7:0]

寄存器0x110位[7:6]-保留

寄存器0x110位[5:0]-直流值通道B[13:8]

这些只读寄存器保存由信道B的信号监视器计算的最新dc偏移值。

信号监视器运动控制(寄存器0x111)位7-保留

位6-RMS/MS幅度输出启用

这些位使20位rms或ms量级测量成为运动上的输出。

位5峰值检波器输出启用

位5启用10位峰值测量作为运动上的输出。

位4-阈值交叉输出启用

位4启用10位阈值测量作为运动上的输出。

位[3:2]-运动SMI SCLK除法

这些位的值设置运动SMI SCLK与输入时钟的除法比。值0x01集合除以2(默认值),值0x10集合除以4,值0x11集合除以8。

位1-运动SMI SCLK睡眠

当信号监视器块没有要传输的数据时,设置位1高将导致SMI SCLK保持低。

位0-信号监视器运动输出启用

设置后,位0使信号监视器的运动输出开始从信号监视器块移出结果数据。

信号监视器控制(寄存器0x112)

第7位-复杂功率计算模式启用

该模式假设I数据出现在一个通道上,Q数据出现在另一个通道上。报告的结果是复合功率,测量如下:

位[6:4]-保留

位3信号监视器RMS/MS选择

设置位3低选择均方根功率测量模式。设置位3高选择ms功率测量模式。

位[2:1]-信号监视模式

位2和位1将寄存器0x116的数据输出的信号监视器模式设置为寄存器0x11B。将位2和位1设置为00选择rms/ms幅度输出,将这些位设置为01选择峰值功率输出,将位1设置为10或11选择阈值交叉输出。

位0-信号监视器启用

设置位0高启用信号监视器块。

信号监视周期(寄存器0x113到寄存器0x115)寄存器0x113,位[7:0]-信号监视周期[7:0]

寄存器0x114,位[7:0]-信号监视周期[15:8]

寄存器0x115,位[7:0]-信号监视周期[23:16]

此24位值设置信号监视器执行其操作的时钟周期数。尽管该寄存器默认为64(0x40),但该寄存器的最小值为128(0x80)个周期,写入小于128的值可能导致结果不准确。

信号监视器结果通道A(寄存器0x116到寄存器0x118)

寄存器0x116,位[7:0]-信号监视器结果通道A[7:0]

寄存器0x117,位[7:0]-信号监视器结果

通道A[15:8]

寄存器0x118,位[7:4]-保留

寄存器0x118,位[3:0]-信号监视器结果

通道A[19:16]

此20位值包含通道A的信号监视块计算的结果。内容取决于寄存器0x112的位[2:1]中的设置。

信号监视器结果通道B(寄存器0x119到寄存器0x11B)

寄存器0x119,位[7:0]-信号监视器结果通道B[7:0]

寄存器0x11A,位[7:0]-信号监视器结果

通道B[15:8]

寄存器0x11B,位[7:4]-保留

寄存器0x11B,位[3:0]-信号监视器结果

通道B[19:16]

此20位值包含由信道B的信号监视块计算的结果。内容取决于寄存器0x112的位[2:1]中的设置。

应用程序信息

设计指南

在将AD9600设计成系统时,设计者应在开始设计和布局之前熟悉这些指南,其中讨论了特定管脚的特殊电路连接和布局要求。

电源和接地建议

将电源连接到AD9600时,设计人员应使用两个单独的1.8V电源:一个用于AVDD和DVD,另一个用于DRVDD。AVDD和DVDD电源虽然来源相同,但应使用铁氧体磁珠或滤波器扼流圈隔离,并具有单独的去耦电容器。用户可以使用多个不同的去耦电容器来覆盖高频和低频。这些应位于靠近PC板级入口点的位置,并靠近具有最小轨迹长度的零件管脚。

使用AD9600时,单块PC板接地平面应足够。通过对PC板的模拟、数字和时钟部分进行适当的解耦和智能分区,可以轻松实现最佳性能。

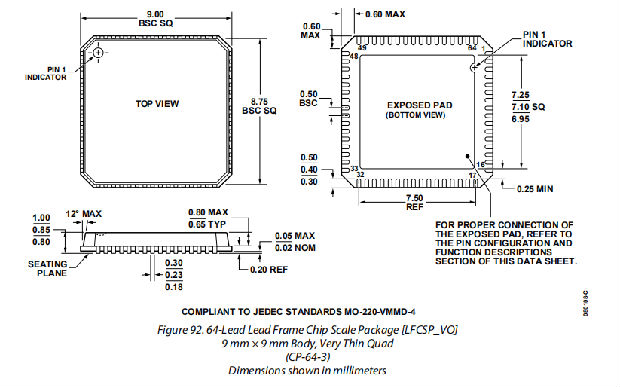

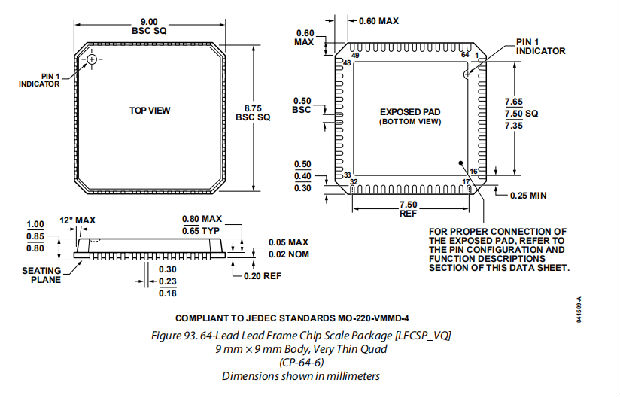

暴露桨叶热段塞建议

为了达到AD9600的最佳电性能和热性能,ADC底部的外露挡板必须连接到模拟接地(AGND)。印刷电路板上一个连续暴露(无焊料屏蔽)的铜平面应与AD9600的暴露叶片引脚0匹配。此外,铜平面应具有多个通孔,以实现最低可能的电阻热路径,以便散热流过PCB底部,这些通孔应填充或塞入非导电环氧树脂。

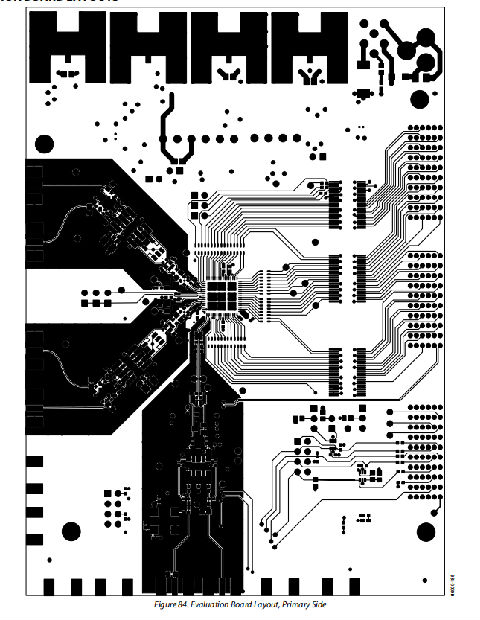

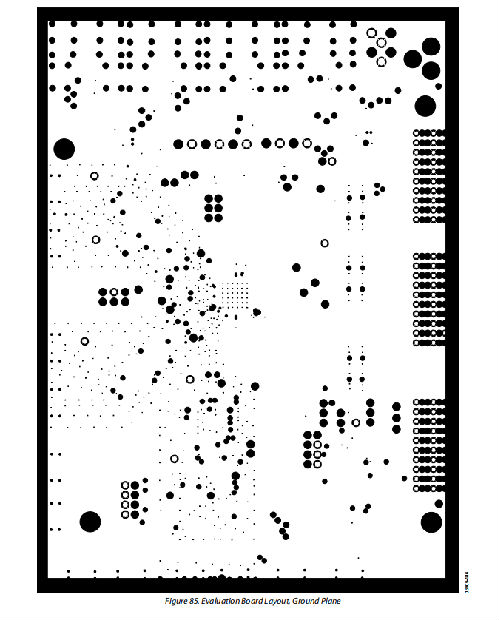

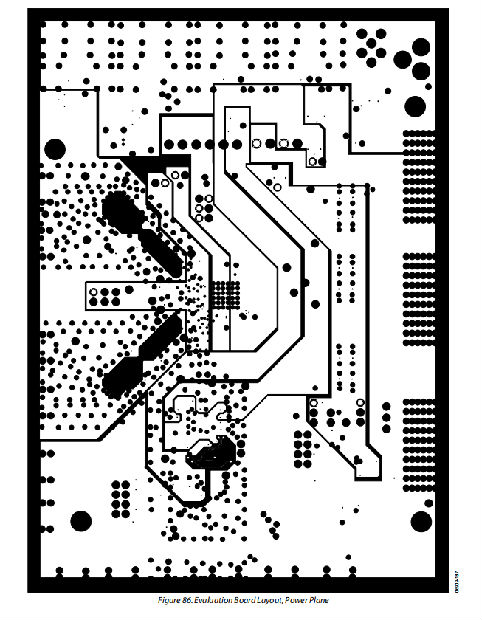

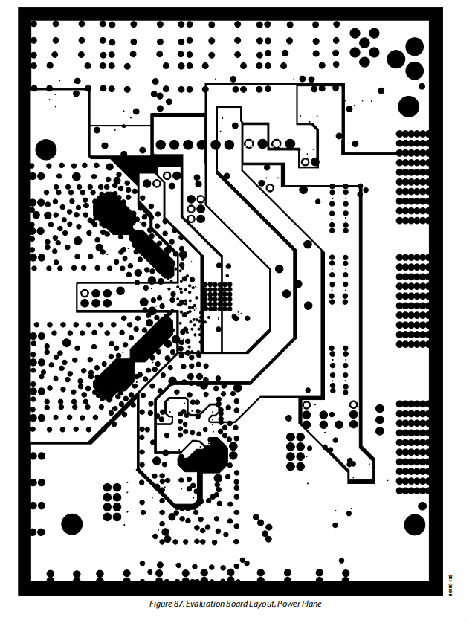

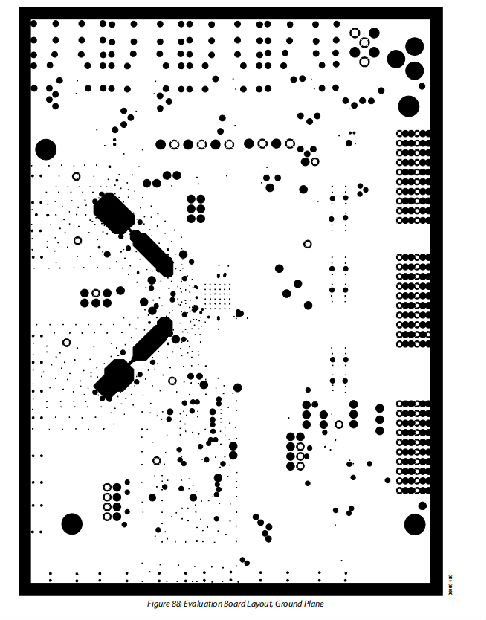

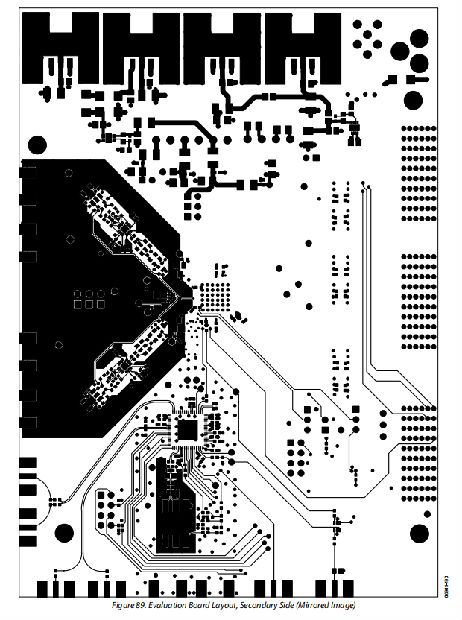

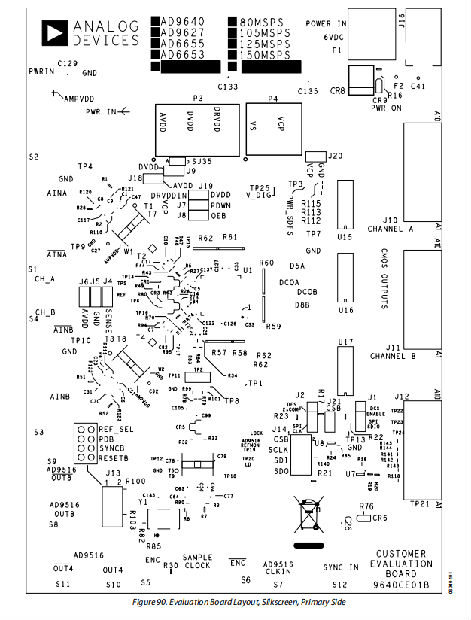

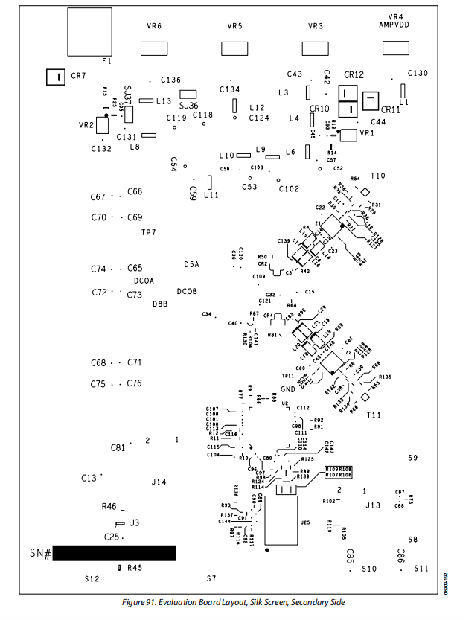

为了使ADC和PCB之间的覆盖率和附着力最大化,需要覆盖一个丝网,将PCB上的连续平面分割成几个均匀的部分。在回流过程中,这在ADC和PCB之间提供了几个连接点。使用一个没有分区的连续平面可以保证ADC和PCB之间只有一个连接点。请参阅评估板布局图(图84至图91)以获取PCB布局的示例。有关芯片级封装的封装和PCB布局的详细信息,请参阅AN-772应用说明,引线框架芯片级封装(LFCSP)的设计和制造指南。

CML

CML引脚应使用0.1μF电容器与接地分离,如图47所示。

印度卢比

AD9600要求用户在RBIAS引脚和接地之间放置一个10 kΩ电阻。此寄存器设置ADC核心的主电流参考,并且至少应有1%的公差。

参考解耦

VREF管脚应与一个低ESR 1.0μF电容器和一个0.1μF陶瓷低ESR电容器并联进行外部解耦接地。

SPI端口

SPI端口不应在需要转换器完全动态性能的期间处于活动状态。由于SCLK、CSB和SDIO信号通常与ADC时钟异步,这些信号的噪声会降低转换器的性能。如果车载SPI总线用于其他设备,则可能需要在该总线和AD9600之间提供缓冲区,以防止这些信号在关键采样期间的转换器输入。

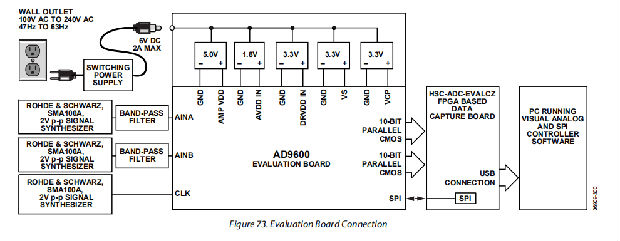

评估委员会

AD9600评估板提供在各种模式和配置下操作ADC所需的所有支持电路。转换器可以使用双巴伦配置(默认)或AD8352差分驱动器进行差分驱动。ADC也可以单端驱动。提供单独的电源引脚,以将DUT与AD8352驱动电路隔离。每个输入配置都可以通过正确连接不同的组件来选择(参见图74到图83)。图73显示了用于评估AD9600交流性能的典型工作台特性设置。

模拟输入和时钟所用的信号源具有非常低的相位噪声(<1ps rms抖动)是实现转换器最佳性能的关键。为了达到规定的噪声性能,还需要对模拟输入信号进行适当的滤波,以消除谐波,降低输入端的集成或宽带噪声。

请参见图74至图91,以获取完整的示意图和布局图,这些示意图和布局图演示了应在系统级应用的路由和接地技术。

电源

评估板配有壁挂式开关电源,提供6伏,2安的最大输出。以47赫兹至63赫兹的频率将电源连接至额定100伏交流电至240伏交流电墙壁插座。电源输出是一个2.1毫米内径的圆形插孔,连接到J16的PCB。一旦安装到PC板上,6 V电源在连接到6个低电压降线性稳压器(为板的各个部分提供适当的偏压)之前将被熔断和调节。

可以使用外部电源操作评估板,方法是卸下L1、L3、L4和L13,以断开开关电源提供的电压调节器。这使得用户能够对电路板的每个部分进行单独的偏置。使用P3和P4为每个部分连接不同的电源。AVDD和DVDD至少需要一个1.8v电源,电流容量为1a;DRVDD建议使用单独的1.8v至3.3v电源。要使用AD8352驱动器操作评估板,需要一个单独的5.0V电源(AMP VDD)和1 a电流能力。为了使用备用SPI选项操作评估板,除了其他电源外,还需要单独的3.3V模拟电源(VS)。3.3V电源(VS)也应具有1A电流能力。如果需要,使用焊料跳线SJ35允许用户分离AVDD和DVD。

输入信号

当将时钟和模拟源连接到评估板时,使用低相位噪声的干净信号发生器,如Rohde&Schwarz SMA100A或Agilent HP8644信号发生器或等效设备,以及1 m屏蔽RG-58 50Ω同轴电缆。输入ADC所需的频率和振幅。模拟设备的AD9600评估板可以接受~2.8V p-p或13dBm正弦波输入。连接模拟输入源时,建议使用带50Ω终端的多极窄带带通滤波器。TTE、Allen Avonics和K&L微波公司提供了此类带通滤波器的良好选择。如果可能,将滤波器直接连接到评估板。

并行CMOS输出直接与模拟接口

设备标准ADC数据采集板(HSC-ADCEVALCZ)。有关ADC数据采集板及其可选设置的更多信息,请访问/FIFO。

输出信号

默认操作和跳线选择设置

以下是AD9600评估板上允许的默认和可选设置或模式的列表。

POWER

将随评估套件提供的开关电源连接在47 Hz至63 Hz和P500的额定100 V ac至240 V ac墙壁插座之间。

VIN

评估板是为双平衡配置模拟输入设置的,在70MHz到200MHz之间具有最佳的50Ω阻抗匹配。为了获得更多的带宽响应,可以改变或移除模拟输入端的差动电容器(见表10)。模拟输入的共模通过ADC的CML引脚从变压器的中心抽头发展而来(参见模拟输入注意事项部分)。

VREF

VREF被设置为1.0V,方法是将检测插脚连接到地上,并在收割台J5上添加一根跨接导线(插脚1到插脚2)。这导致ADC在2.0 V p-p满标度范围内工作。要将ADC置于1.0v p-p模式(VREF=0.5v),应在报头J4上放置一个跳线。评价委员会还包括一个单独的外部参照选择。要使用外部参考,请将J6的针脚1连接到J6的针脚2,并在TP5处提供外部参考。电压参考章节详细说明了VREF选项的正确使用。

印度卢比

RBIA要求10 kΩ电阻器(R503)接地。此引脚用于设置ADC核心偏置电流。

时钟

默认的时钟输入电路是从使用高带宽1:1阻抗比balun(T5)的简单baluncoupled电路导出的,该电路向时钟路径添加非常低的抖动量。时钟输入端接50Ω,交流耦合以处理单端正弦波输入。变压器将单端输入转换为差分信号,该差分信号在输入ADC时钟输入之前被截断。当使用AD9600输入时钟分配器时,可以通过连接器S5将高达625mhz的时钟频率输入到评估板中。

PDWN

要启用断电功能,请连接J7,将PDWN引脚短接至AVDD。

中央结算银行

CSB引脚在内部上拉,将芯片设置为外部引脚模式,以忽略SDIO和SCLK信息。要将CSB引脚的控制连接到评估板上的SPI电路,请将J21的引脚1连接到J21的引脚2。

SCLK/DFS系统

如果SPI端口处于外部pin模式,则SCLK/DFS pin设置输出的数据格式。如果管脚是左浮动的,管脚会在内部下拉,将默认数据格式条件设置为偏移二进制。将J2的Pin 1连接到J2的Pin 2将格式设置为twos补码。如果SPI端口处于串行引脚模式,则将J2的引脚2连接到J2的引脚3将SCLK引脚连接到车载SPI电路(请参阅串行端口接口(SPI)部分)。

SDIO/DCS系统

如果SPI端口处于外部pin模式,SDIO/DCS pin动作设置占空比稳定器。如果管脚保持浮动,管脚会在内部上拉,将默认条件设置为“启用DCS”。要禁用DCS,请将触针1连接到触针2。如果SPI端口处于串行pin模式,则将J1的引脚2连接到J1的引脚3将SDIO引脚连接到车载SPI电路(请参阅串行端口接口(SPI)部分)。

备用时钟配置

AD9600评估板上提供了两个时钟选项。第一种选择是使用车载晶体振荡器(Y1)为部件提供时钟输入。为使该晶体工作,应安装电阻器R8(0Ω)和R85(10 kΩ),并拆下电阻器R82和R30。

第二种选择是使用差分LVPECL时钟,使用AD9516-4(U2)驱动ADC输入。使用此选项时,需要填充AD9516-4充油泵滤清器部件(见图78)。有关更多信息,请参阅AD9516-4数据表。

要将时钟输入(来自S5)配置为驱动AD9516参考输入而不是直接驱动ADC,需要添加、移除和/或更改以下组件。

1、删除默认时钟路径中的R32、R33、R99和R101。

2、使用0.001μF电容器填充C78和C79,在时钟路径中使用0Ω电阻填充R78和R79。

此外,未使用的AD9516输出(一个lvd和一个LVPECL)被路由到评估板上的可选连接器S8到S11。

替代模拟输入驱动器配置

本节提供使用AD8352的替代模拟输入驱动器配置的简要说明。使用此驱动器选项时,需要填充一些其他组件。有关AD8352差分驱动器的更多详细信息,包括其工作原理和可选的管脚设置,请参阅AD8352数据表。

要将模拟输入配置为驱动AD8352而不是默认变压器选项,需要为通道A添加、删除和/或更改以下组件。此外,应更改通道B的相应组件。

1、删除默认模拟输入路径中的C1、C17、C18和C117。

2、在模拟输入路径中使用0.1μF电容器填充C8和C9。要在差分输入模式下驱动AD8352,请填充变压器T10;电阻器R1、R37、R39、R126和R127;以及电容器C10、C11和C125。

3、用所需组件(包括可选低通滤波器)填充可选放大器输出路径。安装0Ω电阻器R44和R48。电阻R43和R47应增加(通常为100Ω),以将AD8352所示的输出阻抗增加至200Ω。

评估板布局

外形尺寸

[一]用低输入频率、满标度正弦波测量,每个输出位上大约有5 pF负载。

[二]输入电容是指一个差动输入引脚与AGND之间的有效电容。等效模拟输入结构见图8。

[三]使用直流输入测量备用电源,CLK+和CLK-引脚不活动)设置为AVDD或AGND。

[四]有关完整的定义,请参阅AN-835应用说明,了解高速ADC测试和评估。

[五]串扰在100 MHz下测量,在一个信道上有-1 dBFS,在备用信道上没有输入。

[六]在5 pF负载下,测量从CLK+和CLK-引脚50%转换到输出数据引脚50%转换的输出传播延迟。

[七]唤醒时间取决于去耦电容的值。