128点击型号即可查看芯片规格书

AT25512点击型号即可查看芯片规格书

特征

兼容串行外围接口(SPI);支持SPI模式0(0,0)和3(1,1);数据表描述了模式0操作低压运行;1.8(VCC=1.8V至5.5V);20MHz时钟频率(4.5V至5.5V);支持128字节页面模式和字节写入操作;块写保护;保护1/4、1/2或整个阵列;为两个硬件写入保护(WP)引脚和写禁用指令和软件数据保护;自动定时写入周期(最大5ms);高可靠性;耐久性:1000000次写入周期;数据保存:40年;无铅/无卤装置;8-引线JEDEC SOIC、8-引线TSSOP和8-pad UDFN封装;模具销售选项:晶圆形状、华夫饼包装和凸模。

说明

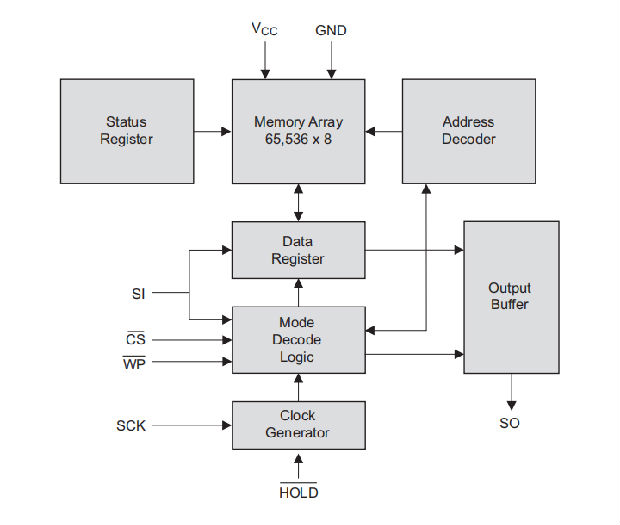

Atmel®AT25512提供524288位串行电擦除可编程只读存储器(EEPROM),每8位65536字。该设备经过优化,可用于许多工业和商业应用,其中低功率和低电压操作是必不可少的。这些设备有节省空间的8-lead JEDEC SOIC、8-lead TSSOP和8-pad UDFN封装。此外,该设备的工作电压为1.8伏至5.5伏。

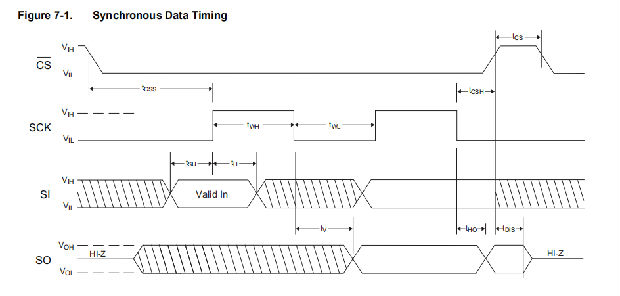

AT25512通过芯片选择引脚(CS)启用,并通过三线接口,包括串行数据输入(SI)、串行数据输出(SO)和串行时钟(SCK)。所有编程周期都是完全自动计时的,在写入之前不需要单独的擦除周期。

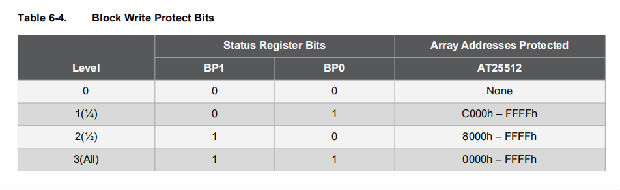

块写保护通过对状态寄存器进行编程来启用,状态寄存器可以是顶部的1/4、顶部的1/2或整个写保护阵列。单独的程序启用和程序禁用说明提供额外的数据保护。通过WP pin提供硬件数据保护,以防止意外写入状态寄存器。保持引脚可用于在不重置串行序列的情况下暂停任何串行通信。

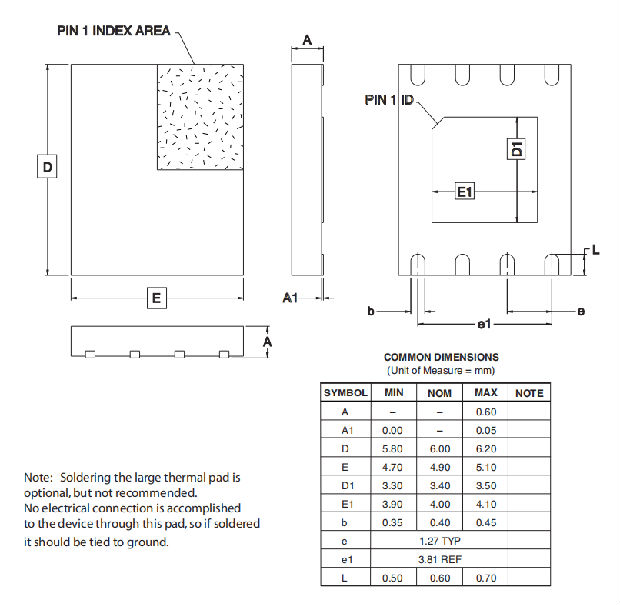

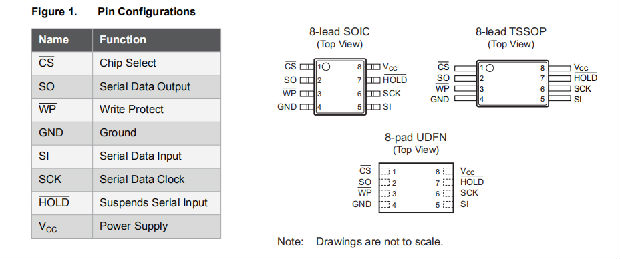

1、引脚配置和引脚

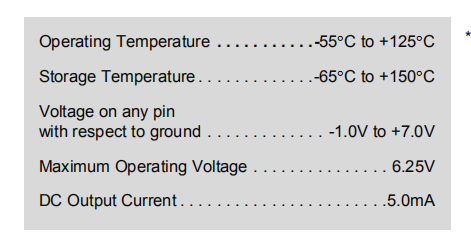

2、绝对最大额定值*

超过“绝对最大额定值”下列出的应力可能会对设备造成永久性损坏。这只是一个应力额定值,并不意味着设备在这些或任何其他条件下的功能操作超出了本规范操作章节的规定。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

3、方块图

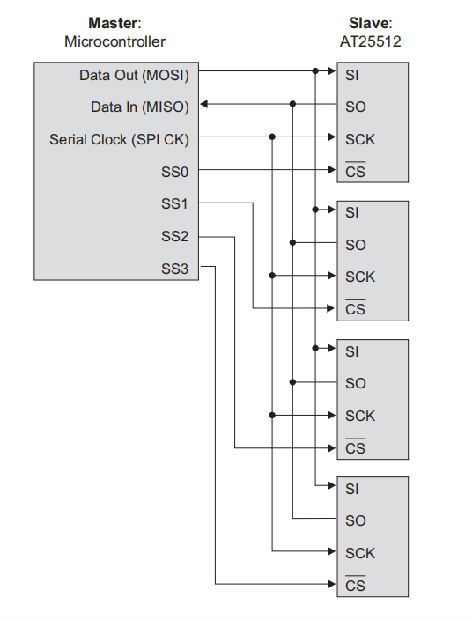

5、串行接口说明

主人:产生串行时钟的设备。

从机:由于串行时钟引脚(SCK)始终是一个输入,AT25512始终作为从机运行。

发射机/接收机:AT25512具有用于数据传输(SO)和接收(SI)的单独管脚。

最高有效位:最高有效位(MSB)是发送和接收的第一个位。

串行操作码:选择设备后,CS将变低,第一个字节将被接收。此字节包含定义要执行的操作的操作码。

无效的操作码:如果接收到无效的操作码,则不会将任何数据移动到AT25512,串行输出引脚(因此)将保持高阻抗状态,直到再次检测到CS的下降沿。这将重新初始化串行通信。

芯片选择:当CS引脚低时,选择AT25512。当未选择设备时,数据将不通过SI引脚接受,SO引脚将保持高阻抗状态。

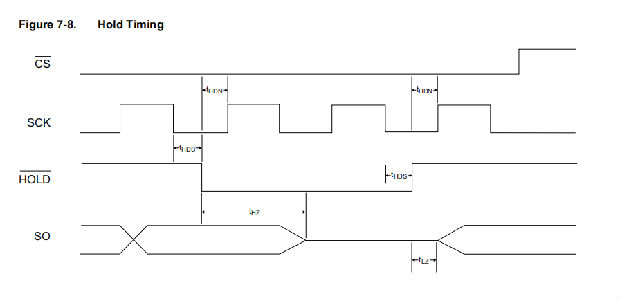

保持:保持引脚与CS引脚一起用于选择AT25512。当设备被选中并且串行序列正在进行时,可以使用Hold暂停与主设备的串行通信,而不重置串行序列。要暂停,必须在SCK引脚低时将保持引脚调低。要恢复串行通信,当SCK引脚低时保持引脚高(SCK仍然可以切换在保持期间)。当SO管脚处于高阻抗状态时,对SI管脚的输入将被忽略。

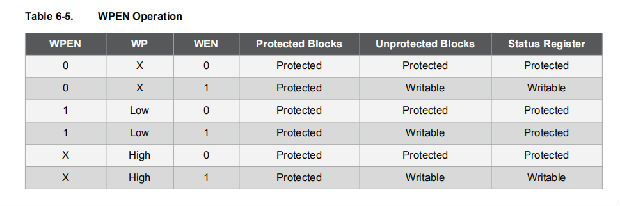

写保护:当保持高位时,写保护引脚(WP)将允许正常的读/写操作。当WP pin变低,WPEN位为1,所有对状态寄存器的写操作都被禁止。当CS仍然低时,WP变低将中断对状态寄存器的写入。如果内部写入循环已经启动,WP变低对状态寄存器的任何写入操作都没有影响。当状态寄存器中的WPEN位为零时,WP pin函数被阻塞。这将允许用户在一个WP管脚接地的系统,仍然能够写入状态寄存器。当WPEN位设置为1时,启用所有WP pin功能。

图5-1。SPI串行接口

6、功能描述

AT25512设计用于直接与6800型系列微控制器的同步串行外围接口(SPI)接口。

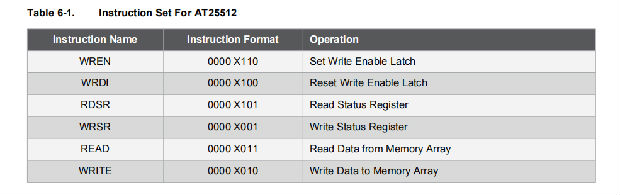

AT25512使用8位指令寄存器。说明清单及其操作代码见表7-3。所有指令、地址和数据都先用MSB进行传输,并以从高到低开头CS转换。

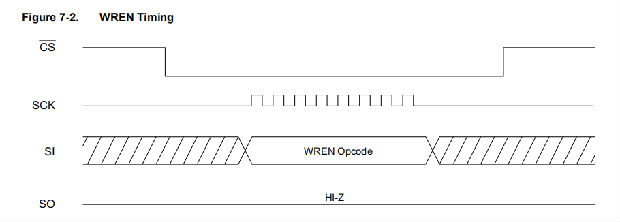

写入启用(WREN):应用VCC时,设备将在写禁用状态下通电。因此,所有编程指令前面都必须有一条允许写入指令。

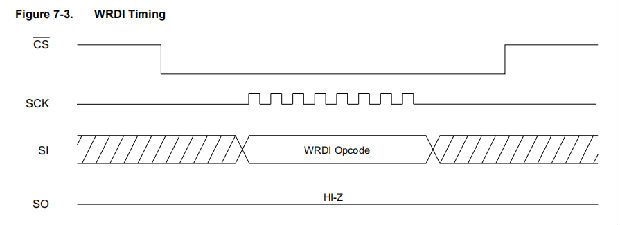

写禁用(WRDI):为了防止设备意外写入,Write Disable指令禁用所有编程模式。WRDI指令与WP引脚的状态无关。

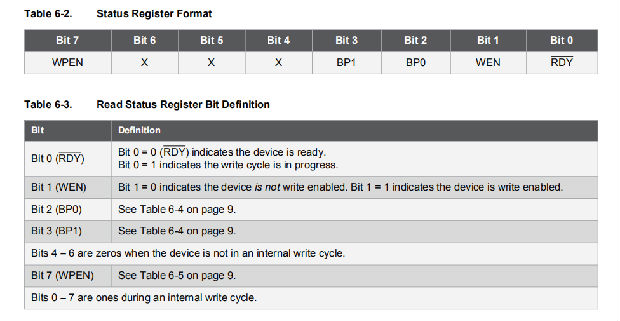

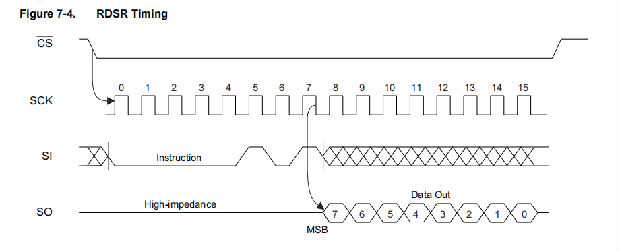

读取状态寄存器(RDSR):读取状态寄存器指令提供对状态寄存器的访问。

设备的就绪/忙碌和写入启用状态可以由RDSR指令确定。类似地,块写入保护位指示所采用的保护的范围。这些位是使用WRSR指令设置的。

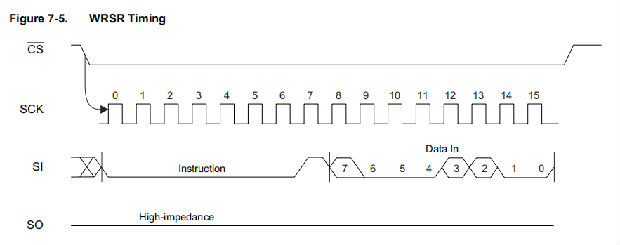

写入状态寄存器(WRSR):WRSR指令允许用户从四个保护级别中选择一个。AT25512分为四个阵列段:

1、无或

2、顶部四分之一(四分之一)或

3、上半部分(1/2)或

4、所有的内存段都可以被保护

因此,任何选定段内的任何数据都将是只读的。块写保护级别和相应的状态寄存器控制位如表6-4所示。

三位BP0、BP1和WPEN是非易失性单元,它们具有与常规存储单元(例如WREN、tWC、RDSR)相同的属性和功能。

WRSR指令还允许用户通过使用Write Protect enable(WPEN)位来启用或禁用Write Protect(WP)管脚。当WP引脚低且WPEN比特是一个。当WP pin为高或WPEN位为零时,将禁用硬件写保护。当设备为硬件写保护时,对状态寄存器的写操作(包括块保护位和WPEN位)和内存阵列中的块保护部分将被禁用。只允许写入不受块保护的内存段。

注意:当WPEN位为硬件写保护时,只要WP pin保持低位,就不能将其改回零。

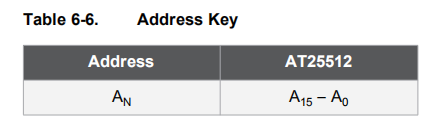

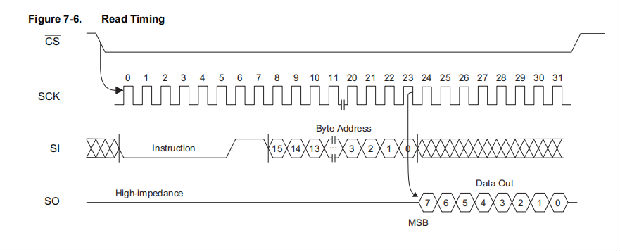

读取顺序(读取):通过SO引脚读取AT25512需要以下顺序。在CS线被拉低以选择一个设备后,读取的操作码通过SI线传输,后面跟着要读取的字节地址(见表6-6)。完成后,将忽略SI行上的任何数据。数据(D7–D0)位于然后将指定的地址移到SO行。如果只读取一个字节,那么在数据输出之后,CS行应该被驱动得很高。由于字节地址自动递增,数据将继续移出,因此可以继续读取序列。当达到最高地址时,地址计数器将滚动到最低地址,允许在一个连续的读取周期中读取整个内存。

写入序列(写入):为了对AT25512进行编程,必须执行两条单独的指令。首先,设备必须通过write Enable(WREN)指令启用写。然后可以执行写指令。此外,要编程的存储器位置的地址必须在块写入保护级别选择的受保护地址字段位置之外。在内部写入周期中,除RDSR指令外,所有命令都将被忽略。

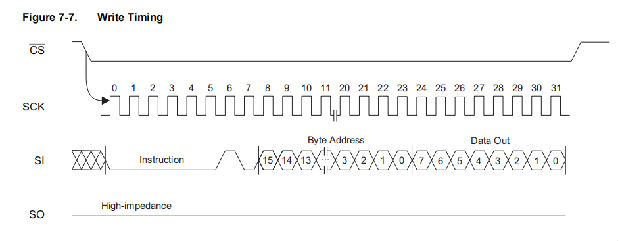

写指令需要以下顺序。在CS线被拉低以选择设备后,写入操作码通过SI线传输,后跟字节地址和要编程的数据(D7–D0(见表6-6)。程序将在CS引脚调高后启动。(在D0(LSB)数据位打卡后,必须在SCK low时间内立即发生CS管脚从低到高的转换。

设备的就绪/忙碌状态可以通过启动读取状态寄存器(RDSR)指令来确定。如果位0=1,则写入周期仍在进行中。如果位0=0,则写入周期已结束。在写编程周期中,只有读状态寄存器指令被启用。

AT25512能够执行128字节的页写入操作。在接收到每个字节的数据后,七个低阶地址位在内部递增一位;地址的高阶位将保持不变。如果传输的数据超过128字节,地址计数器将翻转,先前写入的数据将被覆盖。AT25512在写入周期结束时自动返回到写禁用状态。

注意:如果设备未启用写(WREN),设备将忽略写指令并返回到当CS升高时的待机状态。需要一个新的CS下降沿来重新启动串行通信。

7、时序图(SPI模式0(0,0))

8、包装信息

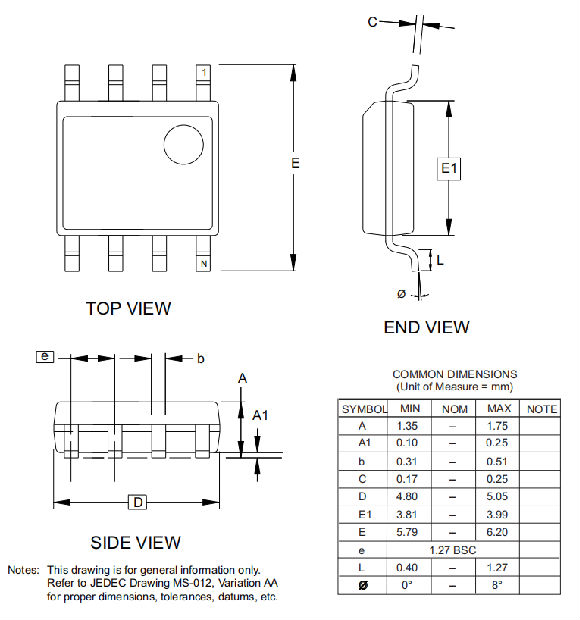

8.1、8S1-8导JEDEC SOIC

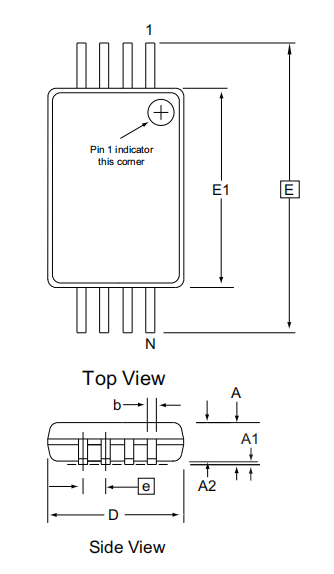

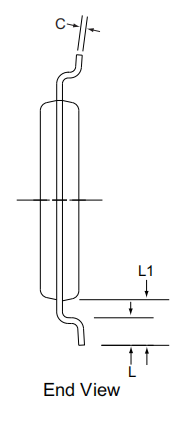

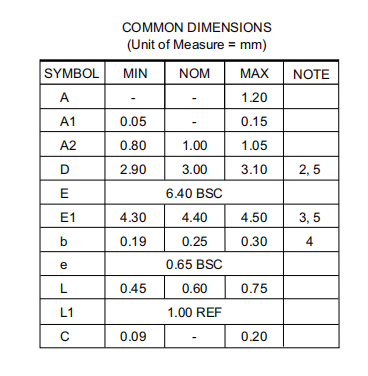

8.2 8X-8导TSSOP

注:1、本图仅供参考。有关正确的尺寸、公差、基准等,请参考JEDEC图纸MO-153,变更AA。

2、尺寸D不包括模具飞边、突出物或浇口伯尔斯。模具飞边、凸出物和浇口毛刺每侧不得超过0.15mm(0.006in)。

3、尺寸E1不包括引线间闪光或突出。每侧导线间闪光和突起不得超过0.25 mm(0.010in)。

4、尺寸b不包括Dambar突出部分。在最大材料条件下,允许的坝筋突出量应超过b尺寸的0.08mm。Dambar不能位于脚的下半径。突出物与相邻导线之间的最小间距为0.07mm。

5、尺寸D和E1在基准面H处确定。

9.3 8Y7 — 8-pad UDFN