198点击型号即可查看芯片规格书

208点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

摘要

通信、音频、汽车、仪表和工业用高性能信号计算机;超级哈佛架构计算机(SHARC);四条独立总线,用于单周期上的双数据、指令和I/O获取;32位定点运算;32位和40位浮点运算;544kbits片上SRAM存储器和集成I/O;外围设备:I2S支持,8个同时接收和传输信道;主要特点:66mips,198 MFLOPS峰,132 MFLOPS持续;性能:用户可配置544kbits片上SRAM存储器;两个外部端口、DMA通道和八个串行端口,DMA通道;低成本无胶接口SDRAM控制器;外部存储器(@66兆赫);64M字外部地址范围;12个可编程I/O引脚和两个带事件的定时器;捕获选项;与ADSP-2106x系列兼容的代码;208铅MQFP或196球迷你BGA包;3.3伏操作;灵活的数据格式和40位扩展精度;32位单精度和40位扩展精度IEEE;浮点数据格式;32位定点数据格式,整数和小数,带双80位累加器;并行计算;单周期乘法和算术运算与双内存读/写和指令获取并行;用加法和减法相乘加速FFT,但计算简单;1024点复FFT基准:0.274 ms(18221周期)。

544kbits可配置片上SRAM;通过核心处理器和DMA实现独立访问的双端口;可配置为块0和块1中16、32、48位数据和程序字的组合DMA控制器;10个DMA通道,2个专用于外部端口;8个专用于串行端口;并行、高达66兆赫的后台DMA传输;使用全速处理器执行;在以下之间执行传输:内部RAM和主机;内部RAM和串行端口;内部RAM和主/从SHARC;内部RAM和外部存储器或I/O设备;外部存储器和外部设备;主机处理器接口;8位、16位和32位微处理器的高效接口;主机可直接读写ADSP-21065L IOP寄存器;多处理;无胶并行分布式片上总线仲裁;两台ADSP-21065Ls Plus主机之间的总线连接;132mbytes/s并行总线传输速率;串行端口;独立的发送和接收功能;可编程的3位到32位串行字宽度;I2S支持8次发射和8次接收频道;工业标准编解码器的无胶接口;带-法则/A法则硬件的TDM多信道模式压扩;多信道信令协议。

一般说明

ADSP-21065L是SHARC的强大成员为成本敏感应用程序优化的32位处理器系列。SHARC Super Harvard体系结构提供了业界任何32位DSP中最高级别的性能和内存集成它们也是业界唯一同时提供固定和浮点功能而又不影响精度或性能的DSP。

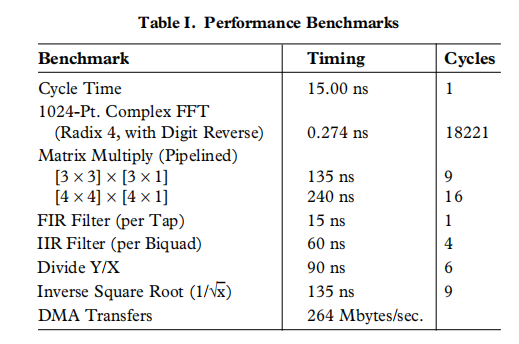

ADSP-21065L采用高速、低功耗CMOS工艺,采用0.35微米技术制造,具有32位DSP-66 MIPS(198 MFLOPS)的最高性能。通过片上指令缓存,处理器可以在一个周期内执行每一条指令。表1列出了ADSP-21065L。

ADSP-21065L SHARC结合了浮点数字信号处理器内核和集成的片上系统功能,包括544kbit的SRAM内存、主机处理器接口、DMA控制器、SDRAM控制器和增强的串行端口。

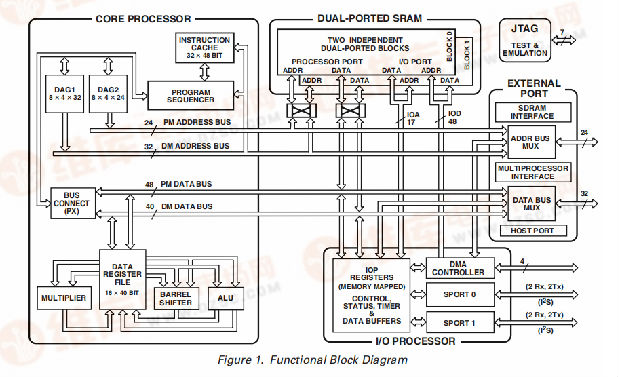

图1显示了ADSP-21065L的框图,说明了以下架构特性:带有共享数据寄存器文件;数据地址生成器(DAG1、DAG2);带指令缓存的程序序列器;具有事件捕获模式的计时器;片上双端口SRAM;与片外存储器和外围设备;主机端口和SDRAM接口;DMA控制器;增强的串行端口;JTAG测试访问端口。

ADSP-21000系列核心架构

ADSP-21065L的代码和功能与ADSP-21060/ADSP-21061/ADSP-21062兼容。ADSP-21065L包括SHARC家族核心的以下架构特性。

独立的并行计算单元

算术/逻辑单元(ALU)、乘法器和移位器都执行单周期指令。这三个单元并行排列,最大化了计算吞吐量。单个多功能指令执行并行运算单元和乘法器操作。这些计算单元支持IEEE 32位单精度浮点、扩展精度40位浮点和32位定点数据格式。

数据寄存器文件

通用数据寄存器文件用于在计算单元和数据总线之间传输数据,以及存储中间结果。这个10端口,32寄存器(16个主寄存器,16个次寄存器)寄存器文件,结合ADSP21000哈佛体系结构,允许计算单元和内部存储器之间的无约束数据流。

指令和两个操作数的单周期获取ADSP-21065L采用了增强的超级哈佛体系结构,其中数据存储器(DM)总线传输数据,程序存储器(PM)总线传输指令和数据(见图1)。通过其独立的程序和数据存储总线以及片上指令缓存,处理器可以在一个周期内同时获取两个操作数和一条指令(从缓存)。

指令缓存

ADSP-21065L包括一个片上指令缓存,它支持三总线操作来获取一条指令和两个数据值。缓存是选择性的,只缓存获取与PM总线数据访问冲突的指令。这允许全速执行核心、循环操作,如数字滤波器乘法累加和FFT蝶形处理。

带硬件循环缓冲区的数据地址生成器ADSP-21065L的两个数据地址生成器(DAG)在硬件上实现循环数据缓冲区。圆形缓冲器允许有效编程延迟线和数字信号处理所需的其他数据结构,通常用于数字滤波器和傅里叶变换。ADSP-21065L的两个DAG包含足够的寄存器,可以创建多达32个循环缓冲区(16个主寄存器集,16个次寄存器集)。DAG自动处理环绕的地址指针,减少开销,提高性能,并简化实现。循环缓冲区可以在任何内存位置开始和结束。

灵活指令集

48位指令字可容纳各种并行操作,以实现简洁的编程。例如,ADSP21065L可以有条件地在一条指令中执行乘法、加法、减法和分支。

ADSP-21065L功能

ADSP-21065L旨在实现最高的系统吞吐量,以实现最大的系统性能。它可以由晶体或TTL兼容的时钟信号来计时。ADSP-21065L使用的输入时钟的频率等于指令速率的一半——33兆赫的输入时钟产生15纳秒的处理器周期(相当于66兆赫)。ADSP-21065L上的接口操作如下所示。在本文后面,1x=输入时钟频率,2x=处理器的指令速率。

以下时钟操作额定值基于1x=33MHz(指令速率/核心=66 MHz):

特别提款权 66兆赫

外部SRAM 33兆赫

串行端口 33兆赫

多处理 33兆赫

主机(异步) 33兆赫

扩充ADSP-21000系列核心,ADSP-21065L增加了以下架构功能:

双端口片上存储器

ADSP-21065L包含544kbits的片上SRAM,分为两组:0组288kbits,1组256kbits。第0列配置9列2K×16位,第1列配置8列2K×16位。每个内存块都是双端口的,由核心处理器和I/O处理器或DMA控制器进行单周期独立访问。双端口存储器和独立的片上总线允许在一个周期内从核心进行两次数据传输,从I/O进行一次数据传输(ADSP-21065L存储器映射见图4)。

在ADSP-21065L上,存储器可以配置为32位数据的最大16K字,16位数据的最大34K字,48位指令(和40位数据)的最大10K字,或最大544kbits的不同字大小的组合。所有存储器都可以作为16位、32位或48位访问。

虽然每个存储块可以存储代码和数据的组合,但是当一个块存储数据时,使用DM总线进行传输,而另一个块存储指令和数据时,使用PM总线进行传输,访问效率最高。以这种方式使用DM和PM总线,每个内存块有一个专用的总线,确保单周期执行两次数据传输。在这种情况下,指令必须在缓存中可用。当其中一个数据操作数通过ADSP21065L的外部端口传输到片外或从片外传输时,也保持单周期执行。

片外存储器和外设接口ADSP-21065L的外部端口提供处理器与片外存储器和外围设备的接口。64M字的片外地址空间包含在ADSP-21065L的统一地址空间中。用于程序存储器、数据存储器和I/O的独立片上总线在外部端口上多路复用,以创建具有单个24位地址总线、四个存储器选择和单个32位数据总线的外部系统总线。片内超级哈佛架构提供三总线性能,片外统一地址空间为设计者提供灵活性。

SDRAM接口

SDRAM接口使ADSP-21065L能够以2x时钟频率在同步DRAM(SDRAM)之间传输数据。同步方法加上2倍时钟频率支持高达220mbytes/sec的高吞吐量数据传输。

SDRAM接口提供了一个无胶接口,带有标准SDRAM-16mb、64mb和128mb,包括支持ADSP-21065L和SDRAM之间附加缓冲区的选项。SDRAM接口非常灵活,能够将SDRAM连接到ADSP-21065L的四个外部存储器组中的任何一个。

多个SDRAM设备并行连接的系统可能需要缓冲以满足总体系统计时要求。ADSP-21065L支持地址和控制信号的流水线,以便在自身和多个SDRAM设备之间实现这种缓冲。

主机处理器接口

ADSP-21065L的主机接口提供了与标准微处理器总线(8位、16位和32位)的简单连接,无需额外的硬件。支持异步传输速度高达1x时钟频率,主机接口是通过ADSP-21065L的外部端口访问的。主机接口提供两个DMA通道;代码和数据传输以较低的软件开销完成。

主机处理器使用主机总线请求(HBR)、主机总线授权(HBG)和就绪(REDY)信号请求ADSP-21065L的外部总线。主机可以直接读写ADSP-21065L的IOP寄存器,可以访问DMA通道设置和邮箱寄存器。矢量中断支持使主机命令的有效执行成为可能。

DMA控制器

ADSP-21065L的片上DMA控制器允许零开销、无需处理器干预的非侵入式数据传输。DMA控制器对处理器核心独立且不可见地操作,允许在核心同时执行其程序指令时进行DMA操作。

DMA传输可以发生在ADSP-21065L的内部存储器和外部存储器、外部外设或主机处理器之间。DMA传输也可以发生在ADSP-21065L的内存和串行端口之间。外部存储器和外部外围设备之间的DMA传输是另一种选择。在DMA传输期间执行16、32或48位内部字的外部总线打包。

ADSP-21065L上有10个DMA通道,其中8个通过串行端口,2个通过处理器的外部端口(用于主机处理器、其他ADSP-21065L、内存或I/O传输)。程序可以下载到ADSP21065L使用DMA传输。异步片外外设可以使用DMA请求/授权线(DMAR1-2、DMAG1-2)控制两个DMA信道。其他DMA功能包括完成DMA传输时的中断生成和自动链接DMA传输的DMA链接。

串行端口

ADSP-21065L具有两个同步串行端口,为各种数字和混合信号外围设备提供廉价的接口。串行端口可以在1x时钟频率下工作,为每个端口提供33 Mbit/s的最大数据速率。每个串行端口都有一组主和一组次发射和接收通道。独立的发送和接收功能为串行通信提供了更大的灵活性。串行端口数据可以通过DMA自动地在片上存储器之间传输。每个串行端口都支持三种操作模式:DSP串行端口模式、I2S模式(音频编解码器常用的接口)和TDM(时分多路复用)多通道模式。

串行端口可以使用小端或大端传输格式,可选字长为3位到32位。它们提供可选的同步和传输模式以及可选的μ-律或A-律压扩。串行端口时钟和帧同步可以在内部或外部生成。串行端口还包括关键字和密钥掩码功能,以增强处理器间的通信。

可编程定时器和通用I/O端口ADSP-21065L有两个独立的定时器块,每个定时器块执行两个脉冲宽度生成和脉冲计数与捕获功能。

在脉冲宽度产生模式下,ADSP-21065L可以在最大71.5秒的周期内产生具有任意脉冲宽度的调制波形。

在脉冲计数器模式下,ADSP-21065L可以测量输入波形的高或低脉冲宽度和周期。

ADSP-21065L还包含12个可编程的通用I/O引脚,可作为输入或输出。作为输出,这些管脚可以向外围设备发送信号;作为输入,这些管脚可以提供条件分支的测试。

程序启动

ADSP-21065L的内部存储器可以在系统通电时从8位EPROM、主机处理器或外部存储器。启动源的选择由BMS(启动内存选择)和BSEL(EPROM启动)控制别针。8位、16位或32位主机处理器均可用于引导。有关详细信息,请参阅本数据表“管脚说明”部分中的BMS和BSEL管脚说明。

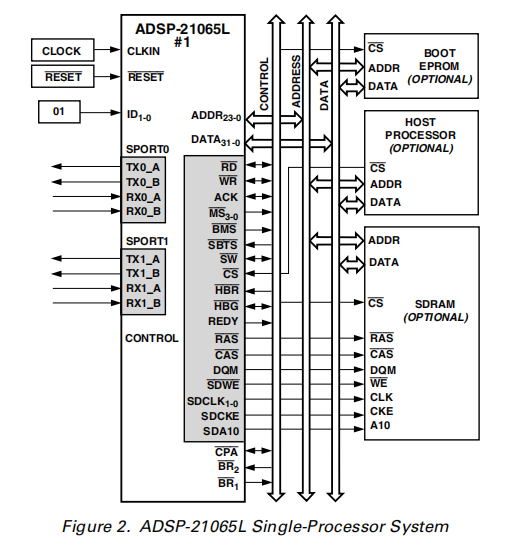

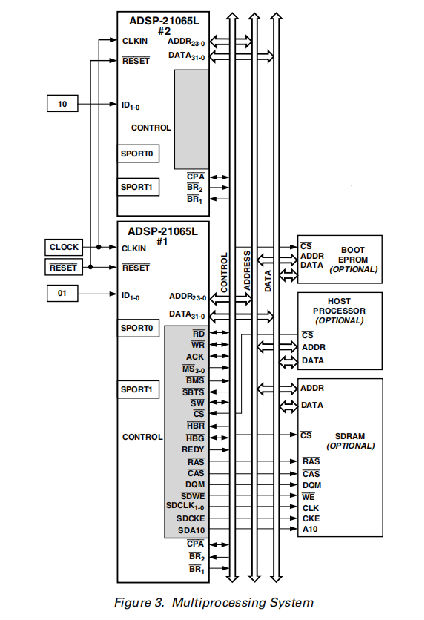

多处理

ADSP-21065L为多处理的数字信号处理系统提供了强大的功能。统一的地址空间允许处理器间直接访问两个ADSP-21065L的IOP寄存器。分布式总线仲裁逻辑包含在芯片上,用于简单、无胶连接最多包含两个ADSP-21065L和一个主机处理器的系统。主处理器转换只产生一个周期的开销。总线锁允许信号量的不可分割的读-修改-写序列。为处理器间命令提供矢量中断。外部端口上处理器间数据传输的最大吞吐量为132 MB/秒。

开发工具

ADSP-21065L支持一整套软件和硬件开发工具,包括EZ-ICE®InCircuit模拟器和开发软件。

用于ADSP-21060/ADSP-21062的EZ-ICE硬件也完全模拟ADSP-21065L。

SHARC开发工具系列和VisualDSP®集成项目管理和调试环境都支持ADSP-21065L。VisualDSP项目管理环境使您能够从单个集成程序中开发和调试应用程序。

SHARC开发工具包括一个基于代数语法的易于使用的汇编程序;一个汇编库/库;一个链接器;一个加载程序;一个循环精确的指令级模拟器;一个C编译器;以及一个包含DSP和数学函数的C运行时库。

使用Visual DSP调试器调试C和汇编程序,您可以:

8226;查看混合C和汇编代码

•插入断点

•设置观察点

•跟踪总线活动

•概要程序执行

•填充和转储内存

•创建自定义调试器窗口

Visual IDE使您能够定义和管理多用户项目。它的对话框和属性页允许您配置和管理所有SHARC开发工具。此功能使您能够:

•控制开发工具如何处理输入和生成输出。

•与工具的命令行开关保持一对一的通信。

EZ-ICE仿真器利用ADSP-21065L处理器的IEEE 1149.1jtag测试接入端口,在仿真过程中对目标板处理器进行监控。EZ-ICE提供全速仿真,允许检查和修改内存、寄存器和处理器堆栈。通过使用处理器的JTAG接口确保了非侵入式电路内仿真。仿真程序不会影响目标系统的加载或定时。

除了模拟设备提供的软件和硬件开发工具外,第三方还提供了一系列支持SHARC处理器系列的工具。硬件工具包括SHARC-PC插件卡、多处理器SHARC-VME板、具有多个SHARC和附加内存的子模块和模块。这些模块基于SHARCPAC™ 模块规格。第三方软件工具包括Ada编译器、DSP库、操作系统和框图设计工具。

附加信息

有关ADSP-21065L指令集和体系结构的详细信息,请参阅ADSP-21065L SHARC用户手册第三版和ADSP-21065L SHARC技术参考。

管脚说明

ADSP-21065L管脚定义如下所示。被识别为同步的输入必须满足与CLKIN(或与用于TMS、TDI的TCK)有关的定时要求。标识为异步(A)的输入可以异步断言为CLKIN(或异步断言为TRST的TCK)。

除了ADDR23-0、DATA31-0、FLAG11-0、SW和具有内部上拉或下拉电阻器(CPA、ACK、DTxX、DRxX、TCLKx、RCLKx、TMS和TDI)的输入外,未使用的输入应与VDD或GND连接或拉接-这些引脚可以保持浮动。这些引脚有一个逻辑电平保持电路,防止输入内部浮动。

I=输入 S=同步 P=电源 (O/D)=明沟 O=输出 A=异步 G=接地

T=三种状态(当SBTS被断言时,或当ADSP-2106x是总线从机时)

时钟信号

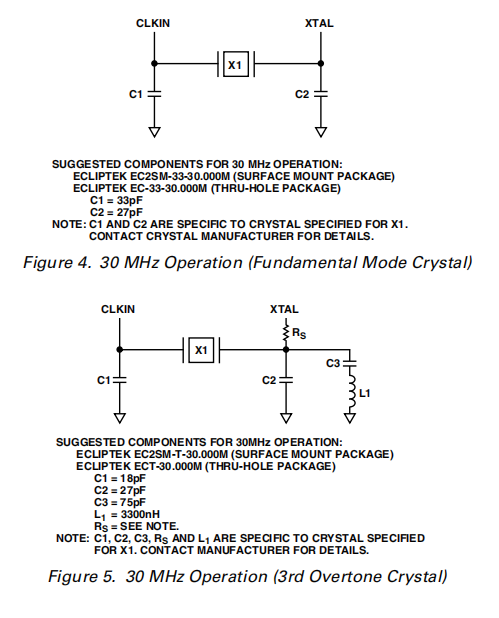

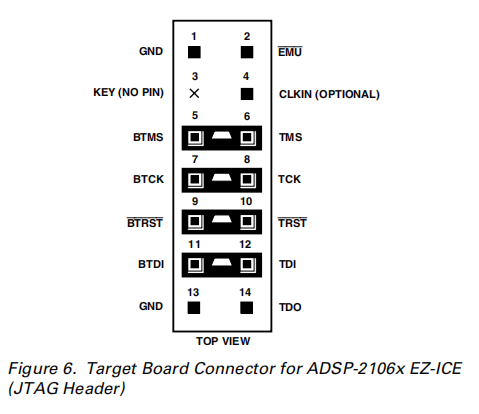

ADSP-21065L可以使用外部时钟或晶体。请参阅CLKIN pin说明。通过将必要的组件连接到CLKIN和XTAL,可以将ADSP-21065L配置为使用其内部时钟生成器。你可以使用在基本模式下工作的晶体或在泛音下工作的晶体。图4显示了在基本模式下运行的晶体所使用的组件连接,图5显示了在泛音下运行的晶体所使用的组件连接。

EZ-ICE探头靶板连接器

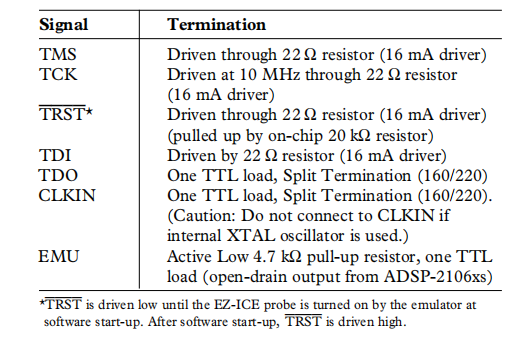

ADSP-2106x EZ-ICE仿真器采用ADSP-2106x的IEEE1149.1JTAG测试接入端口,在仿真过程中对目标板处理器进行监控。EZ-ICE探头要求ADSP-2106x的CLKIN、TMS、TCK、TRST、TDI、TDO、EMU和GND信号可通过14针连接器(2行x 7针条头)在目标系统上访问,如图6所示。EZ-ICE探针直接插在该连接器上,用于板上模拟芯片。如果您打算使用ADSP-2106x EZ-ICE,则必须将此连接器添加到目标板设计中。

EZ-ICE连接器和共享EZ-ICE JTAG引脚的最远设备之间的总跟踪长度应限制在最大15英寸,以保证运行。对长度的限制必须包括EZ-ICE JTAG信号,这些信号被路由到一个或多个2106x设备或2106x和链上其他JTAG设备的组合。

14针,双列针带式收割台的销3位置为键,您必须从收割台上拆下销3。销必须为0.025平方英寸,长度至少为0.20英寸。销间距应为0.1×0.1英寸。可从3M、McKenzie和Samtec等供应商处获得针带头。

提供BTMS、BTCK、BTRST和BTDI信号,以便测试接入端口也可用于板级测试。当连接器不用于仿真时,在Bxxx引脚和xxx引脚之间放置跳线。如果您不打算使用测试访问端口进行板测试,请将BTRST连接到GND,并将BTCK连接到VDD。必须在通电后(通过连接器上的BTRST)或保持低位以使ADSP-2106x正常工作,才能断言TRST引脚。EZ-ICE探针上未连接任何Bxxx引脚(引脚5、7、9、11)。

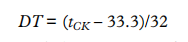

JTAG信号在EZ-ICE探头上终止,如下所示:

将CLKIN连接到EZ-ICE割台的插脚4是可选的。emulator仅在被指示以同步方式执行诸如启动、停止和单步执行两个ADSP-21065L等操作时使用CLKIN。如果不需要在两个处理器上同步执行这些操作,只需将EZ-ICE头的引脚4连接到地上。

对于使用内部时钟发生器和外部离散晶体的系统,不要将CLKIN管脚直接连接到JTAG探头。这将加载振荡器电路,并可能导致其无法振荡。相反,JTAG探头的CLKIN可以由XTAL引脚通过高阻抗缓冲器驱动。

如果需要同步多处理器操作且CLKIN已连接,则多个ADSP-2106x处理器与EZ-ICE头上的CLKIN管脚之间的时钟偏差必须最小。如果偏差过大,同步操作可能在处理器之间关闭一个周期。对于同步多处理器操作,TCK、TMS、CLKIN和EMU应被视为倾斜方面的关键信号,并应在您的电路板上尽可能短地布置。

如果不需要同步多处理器操作(即CLKIN未连接),只需在TCK和TMS上使用适当的并行终端。TDI、TDO、EMU和TRST在倾斜方面不是关键信号。

有关SHARC EZ-ICE的完整信息,请参阅ADSP-21000系列JTAG EZ-ICE用户指南和参考。

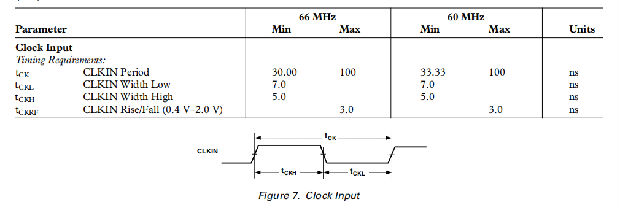

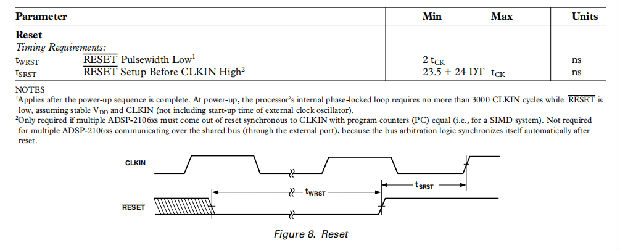

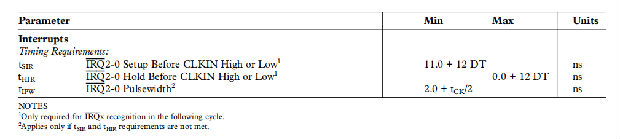

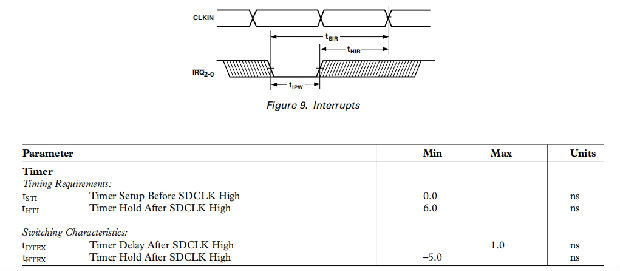

定时规范一般说明

ADSP-21065L提供两种速度等级:60MHz和66MHz指令速率。所示规范基于30 MHz的CLKIN频率(tCK=33.3 ns)。DT降额允许在其他CLKIN频率下的规格(在tCK规格的最小-最大范围内;见下面的时钟输入)。DT是实际CLKIN周期和33.3 ns CLKIN周期之间的差异:

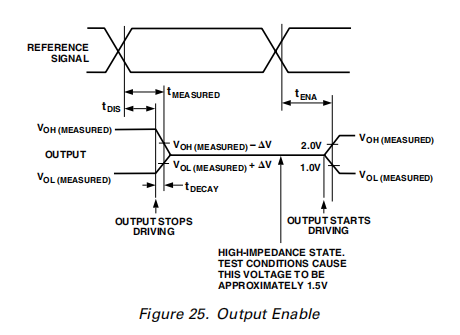

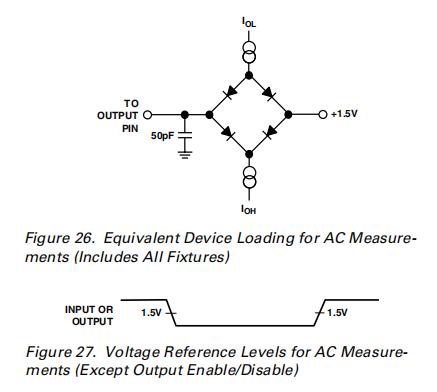

使用给定的精确计时信息。不要试图从其他的加减运算中得到参数。虽然加法或减法会对单个设备产生有意义的结果,但本数据表中给出的值反映了统计变化和最坏情况。因此,不能有意义地添加参数以获得更长的时间。关于电压参考水平,参见图27中交流测量(包括所有固定装置)的等效装置负载。

开关特性指定处理器如何更改其信号。您无法控制处理器外部的定时电路必须设计为与这些信号特性兼容。开关特性告诉你处理器在给定的情况下会做什么。您还可以使用切换特性来确保连接到处理器的设备(如内存)的任何计时要求都得到满足。

时间要求适用于由处理器外部电路控制的信号,如用于读取操作的数据输入。时序要求保证处理器与其他设备一起正常工作。

(O/D)=明沟 (A/D)=主动驱动

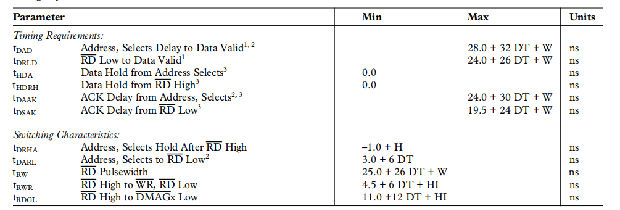

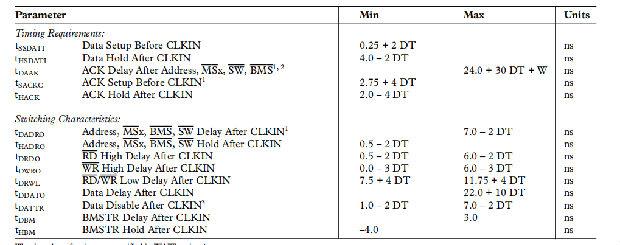

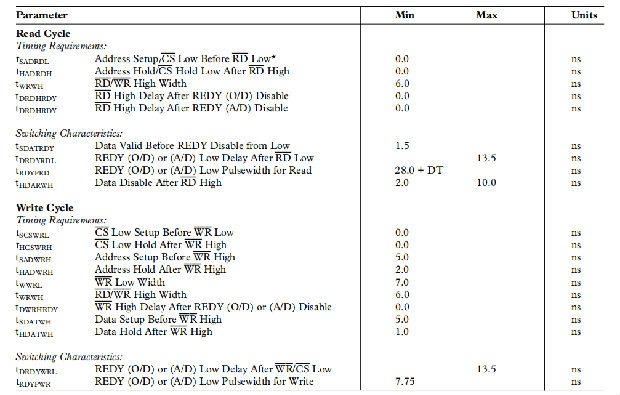

内存读取总线主控

使用这些规范来异步连接到内存(和内存映射外设),而不参考CLKIN。当ADSP-21065L是访问外部内存空间时的总线主机时,这些规范适用。这些开关特性也适用于总线主同步读/写定时(见下面的同步读/写总线主)。如果满足这些定时要求,则可以忽略同步读/写定时(反之亦然)。例外情况是如下注释所述的ACK pin定时要求。

W=(等待寄存器中指定的等待状态数)×tCK。

HI=tCK(如果地址保持周期或总线空闲周期发生,如在等待寄存器中所指定;否则HI=0)。H=tCK(如果在等待寄存器中指定了地址保持周期,则H=0)。

笔记:1、数据延迟/设置:用户必须满足tDAD或tDRLD或同步规范tSSDATI。2、参考MSx、SW、BMS的下降沿。3、在使用内部等待状态模式的外部存储器访问上,没有对ACK进行采样。对于新外部存储器访问的第一个CLKIN周期,ACK必须通过tDAAK或tDSAK或同步规范tSACKC对外部等待状态模式或两者(如果内部等待状态为零,则两者)有效。对于等待状态的外部存储器访问的第二个循环和随后的循环,必须满足外部等待状态模式的同步规范t SACKC和tHACKC,或者两者都满足(在内部等待状态完成后)。

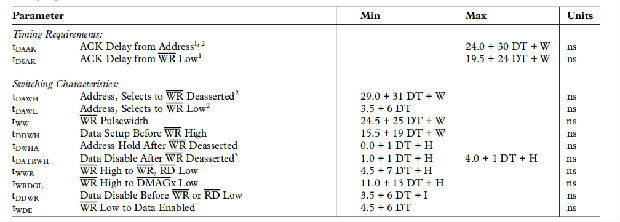

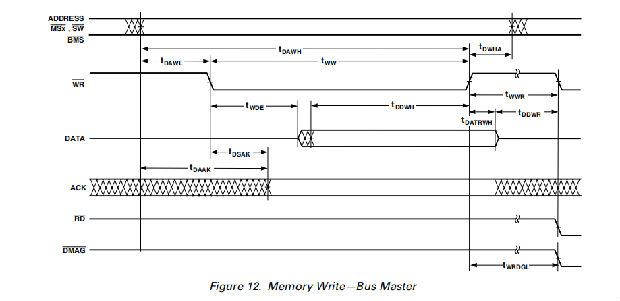

内存写入总线主机

使用这些规范来异步连接到内存(和内存映射外设),而不参考CLKIN。当ADSP-21065L是访问外部内存空间时的总线主机时,这些规范适用。这些开关特性也适用于总线主同步读/写定时(见下面的同步读/写总线主)。如果满足这些定时要求,则可以忽略同步读/写定时(反之亦然)。例外情况是如下注释所述的ACK pin定时要求。

W=(等待寄存器中指定的等待状态数)×tCK。

H=tCK(如果发生地址保持周期,如等待寄存器中所指定;否则H=0)。I=tCK(如果发生总线空闲周期,如等待寄存器中所指定;否则I=0)。

笔记:1、在使用内部等待状态模式的外部内存访问上,没有对ACK进行采样。对于新外部存储器访问的第一个CLKIN周期,ACK必须通过tDAAK或tDSAK或同步规范tSACKC对外部等待状态模式或两者(如果内部等待状态为零,则两者)有效。对于等待状态的外部存储器访问的第二个循环和随后的循环,必须满足外部等待状态模式的同步规范t SACKC和tHACKC,或者两者都满足(在内部等待状态完成后)。2、参考MSx、SW和BMS的下降沿。3、有关给定电容和直流负载的保持时间计算,请参阅测试条件下的系统保持时间计算。

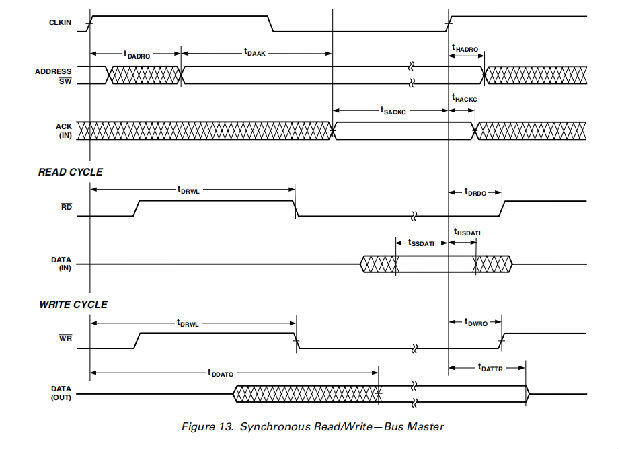

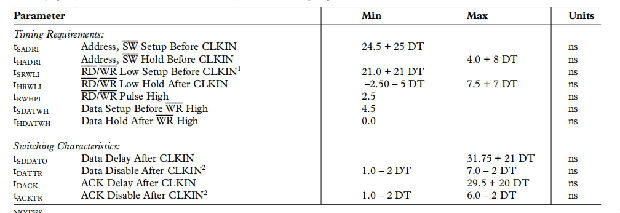

同步读写总线主机

使用这些规范连接到需要CLKIN相对定时的外部内存系统,或访问从ADSP-21065L(在多处理器内存空间中)。这些同步切换特性在异步内存读写期间也有效(请参阅内存读总线主控和内存写总线主控)。

当访问从ADSP-21065L时,这些开关特性必须满足从机同步读/写的时序要求(参见同步读/写总线从机)。从ADSP-21065L还必须满足数据和确认设置和保持时间的(总线主)定时要求。

W=(等待寄存器中指定的等待状态数)×tCK。

笔记:1、数据保持:用户必须满足tHDA或tHDRH或同步规范tHDATI。有关给定电容性和直流负载的保持时间计算,请参阅测试条件下的系统保持时间计算。在使用内部等待状态模式的外部存储器访问上未对。2、ACK进行采样。对于新外部存储器访问的第一个CLKIN周期,ACK必须通过tDAAK或tDSAK或同步规范tSACKC对外部等待状态模式或两者(如果内部等待状态为零,则两者)有效。对于等待状态的外部存储器访问的第二个循环和随后的循环,必须满足外部等待状态模式的同步规范t SACKC和tHACKC,或者两者都满足(在内部等待状态完成后)。3、有关给定电容和直流负载的保持时间计算,请参阅测试条件下的系统保持时间计算。

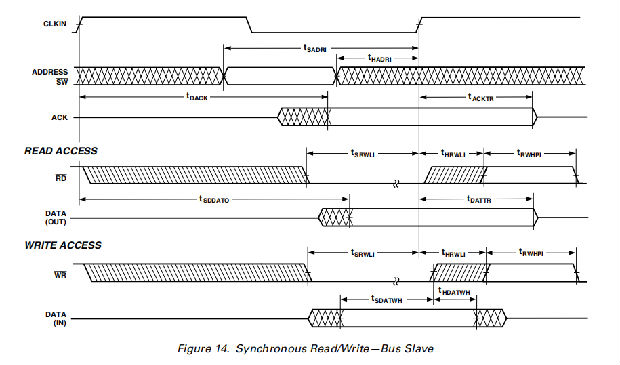

同步读写总线从机

对于从机IOP寄存器或内部存储器(在多处理器内存空间中)的ADSP-21065L总线主访问,请使用这些规范。总线主设备必须满足这些(总线从设备)定时要求。

笔记:1、当多处理器内存空间等待状态(等待寄存器中的MMSWS位)被禁用时,指定tSRWLI;当MMSWS被启用时,tSRWLI(min)=17.5+18 DT。2、有关给定电容和直流负载的保持时间计算,请参阅测试条件下的系统保持时间计算。

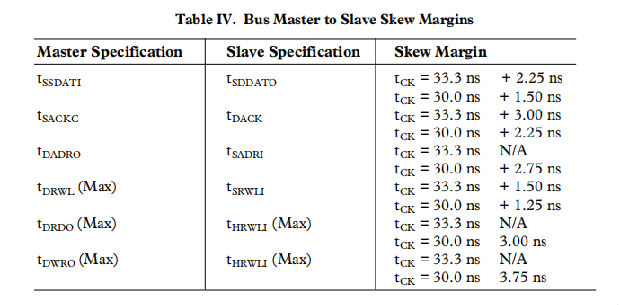

要使两个ADSP-21065Ls作为主从机同步通信,必须满足一定的主从机规格组合。不要直接比较规格值来计算下列规格的主/从时钟偏差。下表显示了适当的时钟偏移边距。

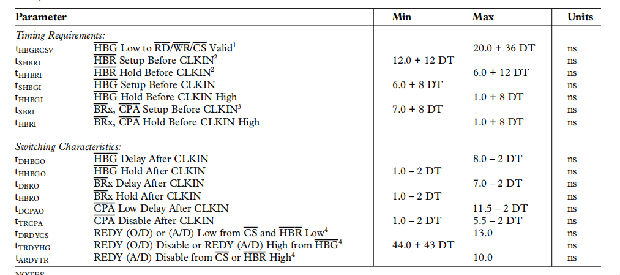

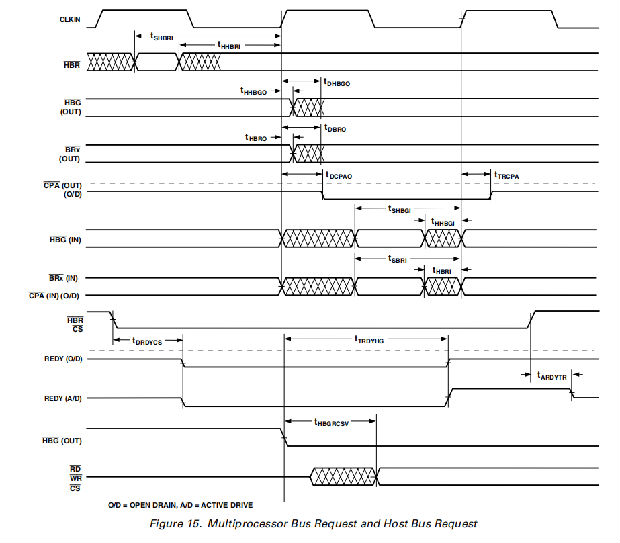

多处理器总线请求和主机总线请求

使用这些规范在多处理ADSP-21065Ls(BRx)或主机处理器(HBR,HBG)。

笔记:1、对于断言了HBR和CS之后的第一个异步访问,ADDR23-0在RD或WR变低之前必须是非ms值1/2 tCK,在HBG变低之后必须是tHBGRCSV低。当HBG被断言时,通过驱动高地址信号很容易实现这一点。请参阅ADSP-21065L SHARC用户手册,第二版。2、仅在当前周期中需要识别。3、CPA断言必须满足CLKIN的设置;deassertion不需要满足CLKIN的设置。4、(O/D)=漏极开路,(A/D)=主动驱动。

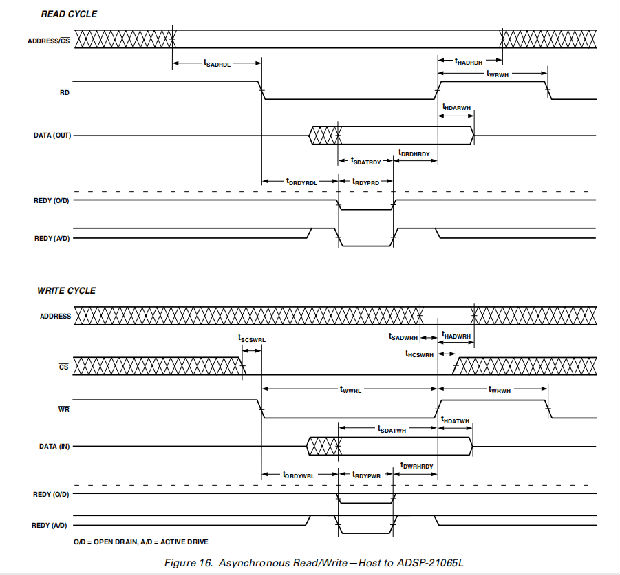

异步读写主机到ADSP-21065L

在主机断言CS和HBR(低)之后,对ADSP-21065L的异步主机处理器访问使用这些规范。在ADSP-21065L返回HBG后,主机可以驱动RD和WR管脚来访问ADSP-21065L的IOP寄存器。HBR和HBG在这个时间点被假定为低。写入可以以(1/2)tCK的最小间隔发生。

注意:如果在HBG变低后RD和地址是有效的tHBGRCSV,则不需要。对于断言HBR之后的第一次访问,ADDR23-0必须是RD或WR变低之前的非最小值1/2 tCLK,或者是HBG变低之后的tHBGRCSV。当HBG被断言时,通过驱动高地址信号很容易实现这一点。请参阅ADSP-21065L SHARC用户手册第二版中的主机接口。

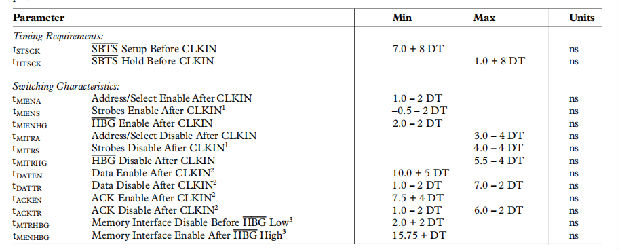

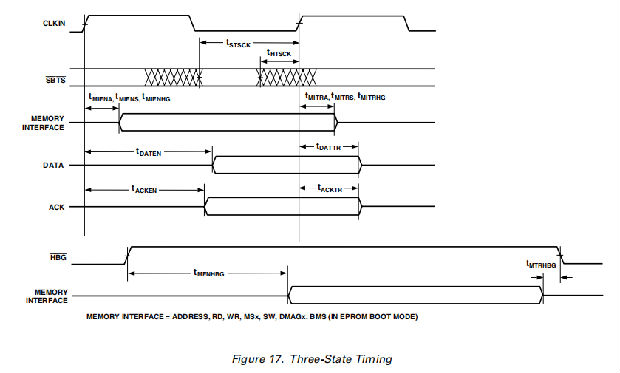

三态定时总线主、从、HBR、SBTS

这些规范显示了内存接口相对于CLKIN和SBTS管脚是如何被禁用(停止驱动)或启用(恢复驱动)的。此定时适用于总线主转换周期(BTC)和主机转换周期(HTC)以及SBTS管脚。

笔记:1、 频闪=RD,WR,SW,DMAG。2、 除了总线主转换周期外,这些规范还适用于总线主/从同步读/写。3、内存接口=地址、RD、WR、MSx、SW、DMAGx、BMS(在EPROM引导模式下)。

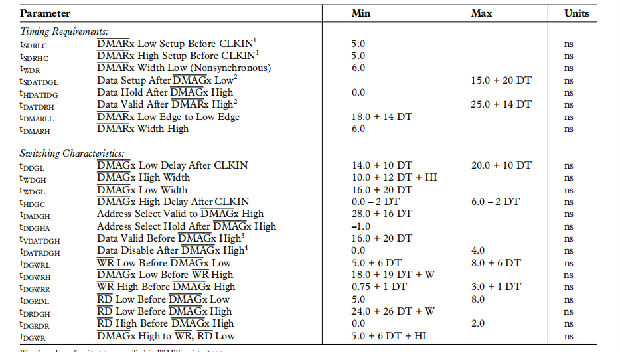

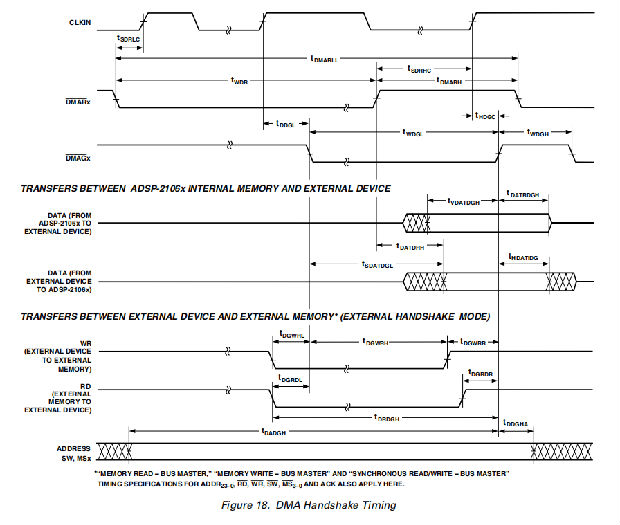

DMA握手

这些规范描述了三种DMA握手模式。在所有三种模式中,DMAR都用于启动传输。对于手摇模式,DMAG控制外部数据的锁定或启用。对于外部握手模式,控制数据传输通过ADDR23-0、RD、WR、SW、MS3-0、ACK和DMAG信号。外部模式不能用于带有SDRAM的传输。为了主模式,数据传输由ADDR23-0、RD、WR、MS3-0和ACK(非DMAG)控制。对于有节奏的主模式,存储器读总线主控、存储器写总线主控和同步读/写总线主控定时规范ADDR23-0、RD、WR、MS3-0、SW、DATA31-0和ACK也适用。

W=(等待寄存器中指定的等待状态数)×tCK。

HI=tCK(如果地址保持周期或总线空闲周期发生,如在等待寄存器中所指定;否则HI=0)。

笔记:1、 仅在当前周期中需要识别。2、 如果DMARx不用于延迟写入完成,则tSDATDGL是数据设置要求。否则,如果DMARx low延迟写入完成,则DMARx调高后可以驱动tDATDRH。3、 如果DMARx不用于延迟读取完成,则tVDATDGH有效。如果使用DMARx延长读取时间,则tVDATDGH=8+9 DT+(n×tCK),其中n等于访问被延长的额外周期数。4、 有关给定电容和直流负载的保持时间计算,请参阅测试条件下的系统保持时间计算。

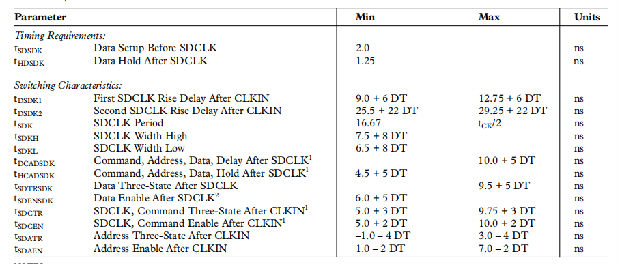

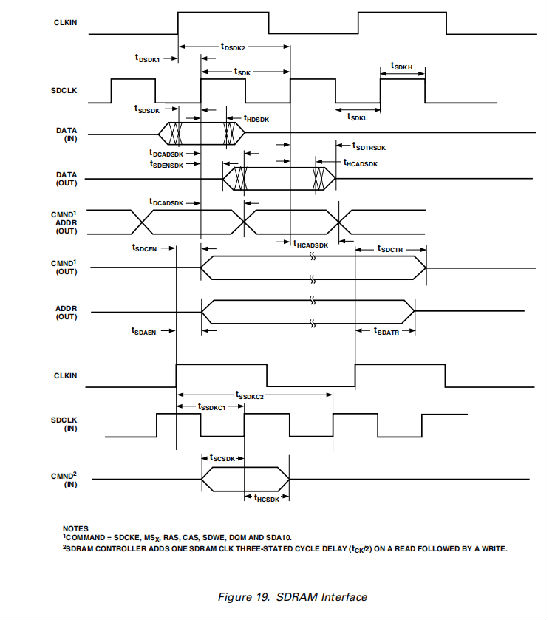

SDRAM接口总线主机

本规范适用于SDRAM的ADSP-21065L总线主访问。

笔记:1、命令=SDCKE、MSx、RAS、CAS、SDWE、DQM和SDA10。2、SDRAM控制器在读后加上一个SDRAM CLK三状态周期延迟(tCK/2)。

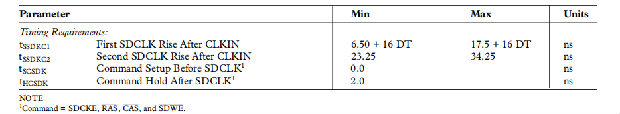

SDRAM接口总线从机

这些定时要求允许总线从机对总线主机的SDRAM命令进行采样,并在刷新发生时进行检测。

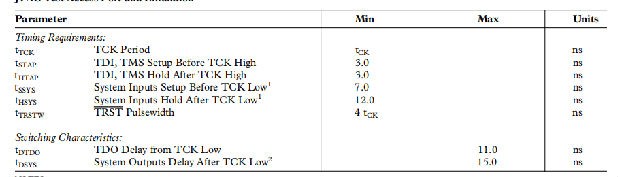

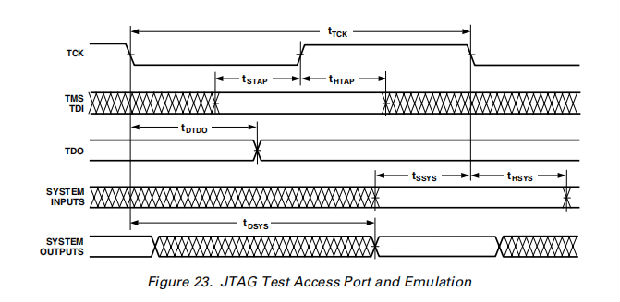

JTAG测试访问端口及仿真

笔记:1、系统输入=DATA31-0,ADDR23-0,RD,WR,ACK,SBTS,SW,HBR,HBG,CS,DMAR1,DMAR2,BR2-1,ID1-0,IRQ2-0,FLAG11-0,DR0x,DR1x,TCLK0,TCLK1,RCLK0,RCLK1,TFS0,TFS1,RFS0,RFS1,BSEL,BMS,CLKIN,RESET,SDCLK0,RAS,CAS,SDWE,SDCKE,PWM事件x。

2、系统输出=DATA31-0,ADDR23-0,MS3-0,RD,WR,ACK,SW,HBG,REDY,DMAG1,DMAG2,BR2-1,CPA,FLAG11-0,PWM事件x,dtx,DT1x,TCLK0,TCLK1,RCLK0,RCLK1,TFS0,TFS1,RFS0,RFS1,BMS,SDCLK0,SDCLK1,DQM,SDA10,RAS,CAS,SDWE,SDCKE,BM,XTAL。

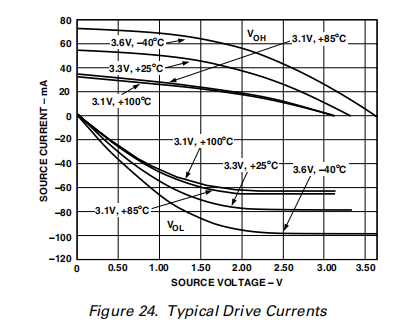

输出驱动电流

测试条件输出禁用时间

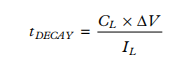

当输出引脚停止驱动,进入高阻抗状态,并开始从其输出的高或低电压衰减时,它们被认为是禁用的。母线上电压衰减∏V的时间取决于电容性负载CL和负载电流IL。此衰减时间可由以下方程式近似计算:

输出禁用时间tDIS是tMEASURED和tDECAY之间的差值,如图26所示。测量的时间t是从基准信号切换到输出电压从测量的输出高电压或输出低电压衰减∏V的时间间隔。tDECAY是用试验载荷CL和IL计算的,且∏V等于0.5 V。

输出启用时间

当输出管脚从高阻抗状态过渡到开始驱动时,输出管脚被认为是启用的。输出启用时间tENA是从参考信号达到高或低电压电平到输出达到指定的高或低跳闸点之间的间隔,如输出启用/禁用图所示。如果启用了多个管脚(如数据总线),则测量值为开始驱动的第一个管脚的测量值。

系统保持时间计算示例

要确定特定系统中的数据输出保持时间,首先使用上面给出的公式计算tDECAY。对于需要保持时间的设备,选择∏V作为ADSP-21065L输出电压和输入阈值之间的差。典型的∏V为0.4 V。CL为总线总电容(每根数据线),IL为总漏电或三态电流(每根数据线)。保持时间为tDECAY加上最小禁用时间(即,写入周期的tDATRWH)。

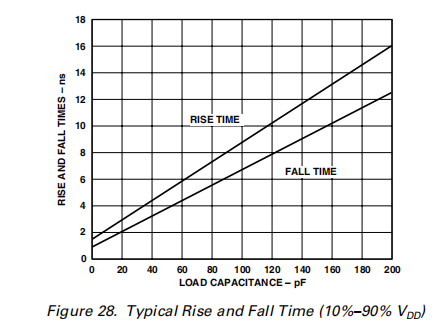

电容性负载

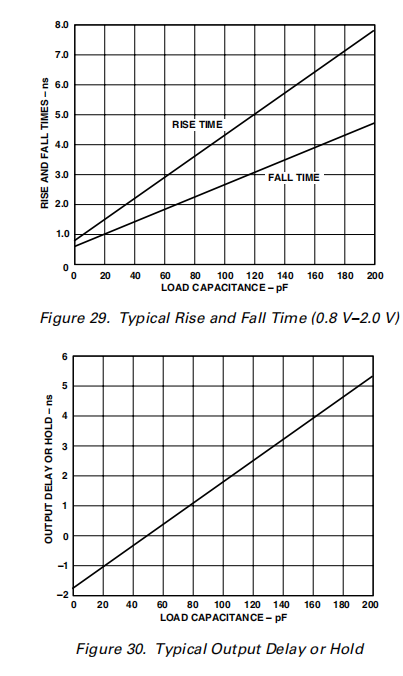

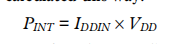

输出延迟和保持基于标准电容负载:所有管脚上50 pF。对于额定值50 pF以外的负载,给出的延迟和保持规范应降低1.8 ns/50 pF。图28和图29显示了输出上升时间如何随电容而变化。图30以图形方式显示了输出延迟和保持是如何随负载电容而变化的。(注意,此图或降额不适用于输出禁用延迟;请参阅上一节测试条件下的输出禁用时间。)图28、图29和图30的图在所示范围之外可能不是线性的。

功耗

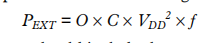

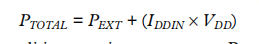

总功耗有两个部分:一个是由于内部电路,另一个是由于外部输出驱动器的切换。内部功耗取决于指令执行的顺序和所涉及的数据操作数。参见电气特性一节中的IDDIN计算。内部功耗的计算方法如下:

总功耗的外部分量是由输出引脚的切换引起的。其大小取决于:

–每个循环中切换的输出引脚数(O)

–引脚可切换的最大频率(f)–引脚的负载电容(C)–引脚的电压摆动(VDD)。

使用以下公式计算外部组件:

负载电容应包括处理器的封装电容(CIN)。频率f包括驱动负载升高然后再降低。在SDRAM突发模式下,地址和数据管脚可以以1/tCK的最大速率驱动高和低。

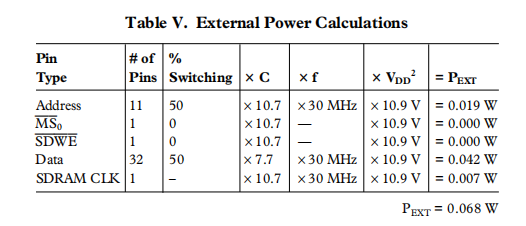

例子:根据以下假设估算PEXT:

–具有一组外部存储器(32位)的系统

–两个1米×16的SDRAM芯片,每个芯片的控制信号负载为3 pF,数据信号负载为4 pF

–外部数据写入以突发模式发生,每1/tCK周期两次,潜在频率为1/tCK周期/s。假设50%引脚切换

–外部SDRAM时钟频率为60 MHz(2/tCK)。

对于可以驱动的每一类管脚,都计算出了PEXT方程:

现在可以通过添加典型的内部功耗来计算这些条件下的典型功耗。(IDDIN见电气特性部分的计算):

请注意,导致最坏情况的PEXT的条件与导致最坏情况的PINT的条件不同。当100%的输出管脚从所有1(1s)切换到所有0(0s)时,不能出现最大管脚数。还要注意的是,应用程序同时切换100%甚至50%的输出并不常见。

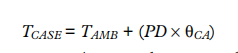

环境条件热特性

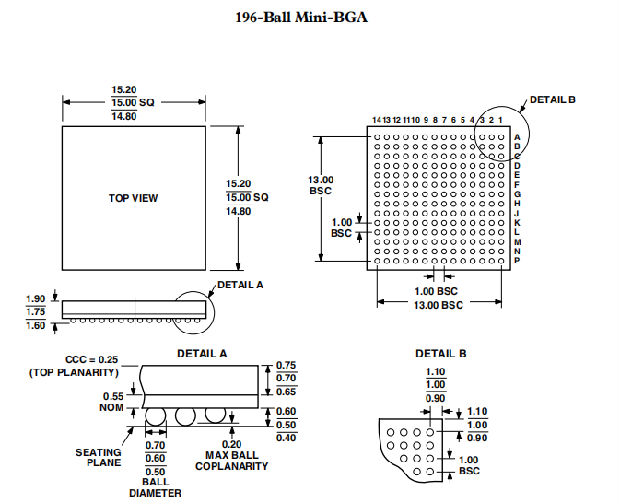

ADSP-21065L采用208铅MQFP和196球迷你BGA封装。

ADSP-21065L是为外壳温度(TCASE)指定的。为确保不超过TCASE,可使用气流源。

TCASE=外壳温度(在包装顶面测量)

PD=功耗(W)(该值取决于具体应用;计算局部放电的方法是显示在功耗下)

θJC=7.1°C/W,208引线MQFP

θJC=5.1°C/W,适用于196球迷你BGA

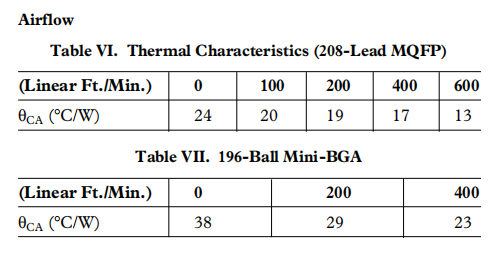

外形尺寸

尺寸单位为英寸和(mm)。

笔记:1、每根导线的实际位置与理想值的偏差在0.003(0.08)以内横向测量时的位置。

2、除非另有说明,中心图是典型的。

3、208铅MQFP是一个公制包。提供英文尺寸为近似值,不得用于电路板设计目的。

外形尺寸

尺寸单位为mm。

笔记:1、 球栅的实际位置相对于包装边缘。每个球的实际位置在其理想位置的0.10以内相对于球网格。

2、 因为这是一个公制包,所以所有测量都以公制单位提供。模拟设备强烈建议您使用公制测量值进行设计只有。

3、 钢球直径已从标称的0.50 mm改为0.60 mm,以符合与JEDEC标准出版物95箱轮廓图MO-151。0.60标称球DIAMETER产品将于2000年7月上市。