454点击型号即可查看芯片规格书

357点击型号即可查看芯片规格书

REF43点击型号即可查看芯片规格书

2048点击型号即可查看芯片规格书

特征

转换时间为1.6s的快速12位ADC;8个单端模拟输入通道每个通道上的过电压保护输入范围的选择:AD7891-1为5 V,10 V;0至+2.5 V,0至+5 V,AD7891-2为2.5 V;并行和串行接口;片上跟踪/保持放大器;片上参考;单电源,低功率运行(最大100兆瓦);断电模式(75 W典型)。

应用

数据采集系统;电动机控制;移动通信基站;仪表。

一般说明

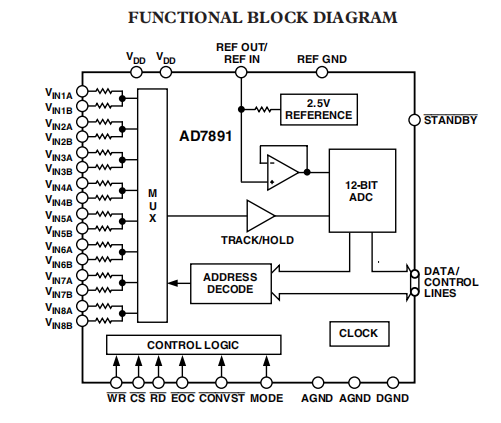

AD7891是一个8通道12位数据采集系统,可选择并行或串行接口结构。该部分包括输入多路复用器、片上跟踪/保持放大器、高速12位ADC、2.5v基准和高速接口。该部件由一个5 V电源供电,可在两种型号的AD7891-1(±5 V和±10 V)和AD7891-2(0 V至+2.5 V、0 V至+5 V和±2.5 V)上接受各种模拟输入范围。

AD7891提供由模式管脚决定的并行或串行接口结构选项。该部分具有标准的控制输入,串行和并行接口的数据访问时间都很快,确保了与现代微处理器、微控制器和数字信号处理器的轻松接口。

除了传统的直流精度指标,如线性、满标度和偏移误差外,该部分还规定了动态性能参数,包括谐波失真和信噪比。

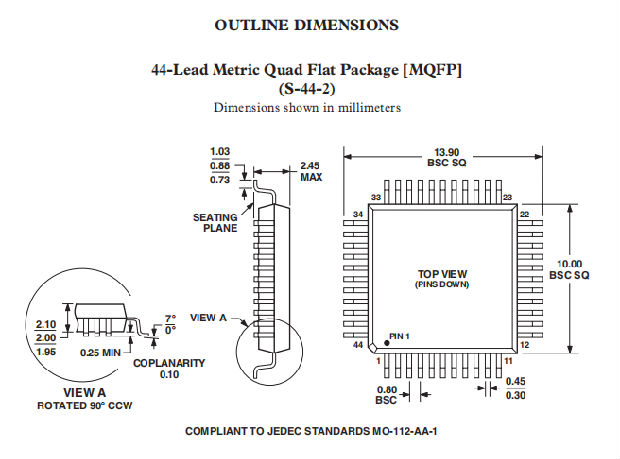

正常模式下的功耗为典型的82mw;备用模式下,功耗降低到典型的75mw。该部件可用于44端子MQFP和44引线PLCC。

产品亮点

1、AD7891是一个完整的单片12位数据采集系统,它将8通道多路复用器、12位ADC、2.5伏参考电压和跟踪/保持放大器集成在一个单片机上。

2、AD7891-2具有1.6 ms的转换时间和0.4 ms的采集时间。这允许采样率为当采样一个信道时为500 kSPS,当信道跳跃时为62.5 kSPS。这些采样率可以通过软件或硬件转换启动来实现。当使用硬件转换启动时,AD7891-1的采集时间为0.6 ms,当使用软件转换启动时,采集时间为0.7 ms。这些采集时间允许硬件和软件转换启动的采样率分别为454.5 kSPS和435 kSPS。

3、AD7891上的每个通道都有过电压保护。这意味着未选择通道上的过电压不会影响选定通道上的转换。AD7891-1可以承受±17 V的过电压。

术语

信噪比

这是在ADC输出端测得的信号与(噪声+失真)的比率。信号是基波的均方根振幅。噪声是所有非基本信号的均方根和,不超过采样频率(fS/2)的一半,直流除外。该比率取决于数字化过程中量化层级的数量;层级越多,量化噪声越小。具有正弦波输入的理想N位转换器的理论信噪比(噪声+失真)由信噪比(噪声+失真)=(6.02N+1.76)dB给出,因此,对于12位转换器,这是74 dB。

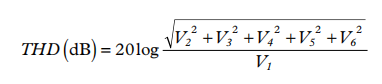

总谐波失真(THD)

THD是谐波的均方根和与基波的比值。对于AD7891,定义为:

其中V1是基波的均方根振幅,V2、V3、V4、V5和V6是第二次谐波至第六次谐波的均方根振幅。

峰值谐波或杂散噪声

峰值谐波或杂散噪声被定义为ADC输出频谱中下一个最大分量(最高fS/2,不包括dc)的均方根值与基波的均方根值之比。通常,本规范的值由频谱中最大的谐波确定,但对于谐波埋入噪声层的部分,它是噪声峰值。

互调失真

当输入由两个频率(fa和fb)的正弦波组成时,任何具有非线性的有源器件都会在mfa±nfb的和频和差频产生畸变产物,其中m,n=0,1,2,3,等等。互调项是指m和n都不等于零的互调项。例如,二阶术语包括(fa+fb)和(fa-fb),而三阶术语包括(2fa+fb),(2fa-fb),(fa+2fb)和(fa-2fb)。

AD7891使用CCIF标准进行测试,其中使用接近输入带宽顶端的两个输入频率。在这种情况下,二阶和三阶项具有不同的意义。二阶项通常在频率上与原始正弦波相距较远,而三阶项通常在接近输入频率的频率上。因此,二阶和三阶项是分别指定的。互调失真的计算是根据THD规范进行的,其中它是单个失真产品的rms和与以dBs表示的基波的rms振幅的比值。

通道间隔离

信道间隔离度是测量信道间串扰水平的一种方法。通过将满标度20 kHz(AD7891-1)或100 kHz(AD7891-2)正弦波信号应用于一个输入通道并确定该信号在其他每个通道中衰减的程度来测量。给出的数字是所有8个频道中最糟糕的情况。

相对精度

相对精度或端点非线性是通过ADC传递函数端点的直线的最大偏差。

微分非线性

这是ADC中任意两个相邻代码之间的测量值与理想1 LSB变化之间的差值。

正满标度误差(AD7891-1、10 V和5 V;AD7891-2、2.5 V)

这是最后一次代码转换的偏差(01。110至01号。111)调整双极零点误差后,从理想的4¥REF IN–3/2 LSB(AD7891-1±10 V范围)、2¥REF IN–3/2 LSB(AD7891-1±5 V范围)或REF IN–3/2 LSB(AD7891-2,±2.5 V范围)。

正满标度误差(AD7891-2,0 V至5 V和0 V至2.5 V)

这是最后一次代码转换的偏差(11。110到11。111)调整单极偏移误差后,从理想的2¥REF IN–3/2 LSB(0 V至5 V范围)或REF IN–3/2 LSB(0 V至2.5 V范围)。

双极零点误差(AD7891-1、10 V和5 V;AD7891-2、2.5 V)

这是中尺度转换(所有0到所有1)与理想AGND–1/2 LSB的偏差。

单极偏移误差(AD7891-2,0 V至5 V和0 V至2.5 V)

这是第一个代码转换的偏差(00。000到00。001)来自理想AGND+1/2 LSB。

负满标度误差(AD7891-1、10 V和5 V;AD7891-2、2.5 V)

这是第一个代码转换的偏差(10。000至10。001)调整双极零点误差后,从理想的-4¥REF IN+1/2 LSB(AD7891-1±10 V范围)、-2¥REF IN+1/2 LSB(AD7891-1±5 V范围)或-REF IN+1/2 LSB(AD7891-2,±2.5 V范围)。

跟踪/保持采集时间

跟踪/保持捕获时间是在转换结束后(跟踪/保持返回到跟踪模式的点)跟踪/保持放大器的输出达到其最终值(在±1/2 LSB范围内)所需的时间。它也适用于在所选输入通道中发生变化的情况,或者在应用于AD7891的所选VIN输入的输入电压上存在阶跃输入变化的情况。这意味着用户必须在转换结束后或在信道改变/阶跃输入改变为VIN后等待跟踪/保持采集时间的持续时间,然后才能开始另一个转换,以确保部件按规范运行。

转换器详细信息

AD7891是一个8通道、高速、12位数据采集系统。它为用户提供信号缩放、多路复用、跟踪/保持、基准、ADC以及高速并行和串行接口逻辑功能。AD7891-1上的信号调节允许部件在单电源工作时接受±5 V或±10 V的模拟输入范围。AD7891-2上的输入电路允许部件在从单个5 V电源操作时再次处理0 V至+2.5 V、0 V至+5 V和±2.5 V的输入信号范围。零件需要2.5 V的参考电压,可从零件自身的内部参考电压或外部参考电压源提供。

在AD7891上通过脉冲CONVST输入或通过将逻辑1写入控制寄存器的SWCONV位来启动转换。当使用硬件CONVST输入时,片上track/hold从track到hold模式,转换序列在CONVST信号的上升沿开始。当启动软件转换启动时,产生内部脉冲,延迟跟踪/保持采集点和转换启动序列,直到脉冲超时。每当向AD7891控制寄存器写入SWCONV位中的1时,就会启动该内部脉冲(从低到高)。然后开始放电,跟踪/保持不能进入保持,转换不能启动,直到脉冲信号变低。内部脉冲持续时间等于跟踪/保持采集时间。这允许用户在更改通道并在同一写入操作中启动转换后获得有效结果。

该部件的转换时钟是内部生成的,AD7891的转换时间距离硬件CONVST信号的上升沿1.6 ms。AD7891-1的跟踪/保持捕获时间为600 ns,而AD7891-2的跟踪/保持捕获时间为400 ns。为了从部件获得最佳性能,数据读取操作不应在转换期间或在下一次转换之前的100 ns期间发生。这使得AD7891-1能够以高达454.5 kSPS的吞吐率运行,而AD7891-2能够以高达500 kSPS的吞吐率在并行模式下运行,并实现数据表规范。在串行模式下,AD7891-1和AD7891-2的最大可实现吞吐量为357 kSPS(假设20 MHz串行时钟)。

所有未使用的模拟输入应连接到标称模拟输入范围内的电压,以避免噪声拾取。为了达到最小功耗,未使用的模拟输入应与AGND连接。

接口信息

AD7891提供两个接口选项,一个12位并行接口和一个高速串行接口。通过模式引脚选择所需的接口模式。这两种接口模式将在下面的章节中讨论。

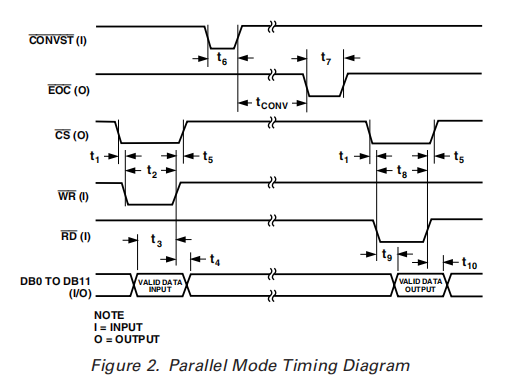

并行接口模式

并行接口模式是通过将模式输入绑定到逻辑高电平来选择的。图2示出了用于硬件转换开始的并行模式下AD7891的操作顺序的时序图。多路复用器地址被写入WR输入上升沿上的AD7891。片上磁道/保持在CONVST上升沿进入保持模式;此时也开始转换。当转换完成时,转换线(EOC)的末端低脉冲,以指示AD7891的输出寄存器中有新的数据可用。该EOC线可用于驱动微处理器的边缘触发中断。CS和RD变低访问12位转换结果。在该部分与栅极阵列或ASIC接口的系统中,该EOC脉冲可应用于CS和RD输入,以将数据从AD7891锁存到栅极阵列或ASIC中。这意味着栅极阵列或ASIC不需要任何转换状态识别逻辑,并且它还消除了栅极阵列或ASIC中生成AD7891的读取信号所需的逻辑。

串行接口模式

串行接口模式是通过将模式输入连接到逻辑低电平来选择的。在这种情况下,并行模式的五个数据/控制输入承担串行接口功能。

AD7891上的串行接口是具有读写功能的5线接口,数据通过数据输出线从输出寄存器读取,数据通过数据输入线写入控制寄存器。该部件在从机或外部时钟模式下工作,需要一个外部应用的串行时钟到SCLK输入,以访问数据寄存器中的数据或将数据写入控制寄存器。读(RFS)和写(TFS)操作有单独的帧信号。AD7891上的串行接口设计为允许部件连接到提供与串行数据同步的串行时钟的系统,例如80C51、87C51、68HC11和68HC05,以及大多数数字信号处理器。

在串行模式下使用AD7891时,数据线DB11至DB10应连接至逻辑低,CS、WR和RD输入应连接至逻辑高。引脚DB4到DB0可以绑定到逻辑高或逻辑低,但不能保持浮动,因为这种情况可能导致AD7891吸取大量电流。

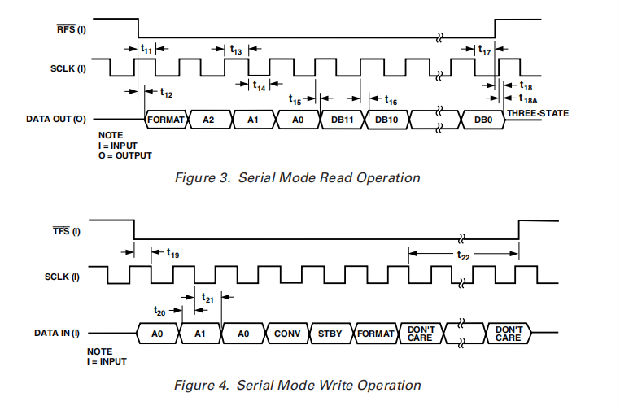

读取操作

图3显示了串行模式下从AD7891读取数据的时序图。RFS低到访问AD7891的数据。串行时钟输入不必是连续的。串行数据可以以字节数访问。但是,在数据传输操作期间,RFS必须保持较低。16位数据以串行模式传输,数据格式位在前,控制寄存器中的3个地址位在后,12位转换结果从MSB开始。串行数据在SCLK上升沿从设备中计时,在SCLK下降沿有效。在读取操作结束时,数据输出线由SCLK或RFS输入上的上升沿三个表示,以先发生的为准。

写操作

图4显示了对AD7891的控制寄存器的写操作。TFS输入变低,以指示将要发生串行写入的部分。AD7891控制寄存器只需要6位数据。它们加载在串行时钟的前六个时钟周期上,忽略所有后续时钟周期的数据。要写入AD7891的串行数据必须在SCLK的下降沿上有效。

简化串行接口

为了在串行模式下最小化到AD7891的互连线的数量,用户可以将AD7891的RFS和TFS线连接在一起,同时从部件读写。在这种情况下,应在数据输入线上提供选择输入通道并提供转换开始命令的新控制寄存器数据线,而该部分在数据输出线上提供刚刚完成的转换的结果。

电路描述参考

AD7891包含一个标号为REF OUT/REF的参考管脚,该管脚提供对零件自身2.5V内部参考电压的访问,或连接外部2.5V参考电压以提供零件的参考电压源。该部件规定为2.5 V参考电压。参考源中的错误会导致AD7891的传输函数中的增益错误,并添加到零件上指定的满标度错误中。它们还会导致注入衰减器级的偏移误差。

AD7891包含一个片上2.5伏参考电压。要将此参考用作AD7891的参考源,只需将0.1 mF的盘式陶瓷电容器从REF OUT/REF IN引脚连接到REF GND。REFGND应连接到AGND或模拟接地平面。出现在REF OUT/REF IN引脚上的电压在应用到ADC之前被内部缓冲。如果需要在AD7891外部使用该基准,则应对其进行缓冲,因为该部件有一个与该基准串联的FET开关,导致该输出的源阻抗为标称2千瓦。在25∞C时,内部参考的公差为±10 mV,典型温度系数为25 ppm/∞C,最大温度误差为±20 mV。

如果应用程序需要具有更严格公差的参考,或者如果AD7891需要与系统参考一起使用,则可以将外部参考连接到REF OUT/REF IN管脚。外部参考过度驱动内部参考,从而为ADC提供参考源。参考输入在应用到ADC之前被缓冲,最大输入电流为±100毫安。适用于AD7891的基准包括AD580、AD680、AD780和REF43精密2.5V基准。

模拟输入部分

AD7891分为两种类型:AD7891-1,每个输入可配置为±10 V或±5 V输入范围;AD7891-2,每个输入可配置为0 V至+2.5 V、0 V至+5 V和±2.5 V输入范围。

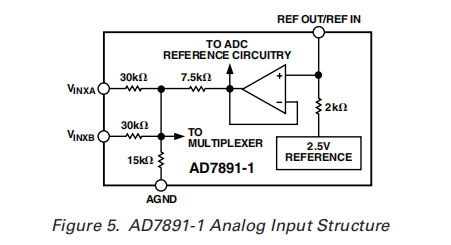

AD7891-1

图5显示了AD7891-1的模拟输入部分。每个输入可配置为±5 V或±10 V操作。对于5V操作,VINXA和VINXB输入连接在一起,输入电压同时施加在两者上。对于±10 V的操作,VINXB输入与AGND相连,输入电压施加到VINXA输入。VINXA和VINXB输入是对称的,完全可以互换。因此,为了便于在±10 V范围内进行PCB布局,当VINXA输入与AGND相连时,可以将输入电压施加到VINXB输入。

±5 V范围的输入电阻通常为20千瓦。对于±10 V输入范围,输入电阻通常为34.3千瓦。电阻输入级后接多路复用器,多路复用器后接轨道/保持放大器的高输入阻抗级。

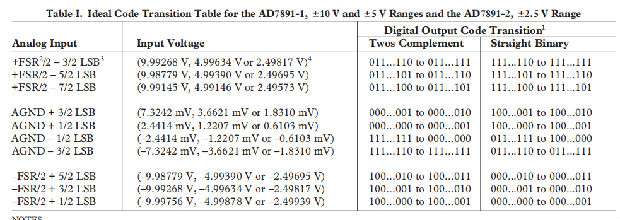

设计的代码转换发生在连续整数LSB值(即1/2 LSB、3/2 LSB、5/2 LSB)之间的中间。LSB大小由公式1给出,LSB=FS/4096。因此,对于±5 V范围,1 LSB=10 V/4096=2.44 mV。对于±10 V范围,1 LSB=20 V/4096=4.88 mV。输出编码由控制寄存器的格式位决定。理想的输入/输出代码转换如表1所示。

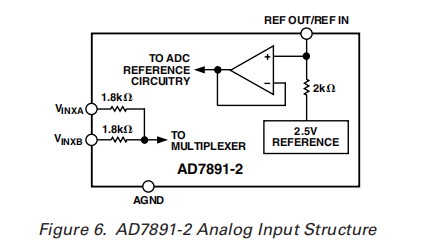

AD7891-2

图6显示了AD7891-2的模拟输入部分。每个输入可配置为0 V至+5 V、0 V至+2.5 V或±2.5 V的输入范围。对于0 V至5 V的输入范围,VINXB输入与AGND相连,输入电压施加到VINXA输入。对于0 V至2.5 V的输入范围,VINXA和VINXB输入连接在一起,输入电压同时施加在两者上。对于±2.5 V输入范围,VINXB输入与2.5 V相连,输入电压施加在VINXA输入上。2.5 V电源必须具有低输出阻抗。如果使用AD7891上的内部引用,则在应用到

VINXB。VINXA和VINXB输入是对称的,完全可以互换。因此,为了便于在0 V至+5 V或±2.5 V范围内进行PCB布局,可以将输入电压施加到VINXB输入,而VINXA输入与AGND或2.5 V相连。

0 V至+5 V和±2.5 V范围的输入电阻通常为3.6千瓦。当输入配置为0 V至2.5 V操作时,输入通过多路复用器和两个并联的1.8千瓦电阻器馈入轨道/保持放大器的高阻抗级。

设计的代码转换发生在连续整数LSB值(即1/2 LSB、3/2 LSB、5/2 LSB)之间的中间。LSB大小由公式1给出,LSB=FS/4096。因此,对于0 V至5 V范围,1 LSB=5 V/4096=1.22 mV;对于0 V至2.5 V范围,1 LSB=2.5 V/4096=0.61 mV;对于±2.5 V范围,1 LSB=5 V/4096=1.22 mV。输出编码由控制寄存器中的格式位决定。表一显示了±2.5 V范围内的理想输入/输出代码转换。表二显示了0 V至5 V范围和0 V至2.5 V范围内的理想输入/输出代码转换。

笔记

1、输出代码格式由控制寄存器中的格式位决定。

2、FSR是满标度范围,在±10 V范围内为+20 V,+10 V为±5 V范围,+5 V为±2.5 V范围,REF IN=+2.5 V。

3、LSB=FSR/4096=+4.88 mV(±10 V范围)、+2.44 mV(±5 V范围)和+1.22 mV(±2.5 V范围),参考电压=+2.5 V。

4、±0 V范围,±5 V范围,或±2.5 V范围。

笔记

1、输出代码格式由控制寄存器中的格式位决定。

2、FSR是满标度范围,0至5 V范围为5 V,0至2.5 V范围为2.5 V,REF IN=2.5 V。

3、LSB=FS/4096=1.22 mV(0至5 V范围)或610 mV(0至2.5 V范围),参考电压=2.5 V。

4、0 V至5 V范围或0 V至2.5 V范围。

AD7891-1和AD7891-2的传递函数

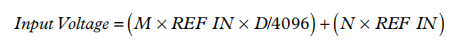

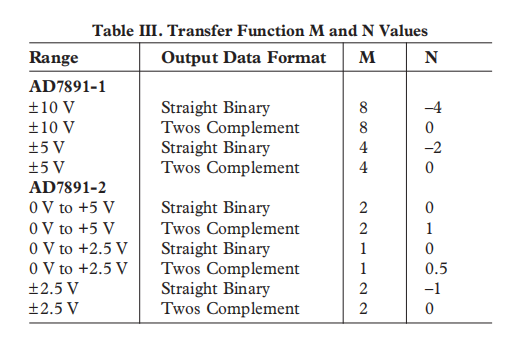

AD7891-1和AD7891-2的传递函数可以是表示为:

D是来自AD7891的输出数据,在0到4095表示直接二进制编码,从-2048到+2047表示两个补码。M的值取决于输入电压范围。N的值取决于输入电压范围和输出数据格式。这些值在表III.REF IN是应用于AD7891的参考电压。

跟踪/保持放大器

AD7891上的跟踪/保持放大器允许ADC将满标度振幅的输入正弦波精确转换为12位精度。即使在ADC的最大吞吐量为454khz(AD7891-1)或500khz(AD7891-2)时,跟踪/保持的输入带宽也大于ADC的奈奎斯特速率。换句话说,跟踪/保持放大器可以处理超过227 kHz(AD7891-1)或250 kHz(AD7891-2)的输入频率。

跟踪/保持放大器获取600 ns(AD7891-1)或400 ns(AD7891-2)的输入信号。跟踪/保持的操作对用户基本上是透明的。跟踪/保持放大器从其跟踪模式转到其在CONVST上升沿上的保持模式。跟踪/保持的光圈时间(即外部CONVST信号和实际进入保持的跟踪/保持之间的延迟)通常为15ns。转换结束时,零件返回其跟踪模式。此时航迹/等待开始获取下一个信号。

备用操作

AD7891可以通过使用备用引脚或控制寄存器的SWSTBY位进入省电或备用模式。当备用输入在逻辑1且SWSTBY位在逻辑0时,AD7891的正常操作发生。当备用pin变低或1写入SWSTBY位时,该部件进入备用操作模式,将其功耗降低到典型的75mw。

当备用物品输入在逻辑1,SWSTBY位是逻辑0。AD7891的唤醒时间通常由REF OUT/REF IN pin和REF GND之间0.1 mF电容器充电所需的时间量确定。如果内部基准用作基准源,则该电容器通过标称2千瓦电阻器充电。假设10个时间常数将电容器充电至12位精度,这意味着唤醒时间为2 ms。

如果使用外部参考,在计算电容器充电需要多长时间时,必须考虑到这一点。如果在AD7891处于待机模式期间,外部参考电压保持在2.5 V,则当部件脱离待机模式时,电容器将已经充电。因此,唤醒时间现在是AD7891的内部电路达到12位精度所需的时间。这通常需要5 ms。如果外部参考也被置于待机状态,则参考的唤醒时间,加上从外部参考对参考电容器充电所需的时间,确定在重新开始转换之前必须经过多少时间。

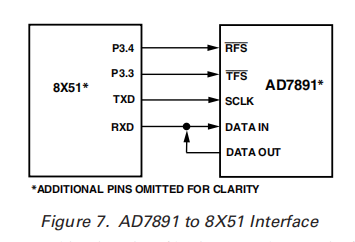

微处理器接口AD7891至8X51串行接口

AD7891和8X51微控制器之间的串行接口如图7所示。8X51的TXD驱动AD7891的SCLK,而RXD向和发送数据

从零件接收数据。与AD7891的最大串行时钟速度相比,8X51的串行时钟速度较慢,因此该接口无法实现AD7891的最大吞吐量。

8X51提供其SBUF寄存器的LSB作为串行数据流中的第一位。AD7891需要先写入6位的MSB。因此,必须正确排列SBUF寄存器中的数据,以便将其考虑在内。当数据被传送到部件时,P3.3被取低。8X51以8位字节传输其数据,在传输周期中仅出现8个下降的时钟边缘。将数据写入AD7891的控制寄存器需要一个8位传输。数据传输完成后,P3.3线将升高以完成传输。

从AD7891读取数据时,8X51的P3.4取低。8X51执行两个8位串行读取,并将P3.4设为高值以完成传输。同样,8X51首先需要LSB,而AD7891首先发送MSB,因此在8X51软件中必须考虑这一点。

在给定的接口中没有规定何时结束转换。如果转换是由软件启动的,则8X51可以在读取有效数据之前等待预定的时间量。或者,EOC信号的下降沿可用于启动中断服务例程,该例程从一部分读取到另一部分的转换结果。

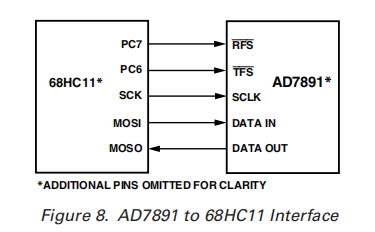

AD7891至68HC11串行接口

图8显示了AD7891和68HC11微控制器之间的串行接口。68HC11的SCK驱动AD7891的SCLK,MOSI输出驱动AD7891的数据输入,MISO输入从AD7891的数据接收数据。68HC11的端口PC6和PC7分别驱动AD7891的TFS和RFS线路。

为了正确操作该接口,68HC11的配置应使其CPOL位为1,CPHA位为0。当数据要传送到AD7891时,PC7被取低。当要从AD7891接收数据时,PC6被取低。68HC11首先以8位字节(MSB)传输和接收串行数据。AD7891还首先发送和接收数据MSB。在68HC11的读或写周期中出现八个下降的时钟边缘。在PC7低的情况下,需要一个8位写操作来写入控制寄存器。当数据被写入时,PC7被取高。从AD7891读取时,在读取前8位之后,PC6保持低位。然后,从AD7891串行地发送第二字节的数据。此传输完成后,PC6线路将处于高位。

如图7中的8X51电路所示,68HC11被告知转换完成的方式在图中未示出。EOC线可用于通知68HC11转换已完成,方法是将其用作中断信号。中断服务程序读取转换结果。如果使用软件转换启动,68HC11可以在读取AD7891之前等待2.0 ms(AD7891-2)或2.2 ms(AD7891-1)。

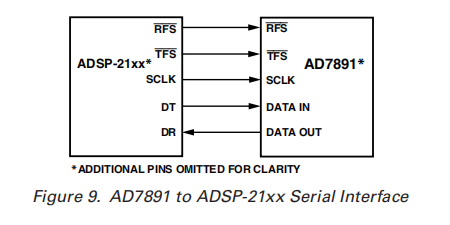

AD7891至ADSP-21xx串行接口

AD7891和ADSP-21xx之间的接口如图9所示。在显示的界面中,可以使用SPORT0或SPORT1将数据传输到AD7891。从部件中读取时,运动必须设置16位的串行字长度。当写入AD7891时,可以使用6位或更多的串行字长度。ADSP-21xx内部SCLK上串行接口的其他设置使用备用成帧模式和活动低成帧信号。通常,来自AD7891的EOC线将连接到a DSP-21xx的IRQ2线,以在转换结束时中断DSP(图中未示出)。

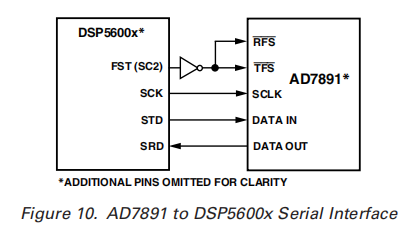

AD7891至DSP5600x串行接口

图10显示了AD7891和DSP5600x系列DSP。从AD7891读取数据时,DSP5600x应设置为16位数据传输、首先是MSB、正常模式同步操作、内部生成的字帧同步和门控时钟。当写入AD7891时,可以使用8位或16位数据传输。来自DSP5600x的帧同步信号在应用于AD7891的RFS和TFS输入之前必须反转,如图10所示。

为了监视AD7891的转换时间,可以使用诸如先前与EOC接口中概述的那些方案。这可以通过将EOC线直接连接到DSP5600x的IRQA输入来实现。

AD7891至TMS320xxx串行接口

AD7891可以连接到TMS320xxx DSPs的串行端口,如图11所示。外部定时生成电路是产生串行时钟和同步所必需的接口。

并行接口

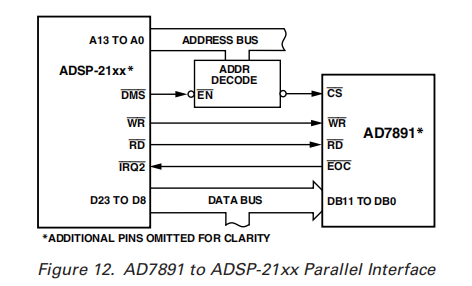

AD7891上的并行端口允许设备作为内存映射或I/O映射设备连接到微处理器或DSP处理器。CS和RD输入是所有存储器外设接口的公共输入。不同处理器的典型接口如图12至15所示。在所示的所有接口中,外部定时器控制AD7891的CONVST输入,EOC输出中断主机DSP。

AD7891至ADSP-21xx

图12显示了作为内存映射设备连接到ADSP-21xx系列DSP的AD7891。根据DSP的时钟速度,将AD7891接口到ADSP-21xx可能需要一个等待状态。此等待状态可通过ADSP-21xx的数据存储器等待状态控制寄存器进行编程(有关详细信息,请参阅ADSP-2100系列用户手册)。以下指令从AD7891读取数据。

MR = DM (ADC)

其中ADC是AD7891的地址。

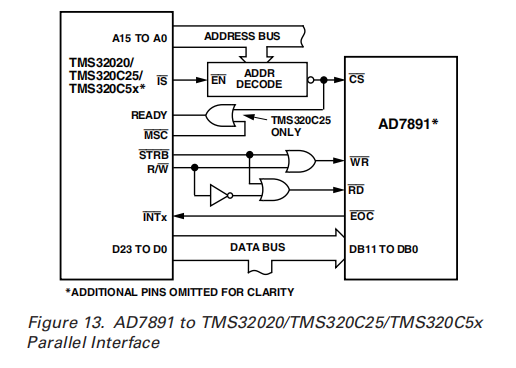

AD7891至TMS32020、TMS320C25和TMS320C5x

AD7891和TMS32020之间的并行接口,TMS320C25和TMS320C5x系列的dsp如图13。为AD7891选择的内存映射地址应落在DSP的I/O内存空间中。

并行接口

AD7891上的并行接口足够快,可以在没有额外等待状态的情况下与TMS32020接口。如果在与TMS320C25接口时使用高速粘合逻辑(如74AS设备)来驱动WR和RD线路,则无需等待状态。但是,如果使用较慢的逻辑,则在读取和写入部件时,数据访问可能会减慢到需要插入一个等待状态的程度。在这种情况下,该等待状态可以使用单或门来组合CS和MSC信号以驱动TMS320C25的就绪线路来生成,如图13所示。当以最快的时钟速度使用TMS320C5x时,需要额外的等待状态。等待状态可通过IOWSR和CWSR寄存器编程(有关详细信息,请参阅《TMS320C5x用户指南》)。

使用以下指令从ADC读取数据:在D,ADC,其中D是存储数据的存储器位置,ADC是AD7891的I/O地址。

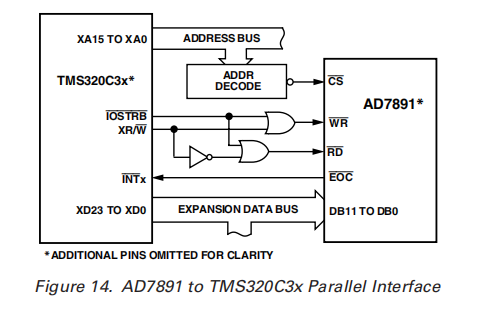

AD7891至TMS320C3x

图14显示了AD7891和TMS320C3x系列dsp之间的并行接口。AD7891接口到TMS320C3x的扩展总线。该接口需要一个单一的等待状态。这可以使用扩展总线控制寄存器的WTCNT位进行编程(有关详细信息,请参阅TMS320C3x用户指南)。可以使用以下指令读取来自AD7891的数据:本地设计院¥ ,ARn接收,其中ARn是包含TMS320C3x存储器空间中的AD7891地址的低16位的辅助寄存器,Rx是加载ADC数据的寄存器。

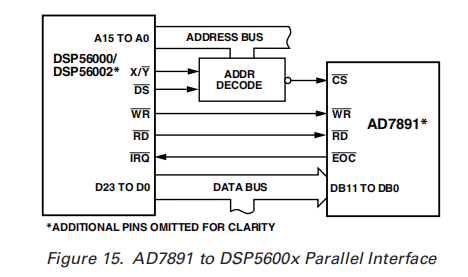

AD7891至DSP5600x

图15显示了AD7891和DSP5600x系列DSP之间的并行接口。AD7891应该映射到Y数据存储器的前64个位置。如果此接口需要额外的等待状态,可以使用端口A总线控制寄存器对其进行编程(有关详细信息,请参阅DSP5600x用户手册)。可使用以下指令从AD7891读取数据:移动:ADC,X0,其中ADC是DSP5600x地址空间中AD7891映射到的地址。

电源旁路及接地

在任何精度很重要的电路中,仔细考虑电源和接地回路布局有助于确保指定的性能。安装AD7891的印刷电路板的设计应使模拟和数字部分分开并限制在电路板的某些区域。这有助于使用易于分离的地平面。最小蚀刻技术通常对地平面最好,因为它提供了最好的屏蔽。数字和模拟地面只能在一个地方连接。如果AD7891是唯一需要AGND到DGND连接的设备,则接地平面应连接在AD7891的AGND和DGND管脚处。如果AD7891处于多个设备需要AGND到DGND连接的系统中,则仍应仅在一个点进行连接,即在尽可能靠近AD7891的位置建立星形接地点。

应避免设备下方的数字线路,因为这些耦合噪声会影响模具。模拟地面应允许在AD7891下运行,以避免噪声耦合。AD7891的电源线应使用尽可能大的轨迹,以提供低阻抗路径,并减少故障对电源线的影响。时钟之类的快速开关信号应该用数字接地屏蔽,以避免将噪声辐射到电路板的其他部分,并且决不能在模拟输入端附近运行。避免数字和模拟信号交叉。板的相对侧上的痕迹应彼此成直角。这减少了通过电路板的馈通效应。微带技术是目前为止最好的技术,但并不总是可能与双面板。在这种技术中,电路板的组件侧专用于接地平面,而信号线则放置在焊料侧。

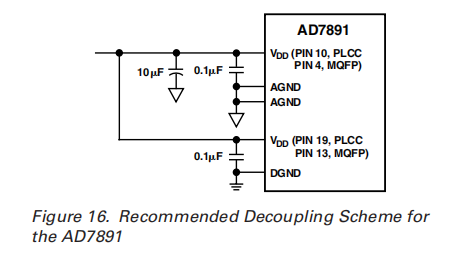

AD7891应该有足够的电源旁路,位置尽可能靠近封装,理想情况下正好靠在设备上。其中一个VDD引脚(PLCC封装的引脚10和MQFP封装的引脚4)主要驱动芯片上的模拟电路。该引脚应与模拟接地平面分离,并与一个10μf钽珠电容器并联,0.1μf电容器并联。另一个VDD管脚(PLCC包上的管脚19和MQFP包上的管脚13)主要驱动

芯片上的数字电路。该引脚应使用0.1 mF电容器与数字接地平面分离。0.1 mF电容器应具有低有效串联电阻(ESR)和有效串联电感(ESI),如普通陶瓷类型或表面贴装类型,它们在高频下提供低阻抗接地路径,以处理内部逻辑开关引起的瞬态电流。图16显示了推荐的解耦方案。

AD7891性能线性

AD7891的线性度主要由片上12位DAC决定。这是一个分段的DAC,它被激光修剪为12位积分线性和微分线性。AD7891的典型INL为±0.25 LSB,而典型DNL为±0.5 LSB。

噪声

在ADC中,噪声在直流应用中表现为码不确定性,在交流应用中表现为噪声下限(例如在FFT中)。在采样a dc(如AD7891)中,从dc到采样频率的一半,关于模拟输入的所有信息都出现在基带中。跟踪/保持放大器的输入带宽超过奈奎斯特带宽,因此,在存在此类信号的应用中,应使用抗混叠滤波器去除输入信号中fS/2以上的不需要信号。

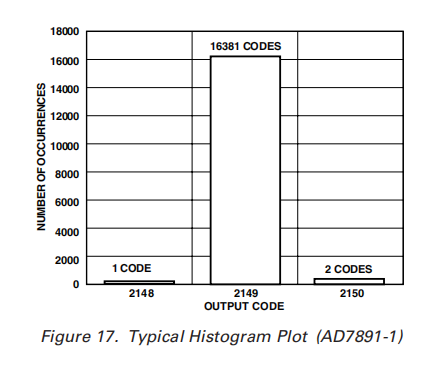

图17显示了使用AD7891-1对直流输入信号进行16384次转换的直方图。模拟输入按以下方式设置在代码转换的中心。选择了初始直流输入电平并进行了多次转换。记录得到的直方图并调整应用的级别,以便仅生成两个出现次数相等的代码。这表明已经找到了这两个代码之间的转换点。记录了发生这种情况的电压水平。这两个代码中的一个的另一个边以类似的方式被发现。然后,代码中心的dc电平可以计算为两个转换电平的平均值。AD7891-1输入配置为±5 V输入范围,转换后以并行模式从部件读取数据。在AD7891-1的±10 V范围和AD7891-2的所有输入范围内也发现了类似的结果。同样的性能是在串行模式下实现的,同样是在转换后从AD7891-1读取的数据。除了3个外,所有的代码都出现在一个输出箱中,这表明ADC具有良好的噪声性能。

动态性能

AD7891包含一个片上跟踪/保持放大器,允许该部分在其任何输入通道上采样高达250 kHz的输入信号。AD7891的许多应用要求它通过八个通道的低频输入信号进行排序。然而,对于某些应用,转换器在高达250 kHz输入频率的信号上的动态性能值得关注。对于这些较宽带宽的信号,建议采用硬件转换开始采样的方法。

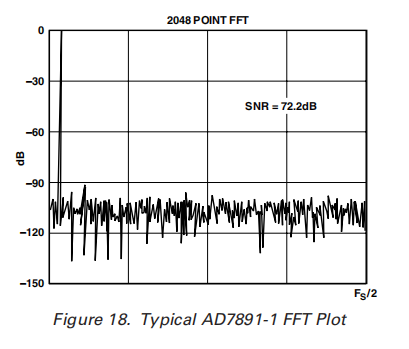

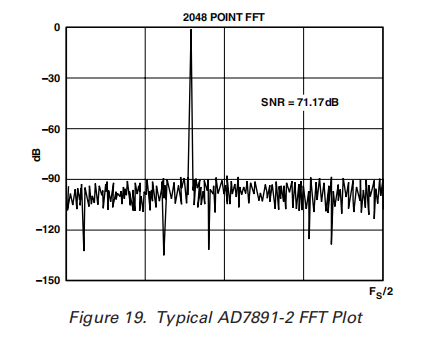

这些应用需要有关输入信号的光谱内容的信息。规定了信噪比(噪声+失真)、总谐波失真、峰值谐波或杂音以及互调失真。图18显示了一个典型的10 kHz,±10 V输入的FFT图,该图在AD7891-1在500 kHz下工作后被数字化,输入连接为±10 V操作。信噪比为72.2db,总谐波失真为-87db。图19显示了一个典型的100 kHz、0 V至5 V输入的FFT图,在AD7891-2以500 kHz的频率工作后,输入连接为0 V至5 V操作。信噪比为71.17db,总谐波失真为-82.3db。应该注意的是,在转换过程中读取零件的读数确实对动态性能有重大影响。因此,对于采样应用,建议在转换期间不要读取。

有效位数

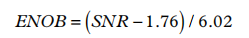

信噪比(噪声+失真)的公式(见术语部分)与转换器的分辨率或位数有关。重写公式给出了以有效位数(ENOB)表示的性能度量。

其中SNR是信噪比。

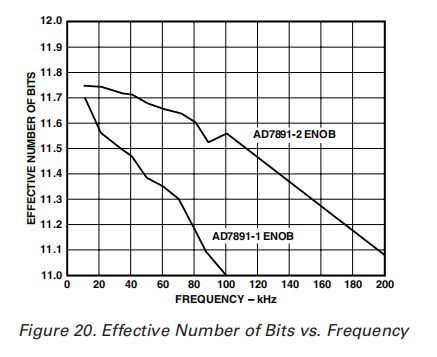

一个设备的有效比特数可以从其测量的信噪比计算出来。图20显示了AD7891-1和AD7891-2从直流到200 kHz的有效比特数与频率的典型关系图。采样频率为500khz。AD7891-1输入配置为±10 V操作。AD7891-2输入配置为0至5 V操作。AD7891-1曲线图只有100 kHz,因为在更高的频率下没有足够质量的±10 V正弦波。

图20显示AD7891-1将100 kHz的输入正弦波转换为11的有效比特数,相当于68.02 dBs的(噪声+失真)电平的信号。AD7891-2将200 kHz的输入正弦波转换为11.07的有效位数,相当于68.4 dBs的信号到(噪声+失真)电平。

外形尺寸

44铅塑料引线芯片载体(P-44A)

尺寸单位为英寸和(毫米)