AFE1105点击型号即可查看芯片规格书

750点击型号即可查看芯片规格书

特征

●完整的模拟接口;T1、E1和MDSL运行

●时钟可缩放速度

●单片解决方案

●仅+5V(5V或3.3V数字)

●250兆瓦功耗;48针SSOP

●运行温度为-40°C至+85°C

说明

Burr Brown的模拟前端通过提供连接Metalink MtH1210B HDSL数字信号处理器或外部折衷混合和1:2.3所需的所有有源模拟电路,大大降低了HDSL或MDSL系统的尺寸和成本HDSL线路变压器。所有内部筛选器响应为以及带有时钟的脉冲发生器输出刻度允许AFE1105在比特率范围从196kbps到1.168Mbps。

在功能上,这个单元被分成一个传输和接收部分。发送部分生成、过滤和缓冲输出的2B1Q数据。接收节过滤并数字化接收的符号数据打电话给MtH1210B。HDSL模拟接口是一个单片设备在0.6μCMOS上制造。它在一个+5V的电压下工作供应。它被封装在48针SSOP封装中。

典型性能曲线

脉冲变压器输出端

除非另有规定,通常在25°C时,AVDD=+5V,DVDD=+3.3V。

操作理论

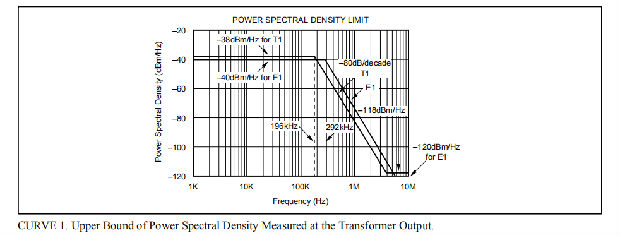

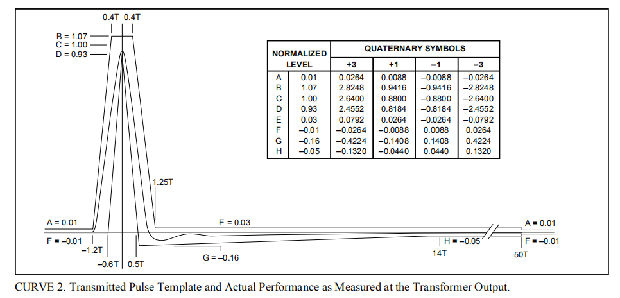

传输通道由开关电容脉冲形成网络和差分线路驱动器组成。脉冲形成网络从MtH1210B的XMTDA输出接收符号数据,并生成2B1Q输出波形。输出满足欧洲电信标准协会文件RTR/TM-03036中E1模式的脉冲屏蔽和功率谱密度要求,以及Bellcore技术咨询TA-NWT-001210中T1模式的第6.2.1和6.2.2.1节的要求。差分线路驱动器使用组合输出级,将B类操作(用于高效驱动大信号)与AB类操作(用于最小化交叉失真)相结合。

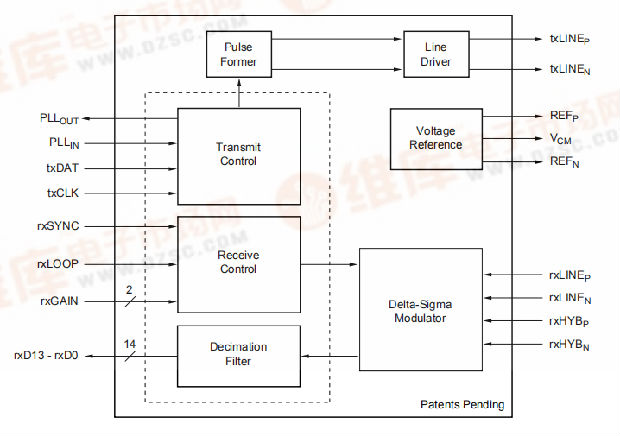

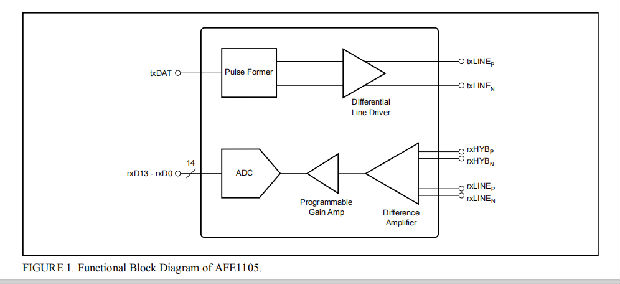

接收通道是围绕四阶delta-sigma a/D转换器设计的。它包括一个差分放大器,设计用于降低一阶模拟串扰的外部折衷混合。还包括增益为0dB至+9dB的可编程增益放大器。在24倍过采样率下工作的delta-sigma调制器在高达584kHz的输出速率下产生14位分辨率。AFE1105的基本功能如下图1所示。

接收信道通过将两个差分输入相加来工作,一个来自线路(rxLINE),另一个来自折衷混合(rxHYB)。在标题为“AFE中的回声消除”的段落中描述了这两个输入的连接,以便从线信号中减去混合信号。差分放大器中每个输入的等效增益为1。然后,产生的信号传递到可编程增益放大器,该放大器可设置为0dB到9dB的增益。ADC将信号转换为14位数字字rxD13-rxD0。

rxLOOP输入

rxLOOP是环回控制信号。启用时,rxLINEP和rxLINEN输入与AFE断开连接。rxHYBP和rxHYBN输入保持连接。通过向rxLOOP应用正信号(逻辑1)来启用环回。

AFE中的回声消除

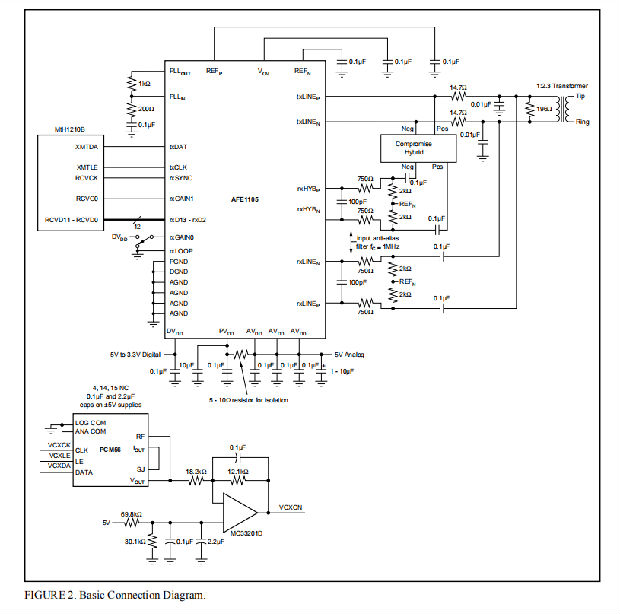

rxHYB输入被设计为从rxLINE输入中减去用于一阶回波消除。要实现这一点,请注意rxLINE输入连接到变压器上的相同极性信号(正到正和负到负),而rxHYB输入通过折衷混合(负到正和正到负)连接到相反极性,如图2所示。

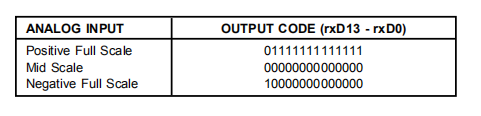

接收数据编码

来自接收通道A/D转换器的数据被编码为two的补码。

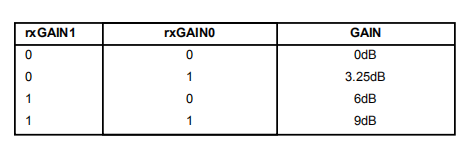

接收通道可编程

增益放大器

接收通道输入端放大器的增益由两个增益控制引脚rxGAIN1和rxGAIN0设置。这个结果在0dB和+9dB之间的增益如下所示。

rxHYBAND rxLINE输入抗锯齿滤波器

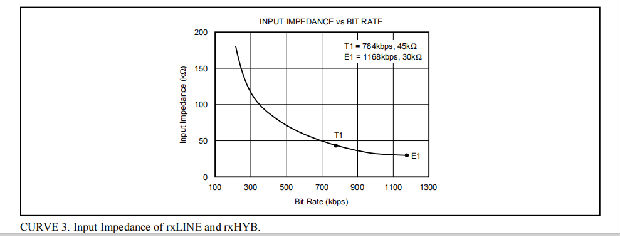

rxLINE和rxHYB差分输入的输入抗混叠滤波器的–3dB频率应大约为1MHz。两个输入电阻的滤波器建议值分别为750Ω和电容器的100 pF。两个750Ω电阻器和100pF电容器一起产生的–3dB频率略高于1MHz。750Ω输入电阻将使分压器损耗最小,输入阻抗为AFE1105。

此电路同时适用于T1和E1速率。对于较慢的速率,抗混叠滤波器将提供最佳性能,其-3dB频率约等于比特率。例如,500kHz的a–3dB频率应用于500kbps的单对比特率。

rxHYB和rxLINE输入偏置电压

txLINE管脚上的变送器输出集中在中刻度2.5V处。但是,在上图2中所示的电路中,rxLINE输入信号集中在1.5V处。

在AFE1105内部,如上文关于回声消除的段落所述,减去rxHYB和rxLINE信号。这意味着rxHYB输入需要以1.5V为中心,就像rxLINE信号以1.5V为中心一样。REFN(引脚36)是1.5V电压源。外部折衷混合电路的设计必须使rxHYB输入的信号集中在1.5V。

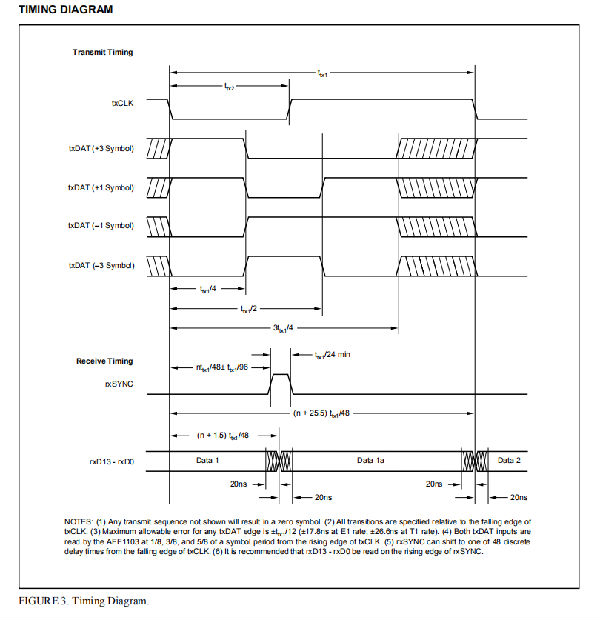

接收定时

rxSYNC信号控制A/D转换器抽取滤波器的部分和A/D转换器的数据输出定时。它由用户以符号速率生成,并且必须与txCLK同步。rxSYNC的上升沿可以出现在txCLK的下降沿处,或者可以由用户以符号周期的1/48的增量将其移动到txCLK下降沿之后的47个离散延迟时间中的一个。

A/D转换器抽取滤波器的带宽等于符号速率的一半。A/D转换器的数据输出速率是符号速率的2倍。AFE1105的规范假设每个符号周期使用一个A/D转换器输出,而忽略另一个插值输出。上面的接收时序图建议使用rxSYNC脉冲读取符号周期中的第一个数据输出。可以使用任一数据输出。这两种数据输出可用于更灵活的后处理。

规范讨论

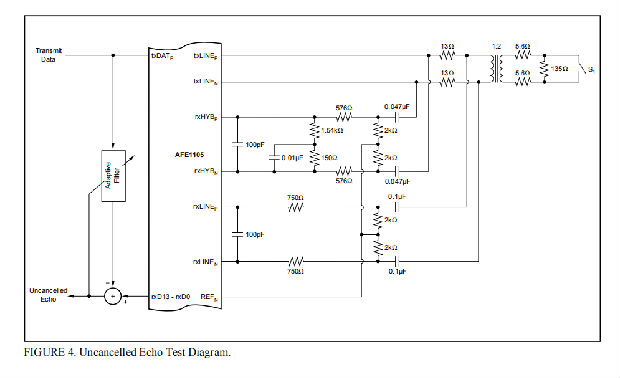

未消除回声

衡量收发机性能的关键是非抵消回波。如图4所示进行测量。AFE连接到一个输出电路,包括一个典型的1:2线路变压器。线路由135Ω电阻模拟。符号序列由测试仪生成并应用于AFE和自适应滤波器的输入。自适应滤波器的输出从AFE输出中减去,形成未消除的回波信号。一旦滤波器抽头收敛,将计算未消除回波的RMS值。由于不存在远端信号源或附加线噪声,因此未消除的回波仅包含在发射机和接收机中产生的噪声和线性误差。

未消除回波的数据表值是RMS未消除回波(指通过接收器增益输入的接收器)与标称传输信号(13.5dBm到135Ω或1.74Vrms)的比值。该回波值在多种条件下测量:启用环回(线路输入断开);在所有接收器增益范围内禁用环回;以及线路短路(图4中S1闭合)。

布局

HDSL系统的模拟前端有许多相互冲突的需求。它必须以相当高的速度接收和发送数字输出,将相位锁定到高速数字时钟,并将线路输入转换为高精度(14位)数字输出。因此,AFE1105实际上有三个部分:数字部分、锁相环和模拟部分。

AFE1105数字部分的电源电压范围为3.3V至5V。该电源应与数字接地分离,并在靠近DGND(引脚12)和DVDD(引脚13)的地方放置一个0.1μF的陶瓷电容器。理想情况下,数字电源平面和数字接地平面都应连接到AFE1105的数字管脚(管脚3到26)上下。然而,DVDD可以由宽的印刷电路板(PCB)轨迹提供。强烈建议在所有数字管脚下安装一个数字接地平面。

锁相环由PVDD(pin 2)供电,其接地参考PGND(pin 1)。注意,PVDD必须在4.75V到5.25V的范围内。AFE1105的这一部分应与两个10μF钽电容器分离以及0.1μF陶瓷电容器。陶瓷电容器应尽可能靠近AFE1105。钽电容器的放置并没有那么关键,但应该靠近。在每种情况下,电容器应连接在PVDD和PGND之间。

在大多数系统中,从AVDD供应中获得PVDD是很自然的。应使用5Ω至10Ω电阻器将PVDD连接至模拟电源。该电阻器与10μF电容器组合形成低通滤波器-防止AVDD上的故障影响PVDD。理想情况下,PVDD将源自印刷电路板电源连接器附近的模拟电源(通过电阻器)。同样地,PGND应该连接到一个大的PCB轨迹或小的接地平面,它返回到PVDD电源路径下的电源连接器。PGND“接地平面”也应延伸至PLLIN和PLLOUT(引脚47和48)下方。

AFE1105的其余部分应视为模拟。所有AGND引脚应直接连接到一个公共模拟接地平面,所有AVDD引脚应连接到一个模拟5V电源平面。这两个平面都应该有一个低阻抗的电源路径。

理想情况下,所有接地平面和迹线以及所有电源平面和迹线应在连接在一起之前(如有必要)返回到电源连接器。每个接地和电源线对应相互布线,不应重叠另一线对的任何部分,线对之间的距离应至少为0.25英寸(6mm)。一个例外是数字和模拟接地平面应该通过一个小的轨迹连接在AFE1105下面。