128点击型号即可查看芯片规格书

AD7376点击型号即可查看芯片规格书

特征

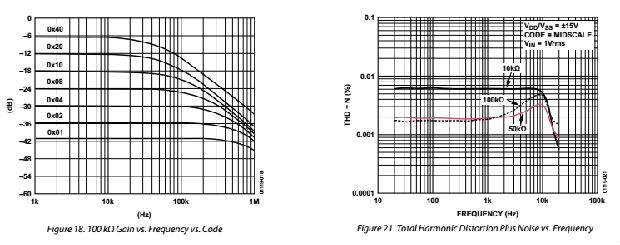

128个位置;10 kΩ, 50 kΩ, 100 kΩ;20 V至30 V单电源操作±10 V至±15 V双电源操作;3线SPI®兼容串行接口THD 0.006%典型可编程预设;断电:小于1微安;iCMOS™工艺技术。

应用

高压DAC;可编程电源;可编程增益和偏移调整;可编程滤波器,延迟;执行器控制;音频音量控制;机械电位计的更换。

一般说明

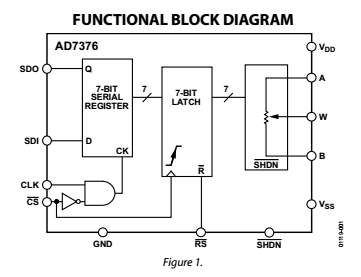

AD7376是市场上为数不多的高电压、高性能数字电位器2之一。该器件可用作可编程电阻或电阻分压器。AD7376具有与机械电位器、可变电阻器和微调器相同的电子调节功能,具有增强的分辨率、固态可靠性和可编程性。通过数字控制而不是手动控制,AD736提供了布局灵活性,并允许闭环动态可控性。

AD7376在关机时具有睡眠模式可编程性,可用于在设备激活前对预设进行编程,从而为昂贵的EEPROM解决方案提供替代方案。

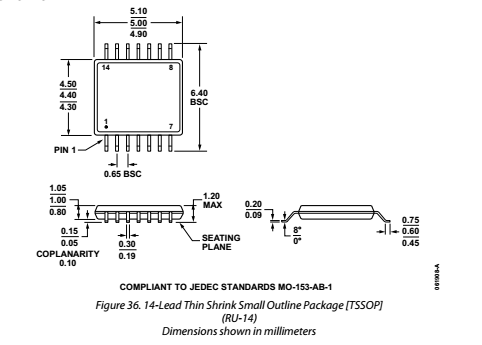

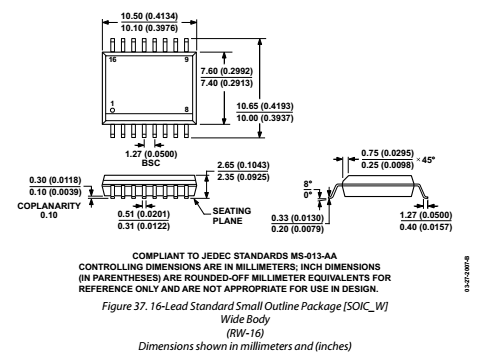

AD7376有14线TSSOP和16线宽体SOIC封装,可选10 kΩ、50 kΩ和100 kΩ。所有部件都保证在-40°C至+85°C的扩展工业温度范围内工作。

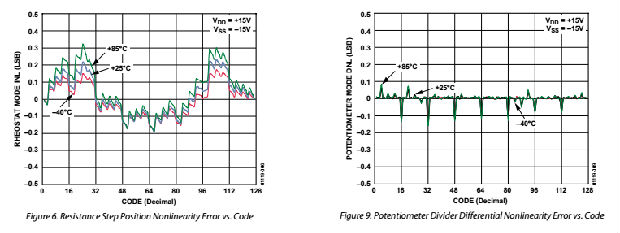

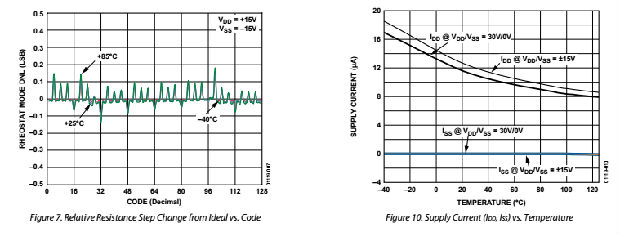

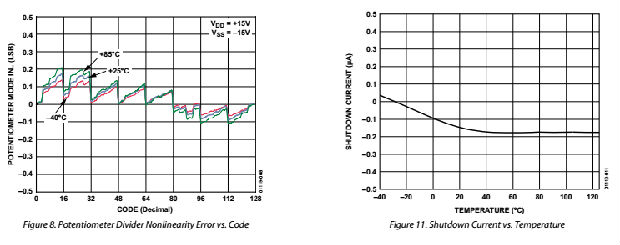

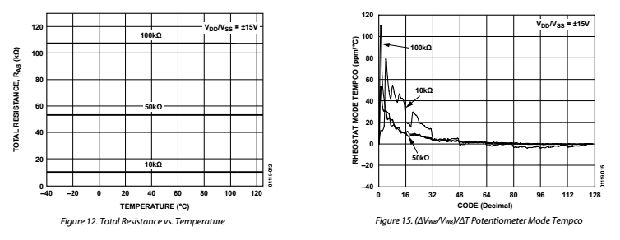

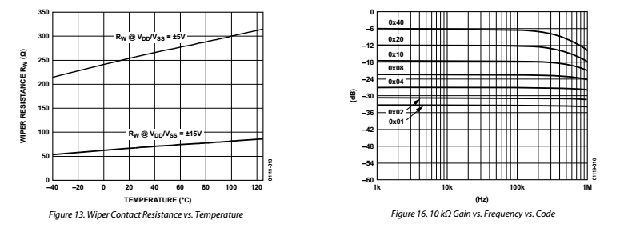

典型性能特征

操作理论

可变电阻编程

变阻器操作

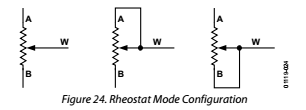

当只有两个端子用作可变电阻器时,该部件在变阻器模式下工作。未使用的终端可以保持浮动或绑定到W终端,如图24所示。

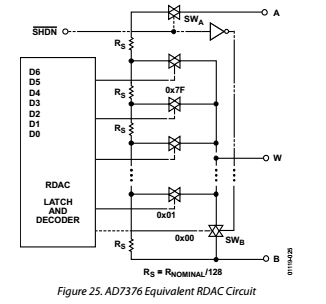

端子A和B之间的标称电阻RAB有10 kΩ、50 kΩ和100 kΩ,公差为±30%,并有128个分接点可通过雨刮器端子接入。对RDAC锁存器中的7位数据进行解码,以选择128个可能设置中的一个。图25显示了一个简化的RDAC结构。

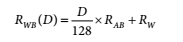

确定W和B端子之间的数字程控输出电阻的一般公式是:

其中:D是从0到127的7位RDAC寄存器中加载的二进制代码的十进制等效值。RAB是端到端的阻力。RW是由内部开关的导通电阻产生的雨刮器电阻。

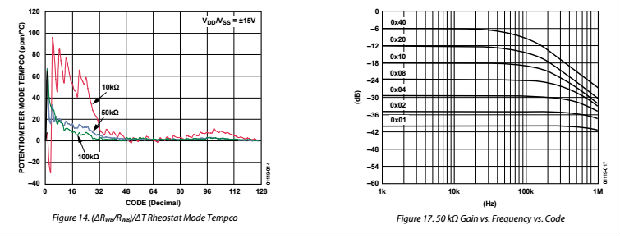

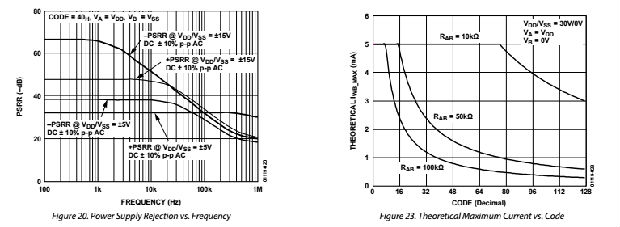

AD7376雨刮器开关采用传输门CMOS拓扑结构,门电压由VDD导出。每个开关的导通电阻RW是VDD和温度的函数(见图13)。与RAB的温度系数相反,雨刮器电阻的温度系数明显更高,因为雨刮器电阻每100°增加一倍。因此,用户必须考虑RW对期望阻力的贡献。另一方面,每个开关的导通电阻对抽头电位不敏感,在120Ω时保持相对平坦,在15 V的VDD和25°C的温度下是典型的。

假设使用10 kΩ部件,则雨刮器的第一个连接从编程代码0x00的B端子开始,其中SWB闭合。因此,端子W和B之间的最小电阻一般为120Ω。第二个连接是第一个抽头点,对应于198Ω(RWB=1/128×RAB+RW=78Ω+120Ω),用于编程代码0x01,依此类推。

每增加一个LSB数据值,雨刮器向上移动电阻梯,直到最后一个抽头点达到10042Ω(RAB–1 LSB+RW)。不管该部件工作于哪一个设置,都应该注意限制在A和B、W和A、W和B端子之间传导的电流到最大5毫安的直流电流和最大的20毫安的脉冲电流。否则,可能会导致内部开关触点退化或损坏。与机械电位器类似,W和A端子之间的RDAC的电阻也产生数字控制的互补电阻RWA。

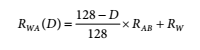

使用这些端子时,可以打开B端子。设置RWA的电阻值开始于电阻的最大值,并且随着加载到锁存器中的数据的值增加而减小。此操作的一般方程式为:

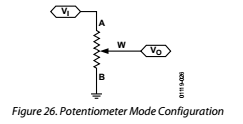

对电位计分压器编程

电压输出操作

数字电位器很容易在雨刮器W到端子B和雨刮器W到端子a处产生与端子a到端子B处的输入电压成比例的分压器。与VDD到接地的极性(必须为正)不同,在端子a到端子B、雨刮器W到端子a和雨刮器W到端子B之间的电压可以是极性。

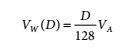

如果忽略擦拭器阻力的影响以达到近似目的,将端子A连接到30 V,将端子B连接到接地,在刮水器W到端子B处产生小于30 V的0 V到1 LSB的输出电压。每个LSB的电压等于施加在端子A和B上的电压除以电位计分压器的128个位置。对于施加在端子A和B上的任何有效输入电压,定义VW相对于接地的输出电压的一般方程式为:

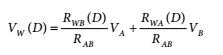

更精确的计算包括雨刮器阻力V的影响,

数字电位器在分压器模式下的操作会导致更精确的超温操作。与变阻器模式不同,分压器模式下的输出电压主要取决于内部电阻器RWA和RWB的比值,而不是绝对值。因此,温度漂移降低到5ppm/℃。

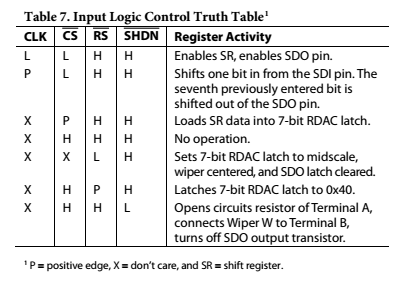

三线串行总线数字接口

AD7376包含一个3线数字接口(CS、CLK和SDI)。必须先加载7位串行字MSB。单词的格式如图2所示。正边缘敏感CLK输入需要干净的转换,以避免将不正确的数据计时到串行输入寄存器中。标准逻辑族工作良好。当CS低时,时钟将数据加载到每个正时钟边缘的串行寄存器中。

表3中的数据设置和保持时间确定了有效的计时要求。AD7376使用一个7位串行输入数据寄存器字,当CS线返回逻辑高电平时,该字被传输到内部RDAC寄存器。忽略多余的MSB位。

AD7376随机启动。但是,通过使用额外的I/O操作RS或SHDN,可以实现中刻度预设或任何理想的预设。

当复位(RS)引脚被断言时,雨刮器复位到中刻度值。如果使用额外的I/O,则可以动态或在通电期间实现中刻度重置。

当SHDN引脚被断言时,AD7376打开SWA,让端子A浮动,并使雨刮器W短接到端子B。在关机模式下,AD7376消耗的功率可以忽略不计,一旦SHDN引脚被释放,AD7376将恢复先前的设置。另一方面,AD7376可以在关机期间使用任何设置进行编程。由于在通电期间有一个额外的可编程I/O断言关闭,这个独特的功能允许AD7376在任何需要的水平上进行可编程预设。

表7显示了所有操作的逻辑真值表。

菊花链操作

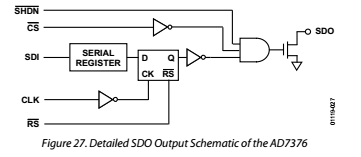

图27显示了串行数据输出引脚(SDO)的详细信息。SDO将前一帧中的SDI内容移出;因此,它可以用于菊花链多个设备。SDO引脚包含一个开漏N沟道MOSFET,如果使用SDO功能,则需要一个上拉电阻器。

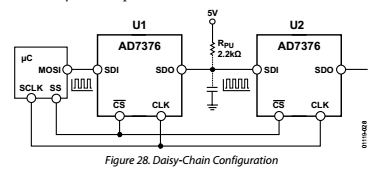

用户需要将一个包的SDO pin绑定到下一个包的SDI pin。例如,在图28中,如果两个AD7376是菊花链,则每次操作总共需要14位数据。第一组7位进入U2;第二组7位进入U1。在所有14位都进入各自的串行寄存器之前,CS应保持低电平。然后将CS拉高完成操作。

当菊花链连接多个设备时,用户可能需要增加时钟周期,因为上拉电阻和SDO到SDI接口处的电容性负载可能会导致后续设备的时间延迟。

ESD保护

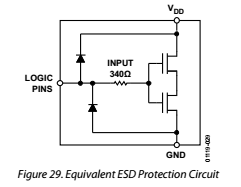

所有数字输入均采用串联输入电阻器和ESD结构进行保护,如图29所示。这些结构适用于数字输入管脚CS、CLK、SDI、RS和SHDN。

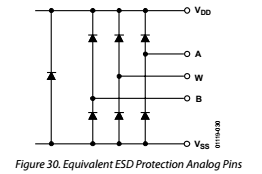

所有模拟终端也由ESD保护二极管保护,如图30所示。

终端电压工作范围

AD7376 VDD和VSS电源定义了正确3端数字电位器操作的边界条件。端子A、B和W上出现的比VDD更正或比VSS更负的外加信号将被内部正向偏置二极管钳制(见图30)。

上电和断电顺序

由于ESD保护二极管限制了端子A、B和W处的电压符合性(见图30),因此在向端子A、B和W施加电压之前给VDD/VSS通电是很重要的。否则,二极管会有正向偏压,从而导致VDD/VSS意外通电并影响系统。同样,VDD/VSS最后应该关机。理想的通电顺序如下:GND、VDD、VSS、数字输入和VA/VB/VW。VA、VB、VW和数字输入的供电顺序并不重要,只要它们是在VDD/VSS之后供电的。

布局和电源偏压

采用紧凑、最小引线长度的布局设计是一种良好的做法。通向输入端的导线应尽可能直接,最小导线长度。接地路径应具有低电阻和低电感。

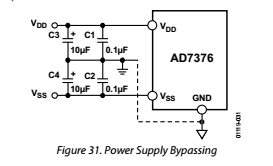

同样,用高质量的电容器旁路电源也是一个很好的做法。应在电源处使用低ESR(等效串联电阻)的1μF至10μF钽或电解电容器,以尽量减少瞬态干扰和滤除低频纹波。图31显示了AD7376的基本电源旁路配置。

AD7376的接地引脚是数字接地参考。为了将数字接地弹跳降至最低,AD7376数字接地端子应远程连接至模拟接地(见图31)。

应用程序信息

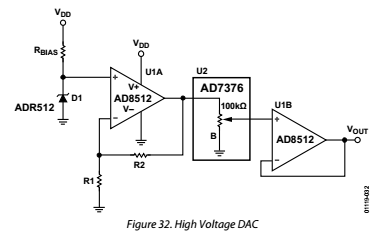

高压DAC

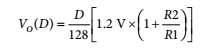

AD7376可以配置为高达30V的高压DAC。电路如图32所示。输出是:

其中D是0到127之间的十进制代码。

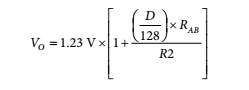

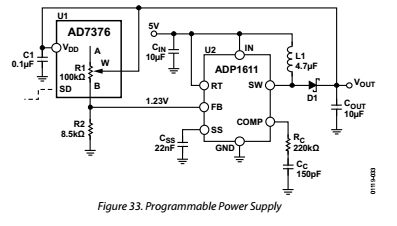

可编程电源

对于ADP1611这样的升压调节器,AD7376可以用作调节器FB引脚的可变电阻器,以提供可编程电源(见图33)。输出是:

注意,AD7376的VDD来自输出。最初,L1起短路作用,VDD是一个低于+5v的二极管电压降。输出缓慢地建立到最终值。

AD7376关机休眠模式编程可用于在通电时编程所需的预设电平。

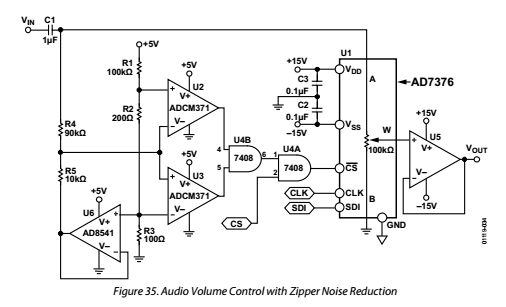

音频音量控制

AD7376具有良好的THD性能和高压性能,可用于数字音量控制。如果直接将AD7376用作音频衰减器或增益放大器,则在任意时间音量水平的大阶跃变化可导致音频信号的突然中断,从而产生可听见的拉链噪声。为了防止这种情况,可以将过零窗口检测器插入CS线,以延迟设备更新,直到音频信号穿过窗口。由于输入信号可以在任何直流电平而不是绝对零伏电平上工作,因此在这种情况下,过零意味着信号是交流耦合的,而直流偏移电平是信号零参考点。

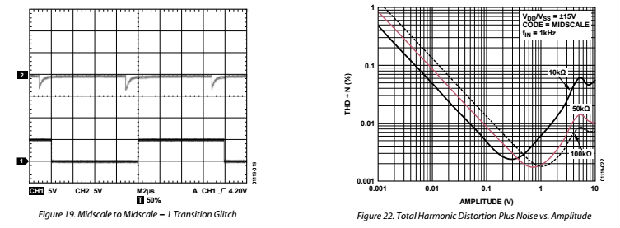

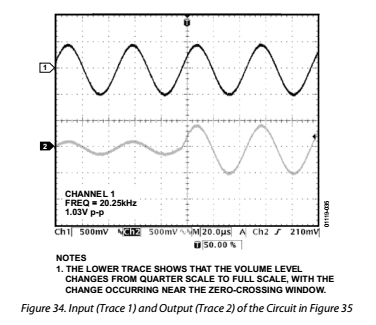

减少拉链噪声的配置和使用该配置的结果分别如图35和图34所示。输入由C1进行交流耦合并在输入由U2、U3和U4B形成的窗口比较器之前衰减。U6用于建立信号零参考。比较器的上限设置在其偏移量之上,因此,在本例中,每当输入在2.502 V和2.497 V(或0.005 V窗口)之间时,输出脉冲高。此输出与芯片选择信号一起使用,以便AD7376在信号穿过窗口时更新。为避免设备不断更新,芯片选择信号应编程为两个脉冲,而不是图2所示的脉冲。

在图34中,较低的记录道显示,当信号在过零窗口附近发生变化时,音量级别从四分之一刻度变为满刻度。

AD7376关机睡眠模式编程功能可用于通过保持SHDN低和编程零刻度在通电时使设备静音。

外形尺寸