115点击型号即可查看芯片规格书

256点击型号即可查看芯片规格书

AD7764点击型号即可查看芯片规格书

8192点击型号即可查看芯片规格书

特征

高性能24位∑-∏ADC;78 kHz输出数据速率下的115 dB动态范围;312kHz输出数据速率下109 dB动态范围;312千赫最大全滤波输出字速率;引脚可选择过采样率(64×、128×、256×);低功率模式;柔性SPI;全差分调制器输入;用于信号缓冲的片上差分放大器;片上参考缓冲器;全频带低通有限脉冲响应(FIR)滤波器;超量程报警引脚;数字增益校正寄存器;断电模式;通过SYNC pin同步多个设备;菊花链。

应用

数据采集系统;振动分析;仪表。

一般说明

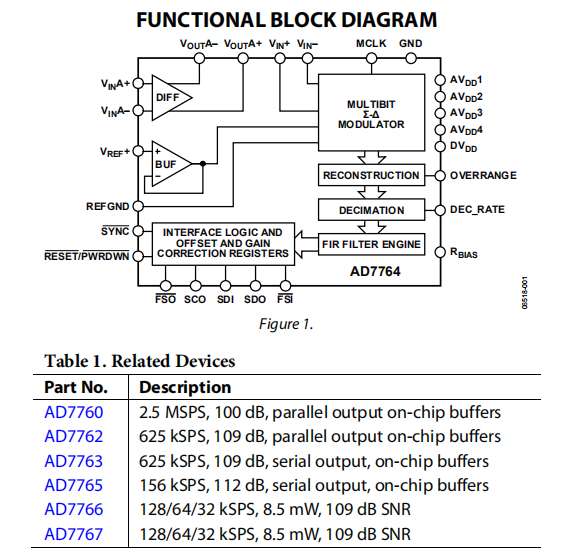

AD7764是一种高性能的24位sigma-delta(∑-Δ)模数转换器(ADC)。它结合了宽输入带宽、高速率和在312kHz输出数据速率下109dB动态范围的性能。该转换器具有优良的直流特性,非常适合于需要直流数据的交流信号的高速数据采集。

使用AD7764简化了前端抗混叠滤波要求,大大简化了设计过程。AD7764提供64×、128×、和256×。其他功能包括一个集成的缓冲器来驱动基准,以及一个全差分放大器来缓冲和电平移动调制器的输入。

当输入信号超出可接受范围时,超量程报警引脚会显示。内部增益和内部超量程寄存器的增加使AD7764成为一个紧凑的、高度集成的数据采集设备,只需要最少的外围组件。

AD7764还提供低功耗模式,在不降低输出数据速率或可用输入带宽的情况下显著降低功耗。

差分输入由模拟调制器以高达40 MSPS的速度采样。调制器输出由一系列低通滤波器处理。应用于AD7764的外部时钟频率确定采样率、滤波器角频率和输出字速率。

AD7764设备拥有一个全波段机载FIR滤波器。滤波器的全阻带衰减是在奈奎斯特频率下实现的。这一特性提供了更高的保护,防止高于奈奎斯特频率的信号被混叠回输入信号带宽。

提供给AD7764的参考电压决定输入范围。在4V参考电压下,模拟输入范围为±3.2768V差分,偏置在2.048V的共模附近。这种共模偏置可以使用片上差分放大器实现,进一步降低外部信号调节要求。

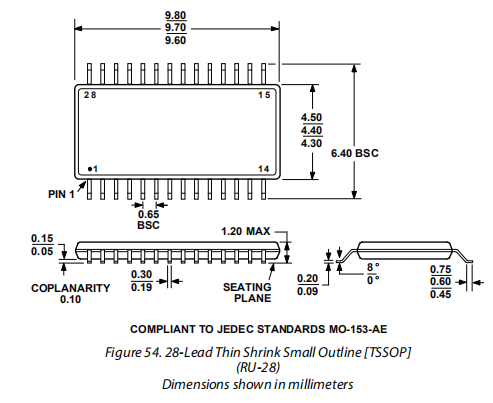

AD7764采用28铅TSSOP封装,并在工业温度范围内指定为-40°C至+85°C。

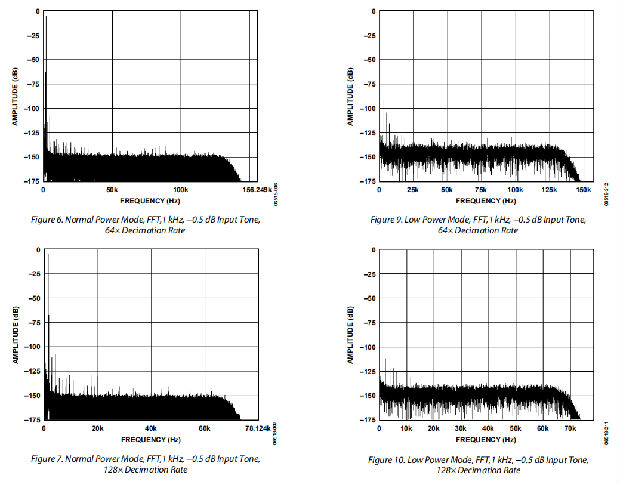

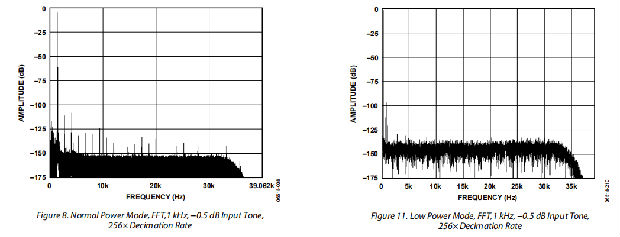

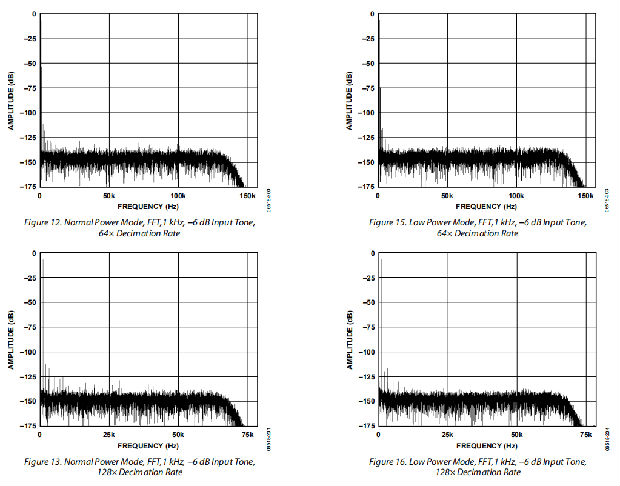

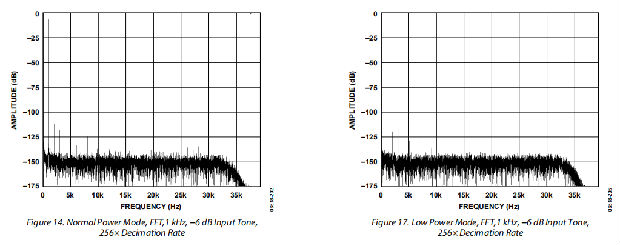

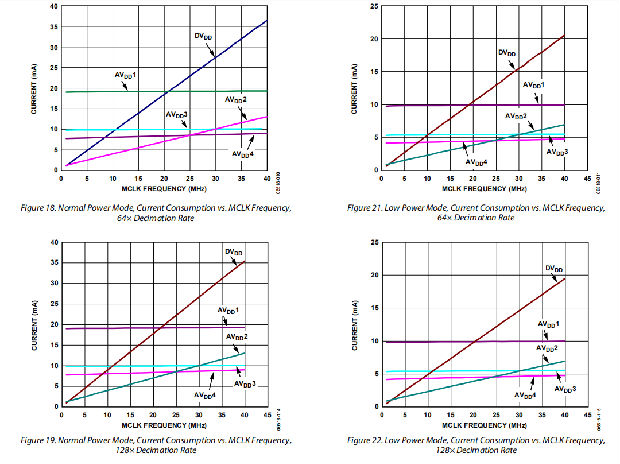

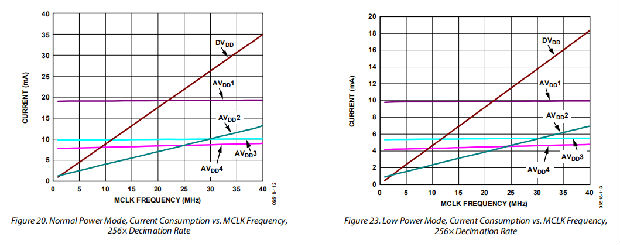

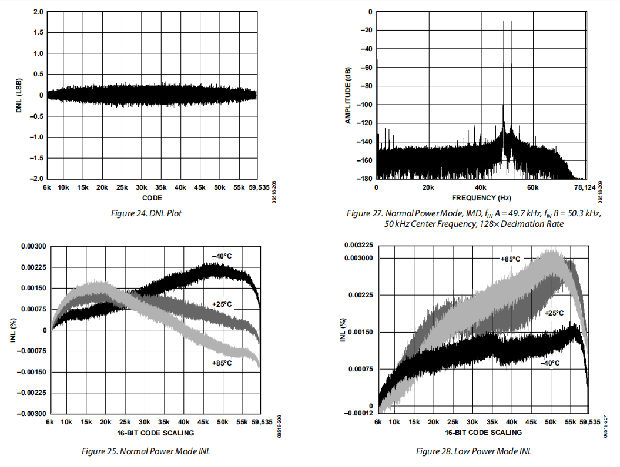

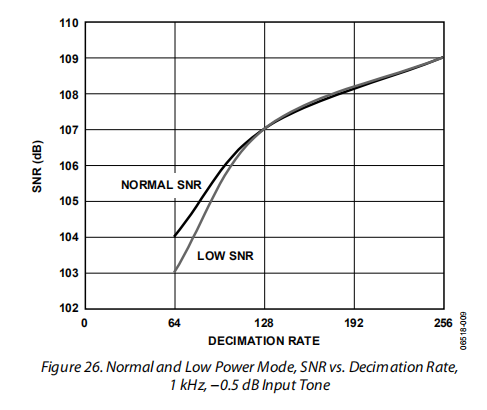

典型性能特征

AV1=DV=2.5V,AV2=AV3=AV4=5V,V+=4.096V,MCLK振幅=5V,T=25°C。测量到16位精度的线性曲线。减少输入信号以避免调制器过载和数字削波;在正常功率模式下,从262144个采样中生成-0.5db音调的快速傅里叶变换(FFTs)。所有其他fft都是从8192个样本生成的。

术语

信噪比

实际输入信号的均方根值与奈奎斯特频率以下所有其他谱分量的均方根和之比,不包括谐波和直流电。信噪比用分贝(dB)表示。

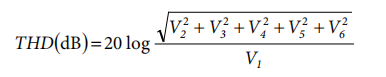

总谐波失真(THD)

谐波的均方根和与基波的比值。对于AD7764,定义为:

其中:V1是基波的均方根振幅。V2、V3、V4、V5和V6是第二个六次谐波。

非谐波无杂散动态范围(SFDR)均方根信号振幅与峰值杂散频谱分量均方根值之比,不包括谐波。

动态范围

满标度的均方根值与输入短路时测得的均方根噪声之比。动态范围的值以分贝表示。

互调失真

当输入由两个频率(fa和fb)的正弦波组成时,任何具有非线性的有源器件都会在mfa±nfb的和频和差频产生畸变产物,其中m,n=0,1,2,3,等等。互调失真项是指m和n都不等于0的项。例如,二阶项包括(fa+fb)和(fa-fb),而三阶项包括(2fa+fb),(2fa-fb),(fa+2fb)和(fa-2fb)。

AD7764使用CCIF标准进行测试,该标准使用接近输入带宽顶端的两个输入频率。在这种情况下,二阶项通常在频率上与原始正弦波相距,而三阶项通常在接近输入频率的频率上。因此,二阶和三阶术语是分别指定的。互调失真的计算是根据THD规范进行的,其中它是单个失真产品的rms和与以分贝表示的基本原理和的rms振幅的比值。

积分非线性(INL)

与通过ADC传递函数端点的直线的最大偏差。

微分非线性(DNL)

ADC中任意两个相邻码之间的测量值与理想1 LSB之间的差值发生变化。

零误差

理想中刻度输入电压(当两个输入短接在一起时)与产生中刻度输出代码的实际电压之间的差。

零误差漂移

由于温度变化1°C而引起的实际零误差值的变化。表示为室温下满量程的百分比。

增益误差

第一个转变(从100…000到100…001)应该发生在模拟电压1/2 LSB以上的标称负满标度。最后一次转换(从011…110到011…111)应该发生在低于额定满标度的模拟电压1 1/2 LSB的情况下。增益误差是最后一个跃迁的实际电平与第一个跃迁的实际电平之间的差与理想电平之间的差的偏差。

增益误差漂移

由于温度变化1°C而引起的实际增益误差值的变化。表示为室温下满量程的百分比。

操作理论

AD7764具有一个片上全差分放大器,用于馈送∑-Δ调制器管脚、一个片上参考缓冲器和一个FIR滤波器块,以执行∑-Δ调制器输出所需的数字滤波。使用这种∑-Δ转换技术,加上数字滤波,将模拟输入转换为等效数字字。

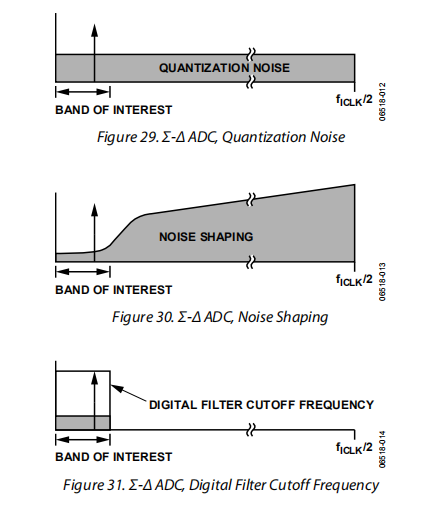

∑-Δ调制与数字滤波

对应用于调制器的输入波形进行采样,并以等于ICLK的速率将等效数字字输出到数字滤波器。通过采用过采样,量化噪声在0到f的宽带宽上传播。这意味着包含在感兴趣的信号频带中的噪声能量被降低(参见图29)。为了进一步降低量化噪声,采用高阶调制器来塑造噪声频谱,以便将大部分噪声能量移出信号频带(见图30)。

跟随调制器的数字滤波去除了较大的带外量化噪声(见图31),同时还根据所使用的抽取率,将滤波器输入处的数据速率从f降低到滤波器输出处的f/64或更低。

AD7764采用三个串联FIR滤波器。通过使用不同的抽取率组合,可以以三种数据速率从AD7764获得数据。

第一滤波器在ICLK MHz处从调制器接收数据,在ICLK MHz处抽取4×以输出(ICLK/4)MHz处的数据。第二个滤波器允许抽取率在8×到32×之间选择。

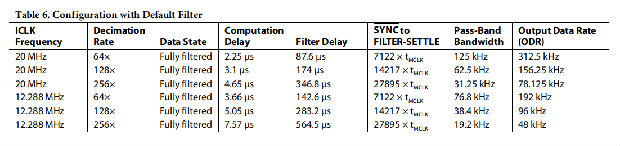

第三个滤波器的固定抽取率为2×。表6显示了数字滤波的一些特性,其中ICLK=MCLK/2。滤波器的群延迟定义为脉冲响应中心的延迟,等于计算量加上滤波器延迟。直到有效数据可用(滤波器设置状态位被设置)的延迟大约是滤波器延迟加上计算延迟的两倍。这在表6中列出了MCLK周期。

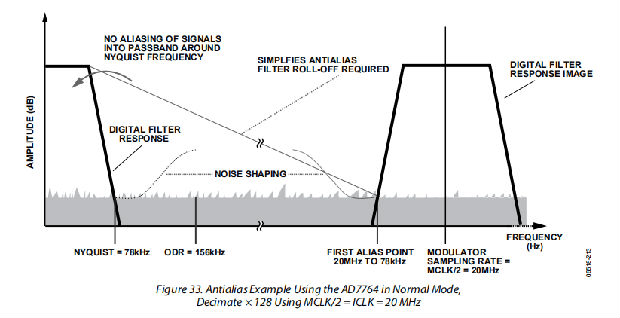

AD7764抗混叠保护

AD7764及其在AD776x家族中的对应产品(即AD7760、AD7762、AD7763和AD7765)的抽取提供了顶级抗锯齿保护。

AD7764的抽取滤波器在整个阻带上具有超过115分贝的衰减,其范围从奈奎斯特频率(即ODR/2)到ICLK–ODR/2(其中ODR是输出数据速率)。在Nyquist频率处启动停止频带可防止Nyquist以上的任何信号分量(以及直至ICLK–ODR/2)混叠到所需的信号带宽中。

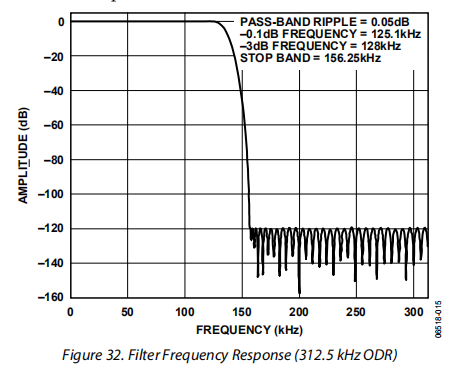

图32显示了当AD7764以40MHz MCLK以抽取×128模式工作时抽取滤波器的频率响应。注意,第一个停止带频率发生在奈奎斯特。滤波器的频率响应与抽取率的选择和MCLK频率的应用。采用低功耗模式时,调制器采样率为MCLK/4。以AD7764为例,在正常功率和十进制×128模式下,第一个可能的假频是ICLK频率减去数字滤波器的通带(见图33)。

AD7764输入结构

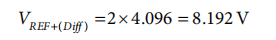

AD7764需要4.096 V输入到参考引脚,V+,由高精度基准提供,如ADR444。由于器件∑-Δ调制器的输入是全差分的,因此有效差分参考范围为8.192 V。

正如∑-Δ调制器所固有的,只有其中的一部分可使用完整参考。使用AD7764,80%的差分参考可以应用于调制器的差分输入:

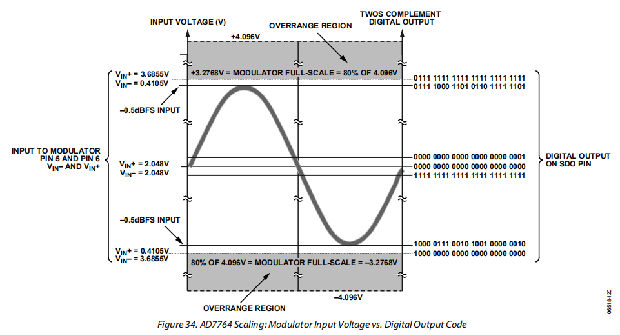

这意味着最大可±3.2768 V P P满刻度可以应用于AD77 64调制器输入(引脚5和引脚6)中的每一个,AD7764的输入比满标度低-0.5分贝(-0.5分贝)。AD7764调制器输入必须具有2.048 V的共模输入。

图34显示了施加到调制器管脚的差分电压和相应的24位双补数字输出之间的相对比例。

片上差分放大器

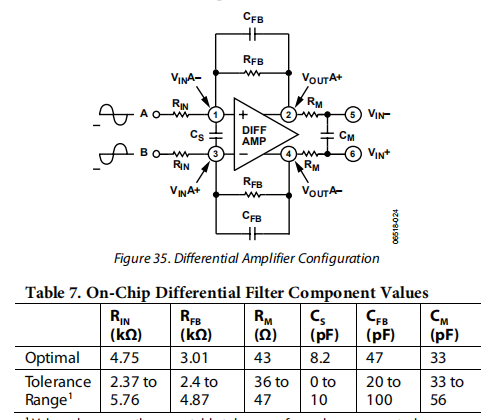

AD7764包含一个车载差分放大器,建议用于驱动调制器输入引脚。AD7764上的引脚1、引脚2、引脚3和引脚4是放大器的差分输入和输出引脚。外部组件R、R、C、C和R被放置在插脚1到插脚6的周围,以创建建议的配置。

为了达到指定的性能,差分放大器应配置为一阶抗混叠滤波器,如图35所示,使用表7中列出的分量值。然后,差分放大器的输入在应用到调制器输入V-和V+(针脚5和针脚6)之前通过外部元件网络进行布线。以表中的最佳值为例,在19.6mhz的第一个别名点处产生25db的衰减。

每个差分放大器输入端(触针VA+和触针VA-)的共模输入范围为-0.5 V dc到2.2 V dc。放大器的恒定输出共模电压为2.048 V,即V/2,调制器输入引脚所需的共模电压(V+和V-)。

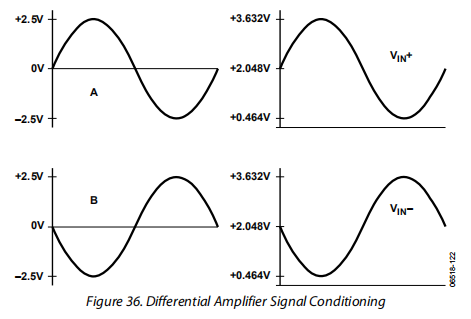

图36显示了使用表7中详述的差分放大器配置进行的信号调节,差分放大器的输入信号为±2.5V。本例中的放大器绕地偏置,并按比例缩放以提供每个2.048 V共模调制器输入上的±3.168 V p-p(–0.5 dBFS)。

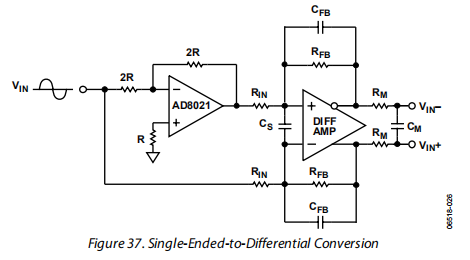

为了从AD77 64获得最大的性能,建议用差分信号驱动ADC。图37显示了一个双极,单端信号偏置在地面上,如何使用外部运算放大器驱动AD7764,如AD8021。

调制器输入结构

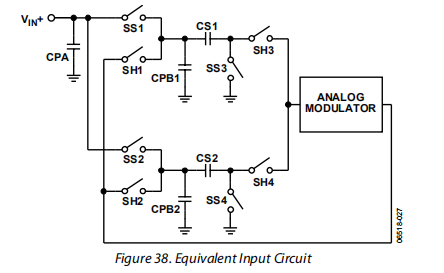

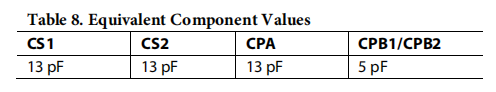

AD7764采用双采样前端,如图38所示。为简单起见,仅显示V+的等效输入电路。V-的等效电路相同。

SS1和SS3采样开关由ICLK驱动,而SS2和SS4采样开关由ICLK驱动。当ICLK高时,模拟输入电压连接到CS1。在ICLK的下降沿上,SS1和SS3开关打开,模拟输入在CS1上采样。类似地,当ICLK低时,模拟输入电压连接到CS2。在ICLK的上升沿,SS2和SS4开关打开,模拟输入在CS2上采样。

CPA、CPB1和CPB2电容器表示包括与MOS开关相关联的结电容的寄生电容。

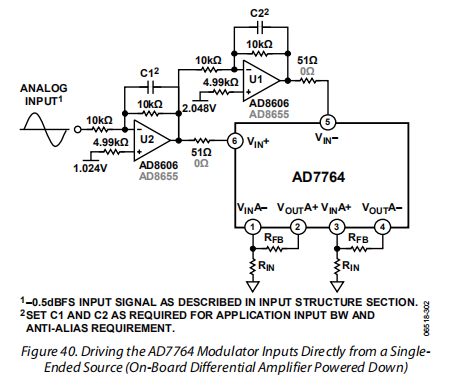

直接驱动调制器输入

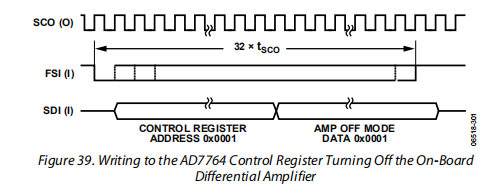

AD7765可以配置为禁用车载差分放大器,并且可以使用离散放大器直接驱动调制器。这允许用户降低功耗。

为了关闭板载差分放大器的电源,用户发出一个写操作,将控制寄存器中的AMP关闭位设置为逻辑高(见图39)。

AD7764调制器输入必须具有2.048 V的共模电压,并符合AD7764输入结构一节中所述的振幅。

图40所示为驱动AD7764的典型电路的一个示例,该AD7764用于需要优异的ac和dc性能的应用。AD8606或AD8656可用于直接驱动AD7764调制器输入。

最佳做法是通过典型的输入电阻将差分放大器输入短接地,并保留典型的反馈电阻。

AD7764接口

读取数据

AD7764使用与SPI兼容的串行接口。图2中的时序图显示了AD7764如何传输其con-version结果。

从AD7764读取的数据使用串行时钟输出(SCO)进行计时。SCO频率是AD7764的MCLK输入频率的一半。

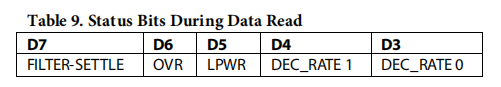

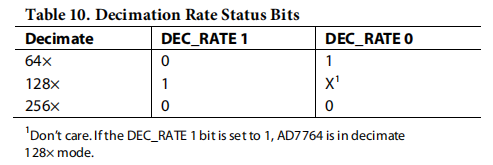

串行数据输出(SDO)线上的转换结果输出由帧同步输出(FSO)构成,FSO在32个SCO周期内被逻辑低发送。新转换结果的每一位都被记录在上升SCO边缘的SDO线上,并且在下降SCO边缘有效。32位结果由24个数据位、5个状态位和3个零组成。表9列出了五个状态位,并在下表中进行了说明。

(1)、FILTER-SETTLE位指示从AD7764输出的数据是否有效。重置设备后(使用重置pin)或清除数字滤波器(使用SYNCpin),FILTER-SETTLE位逻辑变低,表示FILTER的完全稳定时间尚未过去,并且数据尚未有效。当部件的输入已断言超范围警报时,FILTER-SETTLE位也将变为零。

(2)、OVR(overrange)位在overrange Alerts部分描述。

(3)、当AD7764在低功率模式下运行时,LPWR位设置为逻辑高。有关更多详细信息,请参阅电源模式部分。

(4)、DEC_RATE 1和DEC_RATE 0位表示所使用的抽取率。表10是抽取率位的真值表。

读取状态和其他寄存器

AD7764具有增益校正寄存器、超量程寄存器和只读状态寄存器。要读取这些寄存器的内容,用户必须首先写入设备的控制寄存器,并设置与要读取的寄存器相对应的位。下一个读取操作输出选定寄存器(SDO管脚上)的内容,而不是转换结果。

为了确保下一个读取周期包含写入的寄存器的内容,对该寄存器的写入操作必须是在FSO下降沿之前至少完成8×t,这表示下一个读取周期的开始。有关更多详细信息,请参见图4。AD7764寄存器部分提供有关控制寄存器中相关位的更多信息。

写入AD7764

对AD7764的写操作如图3所示。串行写入操作与SCO信号同步。在SCO信号的下降沿上检查帧同步输入FSI的状态。如果FSI线低,则串行数据输入(SDI)线上的第一个数据位锁定在下一个SCO下降沿上。

将FSI信号的活动边缘设置为在SCO信号高或低时出现,以允许满足SCO下降边缘的设置和保持时间。FSI信号的宽度可以设置为1到32 SCO周期宽度。忽略32个SCO周期过去之前出现的第二个或随后的下降沿。

图3详细说明了通过SDI引脚写入AD7764的串行数据的格式。写操作需要32位。前16位用于选择要读取的数据的寄存器地址。第二个16位包含所选寄存器的数据。

即使在读取转换结果时,也允许随时写入AD7764。请注意,在写入设备之后,直到过滤器的设置时间结束之后,才会输出有效数据。此时,FILTER-SETTLE状态位被断言,以指示过滤器已设置好,并且在输出中有效数据可用。

AD7764功能

同步

AD7764的同步输入提供同步功能,允许用户开始从已知时间点收集模拟前端输入的样本。

同步功能允许操作多个AD7764设备来自使用公共同步和复位信号的同一主时钟,以便每个ADC同时更新其输出寄存器。请注意,同步化的所有设备必须以相同的功率模式和相同的抽取率运行。

对于具有多个AD7764的系统,将公共MCLK、同步和复位信号连接到每个AD7764。

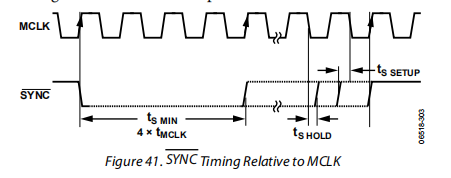

AD7764同步引脚由MCLK的下降沿轮询。当MCLK下降沿检测到同步输入信号逻辑低时,AD7764设备进入同步状态。此时,数字滤波器定序器重置为0。滤波器保持在复位状态(同步模式),直到第一个MCLK下降边缘感应同步逻辑高在可能的情况下,确保同步的所有转换与MCLK的上升沿同步发生(即,尽可能远离MCLK的下降沿或判定沿)。否则,请遵守图41中指定的定时,该定时不包括同步上升沿在围绕MCLK下降沿的10ns窗口中发生。

保持低同步逻辑至少四个MCLK周期。当MCLK下降沿检测到同步已返回逻辑高位时,AD7764滤波器开始收集输入样本同时。FSO下降沿也同步,允许同时输出转换数据。

在同步之后,数字滤波器需要时间来稳定,然后才能从AD7764读取有效数据。用户通过检查每次转换时输出的FILTER-SETTLE状态位(见表9中的D7),知道SDO行上有有效数据结果。从SYNC的上升沿到FILTER-SETTLE位断言的时间取决于所使用的过滤器配置。有关计算过滤器结算资产之前的时间的详细信息,请参阅“操作理论”部分和表6中列出的值。注意,FILTER_SETTLE位被设计为一个反动标志,用于指示转换数据输出何时有效。

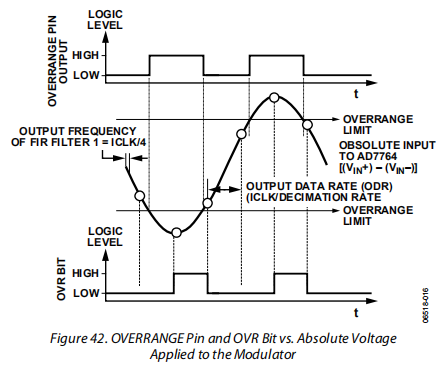

超范围警报

AD7764在管脚和状态位输出中提供超量程功能。当施加到AD7764调制器输入引脚的电压超过在超量程寄存器中设置的限值时,超量程警报指示,所施加的电压接近调制器将超量程的水平。要设置此限制,用户必须对寄存器进行编程。默认超量程限制设置为V电压的80%(见AD7764寄存器部分)。

超量程引脚输出逻辑高,提醒用户调制器已采样的输入电压的幅度大于超量程寄存器中设置的超量程限制。当调制器采样高于超量程限制的输入时,超量程引脚设置为逻辑高。当输入返回到极限以下时,超量程引脚返回到零。过量程引脚在第一个FIR滤波器级之后更新。其输出在ICLK/4频率下变化。

在数据转换期间,OVR状态位作为SDO上的位D6输出,可以在AD7764状态寄存器中进行检查。该位的动态性不如过量程引脚输出。它会在每次转换结果输出时更新;也就是说,比特会随着输出数据速率而变化。如果在为特定转换结果输出采集样本的过程中,调制器对超过超范围限制的电压输入进行了采样,则OVR位被设置为逻辑高。

图42中来自FIR滤波器1的输出点没有被绘制成相对于输出数据速率点的比例。FIR滤波器1输出的更新速度比输出数据速率快16×32×或64×取决于操作中的抽取率。

功率模式

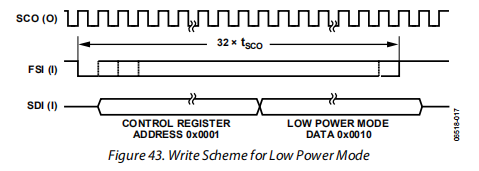

低功率模式

在通电期间,AD7764默认在正常电源模式下工作。不需要寄存器写入。AD7764还提供低功耗模式。为了在低功耗模式下操作设备,用户将控制寄存器中的LPWR位设置为逻辑高(见图43)。在低功耗模式下操作AD7764不会影响输出数据速率或可用带宽。

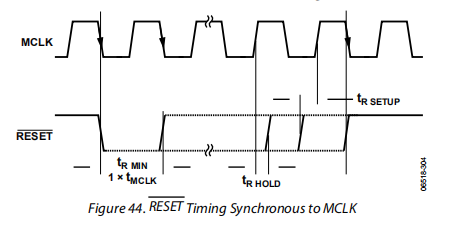

复位/PWRDWN模式

AD7764具有复位/PWRDWN引脚。将该引脚逻辑的输入保持在低位,使AD7764处于断电模式。所有内部电路复位。设备初始通电后,向AD7764施加复位脉冲。AD7764复位引脚由MCLK上升沿轮询。当MCLK上升检测到复位输入信号为逻辑低时,AD7764设备进入复位状态。AD7764从第一个MCLK上升沿的复位中出来,该上升沿感觉复位为逻辑高。

最佳实践是确保复位的所有转换与MCLK的下降沿同步发生;否则,遵循图44所示的定时要求。

复位应保持逻辑低至少一个MCLK周期,以发生有效的复位。

在多个AD7764设备正在同步的情况下使用同步脉冲,在菊花链多个AD7764设备,必须在除了普通同步和MCLK信号。

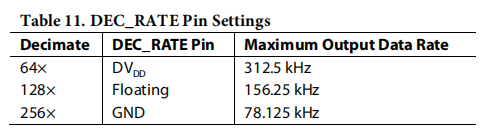

抽取率PIN

AD7764的抽取率是使用DEC_rate管脚选择的。表11显示了三种抽取率所需的电压输入设置。

菊花链

菊花链允许许多设备使用相同的数字接口线。此功能对于减少组件数量和布线连接尤其有用,例如在隔离的多转换器应用程序中或对于接口容量有限的系统。数据回读类似于移位寄存器。当使用菊花链时链条必须以共同的动力模式和共同的抽取率运行。

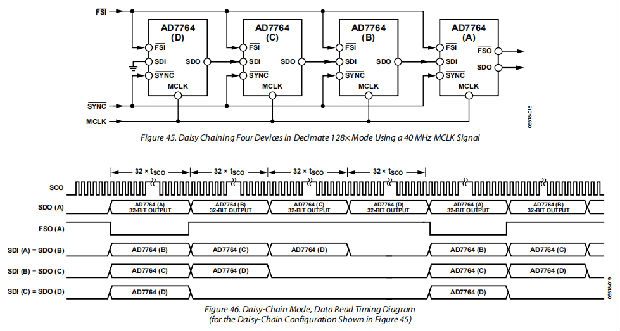

图45中的框图显示了如何连接设备以实现菊花链功能。图45显示了四个AD7764设备与应用的公共MCLK信号菊花链在一起。只能在128×或256×模式下工作。

以菊花链模式读取数据

参考图45,注意AD7764(A)的SDO线路提供来自AD7764转换器链的输出数据。另外,请注意,对于链中的最后一个设备AD7764(D),SDI管脚接地。链中的所有设备必须使用公共MCLK和同步信号。要启用菊花链转换过程,请将公共同步脉冲应用于所有设备(请参阅同步部分)。

当同步脉冲应用于所有设备后,在断言滤波器定位之前必须经过滤波器定位时间,这表示设备链输出处的有效转换数据。如图46所示,第一个转换结果从标记为AD7764(A)的设备输出。然后,此32位转换结果后跟AD7764(B)、AD7764(C)和AD7764(D)设备的转换结果,所有转换结果都以MSB第一个序列输出。从菊花链输出的信号是来自AD7764(A)的SDO引脚和链中第一个设备AD7764(A)输出的FSO信号。

FSO的下降沿向链中第一个转换输出的MSB发出信号。FSO在输出AD7764(A)结果所需的32个SCO时钟周期内保持逻辑低电平,然后在从AD7764(B)、AD7764(C)和AD7764(D设备)输出转换结果的过程中变为逻辑高电平。

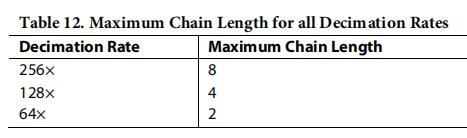

可以菊花链的设备的最大数目取决于所选择的抽取速率。通过简单地将所选择的抽取率除以32(计算每个转换必须被记录的比特数)来计算可菊花链的设备的最大数目。表12提供了每个抽取速率的链式设备的最大数目。

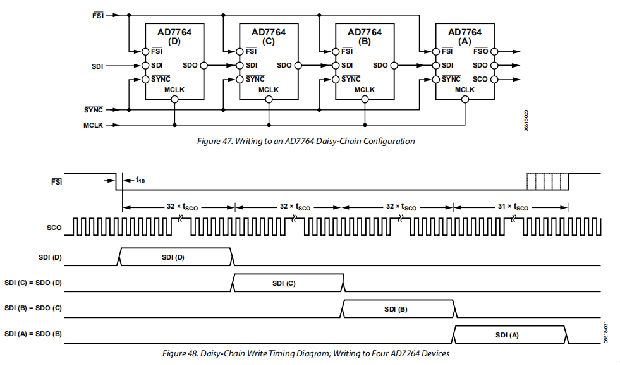

以菊花链模式写入数据

以菊花链模式写入AD7764设备与写入单个设备类似。串行写入操作与SCO信号同步。在SCO信号的下降沿上检查帧同步输入FSI的状态。如果FSI线低,则SDI线上串行数据的第一个数据位锁定在下一个SCO下降沿上。

以菊花链模式向AD7764写入数据与向单个设备写入数据具有相同的计时结构(见图3)。写入单个设备和写入多个菊花链设备的区别在于-FSI信号的增强。菊花链中的设备数量决定了FSI信号必须保持逻辑低电平的周期。要写入菊花链中的n个设备,FSI下降沿与FSI的上升沿必须在32×n-1到32×n SCO周期之间。例如,如果以菊花链模式向三个AD7764设备写入数据,则FSI在32×3-1到32×3 SCO脉冲之间逻辑低。这意味着,金融稳定指数的上升边缘必须出现在64至96上合组织时期之间。

AD7764设备可以随时写入。坠落FSI的边缘覆盖从SDO读取数据的所有尝试别针。在菊花链的情况下,FSI信号保持逻辑低电平超过32 SCO周期向AD7764设备指示链中还有更多的设备。这意味着AD7764将SDI引脚上输入的数据定向到其SDO引脚。这样可以确保数据传递到链中的下一个设备。

计时AD7764

AD7764需要外部低抖动时钟源。此信号应用于MCLK引脚。从MCLK输入信号导出内部时钟信号(ICLK)。ICLK控制AD7764的内部操作。最大值ICLK频率为20兆赫。要生成ICLK,ICLK = MCLK/2,对于等于音频系统中使用的输出数据速率,可以使用12.288mhz的ICLK频率。如表6所示,使用该ICLK频率可以实现96 kHz和48 kHz的输出数据速率。

MCLK抖动要求

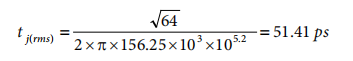

MCLK抖动要求取决于许多因素,具体如下:

其中:OSR=过采样率=fICLK/ODR。最大输入频率。SNR(dB)=目标SNR。

例1,这个例子可以从表6中获得,其中:ODR=312.5千赫。fICLK=20兆赫。fIN(最大值)=156.25 kHz。信噪比=104分贝。

这是一个满量程的最大允许时钟抖动,156.25 kHz输入音,具有给定的ICLK和输出数据速率。

例2,第二个例子也可以从表6中获得,其中:ODR=48千赫。fICLK=12.288兆赫。fIN(最大值)=19.2千赫。信噪比=109分贝。

输入振幅对这些抖动数字也有影响。例如,如果输入电平比满标度低3db,则允许的抖动增加一个因子√2,将第一示例增加到144.65ps rms。当最大回转速率通过振幅的减小而减小时,就会发生这种情况。

图49和图50示出了这一点,示出了相同频率但具有不同振幅的正弦波的最大回转率。

去耦和布局信息

电源去耦

应用于AD77 64的电源的解耦对于实现最大性能是重要的。每个电源插脚必须用100 nF,0603外壳大小的电容器与正确的接地插脚断开。

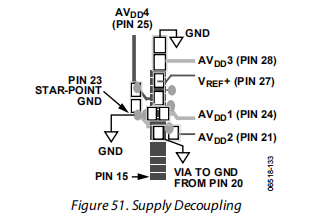

请特别注意将针脚7(AV2)直接与最近的接地针脚(针脚8)分离。数字接地引脚AGND2(引脚20)直接接地。另外,将REFGND(针脚26)直接接地。

DV(引脚17)和AV3(引脚28)电源应在远离设备的一点处与接地平面断开。建议通过0603尺寸的100 nF电容器将连接到以下电源引脚的电源与连接到引脚23(AGND1)的星形接地点断开:V+(引脚27);AV4(引脚25);AV1(引脚24);AV2(引脚21)。

图51所示为连接到AD7764右侧的这些电源的布局解耦方案。注意在引脚23处创建的星点接地。

参考电压滤波

低噪声参考源,如ADR444或ADR434(4.096 V),适合与AD7764一起使用。提供给AD7764的参考电压应如图52所示进行解耦和滤波。

参考电压电源的推荐方案是200Ω串联电阻连接到100μF钽电容器,然后是非常接近V+引脚的10 nF去耦电容器。

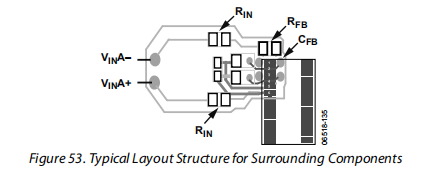

差分放大器组件

表7详细说明了片上差分放大器周围推荐使用的组件。匹配差分放大器两侧的元件对于最小化应用于放大器的信号失真非常重要。这些部件需要0.1%或更高的公差。差动放大器两侧轨道的对称布线也有助于实现所述性能。图53显示了差动放大器周围组件的典型布局。注意,两条差分路径的迹线尽可能对称,并且反馈电阻和电容器放置在PCB的底部,以实现最简单的布线。

布局注意事项

尽管使用正确的组件对于实现最佳性能至关重要,但正确的布局同样重要。上的AD7764产品页包含AD7764评估板的Gerber文件。在使用AD7764设计任何系统时,应将Gerber文件用作参考。

应仔细考虑使用地平面。为确保通过去耦电容器的回流流向正确的接地引脚,电容器的接地侧应尽可能靠近与该电源相关的接地引脚,如“电源去耦”一节中建议的那样。

使用AD7764

步骤1到步骤5详细说明了通电和使用AD7764的顺序。

1、给设备通电。

2、应用MCLK信号。

3、在至少一个MCLK循环中采用低复位,最好与下降的MCLK边缘同步。如果要同步多个部件,请对所有设备应用公用重置。

4、释放复位后,至少等待两个MCLK周期。

5、如果多个部分正在同步,则必须对这些部分应用同步脉冲,最好与MCLK上升沿同步。在设备不同步的情况下,不需要同步脉冲;逻辑高信号应简单地应用于同步管脚。当应用同步脉冲时,

(1)、向设备发出同步脉冲不得与向设备写入同步脉冲同时发生。

(2)、确保同步脉冲在至少四个MCLK周期内处于低位。

然后可以使用默认增益和超范围阈值从设备读取数据。但是,在经过筛选器的设置时间之前,读取的转换数据无效。一旦发生这种情况,就设置FILTER-SETTLE状态位,表示数据有效。

增益和超量程阈值的值可以在这个阶段写入或从相应的寄存器读取。

偏置电阻选择

AD7764需要在R和AGNDx引脚之间连接一个电阻器。应选择电阻值,以便通过电阻对地提供25微安的电流。对于4.096 V参考电压,正确的电阻值为160 kΩ。

AD7764寄存器

AD7764有许多用户可编程寄存器。控制寄存器用于设置片内缓冲器和差分放大器的功能,并提供关闭AD7764的选项。还有数字增益和超量程阈值寄存器。写入这些寄存器包括写入寄存器地址后接16位数据字。本节提供寄存器地址、单个位的详细信息和默认值。

增益寄存器地址0x0004

非位映射,默认值0xA000

增益寄存器按比例缩放,使得0x8000对应于1.0的增益。此寄存器的默认值为1.25(0xA000)。当输入为V+的80%时,这将产生一个满量程的数字输出,以最大的模拟输入范围为±80%的V+P P。

超范围寄存器地址0x0005

非位映射,默认值0xCCCC

将超量程寄存器值与第一抽取滤波器的输出进行比较,以获得具有最小传播延迟的过载指示。这是在任何增益缩放之前。默认值为0xccCC,对应于V+(最大允许模拟输入电压)的80%。假设V+=4.096 V,则当输入电压超过约6.55 V P P微分时,位被设置。如果在调制器速率下连续四个以上采样的模拟输入电压超过V+的100%,则立即设置超范围位。

外形尺寸