1200点击型号即可查看芯片规格书

3750点击型号即可查看芯片规格书

说明

The HCPL-3120 contains a gaasp led while the HCPL-J312 andHCNW3120含有一个Algaas LED。LED是光学的与一个功率输出级的集成电路耦合。这些光电耦合器是理想的驱动功率IGBTS和用于电动机控制逆变器应用的mosfets。茶输出阶段高操作电压范围提供门控制器驱动电压要求电压这些光耦器提供的电流使他们理想化直接驱动胰岛素样蛋白1200 V//100 A.For Igbts with higher ratings,the HCPL-3120系列可用于驱动驱动驱动驱动的离散功率级IGBT GateHCNW3120是高绝缘Viorm电压=1414vpeak in the IEC//en//din en 60747-5-5.HCPL-J312具有VIORM绝缘电压=1230VPEAKand the viorm=630vpeak is also available with the HCPL-3120(备选案文060)保证金建议正常静态防范处理和组装预防损害和/或ESD可能引起的降解

特征

2.5最大峰值输出电流

2.0 A最小峰值输出电流

25 kV/μs VCM最小共模抑制(CMR)=1500伏0.5 V最大低电平输出电压(VOL)消除需要负栅极驱动

CC=5毫安最大供电电流

带滞后的欠压锁定保护(UVLO)

宽工作电压控制范围:15至30伏

500纳秒最大开关速度

工业温度范围:–40°C至100°C

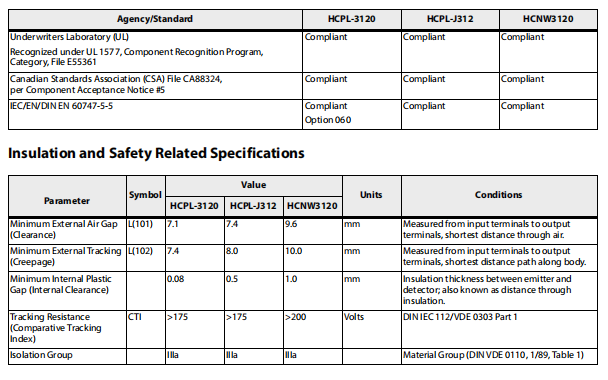

安全批准:UL认可HCPL-3120/J312为3750 Vrms,持续1分钟对于HCNW3120,5000 Vrms,持续1分钟CSA批准批准的IEC/EN/DIN EN 60747-5-5:VIORM=630 V峰值,适用于HCPL-3120(选项060)HCPL-J312的VIORM=1230 V峰值对于HCNW3120,VIORM=1414 V峰值

应用

IGBT/MOSFET栅极驱动

交流/无刷直流电机驱动

工业逆变器

开关电源

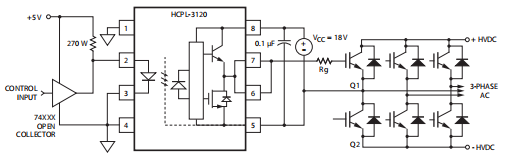

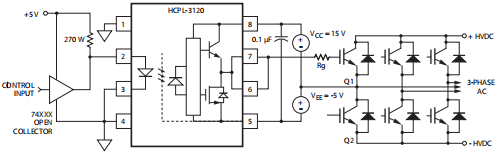

必须在引脚5和引脚8之间连接一个0.1μF的旁路电容器

笔记:

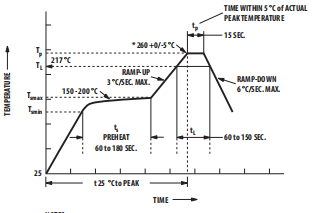

从25°C到最高温度的时间=最多8分钟。最高温度=200°C,最低温度=150°C

注:应使用非卤化物焊剂。宽体400 mils包装的建议峰值温度为245°C

所有Avago技术数据表都报告了光耦组件本身固有的漏电和间隙。这些在确定电路绝缘要求时,尺寸是设备设计师需要的起点。但是,一旦安装在印刷电路板上,必须满足规定的最小爬电和间隙要求个别设备标准。对于漏电,沿印刷电路板表面必须考虑输入和输出引线的焊料圆角。有推荐的技术,如凹槽和肋可用于印刷电路板,以达到所需的爬电和间隙。爬电距离和间隙距离也将根据污染程度和绝缘等级等因素变化。

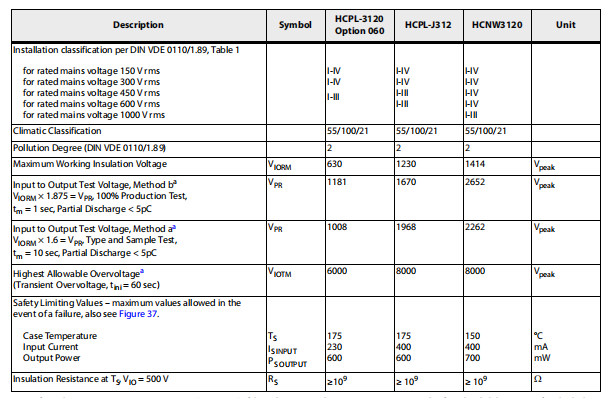

IEC/EN/DIN EN 60747-5-5绝缘相关特性

这些光耦器是安全电气绝缘的“只有在安全极限数据内”。维护安全数据应通过保护电路加以保证。表面安装分类是一级的With CECC 00802.

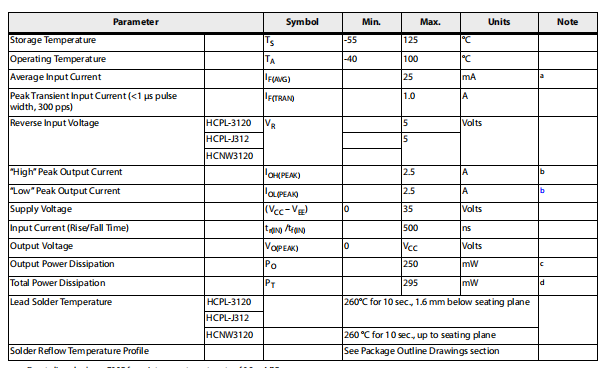

绝对最大额定值

a、 以0.3毫安/摄氏度的速率线性降低70°C以上的自由空气温度。

b.0a.有关限制IOH峰值的更多详细信息,请参见应用部分。

c.以4.8 mW/℃的速率线性降低70℃以上的自由空气温度。

d.在70℃以上的自由空气温度下,以5.4 mW/c的速度直线下降,最大的LED结温不应超过125°C。

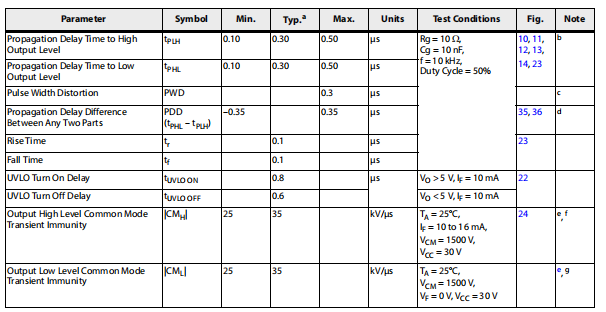

电气规范(DC)

超过推荐的操作条件(TA=-40至100°C,对于HCPL-3120,HCPL-J312 IF(ON)=7至16毫安,对于HCNW3120 IF(ON)=10至16毫安,VF(关)=-3.6至0.8伏,VCC=15至30伏,VEE=接地),除非另有规定。

a、 TA=25°C和VCC–VEE=30 V时的所有典型值,除非另有说明。

b.0 A VO=(VCC–15 V)17 c最大脉冲宽度=10μs,最大占空比=0.2%。

c.0a.有关限制IOH峰值的更多详细信息,请参见应用部分。

d.在这个测试中,VOH是用直流负载电流测量的。当驱动电容性负载时,当IOH接近零安培时,VOH将接近VCC。

e.最大脉冲宽度=1毫秒,最大占空比=20%。

应用程序信息

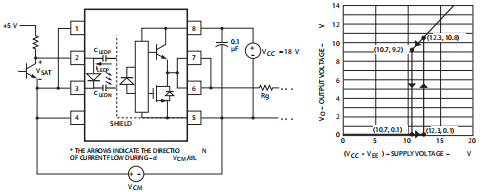

消除负IGBT栅极驱动(讨论适用于HCPL-3120、HCPL-J312和HCNW3120)为了保持IGBT稳定,HCPL-3120具有非常低的最大VoL规格为0.5V。HCPL-3120实现这一非常低的。VOL通过使用一个DMOS晶体管与1(典型)在其下拉电路电阻。当HCPL-3120处于低状态时IGBT栅极通过Rg+1对发射极短路。最小化从HCPL-3120到IGBT栅极的Rg和引线电感发射器(可能通过将HCPL-3120安装在IGBT正上方的小型PC板上)可以消除对负极的需求IGBT门极驱动在许多应用中如图25所示。这种PC板的设计应注意避免IGBT集电极或发射极跟踪接近HCPL-3120输入,因为这可能导致不必要的瞬态信号耦合到HCPL-3120并降低性能。(如果IGBT漏极必须在HCPL-3120输入端附近布线,则LED应当处于关闭状态时反向偏置,以防止从IGBT漏极耦合的瞬态信号打开HCPL-3120。)

选择栅极电阻(Rg)以最小化IGBT开关损失。(讨论适用于HCPL-3120、HCPL-J312和HCNW3120)

步骤1:根据IOL峰值规格计算Rg最小值。图中的IGBT和Rg可以作为一个简单的RC进行分析由HCPL-3120提供电压的电路。

Rg≥(VCC–VEE–VOL)/IOLPEAK

=(VCC–V–2V)/I峰值

=(15V+5V–2V)/2.5A

=7.2≈8上式中2V的体积值是保守的峰值电流为2.5A时的VOL值(见图)。在较低的位置Rg值HCPL-3120提供的电压不理想电压阶跃。这会导致较低的峰值电流(更大的裕度)比这个分析预测的要多。当负栅极驱动不是前一个方程式中使用的V等于零伏特。

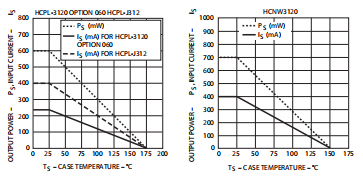

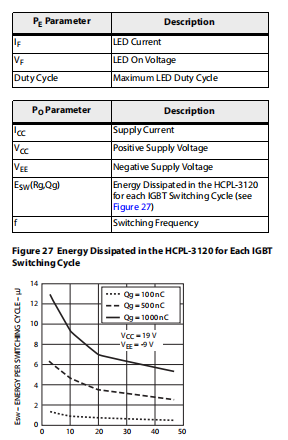

步骤2:检查HCPL-3120的功耗并增加如有必要。HCPL-3120总功耗(PT)为等于发射极功率(PE)和输出的总和

功率(PO):

PT=PE+PO-PE=IF×VF×占空比

PO=PO(偏压)+PO(切换)

=ICC×(VCC–VEE)+ESW(RG,QG)×f对于图中的电路,IF(最坏情况)=16mA,Rg=8,最大占空比=80%,Qg=500 nC,f=20 kHz和TA最大值=85°C:PE=16毫安×1.8伏×0.8=23兆瓦PO=4.25ma×20v+5.2μJ×20khz=85兆瓦+104兆瓦=189兆瓦>178兆瓦(最大值)(85°C时)=250兆瓦-15摄氏度*4.8兆瓦/摄氏度)上式中ICC的4.25ma值为通过降低ICC最大值5毫安(发生在–40°C)至85°C时的ICC最大值(见图)。由于这种情况下的PO大于PO(MAX),Rg必须是增加以降低HCPL-3120的功耗。PO(开关最大值)=PO(最大值)–PO(偏差)=178兆瓦-85兆瓦=93兆瓦ESW(MAX)=(PO(SWITCHINGMAX))/f

=93mW/20kHz=4.65μJ对于Qg=500 nC,从图中,ESW=4.65μJ的值给出Rg=10.3。

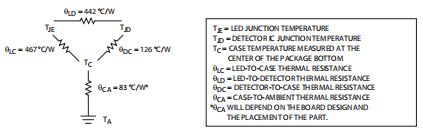

热模型(讨论适用于HCPL-3120、HCPL-J312以及HCNW3120)HCPL-3120的稳态热模型如图。模型中给出的热阻值可用于计算给定的操作条件。如模型所示,所有热量生成的流通过引起这种情况的CA相应的温度TC。θCA的值取决于董事会设计条件,因此由设计师。θCA=83°C/W的值来自使用2.5×2.5英寸PC板进行热测量小痕迹(无接地平面),单个HCPL-3120焊接在板的中心和静止的空气中。绝对的最大功耗降额规范假定θ温度为83°C/W。根据图中的热模式,LED和探测器IC

结温可以表示为:TJE=PE≈(θLC | |(θLD+θDC)+θCA)+PD×((θLC×θDC)/(θLC+θDC+θLD))+θCA)+TA TJD=PE(θLC×θDC)/(θLC+θDC+θLD))+θCA+PD×(θDC | |(θLD+θLC+θCA)+TA

插入图所示的θLC和θDC的值可以得到:TJE=PE×(256°C/W+θCA)+PD•(57°C/W+θCA)+TA TJD=PE×(57°C/W+θCA)+PD×(111°C/W+θCA)+TA例如,给定PE=45 mW,PO=250 mW,TA=70°C,以及θCA=83°C/W:TJE=PE×339°C/W+PD×140°C/W+TA=45兆瓦×339摄氏度/瓦+250兆瓦×140°C/W+70°C=120°CTJD=PE×140°C/W+PD×194°C/W+TA=45兆瓦×140°C/W+250兆瓦×194°C/W+70°C=125°CTJE和TJD应根据电路板限制在125°C特定于应用程序的布局和部件放置(θCA)。

超高CMR性能的LED驱动电路考虑(讨论适用于HCPL-3120、HCPL-J312和HCNW3120)在没有探测器屏蔽的情况下,光耦CMR失效的主要原因是输入端的电容耦合光耦,穿过封装,到达探测器IC,如图所示。HCPL-3120通过使用具有光学透明法拉第屏蔽的探测器集成电路,其将电容耦合电流从敏感集成电路转移电路。但是,此屏蔽不会消除LED和光耦引脚5–8之间的电容耦合,如所示图。这种电容耦合会在共模瞬态过程中引起LED电流的扰动,并成为屏蔽光耦CMR失效的主要原因。高CMR LED驱动电路的主要设计目标是在共模瞬态过程中保持LED处于正确的状态(开或关)。例如,推荐的应用程序电路(图),可以实现25kV/μs CMR,同时最小化组件复杂度。在接下来的两部分中,我们将讨论保持LED处于正确状态的技术。

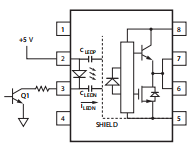

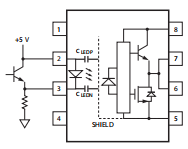

带LED的CMR(CMRH)高CMR LED驱动电路必须在共模瞬态。这是通过过度驱动LED电流超过输入阈值,因此不会被拉在瞬间低于阈值。最小发光二极管10毫安的电流在最大值上提供足够的余量。5毫安的FLH,达到25千伏/微秒CMR。LED熄灭时的CMR(CMRL)高CMR LED驱动电路必须保持LED熄灭(VF≤共模瞬变期间的VF(关)。例如,在a–图中的dVcm/dt瞬态,流过的电流CLEDP也流经逻辑门的RSAT和VSAT。作为只要逻辑门上产生的低电压小于VF(关闭),LED将保持关闭且无共模会发生故障。如图所示,开路集电极驱动电路不能在+dVcm/dt瞬态期间保持LED熄灭,因为流过CLEDN的电流必须由LED提供,不建议用于要求超高CMRL性能。图是替代驱动电路与推荐的应用电路(图)一样,是否通过分流LED实现超高CMR性能处于关闭状态。

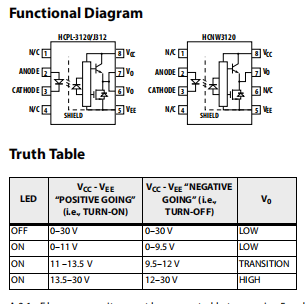

欠压锁定特性(讨论适用于HCPL-3120、HCPL-J312和HCNW3120)HCPL-3120包含欠压锁定(UVLO)用于保护IGBT故障的特性导致HCPL-3120电源电压的条件(相当于完全充电的IGBT栅极电压)下降低于使IGBT保持低电阻所必需的水平国家。当HCPL-3120输出处于高状态时电源电压低于HCPL-3120 VUVLO–阈值(9.5<VUVLO–<12.0)光耦输出将进入低电平典型延时状态,UVLO关断延时,0.6μs。当HCPL-3120输出处于低状态且电源电压高于HCPL-3120vuvlo+阈值(11.0<VUVLO+<13.5)光耦输出将进入高状态(假设LED为“开”),典型延迟为UVLO开启延时0.8μs。IPM死区时间和传播延迟

规格

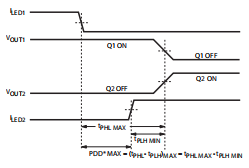

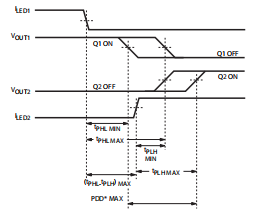

(讨论适用于HCPL-3120、HCPL-J312和HCNW3120)HCPL-3120包括传播延迟差(PDD)旨在帮助设计人员最小化“死区时间”的规范在他们的逆变电源设计中。死区时间是指时间段在此期间,高侧和低侧功率晶体管(Q1图中的Q2)关闭。第一季度和第二季度的任何重叠传导将导致大电流流过高低压电机轨道之间的功率装置

为了在给定的设计中最小化死区时间,开启LED2应延迟(相对于LED1的关闭),以便在最坏的情况下,晶体管Q1刚刚关断当晶体管Q2导通时,如图所示。这个达到此条件所需的延迟量相等传播延迟差的最大值规格,PDDMAX,指定为工作温度范围为-40°C至100°C。利用最大传输延迟延迟LED信号差分确保最小死区时间为零,但是不告诉设计者最大死区时间是什么。最大死区时间相当于差值。最大与最小时滞之间的关系不同规格如图所示。最大值HCPL-3120的停滞时间为700ns(=350ns–(–350ns))以上工作温度范围为-40°C至100°C。注意,用于计算PDD和在相同的温度和试验条件下取死区时间因为考虑中的光耦通常是安装在彼此接近且正在切换的位置相同的IGBT。