1.0主要功能

锁相环(PLL)装置综合来自晶体振荡器或外部参考时钟的输出时钟频率片上可调压控晶体振荡器(VCXO)允许精确的系统频率调谐

通常用于生成MPEG-2解码器时钟

3.3V电源电压

极低相位噪声锁相环

与“可拉”14pF晶体一起使用-不需要外部填充电容器

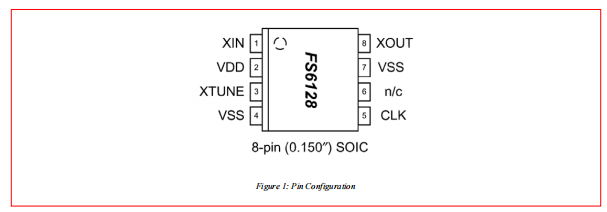

电路板占地面积小(8针0.150“SOIC)

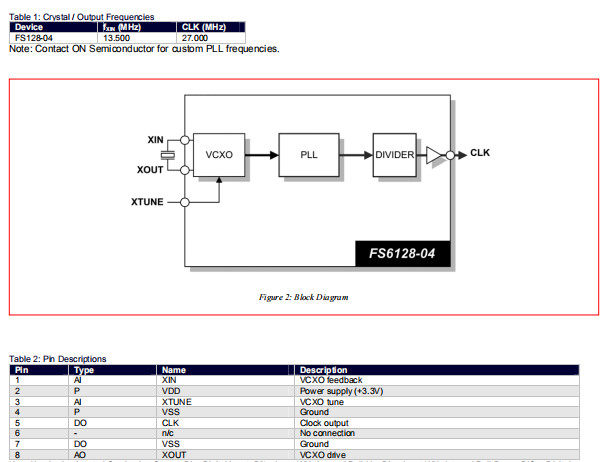

FS6128是一个单片CMOS时钟产生器集成电路,其设计目的是使数字电路的成本和元件数量最小化视频/音频系统。FS6128的核心是当外部谐振器工作时,压控晶体振荡器(VCXO)实现的电路(名义上为13.5兆赫)已连接。VCXO可以精确调整设备频率,以便在具有频率的系统中使用匹配要求,如数字卫星接收机。锁相环高分辨率通过后分频器产生输出时钟(CLK)。CLK频率是按比例计量的来自VCXO频率。将CLK频率锁定到其他系统参考频率可以消除不可预测的视频系统中的伪影,减少由频率谐波叠加引起的电磁干扰。

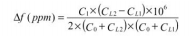

键:AI=模拟输入;AO=模拟输出;DI=数字输入;DIU=带内部上拉的输入;DID=带内部下拉的输入;DIO=数字输入/输出;DI-3=三电平数字输入,DO=数字输出;P=电源/接地;#=有源低引脚

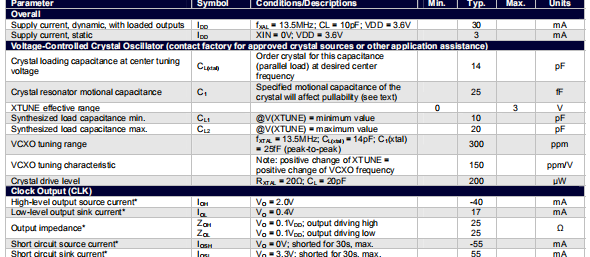

3.1压控晶体振荡器(VCXO)

VCXO为其他FS6128系统组件提供可调谐、低抖动频率参考。负载电容晶体在FS6128的内部。VCXO的运行不需要外部组件(除了谐振器本身)。VCXO频率的连续微调是通过改变XTUNE引脚上的电压来实现的。这个电压的值控制晶体的有效电容。负载电容的实际变化量将改变振荡器频率取决于晶体的特性以及振荡器电路本身。重要的是,晶体负载电容的正确规定,以“中心”调谐范围。见表。

FS6128-04型

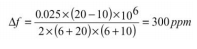

获得晶体振荡器“拉”能力的一个简单公式是:

C0=晶体的分流(或保持)电容

C1=晶体的运动电容

CL1和CL2=FS6128所施加的负载电容的两个极值(最小值和最大值)。

示例:使用具有以下参数的晶体:C1=0.025pF和C0=6pF。使用最小和最大值CL1=10pF,CL2=20pF,调谐范围(峰间)为:

3.2锁相环(PLL)片上锁相环是一种标准的频率锁相环结构。PLL将参考振荡器频率乘以以整数比表示的期望输出频率。频率倍增是精确的,且合成误差为零(除非另有说明指定)。

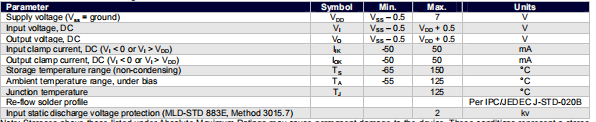

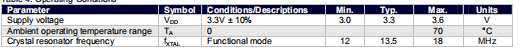

4.0电气规范

注意:在绝对最大额定值以上列出的应力可能对设备造成永久性损坏。这些条件代表一种压力仅限额定值和设备在本规范所述操作限值以上的这些或任何其他条件下的功能运行,并不意味着。暴露于扩展条件的最大额定条件可能影响器件性能、功能和可靠性。

注意:静电敏感装置

如果设备受到高能量的影响,可能会导致功能或性能的永久性损坏静电放电。

表5:直流电气规范

注:除非另有说明,否则任何输出和环境温度范围TA=0°C至70°C时,VDD=3.3V±10%空载。参数用星号(*)表示标称特性数据,不按任何特定限值进行生产测试。其中,最小和最大特征数据为典型值的±3σ。负电流表示电流流出装置。

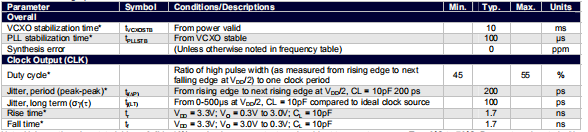

表6:交流定时规范

注:除非另有说明,否则VDD=3.3V±10%,任何输出无负载,环境温度范围TA=0°C至70°C。参数用星号(*)表示标称特性数据,不按任何特定限值进行生产测试。其中,最小和最大特征数据为典型值的±3σ。