LM4040点击型号即可查看芯片规格书

4096点击型号即可查看芯片规格书

610点击型号即可查看芯片规格书

750点击型号即可查看芯片规格书

RS232点击型号即可查看芯片规格书

特征

串行I/O(兼容微丝);2、4或8通道差分或单端多路复用器;模拟输入采样/保持功能;断电模式;可变分辨率和转换率;可编程采集时间;可变数字输出字长和格式;无需进行零刻度或满刻度调整;通过4.096V基准电压进行全面测试和保证;0V至5V模拟输入范围,单5V电源;供给无超温丢失代码。

主要规格

分辨率12位加号;12位加号转换时间:-ADC12H030系列5.5微秒(最大值);-ADC12030系列8.8微秒(最大值);12位加号吞吐量时间-ADC12H030系列8.6微秒(最大值)-ADC12030系列14微秒(最大值);积分线性误差±1 LSB(最大值);单电源5V±10%n功耗33mW(最大)-断电100微瓦(典型值)。

应用

医疗器械;过程控制系统;试验设备。

一般说明

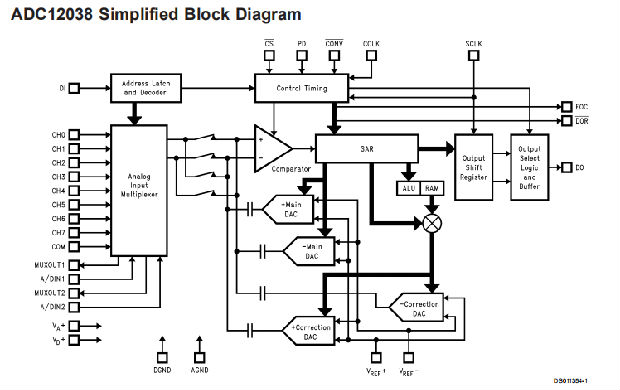

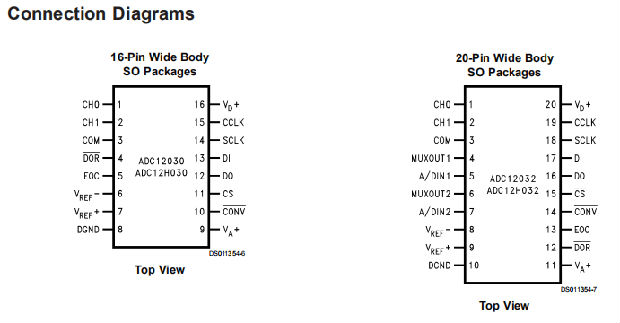

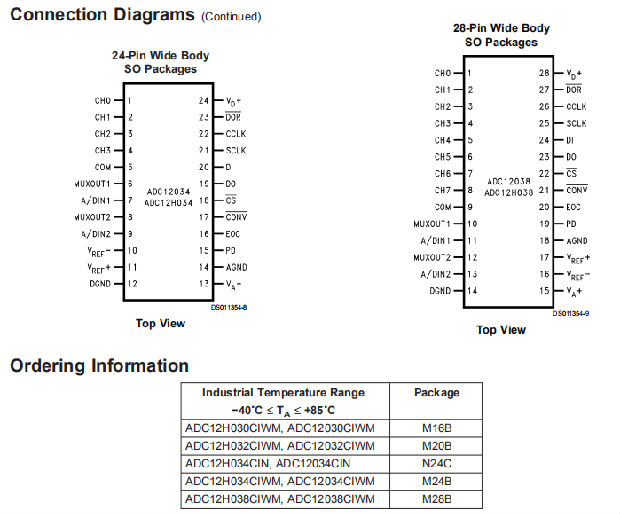

ADC12030和ADC12H030系列为12位以上串行输入输出的逐次逼近A/D转换器以及可配置的输入多路复用器。ADC12032/ADC12H032、ADC12034/ADC12H034和ADC12038/ADC12H038分别有2路、4路和8路多路复用器。差分复用器输出和A/D输入是在MUXOUT1、MUXOUT2、A/DIN1和A/DIN2上提供别针。ADC12030/ADC12H030具有双通道多路复用器,多路复用器输出和内部a/D输入有联系的。ADC12030系列的测试频率为5 MHz时钟,而ADC12H030系列是用8兆赫测试的时钟。根据要求,这些A/D通过自校准调整线性、零和满标度误差至每个小于±1 LSB。模拟输入可以配置为在不同的单端、差分或伪微分模式。全差分单极模拟电路输入范围(0V到+5V)可以用一个+5V电源。在差分模式下,即使负输入大于正是因为12位加号输出数据格式。串行I/O配置为符合NSC MICROWIRE8482;。有关电压参考,请参阅LM4040或LM4041。

程序提示

1.0数字接口

1.1接口概念

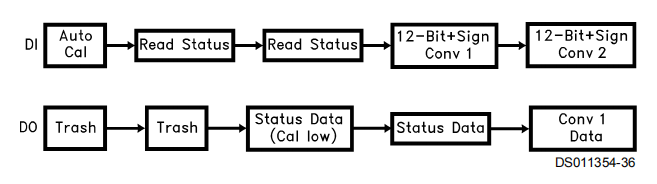

图7中的示例显示了一个典型的事件序列ADC12030/2/4/8通电后:

图7。典型电源供电顺序

通过DI输入A/D的第一条指令启动自动校准。当时DO上的数据输出没有意义,是完全随机。确定自动校准是否完成后,将向A/D。同样,当时的数据输出没有意义因为Auto-Cal过程修改输出中的数据移位寄存器。要检索状态信息,还需要向A/D发出读取状态指令。此时DO上有状态数据。如果状态字中的校准信号为低,则自动校准已完成。因此下一条发出的指令可以开始转换。此时的数据输出再次为状态信息。保持噪音由于损坏了A/D转换,无法读取状态在转换过程中。如果CS在转换过程中被调低,则该转换过早结束。EOC可用于确定转换结束或A/D控制器可以在软件中跟踪何时适合再次与A/D通信。一旦它已确定A/D已完成转换,可向A/D发送另一条指令当下一条指令发送到A/D时,可以访问此转换的数据。

注意,当CS持续较低时,传输SCLK周期的确切数目,如计时所示图表。不这样做将使串行通信与A/D不同步(见第1.3节)。

1.2更改配置

ADC12030/2/4/8通电时的配置默认为12位加号分辨率,先是12位或13位MSB,10 CCLK采集时间,用户模式,无自动校准,无自动归零,加电模式。改变获取时间和打开和关闭符号位需要8位指令发给ADC。此指令不会启动转换。选择多路复用器地址和格式化输出数据开始转换。图8描述了更改ADC12030/2/4/8。

在I/O序列1期间,DI上的指令配置ADC12030/2/4/8,以12位+符号分辨率进行转换。注意,当6 CCLK采集和数据输出如果没有向ADC、I/O序列2和3发出符号指令,则不会启动新的转换。数据这些指令期间的输出来自转换N在I/O序列1期间启动。配置修改时序图详细描述了不带标志的数据输出所需的事件,带签署,或6/10/18/34 CCLK采集时间模式选择。表5描述了需要输入到完成此配置修改的ADC。这个下一条指令,如图8所示,发送给A/D启动转换N+1,首先是8位分辨率格式的MSB。同样,在这个I/O周期中的数据输出是来自转换N。

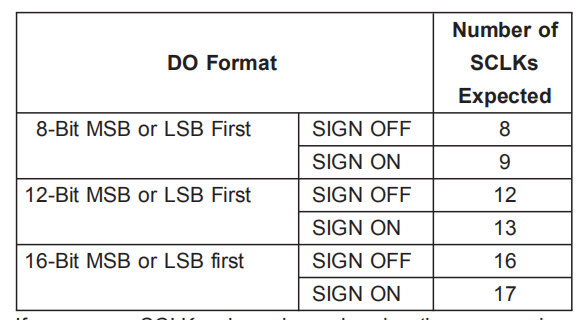

在任何转换I/O序列中应用于A/D的SCLK的数量应根据输出的数据而变化在上一个转换I/O序列期间选择的字格式。可用的各种格式和分辨率有如表1所示。在图8中,因为8位没有符号MSB第一种格式是在I/O序列4中选择的I/O序列5期间所需的SCLK数为8。在下面的I/O序列中,格式更改为12位,无符号MSB优先;因此在I/O序列6相应地更改为12。

1.3 CS低持续考虑

当CS持续较低时,传输ADC期望的SCLK脉冲的确切数量。不这样做将使串行通信与ADC。当电源首次应用于ADC时预计每次I/O传输将看到13个SCLK脉冲。ADC期望看到的SCLK脉冲数为与数字输出字长相同。数字输出字长由数据输出(DO)格式控制。这个DO格式可能在转换开始时更改或者当符号位打开或关闭时。下表详细列出了不同DO格式:

如果错误的SCLK脉冲使通信失去同步,最简单的恢复方法是循环设备的电源。无法轻松地重新同步设备是使CS持续处于低位的一个缺点。

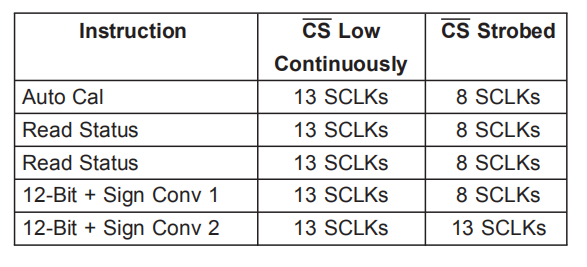

当CS保持低连续性时,I/O交换所需的时钟脉冲数可能不同-ly与循环CS时的情况。以图7(典型电源顺序)中详细描述的I/O顺序为例。下表列出了每条指令所需的SCLK脉冲数:

1.4模拟输入通道选择

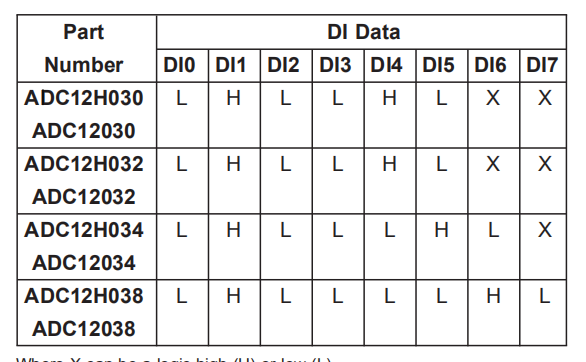

DI上的数据输入还选择特定a/D转换的通道配置(见表2、3、4和表5)。在图8中,只有在I/O序列1、4、5和6期间可以修改通道配置。输入通道在每次新转换开始前重新选择。如下所示为在图8中的I/O序列号4期间,将CH1设置为正输入,而将CH0设置为负输入的不同版本的ADC所需的数据位流:

其中X可以是逻辑高(H)或低(L)。

1.5上/下电

ADC可以随时断电,方法是PD引脚高或通过DI上的指令输入(见表5、6和上/下电时序图)。当ADC以这种方式断电时,A/D转换所需的电路被停用。数字I/O所需的电路保持激活。硬件上/下电由PD引脚的状态控制。软件上/下电由发送给ADC的指令控制。如果在硬件断电生效(PD引脚高)时向ADC发出软件加电指令,则设备将保持断电状态。如果在硬件加电生效(PD引脚低)时向ADC发出软件断电指令,则设备将断电。当设备由软件断电时,可以通过发出软件通电指令或将PD引脚先高后低来通电。如果在A/D转换期间发出断电命令,则该转换将中断。因此,不能依赖上电后的数据输出。

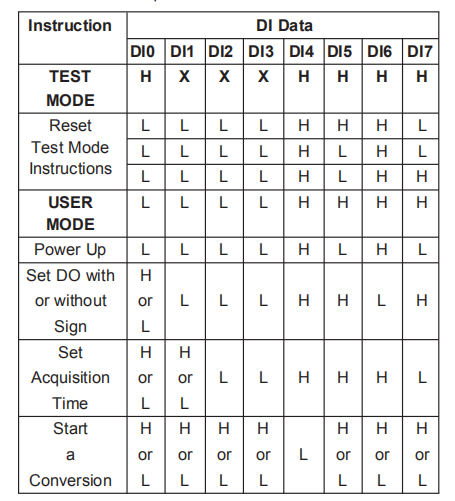

1.6用户模式和测试模式

可以向ADC发出指令,使其进入测试模式。制造商使用测试模式验证设备的完整功能。在测试模式期间,CH0–CH7变为激活输出。如果无意中将设备放入在CS持续低电平的测试模式下,串行通信可能会失去同步。可通过循环设备的电源电压来恢复同步。循环电源电压也会将设备设置为用户模式。如果串行接口中使用了CS,则可以查询ADC以查看其处于何种模式。这是通过向ADC发出“读取状态寄存器”指令来完成的。当状态寄存器的位9为高时,ADC处于测试模式;当位9为低时,ADC处于用户模式。作为循环电源的替代,可以使用指令序列将设备返回到用户模式。此指令序列必须使用CS发送到ADC。下表列出了将设备返回用户模式所需的说明:

X=不在乎

使用用户模式指令返回用户模式后,需要重新发送通电、带或不带符号的数据和采集时间指令,以确保在开始转换之前ADC处于所需状态。

1.7在不启动转换的情况下读取数据

通过确保CONV行在I/O序列期间处于高位,可以在不启动新转换的情况下访问来自特定转换的数据。请参阅读取数据时序图。表6描述了转换销的操作。

2.0模拟多路复用器说明

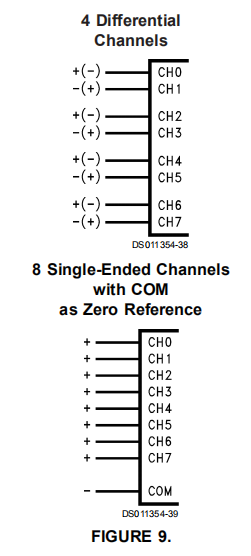

对于ADC12038,模拟输入多路复用器可以配置4个差分通道或8个单端通道,其中COM输入作为零参考或其任何组合(见图9)。VREF+和VREF-引脚上的电压差决定了输入电压范围(VREF)。模拟输入电压范围为0至VA+。当车辆识别号->车辆识别号+时,产生负数字输出代码。

车辆识别号-或车辆识别号+处的实际电压不能低于活动范围。

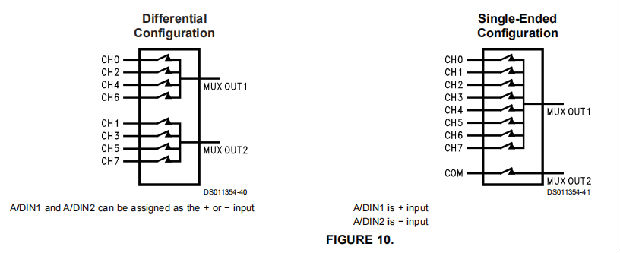

CH0、CH2、CH4和CH6可以分配给MUX-差分配置中的OUT1引脚,而CH1、CH3、CH5和CH7可以分配给MUXOUT2引脚。在差分配置中,模拟输入按如下方式配对:CH0与CH1、CH2与CH3、CH4与CH5和CH6与CH7。A/DIN1和A/DIN2管脚可以指定正负极性。

对于单端多路复用器配置,CH0到CH7可以分配给MUXOUT1管脚。COM管脚总是分配给MUXOUT2管脚。A/DIN1被指定为正输入;A/DIN2被指定为负输入。(见图10)。

ADC12030、2、4、8(表2、3、4)的多路复用器分配表总结了不同版本A/Ds的上述功能。

2.1各种多路复用器配置的偏压

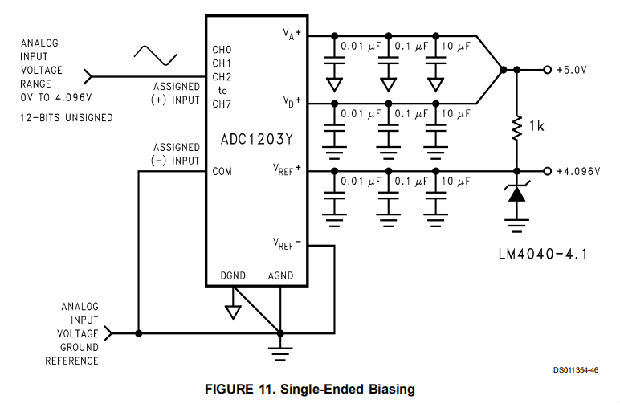

图11是一个偏压单端操作装置的例子。标志位总是低。数字输出范围为0 0000 0000到0 1111 1111 1111。一个LSB等于1 mV(4.1V/4096 LSB)。

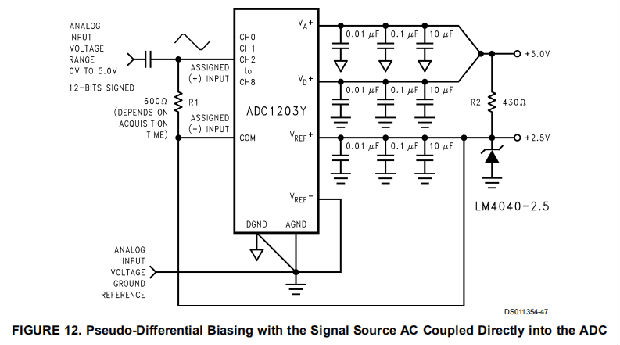

对于伪差分符号运算,图12所示的偏置电路显示耦合到ADC的信号AC。这使数字输出范围为-4096到+4095。如图所示,当参考电压为2.5V时,1LSB等于610μV。尽管ADC未使用2.5V参考电压进行生产测试,但线性误差通常不会变化超过0.1LSB(见典型电气特性部分的曲线)。当ADC设置为10个时钟周期的采集时间时,输入偏置电阻需要小于等于600Ω。注意,虽然输入耦合电容需要相当大,以降低高通角。将采集时间增加到34个时钟周期(以5mhz CCLK频率)将允许600Ω增加到6k,而使用1μF耦合电容器将高通角设置为26hz。将R增加到6k将允许R2为2k。

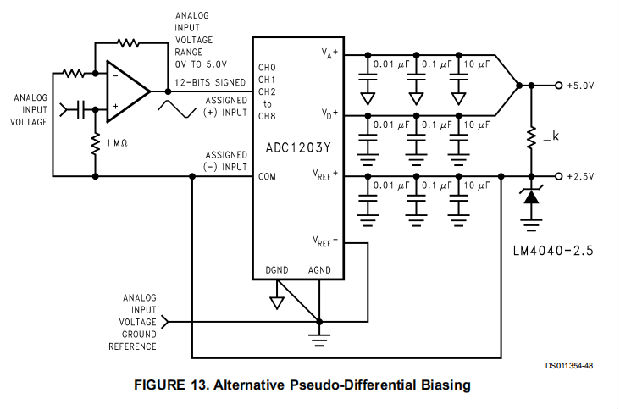

偏置伪差分操作的另一种方法是使用来自LM4040的+2.5V偏置驱动ADC的任何放大器电路,如图13所示。LM4040-2.5的电阻上拉偏置值将取决于运算放大器偏置电路所需的电流。

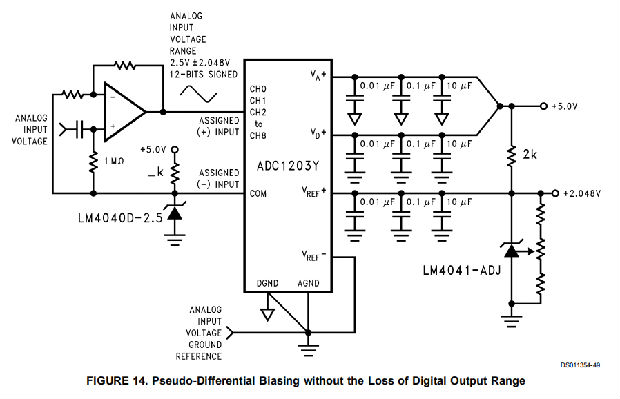

在图13的电路中,由于放大器不能用一个+5V电源摆动到+5V和GND,一些电压范围丢失。如图14所示,使用可调版本的LM4041将满标度电压精确设置为2.048V,使用较低等级的LM4040D-2.5将所有电压偏置至2.5V,将允许使用所有ADC的数字输出范围−4096至+4095,同时为放大器留出足够的头部空间。

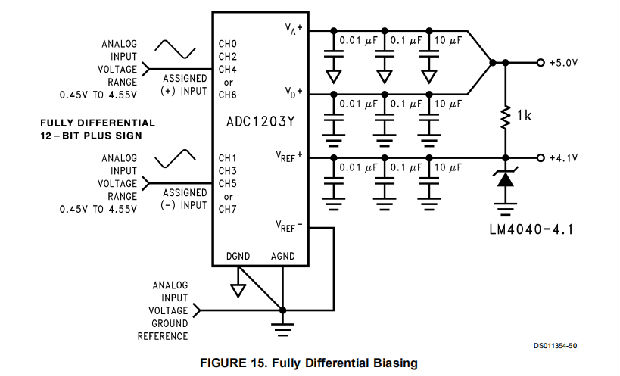

全差分操作如图15所示。这种情况下,一个LSB等于(4.1V/4096)=1 mV。

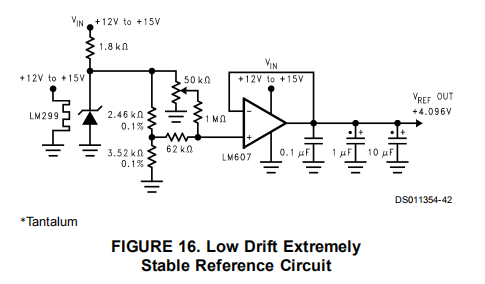

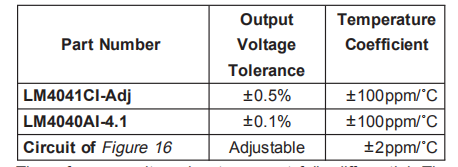

3.0参考电压

施加到VREF+和VREF的电压的差异限定了模拟输入跨距(在两个多路复用器输入之间施加的电压或施加到多路复用器输入和模拟接地之一的电压之间的差值),其中存在4095个正和4096个负码。驱动VREF+或VREF-的电压源必须具有非常低的输出阻抗和噪声。图16中的电路是适合与设备一起使用的非常稳定参考的示例。

ADC 12030/2/4/8可用于比率测量或绝对参考应用。在比率测量系统中,模拟输入电压与模数转换器参考电压成正比。当该电压为系统电源时,VREF+引脚连接至VA+,VREF-连接至接地。由于模拟输入电压和ADC参考电压同时移动,该技术放宽了系统参考稳定性要求。这将为给定的输入条件维护相同的输出代码。对于绝对精度,当模拟输入电压在非常特定的电压限制之间变化时,可以将时间和温度稳定的电压源连接到参考输入。通常,参考电压的大小需要对零参考电压引起的满标度误差进行初始调整。

以下是推荐的参考资料以及一些关键规范。

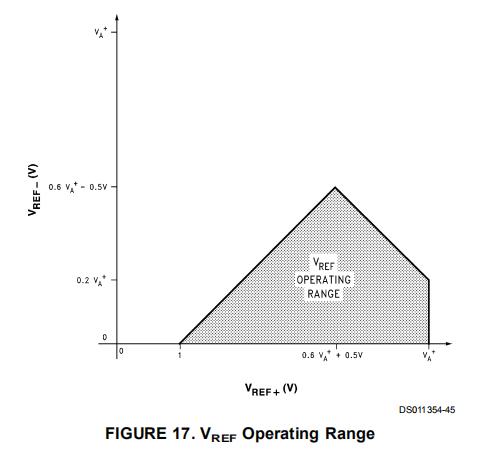

参考电压输入不是完全差分的。如果VREF+低于VREF-,ADC12030/2/4/8将不会生成正确的转换或比较。当VREF+和VREF-相差1V且始终保持接地和VA+之间时,将产生正确的转换。VREF共模范围(VREF++VREF-)/2限制为(0.1 x VA+)到(0.6 x VA+)。因此,当VA+=5V时,参考梯形图的中心不应低于0.5V或高于3.0V。图17是电压限制的图形表示VREF+和VREF-。

4.0模拟输入电压范围

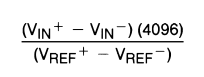

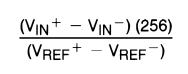

ADC12030/2/4/8的全差分ADC产生一个2的补码输出,该补码输出是通过使用下面所示的等式得到的:对于(12位)分辨率,输出码=

对于(8位)分辨率,输出代码=

如果上述公式的结果不是整数,则舍入到12位分辨率为-4096到4095之间的最接近整数值,8位分辨率为-256到255之间的最接近整数值。

示例如下表所示:

5.0输入电流

在采集窗口(tA)开始时,根据输入电压极性,充电电流流入或流出模拟输入引脚(a/DIN1和a/DIN2)。当A/DIN1与MUXOUT1绑定,A/DIN2与MUXOUT2绑定时,模拟输入引脚为CH0–CH7和COM。该输入电流的峰值将取决于实际输入电压、源阻抗和内部多路开关接通电阻。MUXOUT1与A/DIN1和MUXOUT2与A/DIN2相连,内部多路开关接通电阻通常为1.6 kΩ。A/DIN1和A/DIN2 mux导通电阻通常为750Ω。

6.0输入源电阻

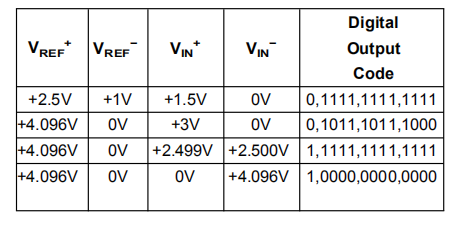

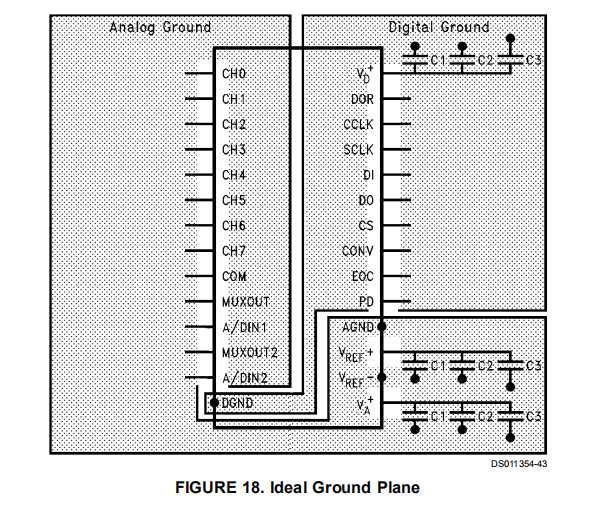

对于低阻抗电压源(<600Ω),在2微秒(10个CCLK周期,fC=5mhz)的S/H采集时间结束之前,输入充电电流将衰减到不会产生任何转换误差的值。对于高源阻抗,S/H的捕获时间可以增加到18或34个CCLK周期。对于较低的ADC分辨率和/或较慢的CCLK频率,S/H的捕获时间可以减少到6 CCLK周期。为了确定不同分辨率下具有特定源阻抗的采集时间所需的时钟周期(Nc)数量,可以使用以下方程式:

其中fC是转换时钟(CCLK)频率,单位为MHz,RS是外部源电阻,单位为kΩ。作为一个例子,以12位+符号的分辨率、5 MHz时钟频率和最大转换时间为34个转换时钟周期,ADC的模拟输入可以处理高达6 K的源阻抗。采集时间也可以延长,以补偿MUXOUT和A/DIN管脚之间连接的外部电路的稳定或响应时间。

采集时间tA由SCLK的下降沿开始,由CCLK的上升沿结束(见时序图)。如果SCLK和CCLK是异步的,则可以将一个额外的CCLK时钟周期插入到编程的同步捕获时间中。因此,对于非同步SCLK和CCLKs,采集时间将从转换变为转换。

7.0输入旁路电容

外部电容器(0.01μF–0.1μF)可连接在模拟输入引脚CH0–CH7和模拟接地之间,以过滤与长输入引线相关联的电感拾波引起的任何噪声。这些电容器不会降低转换精度。

8.0噪音

每个模拟多路复用器输入引脚的引线应尽可能短。这将使输入噪声和时钟频率耦合最小化,从而导致转换错误。输入滤波可以用来减少噪声源的影响。

9.0电源

VA+和VD+电源线上的噪声尖峰可能会导致转换错误;比较器将对噪声作出响应。ADC对自动调零或线性校正过程中出现的任何电源峰值都特别敏感。推荐的最小电源旁路电容器是10μF或更大的低电感钽电容器,与0.1μF单片陶瓷电容器并联。根据整体系统要求,可能需要更多或不同的旁路。VA+和VD+电源应使用单独的旁路电容器,并尽可能靠近这些引脚放置。

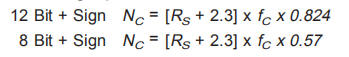

10.0接地

通过适当的接地技术,可以最大化ADC120 30/2/4/8的性能。其中包括使用单独的模拟和数字地面。数字接地平面置于处理数字信号的所有组件下,而模拟接地平面置于处理模拟信号的所有组件下。数字和模拟接地平面仅在一个点连接在一起,电源接地或ADC的引脚。这大大减少了接地回路和噪声的发生。

图18所示为ADC12038的理想接地平面布局以及旁路电容器的理想布局。图18所示的电路板布局使用三个旁路电容器:0.01μF(C1)和0.1μF(C2)表面贴装电容器和10μF(C3)钽电容器。

11.0时钟信号线隔离

ADC12030/2/4/8的性能通过将模拟输入/输出和参考信号导体尽可能地从传输时钟信号的导体布线到CCLK和SCLK引脚而得到优化。印刷电路板上可使用与时钟信号轨迹平行的接地轨迹,以减少模拟输入/输出引脚上的时钟信号干扰。

12.0校准周期

在电源、基准和时钟被给予足够的时间以在初始开启后稳定之后,需要开始校准周期。在校准周期期间,确定采样数据比较器的偏移电压以及任何线性和增益误差的校正值。这些值存储在内部RAM中,并在模数转换期间使用,以将整个满标度、偏移和线性误差降低到指定的限制。满标度误差通常随温度变化±0.4lsb,线性误差变化更小;因此,如果电源电压和环境温度没有显著变化(见典型性能特性中的曲线),通电后只需进行一次校准周期。

13.0自动归零循环

为了校正A/D的零点(偏移)误差的任何变化,可以使用自动调零周期。当环境温度或电源电压显著变化时,可能需要进行自动调零循环。(见典型性能特性中标题为“零误差变化与环境温度”和“零误差变化与电源电压”的曲线。)

14.0动态性能

许多应用要求A/D转换器对交流信号进行数字化,但标准的直流积分和微分非线性规范不能准确地预测交流输入信号下A/D转换器的性能。交流应用的重要规范反映了转换器数字化交流信号的能力,而不会产生明显的频谱误差,也不会给数字化信号增加噪声。动态特性,如信噪比(S/N)、信噪比+失真比(S/(N+D))、有效比特数、全功率带宽、孔径时间和孔径抖动等,是衡量A/D转换器性能的定量指标。

用快速傅立叶变换(FFT)方法可以测量A/D转换器的交流性能。将正弦波形应用于A/D转换器的输入端,然后对数字化波形进行变换。根据得到的FFT数据计算S/(N+D)和S/N,还可以得到谱图。S/N的典型值见电气特性表,S/(N+D)的频谱图见典型性能曲线。

A/D转换器的噪声和失真水平将随着输入信号的频率而变化,在较高的信号频率下会出现更多的失真和噪声。这可以在S/(N+D)与频率曲线中看到。这些曲线还将指示全功率带宽(S/(N+D)或S/N下降3db的频率)。

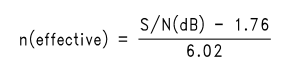

有效位数也可用于描述A/D的噪声性能。理想的A/D转换器将具有一定数量的量化噪声,由其分辨率决定,该量化噪声将产生由以下等式给出的最佳信噪比:

S/N=(6.02 x N+1.76)dB,其中N是A/D的分辨率,单位为位。

因此,实际a/D转换器的有效位可以通过以下方法找到:

作为一个例子,这个带有差分符号5V,10khz正弦波输入信号的设备通常具有78db的S/N,相当于12.6个有效位。

15.0 RS232串行接口

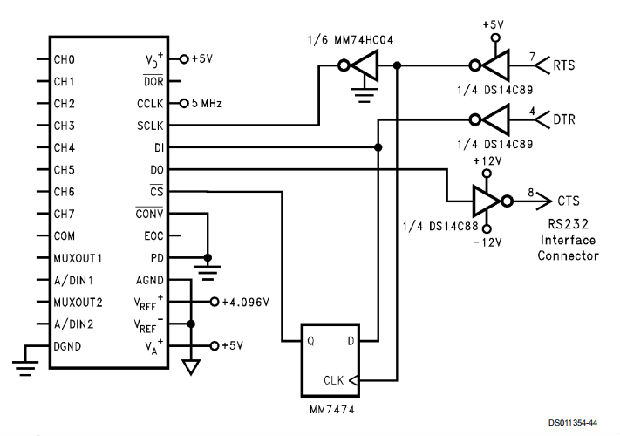

IBM和兼容PC的RS232接口示意图CTS RS232信号线通过电平转换器进行缓冲并连接到ADC12038的DI、SCLK和DO管脚,分别是。D触发器驱动CS控制线。

注:五、 V和Von的ADC12038都有0.01和0.1μF的芯片盖,以及10μF的钽盖。所有逻辑设备均采用0.1μF的电容器进行旁路。一个+丁+裁判+

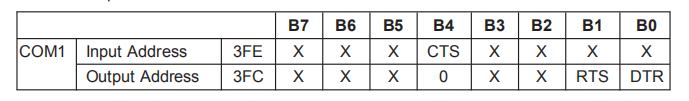

RS232端口的分配如下所示:

下一页显示了一个用Microsoft QuickBasic编写的示例程序。程序提示向A/D发送数据模式选择指令。这可以从前面显示的模式编程表中找到。数据应输入“1”和“0”,如表中所示,先输入DI0。接下来,程序提示输入编程模式选择指令所需的SCLK数。例如,要将所有“0”发送到A/D,选择CH0作为+输入,选择CH1作为-输入,选择12位转换,选择13位MSB第一数据输出格式(如果符号位未被前一条指令关闭)。这将需要13个SCLK周期,因为输出数据格式为13位。部件通电时无自动校准、无自动归零、10 CCLK采集时间、12位转换、带符号的数据输出、通电、先12位或13位MSB,以及用户模式。自动校准、自动归零、通电和断电指令不会更改这些默认设置。应遵循以下通电顺序:

1、运行程序;

2、在响应提示之前,将电源应用于ADC12038;

3、响应程序提示建议向ADC12038发出的第一条指令为自动校准(见第1.1节)。

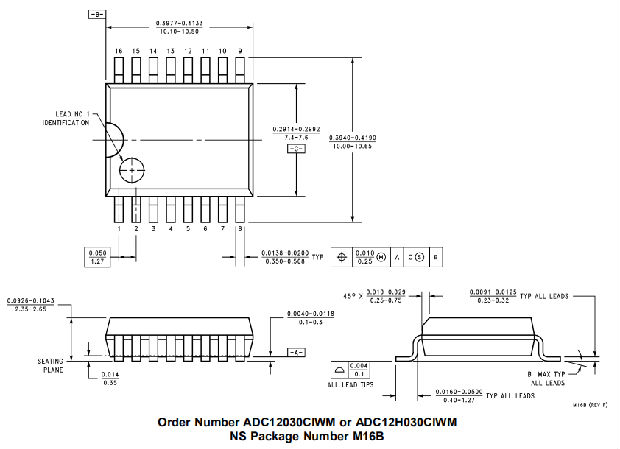

物理尺寸英寸(毫米),除非另有说明。