1596点击型号即可查看芯片规格书

特征

8个模数转换器(ADC)集成在一个软件包中;每通道93.5兆瓦模数转换器功率(50毫秒/秒);信噪比=73分贝(至奈奎斯特);ENOB=12位;SFDR=84 dBc(至奈奎斯特);良好的线性度;DNL=±0.4 LSB(典型);INL=?1.5 LSB(典型)串行LVDS(ANSI-644,默认);低功率,减少信号选项(类似于IEEE 1596.3);数据和帧时钟输出;325MHz,全功率模拟带宽;2V p-p输入电压范围;1.8V电源操作;串行端口控制;全芯片和单通道断电模式;柔性位定位;内置和自定义数字测试模式生成;可编程时钟和数据校准;可编程输出分辨率;待机模式。

应用

医学成像与无损超声;便携式超声和数字波束形成系统;正交无线电接收机;分集无线电接收机;磁带机;光网络;试验设备。

一般说明

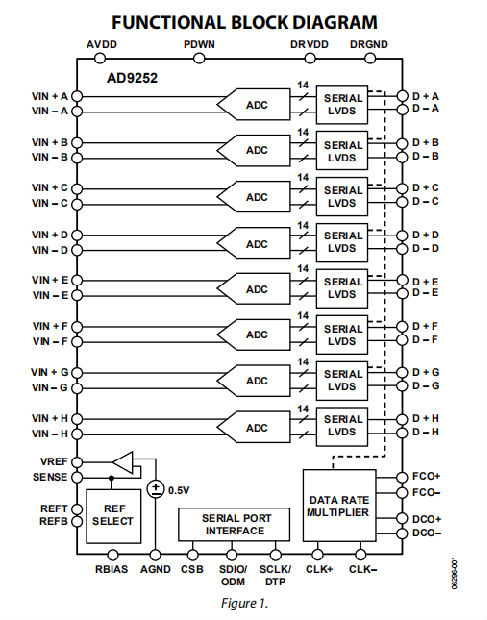

AD9252是一个8进制、14位、50毫秒/秒的ADC,具有片内采样保持电路,设计成本低、功耗低、体积小、使用方便。它以高达50msps的转换速率运行,在小封装尺寸至关重要的应用中,为卓越的动态性能和低功耗进行了优化。

ADC需要一个1.8v电源和LVPECL-/CMOS-/LVDS兼容的采样率时钟,以实现全性能工作。许多应用程序不需要外部引用或驱动程序组件。

ADC自动将采样率时钟乘以适当的LVDS串行数据速率。提供了用于捕获输出上的数据的数据时钟(DCO)和用于发送新输出字节的信令的帧时钟(FCO)。支持单个通道断电,当禁用所有通道时,通常功耗小于2 mW。

ADC包含多个功能设计,以最大限度地提高灵活性和最小化系统成本,如可编程时钟和数据对齐和可编程数字测试模式生成。可用的数字测试模式包括内置的确定性和伪随机模式,以及通过串行端口接口(SPI)输入的自定义用户定义的测试模式。

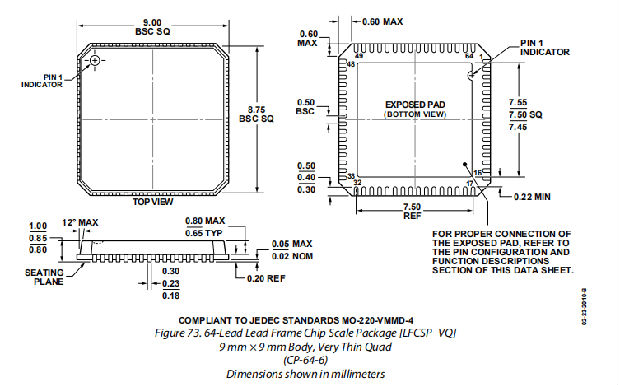

AD9252采用符合RoHS标准的64铅LFCSP。规定在工业温度范围内为-40°C至+85°C。

产品亮点

1、占地面积小。一个小包裹里装着八个adc。

2、低功率93.5兆瓦每通道在50毫秒每秒。

3、使用方便。数据时钟输出(DCO)工作频率高达350MHz,支持双数据速率(DDR)操作。

4、用户灵活性。SPI控制提供了广泛的灵活特征以满足特定的系统要求。

5、Pin兼容系列。这包括AD9212(10位)和AD9222(12位)。

操作理论

AD9252体系结构包括一个流水线ADC,分为三个部分:4位第一级、8个1.5位级和3位闪存。每个阶段都提供足够的重叠,以更正前一阶段中的闪存错误。在数字校正逻辑中,来自每个级的量化输出被组合成最终的14位结果。流水线架构允许第一个阶段使用一个新的输入样本操作,而其余阶段使用前面的样本操作。采样发生在时钟的上升沿。

管道的每一级(不包括最后一级)由连接到开关电容DAC的低分辨率flash ADC和级间剩余放大器(例如,乘法数模转换器(MDAC))组成。剩余放大器放大重建的DAC输出和下一级流水线中的flash输入之间的差异。每个阶段使用一位冗余,以便于对闪存错误进行数字校正。最后一级由一个flash ADC组成。

输出暂存块对齐数据、更正错误并将数据传递到输出缓冲区。然后将数据序列化并与帧和数据时钟对齐。

模拟输入注意事项

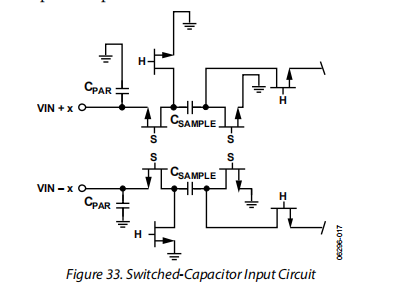

AD9252的模拟输入是设计用于处理差分输入信号的差分开关电容电路。该电路在保持良好性能的同时,还可以支持较宽的共模范围。中间电源的输入共模电压使信号相关误差最小化,并提供最佳性能。

时钟信号在采样模式和保持模式之间交替切换输入电路(见图33)。当输入电路切换到采样模式时,信号源必须能够在半个时钟周期内为采样电容器充电并稳定下来。与每个输入串联的一个小电阻有助于降低从驱动源的输出级注入的峰值瞬态电流。此外,可以将低Q电感器或铁氧体磁珠放置在输入的每一个支路上,以减少模拟输入端的高差分电容,从而实现ADC的最大带宽。在高频驱动转换器前端时,需要使用低Q电感或铁氧体磁珠。可以在输入端放置一个并联电容器或两个单端电容器,以提供匹配的无源网络。这最终会在输入端创建一个低通滤波器,以限制不需要的宽带噪声。更多信息,请参阅AN-742应用说明,开关电容ADC的频域响应;AN-827应用说明,将放大器与开关电容ADC接口的谐振方法;以及模拟对话文章“宽带A/D转换器的变压器耦合前端”(第39卷,2005年4月)。一般来说,精确值取决于应用程序。

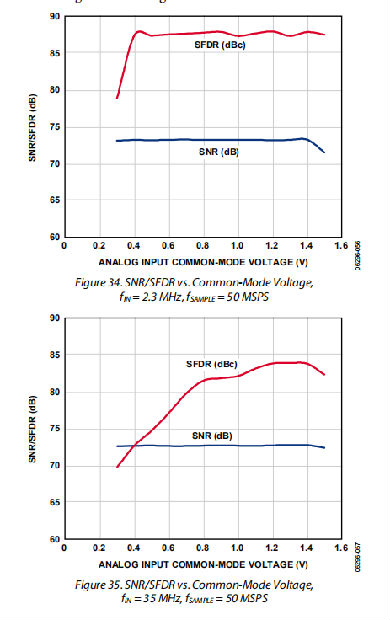

AD9252的模拟输入没有内部直流偏置。因此,在交流耦合应用中,用户必须在外部提供这种偏压。将设备设置为V=AVDD/2以获得最佳性能,但设备可以在更宽的范围内工作,并具有合理的性能,如图34和图35所示。

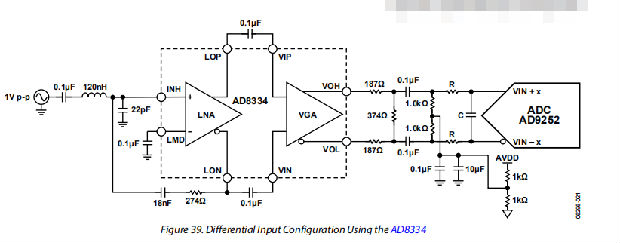

为了获得最佳的动态性能,驱动VIN+x和VIN-x的源阻抗应该匹配,以便共模调节误差是对称的。这些误差通过ADC的共模抑制而减小。内部参考缓冲器分别产生正参考电压和负参考电压REFT和REFB,它们定义了ADC核心的跨距。参考缓冲器的输出共模设置为“中电源”,参考电压和参考电压范围定义为:

从这些方程可以看出,REFT和REFB电压是关于中间供电电压对称的,根据定义,输入跨距是VREF电压值的两倍。

通过将ADC设置为差分配置中的最大跨度来实现最大SNR性能。在AD9252的情况下,可用的最大输入跨度为2V p-p。

差分输入配置

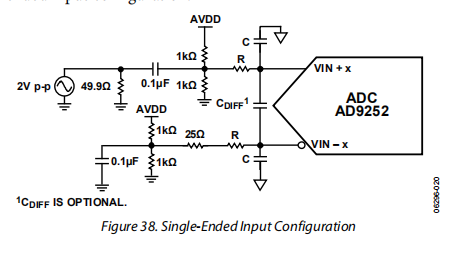

有几种方法可以主动或被动地驱动AD9252;但是,通过差分驱动模拟输入可以获得最佳性能。例如,使用AD8334差动驱动器来驱动AD9252,为基带应用提供了优异的性能和灵活的ADC接口(见图39)。这种配置通常用于医疗超声系统。

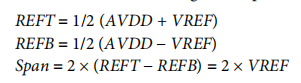

对于信噪比是一个关键参数的应用,差动变压器耦合是推荐的输入配置(见图36和图37),因为大多数放大器的噪声性能不足以达到AD9252的真实性能。无论配置如何,并联电容器C的值取决于输入频率,可能需要减小或移除。

单端输入配置

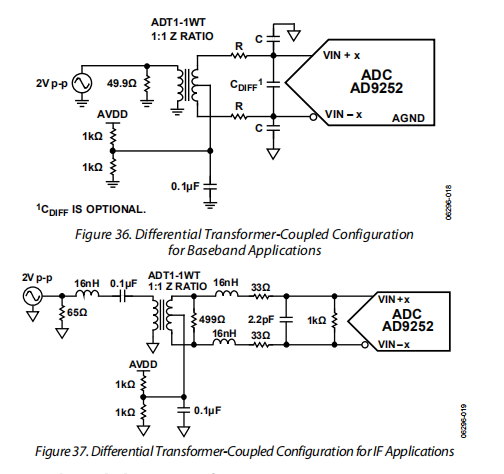

在成本敏感的应用中,单端输入可以提供足够的性能。在这种配置中,由于输入共模振荡过大,SFDR和失真性能下降。如果应用程序需要单端输入配置,请确保每个输入上的源阻抗匹配良好,以实现最佳性能。在终止VIN-x引脚时,2 V p-p的满标度输入仍然可以应用于ADC的VIN+x引脚。图38详细说明了典型的单端输入配置。

时钟输入注意事项

为获得最佳性能,AD9252采样时钟输入(CLK+和CLK-)应使用差分信号计时。该信号通常通过变压器或电容器交流耦合到CLK+和CLK-引脚。这些引脚内部偏压,不需要额外偏压。

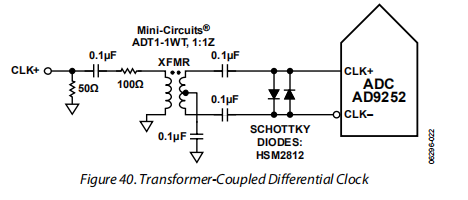

图40显示了对AD9252进行计时的首选方法。低抖动时钟源通过射频变压器从单端转换为差分。跨次级变压器的背靠背肖特基二极管限制到AD9252到大约0.8 V p p差的时钟偏移。这有助于防止时钟的大电压波动通过AD9252的其他部分,并保持信号的快速上升和下降时间,这对低抖动性能至关重要。

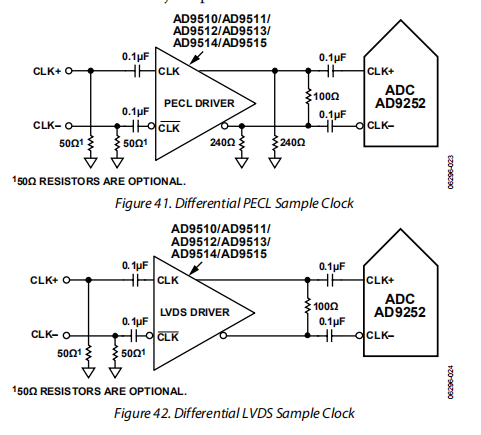

另一种选择是将差分PECL信号与采样时钟输入引脚进行交流耦合,如图41所示。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515系列时钟驱动程序具有出色的抖动性能。

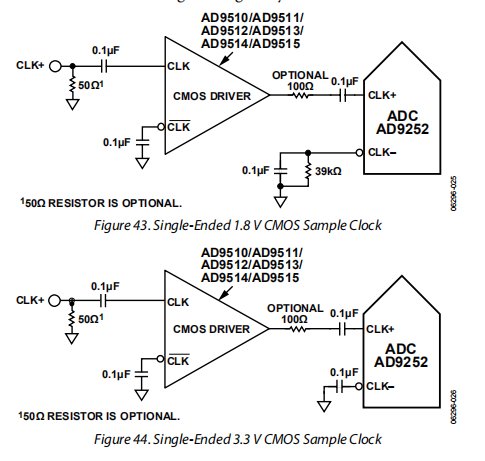

在某些应用中,可以使用单端CMOS信号驱动采样时钟输入。在这种应用中,CLK+应直接从CMOS栅极驱动,CLK引脚应通过与39 kΩ电阻器并联的0.1μF电容器旁路接地(见图43)。虽然CLK+输入电路电源是AVDD(1.8 V),但该输入被设计为承受高达3.3 V的输入电压,使得驱动逻辑电压的选择非常灵活。

时钟占空比注意事项

典型的高速adc使用两个时钟边缘来产生各种内部定时信号。因此,这些adc可能对时钟占空比敏感。通常,时钟占空比需要5%的公差,以保持动态性能特性。AD9252包含一个占空比稳定器(DCS),它对非采样边缘进行重定时,提供具有50%标称占空比的内部时钟信号。这允许在不影响AD9252的性能的情况下有广泛的时钟输入占空比。当DCS开启时,噪声和失真性能在很大的占空比范围内几乎是平坦的。但是,有些应用可能需要关闭DCS功能。如果是这样,请记住,在此模式下操作时,动态范围性能可能会受到影响。有关使用此功能的详细信息,请参阅内存映射部分。

占空比稳定器使用延迟锁定环(DLL)来创建非采样边缘。因此,对采样频率的任何改变都需要大约八个时钟周期,以允许DLL获取并锁定到新的速率。

时钟抖动注意事项

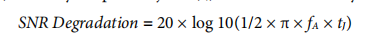

高速、高分辨率的adc对时钟输入的质量非常敏感。给定输入频率下的信噪比衰减(fA)仅由于孔径抖动(tJ)可以通过:

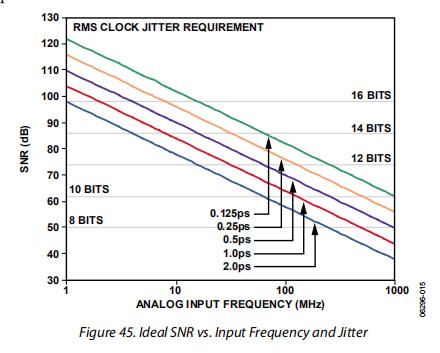

在这个方程中,均方根孔径抖动表示所有抖动源的均方根,包括时钟输入、模拟输入信号和ADC孔径抖动规范。如果欠采样应用对抖动特别敏感(见图45)。一个J型

在孔径抖动可能影响AD9252的动态范围的情况下,时钟输入应被视为模拟信号。时钟驱动器的电源应与ADC输出驱动器电源分开,以避免用数字噪声调制时钟信号。低抖动晶体控制振荡器是最好的时钟源。如果时钟是从其他类型的源(通过选通、除法或其他方法)生成的,则应在最后一步由原始时钟重定时。

请参阅AN-501应用说明和AN-756应用说明,以获取有关ADC的抖动性能的更深入信息。

功耗和掉电模式

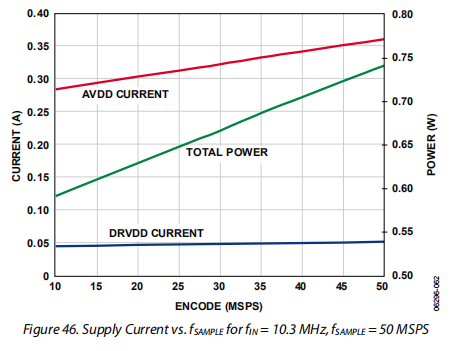

如图46所示,AD9252所消耗的功率与其采样率成正比。数字功耗变化不大,因为它主要由DRVDD电源和LVDS输出驱动器的偏置电流决定。

通过断言PDWN引脚高,AD9252被置于断电模式。在这种状态下,ADC通常耗散11mw。在断电期间,LVDS输出驱动器被置于高阻抗状态。当PDWN引脚拉低时,AD9252返回正常工作模式。该引脚的电压公差为1.8V和3.3V。

在断电模式下,通过关闭参考、参考缓冲器、锁相环和偏置网络来实现低功耗。REFT和REFB上的去耦电容器在进入断电模式时放电,恢复正常工作时必须重新充电。因此,唤醒时间与断电模式下所用的时间相关:较短的周期会按比例缩短唤醒时间。推荐的0.1μF和4.7μF去耦电容在RFT和ReFB上,需要大约1秒来完全放电参考缓冲去耦电容器,并且需要大约375μs来恢复全操作。

使用SPI时,还有其他几种断电选项。用户可以单独关闭每个通道或将整个设备置于待机模式。后一个选项允许用户在需要快速唤醒时间(~600 ns)时保持内部PLL通电。有关使用这些功能的详细信息,请参阅内存映射部分。

数字输出和定时

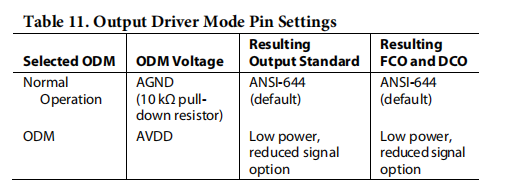

默认情况下,AD9252差分输出在通电时符合ANSI-644 LVDS标准。这可以通过SDIO/ODM管脚或SPI更改为低功耗、低信号选项(类似于IEEE 1596.3标准)。该LVDS标准可以进一步降低设备的总功耗。

36兆瓦。有关更多信息,请参阅SDIO/ODM管脚部分或内存映射部分中的表16。LVDS驱动电流在芯片上导出,并将每个输出的输出电流设置为标称3.5ma。放置在LVDS接收器输入端的100Ω差动终端电阻器导致接收器处的标称350 mV摆动。

AD9252 LVDS输出便于与定制ASIC和FPGAs中的LVDS接收器接口,以在噪声环境中获得优异的交换性能。建议采用单点对点网络拓扑结构,并尽可能靠近接收器放置100Ω终端电阻。如果没有远端接收器终端或差分跟踪路由不良,

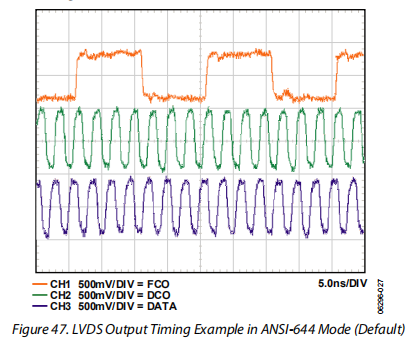

可能导致计时错误。为了避免这种定时误差,建议记录道长度不超过24英寸,并且差分输出记录道应保持在一起且长度相等。当AD9252与适当长度和位置的记录道一起使用时,FCO和数据流的示例如图47所示。

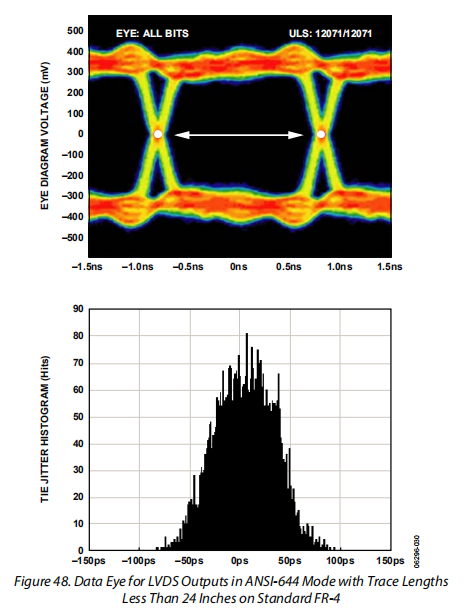

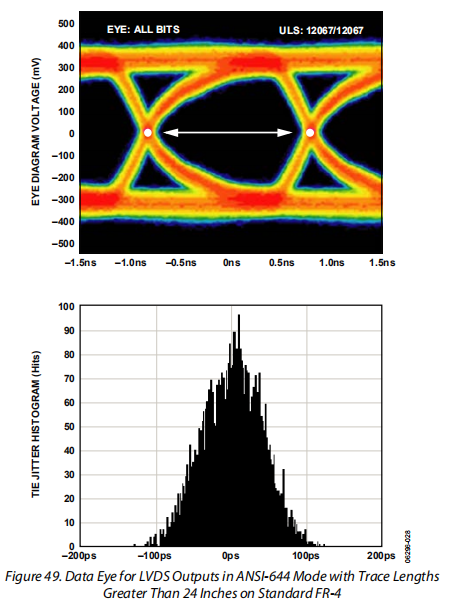

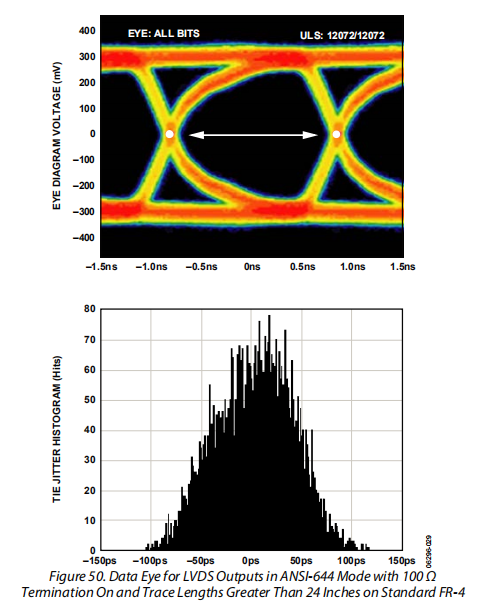

图48显示了使用ANSI-644标准(默认)数据眼和标准FR-4材料上跟踪长度小于24英寸的时间间隔误差(TIE)抖动直方图的LVDS输出示例。图49显示了标准FR-4材料上超过24英寸的痕迹长度示例。注意,领带抖动直方图反映了当边缘偏离理想位置时,数据眼开度的降低。当轨迹长度超过24英寸时,用户有责任确定波形是否满足设计的时间预算。额外的SPI选项允许用户进一步增加所有八个输出的内部终端(增加电流),以驱动更长的跟踪长度(见图50)。即使这会在数据边上产生更尖锐的上升和下降时间,并且不太容易出现位错误,但使用此选项时,DRVDD电源的功耗会增加。此外,请注意图50中的直方图已经改进。

如果由于负载不匹配而需要增加DCO±和FCO±输出的驱动器强度,寄存器0x15允许用户将驱动器强度增加2×。为此,首先在寄存器0x05中设置适当的位。请注意,此功能不能与寄存器0x15中的位4和位5一起使用。位4和位5优先于此功能。有关更多详细信息,请参阅内存映射部分。

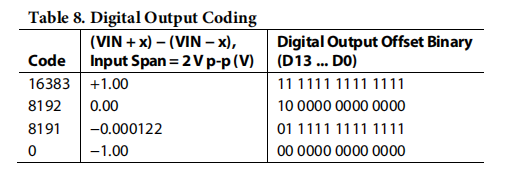

图50。ANSI-644模式下LVDS输出的数据眼,在标准FR-4上,100Ω终端打开,跟踪长度大于24英寸默认情况下,输出数据的格式为偏移二进制。输出编码格式的示例见表8。要将输出数据格式更改为两个补码,请参阅内存映射部分。

来自每个ADC的数据被序列化并在单独的通道上提供。每个串行流的数据速率等于采样时钟速率的14位,最大为700 Mbps(14位×50 MSPs=700 Mbps)。最低的典型转换率为10毫秒/秒。然而,如果特定应用需要更低的采样率,则可以通过SPI设置PLL,以允许低至5 MSPS的编码速率。有关启用此功能的信息,请参阅内存映射部分。

提供两个输出时钟,以协助从AD9252捕获数据。DCO用于对输出数据进行时钟,等于采样时钟(CLK)速率的七倍。数据从AD9252中打卡,必须在上升和支持双数据速率(DDR)捕获的DCO的下降沿。FCO用于发出新输出字节开始的信号,它等于采样时钟速率。有关更多信息,请参见图2中所示的时序图。

当使用SPI时,可以相对于数据边缘以60°增量调整DCO相位。这允许用户在需要时优化系统计时边距。如图2所示,默认DCO+和DCO-定时相对于输出数据边缘为90°。

也可以从SPI启动8位、10位和12位串行流。这允许用户实现不同的串行流来测试设备与低分辨率和高分辨率系统的兼容性。将分辨率更改为8位、10位或12位串行流时,数据流会缩短。12位示例见图3。

当使用SPI时,数据输出可以从其标称状态反转。这不应与将串行流反转为LSB第一模式相混淆。在默认模式下,如图2所示,MSB是数据输出串行流中的第一个。然而,这可以被颠倒,使得LSB在数据输出串行流中处于第一位(参见图4)。

有12个数字输出测试模式选项可通过SPI启动。此功能在验证接收器捕获和定时时非常有用。有关可用的输出位排序选项,请参阅表9。有些测试模式有两个连续的顺序词,可以根据所选择的测试模式以不同的方式进行交替。请注意,有些模式不符合“数据格式选择”选项。此外,可以在0x19、0x1A、0x1B和0x1C寄存器地址中分配客户用户定义的测试模式。除了PN序列短和PN序列长之外,所有的测试模式选项都可以支持8到14位的字长,以便验证对接收器的数据捕获。

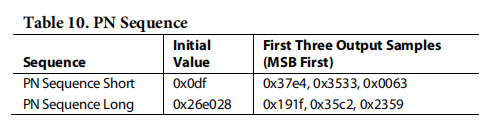

PN序列短模式产生伪随机比特序列,每2-1或511比特重复一次。有关PN序列及其生成方式的说明,请参见ITU-T 0.150(05/96)标准的第5.1节。唯一的区别是起始值必须是一个特定的值,而不是所有的1(初始值见表10)。

PN序列长模式产生伪随机比特序列,每2-1或8388607比特重复一次。有关PN序列及其生成方式的说明,请参见ITU-T 0.150(05/96)标准的第5.6节。唯一的区别是,起始值必须是特定的值,而不是所有的1(初始值见表10),并且AD9252根据ITU标准反转比特流。

SDIO/ODM引脚

SDIO/ODM管脚用于不需要SPI模式操作的应用程序。如果该引脚和CSB引脚在设备通电期间连接到AVDD,则该引脚可以启用低功率、减小信号选项(类似于IEEE1596.3减小范围链路输出标准)。只有当数字输出跟踪长度距离LVDS接收器小于2英寸时,才应使用此选项。使用此选项时,FCO、DCO和输出功能正常,但所有通道的LVDS信号摆动从350 mV p-p减少到200 mV p-p,允许用户进一步降低DRVDD电源的功率。

对于不使用此管脚的应用,应将其系紧。在这种情况下,设备引脚可以保持打开,30 kΩ内部下拉电阻器将此引脚拉低。该引脚仅允许1.8V电压。如果应用要求从3.3 V逻辑电平驱动该引脚,则将1 kΩ电阻器与该引脚串联以限制电流。

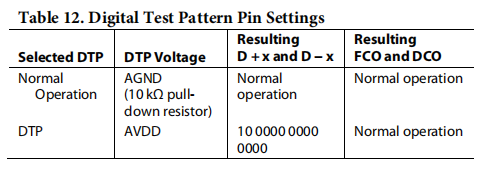

SCLK/DTP引脚

SCLK/DTP引脚用于不需要SPI模式操作的应用程序。如果在设备通电期间,此引脚和CSB引脚保持高电平,则可以启用单个数字测试模式。当SCLK/DTP与AVDD相连接时,ADC通道输出偏移如下模式:10 0000 0000 0000。FCO和DCO功能正常,所有通道都切换出可重复的测试模式。此模式允许用户在FCO、DCO和输出数据之间执行定时对齐调整。对于正常工作,该引脚应通过10 kΩ电阻器连接到AGND。该引脚的电压公差为1.8V和3.3V。

当从SPI端口发出命令时,还可以观察到其他和自定义的测试模式。有关可用选项的信息,请参阅内存映射部分。

CSB引脚

对于不需要SPI模式操作的应用程序,CSB pin应绑定到AVDD。通过将CSB设为high,将忽略所有SCLK和SDIO信息。该引脚为1.8 V和3.3耐电压。

RBIAS销

要设置ADC的内部核心偏置电流,在RBIAS引脚和接地之间放置一个名义上等于10.0 kΩ的电阻器。电阻电流在芯片上导出,并将ADC的AVDD电流设置为50 MSPS时的标称360毫安。因此,必须对该电阻器使用至少1%的公差,以实现一致的性能。

电压基准

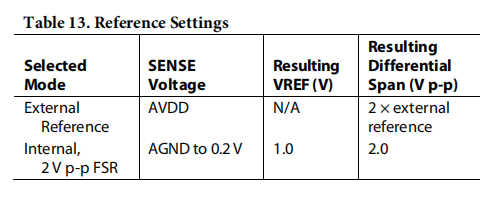

AD9252内置了稳定、准确的0.5V电压基准。这是通过系数2在内部获得的,将VREF设置为1.0V,这将导致全刻度差分输入范围为2V p-p。VREF默认在内部设置;但是,VREF管脚可以用1.0V参考电压从外部驱动提高准确性。

将去耦电容器应用于VREF、REFT和REFB引脚时,使用陶瓷低ESR电容器。这些电容器应靠近ADC引脚,并与AD9252位于同一层PCB上。AD9252参考引脚的推荐电容值和配置如图51所示。

内部参考操作

AD9252内的比较器检测传感管脚处的电位并配置基准。如果传感器接地,参考放大器开关连接到内部电阻分压器(见图51),将VREF设置为1V。

REFT和REFB引脚根据参考配置确定其ADC核心的输入范围。对于内部或外部参考配置,ADC的模拟输入满标度范围等于参考引脚电压的两倍。

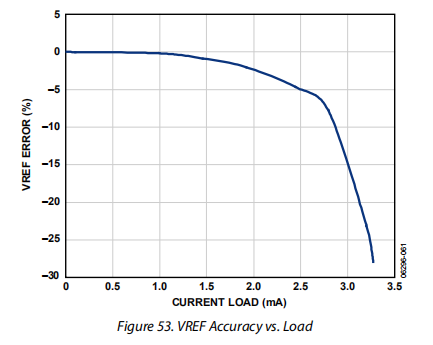

如果AD9252的引用用于驱动多个为了改善增益匹配,必须考虑其他转换器的参考负载。图53描述了负载对内部参考电压的影响。

外部参照操作

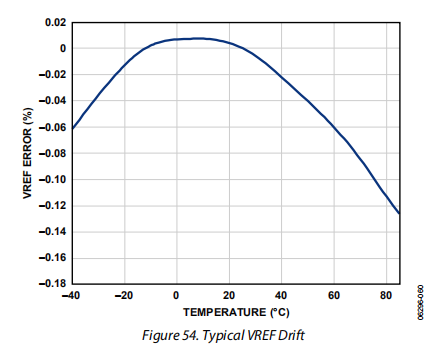

可能需要使用外部基准来提高ADC的增益精度或改善热漂移特性。图54显示了1V模式下内部基准的典型漂移特性。

当检测管脚绑定到AVDD时,内部引用被禁用,允许使用外部引用。外部参考负载相当于6 kΩ负载。内部参考缓冲器为ADC核心生成正负满标度参考(REFT和REFB)。因此,外部参考电压必须限制在1.0V的标称电压范围内。

串行端口接口(SPI)

AD9252串行端口接口允许用户通过ADC内部提供的结构化寄存器空间为特定功能或操作配置转换器。这可以为用户提供额外的灵活性和定制性,这取决于应用程序。地址通过串行端口访问,可以通过端口写入或读取。内存被组织成字节,可以进一步划分为字段,如内存映射部分所述。详细的操作信息可以在AN-877应用说明中找到,通过SPI连接到高速ADC。

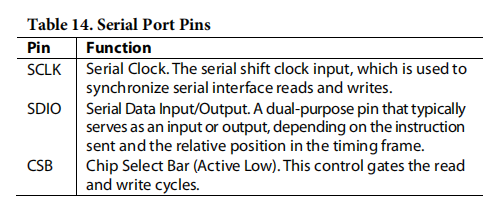

三个管脚定义SPI:SCLK、SDIO和CSB管脚(见表14)。SCLK引脚用于同步显示给ADC的读写数据。SDIO引脚是一个双用途引脚,允许数据发送到内部ADC内存映射寄存器并从中读取。CSB引脚是一个激活的低控制,启用或禁用读写周期。

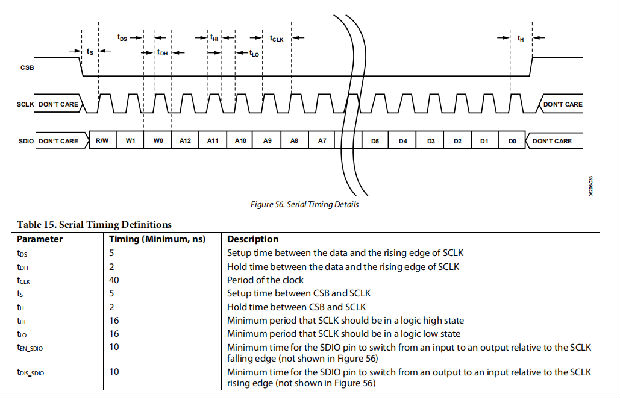

CSB的下降沿与SCLK的上升沿一起决定帧序列的开始。在指令阶段,发送16位指令,然后是一个或多个数据字节,由位字段W0和位字段W1确定。序列定时及其定义的示例可以在图56和表15中找到。

在正常操作期间,CSB用于向设备发送信号,表示要接收和处理SPI命令。当CSB降低时,设备处理SCLK和SDIO以执行指令。正常情况下,CSB保持在低位,直到通信周期完成。然而,如果连接到一个慢的设备上,CSB可以在字节之间调高,从而允许较老的微控制器有足够的时间将数据传输到移位寄存器中。当传输一个、两个或三个字节的数据时,可以暂停CSB。

当W0和W1被设置为11时,设备进入流模式并继续处理数据(读或写),直到CSB被设置为高结束通信周期。这允许在不需要额外指令的情况下完成内存传输。

无论采用哪种模式,如果在字节传输过程中CSB处于高位,SPI状态机将重置,设备将等待新的指令。

除了操作模式之外,SPI端口配置还影响AD9252的操作方式。对于不需要控制端口的应用程序,可以将CSB线系紧并保持在高位。这会将其余的SPI管脚放入其二级模式,如SDIO/ODM管脚和SCLK/DTP管脚部分中所定义的。CSB也可以低绑以启用2线模式。当CSB连接过低时,SCLK和SDIO是通信所需的唯一管脚。尽管设备在通电期间是同步的,但用户在使用此模式时应确保串行端口与CSB线保持同步。在2线模式下操作时,建议仅使用1、2或3字节传输。没有激活的CSB线路,可以输入流模式但不退出。除了字长之外,指令阶段还确定串行帧是读还是写操作,从而允许串行端口用于对芯片进行编程和读取片上存储器的内容。如果指令是回读操作,则执行回读会导致SDIO引脚在串行帧的适当点从输入变为输出。数据可以在MSB或LSB第一模式下发送。MSB first mode是通电时的默认模式,可以通过调整配置寄存器进行更改。有关此功能和其他功能的更多信息,请参阅AN-877应用说明,通过SPI连接到高速ADC。

硬件接口

表14中描述的管脚构成了用户编程设备和AD9252串行端口之间的物理接口。使用SPI时,SCLK和CSB管脚用作输入。SDIO管脚是双向的,在写入阶段作为输入,在回读期间作为输出。

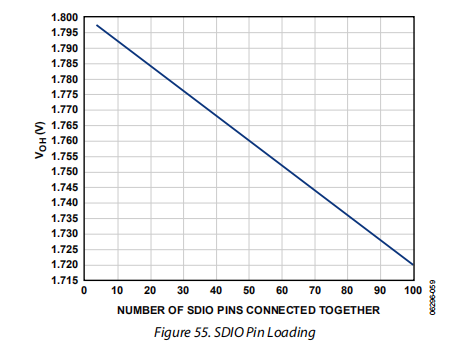

如果多个SDIO管脚共用一个连接,则应注意确保满足适当的V电平。假设每个AD9252的负载相同,图55显示了可以连接在一起的SDIO管脚数和产生的VOH电平。

该接口足够灵活,可由串行PROM或PIC微控制器控制,为用户提供替代全SPI控制器的替代方法来编程ADC(参见AN-812应用说明)。

如果用户选择不使用SPI,则在设备通电期间,当CSB被绑定到AVDD时,这些双功能管脚提供其辅助功能。请参阅“操作原理”一节,以了解有关可固定销功能的详细信息支持在SPI管脚上。

内存映射

读取内存映射表

内存映射寄存器表(表16)中的每一行都有八个地址位置。内存映射分为三个部分:芯片配置寄存器映射(地址0x00到地址0x02)、设备索引和传输寄存器映射(地址0x04、地址0x05和地址0xFF)和ADC功能寄存器映射(地址0x08到地址0x22)。

内存映射最左边的列表示寄存器地址号;默认值显示在最右边的第二列中。第7位列是给定的默认十六进制值的开始。例如,地址0x09(时钟寄存器)的默认值为0x01,表示二进制的位7=0、位6=0、位5=0、位4=0、位3=0、位2=0、位1=0和位0=1或0000 0001。此设置是工作循环稳定器在接通状态下的默认设置。通过将0写入该地址的位0,然后将0x01写入寄存器0xFF(传输位),占空比稳定器关闭。使用传输位跟随每个写入序列以更新SPI寄存器是很重要的。除寄存器0x00、寄存器0x04、寄存器0x05和寄存器0xFF外,所有寄存器都用主从锁存器进行缓冲,并要求写入传输位。有关此功能和其他功能的更多信息,请参阅AN-877应用说明,通过SPI连接到高速ADC。

保留位置

除非写入本数据表中建议的默认值,否则不应写入未定义的内存位置。值标记为0的地址应被视为保留地址,并在通电期间将0写入其寄存器。

默认值

当AD9252从复位中出来时,临界寄存器被预加载默认值。这些值如表16所示,其中X表示未定义的特征。

逻辑电平

对各种寄存器的解释如下:“位被设置”与“位被设置为逻辑1”或“为位写入逻辑1”同义。“清除位”与“位被设置为”同义,“逻辑0”或“为位写入逻辑0”。

应用程序信息

设计指南

在开始AD9252作为一个系统的设计和布局之前,建议设计者熟悉这些指南,其中讨论了特定管脚所需的特殊电路连接和布局要求。

电源和接地建议

将电源连接到AD9252时,建议使用两个单独的1.8V电源:一个用于模拟(AVDD)和一个用于数字(DRVDD)。如果只有一个电源可用,则应首先将其连接至AVDD,然后用铁氧体磁珠或滤波器扼流圈将其分接并隔离,然后再使用DRVDD的去耦电容器。用户可以使用多个不同的去耦电容器来覆盖高频和低频。这些电容器应靠近PC板级的入口点,并靠近跟踪长度最小的部件。

使用AD9252时,单个PC板接地平面应足够。通过对PC板的模拟、数字和时钟部分进行适当的解耦和智能分区,可以轻松实现最佳性能。

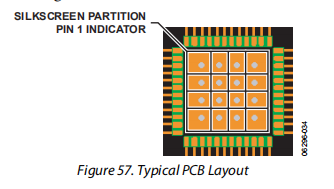

暴露桨叶热段塞建议

要求ADC底部的外露开关板连接到模拟接地(AGND),以获得AD9252的最佳电气和热性能。PCB上的外露连续铜平面应与AD9252外露拨杆的针脚0匹配。铜平面应该有几个通孔,以实现最低可能的电阻热路径,以便散热通过PCB底部。这些通孔应填充或塞住焊料。为了最大化ADC和PCB之间的覆盖和粘附,通过将PCB上的丝网覆盖成几个均匀的部分来分割连续的铜平面。这在回流过程中在ADC和PCB之间提供了多个连接点,而使用一个没有分区的连续平面只保证了一个连接点。PCB布局示例见图57。有关芯片级封装的封装和PCB布局的详细信息,请参阅AN-772应用说明,引线框架芯片级封装(LFCSP)的设计和制造指南。

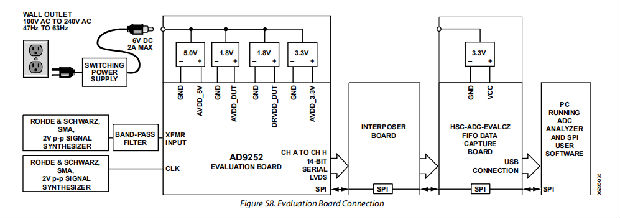

评估委员会

AD9252评估板提供在各种模式和配置下操作ADC所需的所有支持电路。转换器可以使用变压器(默认)或AD8334驱动器进行差动驱动。ADC也可以单端驱动。提供单独的电源引脚,以将DUT与AD8334的驱动电路隔离。可以通过改变不同跳线的连接来选择每个输入配置(参见图62至图66)。图58显示了用于评估AD9252交流性能的典型工作台特性设置。用于模拟输入和时钟的信号源具有非常低的相位噪声(<1ps rms抖动)是实现转换器最佳性能的关键。为了达到规定的噪声性能,还需要对模拟输入信号进行适当的滤波,以消除谐波,降低输入端的集成或宽带噪声。

请参阅图62至图72,以获取完整的示意图和布局图,这些示意图和布局图演示了应在系统级应用的路由和接地技术。

电源

这个评估板有一个壁挂式开关电源,提供6 V,2最大输出。以47赫兹至63赫兹的频率将电源连接至额定100伏交流电至240伏交流电墙壁插座。电源的另一端是一个2.1毫米内径的插孔,连接到P701的PCB。一旦在PC板上,6V电源在连接到三个低电压降线性稳压器之前被熔合和调节,这三个线性稳压器为板上的各个部分提供适当的偏压。

在非故障条件下操作评估板时,可以拆下L701至L704以断开开关电源。这使得用户可以分别对电路板的每个部分进行偏压。使用P702为每个部分连接不同的电源。AVDD U DUT和DRVDD U DUT至少需要一个1.8V电源;但是,建议对模拟和数字信号使用单独的电源,并且每个电源的电流容量为1A。要使用VGA选项操作评估板,需要单独的5.0V模拟电源(AVDD U 5V)。要使用SPI和备用时钟选项操作评估板,除了其他电源外,还需要单独的3.3 V模拟电源(AVDD U 3.3 V)。

输入信号

当将时钟和模拟源连接到评估板时,使用具有低相位噪声的清洁信号发生器,如罗德和施瓦茨SMA或HP864 4信号发生器或等效电路,以及1米、屏蔽、RG-58、50Ω同轴电缆。从ADC规格表中输入所需的频率和振幅。通常,大多数模拟设备公司,评估板可以接受大约2.8伏的P P或13的DBM正弦波输入时钟。连接模拟输入源时,建议使用带50Ω终端的多极窄带带通滤波器。TTE、Allen Avonics和K&L微波公司提供了此类带通滤波器的良好选择。如果可能,滤波器应直接连接到评估板。

输出信号

默认设置使用模拟设备HSC-ADC-FIFO5INTZ与模拟设备标准双通道FIFO数据采集板(HCS-ADC-EVALCZ)接口。八个通道中的两个可以同时评估。有关这些板的通道设置和可选设置的更多信息,请访问/FIFO。

默认操作和跳线选择设置

以下是AD9252版本上允许的默认和可选设置或模式的列表。评估委员会。

(1)、电源:在47 Hz至63 Hz的额定100 V ac至240 V ac墙壁插座和P701之间连接随评估套件提供的开关电源。

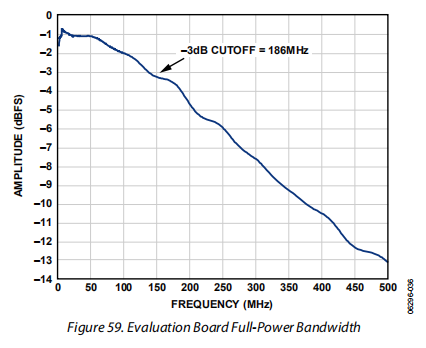

(2)、AIN:评估板是为变压器耦合模拟输入设置的,具有150 MHz带宽的最佳50Ω阻抗匹配(见图59)。为了获得更多的带宽响应,可以改变或移除模拟输入端的差动电容。模拟输入的共模由变压器的中心抽头或AVDD-DUT/2发展而来。

(3)、VREF:VREF通过将传感销接地R317设置为1.0V。这导致ADC在2.0 V p-p满标度范围内工作。评估板上还包括使用ADR510的单独外部参考选项。填充R312和R313,然后拆下C307。电压参考章节中说明了VREF选项的正确使用。

(4)、RBIA:RBIA默认设置为10 kΩ(R301)接地,用于设置ADC核心偏置电流。

时钟:默认的时钟输入电路来自一个简单的变压器耦合电路,该电路使用高带宽1:1阻抗比变压器(T401),为时钟路径添加非常低的抖动。时钟输入端为50Ω,交流耦合以处理单端正弦波类型的输入。变压器将单端输入转换为差分信号,该差分信号在输入ADC时钟输入之前被截断。

差分LVPECL时钟也可用于使用AD9515(U401)的ADC输入。用0Ω电阻填充R406和R407,然后拆下R215和R216以断开默认时钟路径输入。此外,用0.1μF电容器填充C205和C206,并移除C409和C410断开默认时钟路径输出。AD9515有许多针可捆扎选项,设置为默认操作模式。有关这些选项和其他选项的详细信息,请参阅AD9515数据表。

此外,OSC401上还提供了一个车载振荡器,它可以作为主时钟源。设置很快,包括安装R403和一个0Ω电阻,并将使能跳线(J401)设置到接通位置。如果用户希望使用不同的振荡器,可以使用两个振荡器封装选项(OSC401)来检查ADC性能。

(1)、PDWN:要启用断电功能,将J301短接至PDWN引脚的打开位置(AVDD)。

(2)、SCLK/DTP:要在ADC的数字输出端启用数字测试模式,请使用J304。如果J304在设备通电期间连接到AVDD,则启用测试模式10 0000 0000 0000。有关详细信息,请参阅SCLK/DTP管脚部分。

(3)、SDIO/ODM:要启用低功率、减小信号选项(类似于IEEE1595.3缩小范围链路LVDS输出标准),请使用J303。如果J303在设备通电期间绑定到AVDD,它将启用来自默认ANSI-644标准的低功耗、减少信号选项中的LVDS输出。此选项将信号摆幅从350 mV p-p更改为200 mV p-p,从而降低DRVDD电源的功率。有关更多详细信息,请参阅SDIO/ODM Pin部分。

(4)、CSB:要启用SDIO和SCLK管脚上的SPI信息处理,请将J302连接到始终启用模式。要忽略SDIO和SCLK信息,请将J302连接到AVDD。

(5)、非SPI模式:对于希望在不使用SPI的情况下操作DUT的用户,只需移除跳线J302、J303和J304。这将断开CSB、SCLK/DTP和SDIO/ODM引脚与控制总线的连接,使DUT以最简单的模式运行。每个插脚都有内部终端,并将浮动到各自的水平。

(6)、D+x,D-x:如果使用图62所示设置的替代数据捕获方法,则可在高速背板连接器旁边安装可选接收器终端R318和R320至R328。

替代模拟输入驱动器配置

以下是使用AD8334双VGA的替代模拟输入驱动器配置的简要说明。如果使用此驱动器选项,则可能需要填充某些组件,在这种情况下,表17列出了所有必需的组件。有关AD8334双VGA的更多详细信息,包括其工作原理和可选的管脚设置,请参阅AD8334数据表。

要将模拟输入配置为驱动VGA而不是默认的转换器选项,需要删除和/或更改以下组件。

(1)、拆下R102、R115、R128、R141、R161、R162、R163、R164,默认模拟输入路径中的R202、R208、R218、R225、R234、R241、R252、R259、T101、T102、T103、T104、T201、T202、T203和T204。

(2)、在模拟输入路径中使用0Ω电阻器填充R101、R114、R127、R140、R201、R217、R233和R251。

(3)、填充R152、R153、R154、R155、R156、R157、R158、R159,R215、R216、R229、R230、R247、R248、R263、R264、C103,C105、C110、C112、C117、C119、C124、C126、C203、C205、C210、C212、C217、C219、C224和C226带有10 kΩ电阻器,为ADC模拟输入提供输入共模电平。

(4)、填充R105、R113、R118、R124、R131、R137、R151、R160,R205、R213、R221、R222、R237、R238、R255和R256、ADC模拟输入路径中的0Ω电阻器,用于连接VGA输出。

(5)、卸下AD8334模拟输出上的R515、R520、R527、R532、R615、R620、R627和R632。

(6)、卸下R512、R524、R612和R624,将AD8334模式和AD8334 HILO引脚设置为低。有些应用程序可能要求这是不同的。有关这些功能的更多信息,请参阅AD8334数据表。

在这种配置中,L505至L520和L605至L620装有0Ω电阻器,以便在需要额外要求时连接信号并使用滤波器。

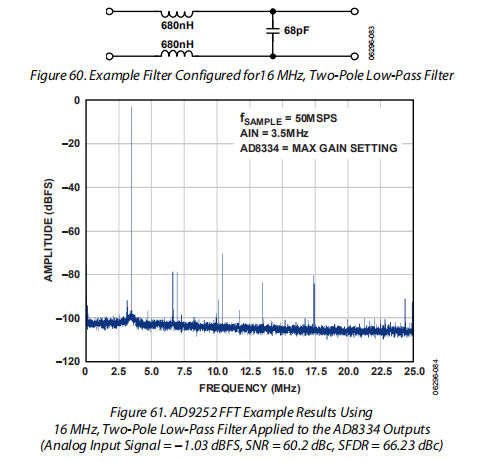

在本例中,对AD8334输出应用了16mhz的双极低通滤波器。需要拆卸和/或更换以下部件:

(1)、卸下AD8334模拟输出上的L507、L508、L511、L515、L516、L519、L607、L608、L611、L612、L615、L616、L619和L620。

(2)、使用680 nH感应器填充L507、L508、L511、L512、L515、L516、L519、L607、L608、L611、L612、L615、L616、L619和L620。

(3)、使用68 pF电容器填充C543、C547、C551、C555、C643、C647、C651和C655。

外形尺寸