120点击型号即可查看芯片规格书

240点击型号即可查看芯片规格书

摘要

用于通信、图形和成像应用的高性能信号处理器;超级哈佛建筑;四条独立总线用于双数据采集,指令获取和非侵入式I/O;32位IEEE浮点计算单元-乘法器、算术运算器和移位器;双端口片上SRAM与集成I/O;外设-一个完整的片上系统;集成多处理功能。

主要特点

40 MIPS,25 ns指令速率,单周期指令执行;120 MFLOPS峰值,80 MFLOPS持续性能模位反向双数据地址发生器;零开销的高效程序排序;循环:单循环循环设置;IEEE JTAG标准1149.1测试访问端口和片上仿真;240引线热增强MQFP封装;225 PBGA包装;32位单精度和40位扩展精度;IEEE浮点数据格式或32位定点数据格式;并行计算;并行单周期乘法和算术运算;具有双内存读/写和指令获取功能;加速FFT的乘法加减法;蝶形计算;4mbit片上SRAM;双端口,由核心处理器独立访问和DMA;片外存储器接口;4千兆字可寻址;可编程等待状态生成,页面模式DRAM支持。

DMA控制器

用于ADSP-2106x之间传输的10个DMA信道;内部存储器和外部存储器;外围设备、主机处理器、串行端口或链路港口;40兆赫的后台DMA传输,与全速处理器并行执行;16位和32位微处理器的主机处理器接口;主机可直接读写ADSP-2106x内部记忆;多处理;可扩展DSP多处理的无胶连接;建筑;并行总线的分布式片上总线仲裁;连接多达六个ADSP-2106xs Plus主机;用于点到点连接和阵列的六个链路端口多处理;240mbytes/s并行总线传输速率通过链路端口的240 MB/s传输速率。

串行端口

两个40mbit/s同步串行端口;压扩硬件独立的发送和接收功能。

一般说明

ADSP-21060 SHARC超级哈佛结构计算机是一种信号处理微型计算机,提供了新的功能和性能水平。ADSP-2106x SHARC是为高性能而优化的32位处理器数字信号处理器应用。a DSP-2106x以adsp2100dsp为核心,构成一个完整的片上系统,增加了一个双端口片上SRAM和一个专用I/O总线支持的集成I/O外设。

ADSP-2106x采用高速低功耗CMOS工艺制造,指令周期为25ns,工作速度为40MIPS。通过片上指令缓存,处理器可以在一个周期内执行每一条指令。表一显示了ADSP-2106x的性能基准。

ADSP-2106x SHARC代表了一种新的信号计算机集成标准,它将高性能浮点数字信号处理器内核与集成的片上系统功能相结合,包括一个4mbit的SRAM内存主机处理器接口、DMA控制器、串行端口以及用于无胶数字信号处理器多处理的链路端口和并行总线连接。

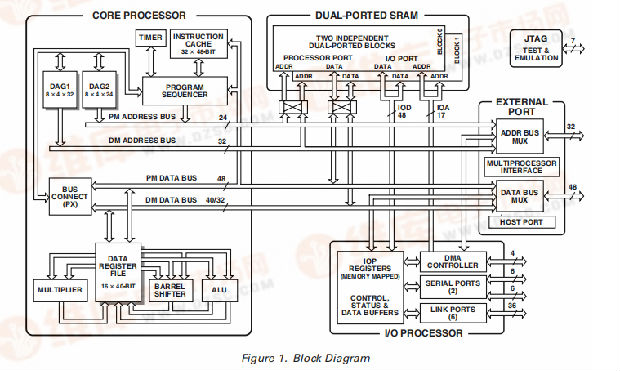

图1显示了ADSP-2106x的框图,说明了以下架构特性:

带有共享数据寄存器文件;数据地址生成器(DAG1、DAG2);带指令缓存的程序序列器;片上定时SRAM与片外存储器和外围设备;主机端口和多处理器接口;DMA控制器;串行端口和链路端口;JTAG测试访问端口。

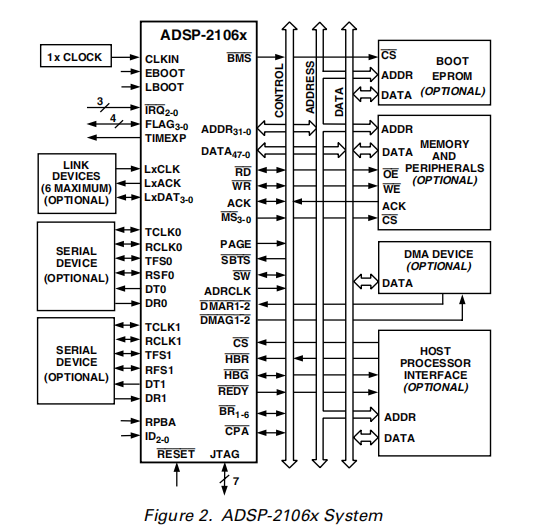

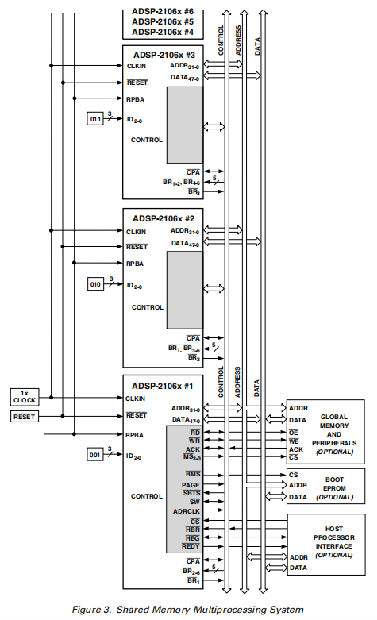

图2显示了一个典型的单处理器系统。多处理系统如图3所示。

ADSP-21000系列核心架构

ADSP-2106x包含ADSP-21000系列核心的以下架构功能。ADSP-21060与ADSP-21061和ADSP-21062的代码和功能兼容。

独立的并行计算单元

算术/逻辑单元(ALU)、乘法器和移位器都执行单周期指令。这三个单元并行排列,最大化了计算吞吐量。单个多功能指令执行并行运算单元和乘法器操作。这些计算单元支持IEEE 32位单精度浮点、扩展精度40位浮点和32位定点数据格式。

数据寄存器文件

通用数据寄存器文件用于在计算单元和数据总线之间传输数据,并用于存储中间结果。这个10端口,32寄存器(16个主寄存器,16个次寄存器)寄存器文件,结合ADSP21000哈佛体系结构,允许计算单元和内部存储器之间的无约束数据流。

指令和两个操作数的单周期获取ADSP-2106x采用了增强的哈佛体系结构,其中数据存储器(DM)总线传输数据,程序存储器(PM)总线传输指令和数据(见图1)。由于其独立的程序和数据存储总线以及片上指令缓存,处理器可以在一个周期内同时获取两个操作数和一条指令(从缓存)。

指令缓存

ADSP-2106x包括一个片上指令缓存,它支持三总线操作来获取一条指令和两个数据值。缓存是选择性的,只缓存取数与PM总线数据访问冲突的指令。这允许全速执行核心、循环操作,如数字滤波器乘法累加和FFT蝶形处理。

带硬件循环缓冲区的数据地址生成器ADSP-2106x的两个数据地址生成器(DAG)在硬件上实现循环数据缓冲区。圆形缓冲器允许有效编程延迟线和数字信号处理所需的其他数据结构,通常用于数字滤波器和傅里叶变换。ADSP-2106x的两个DAG包含足够的寄存器,可以创建多达32个循环缓冲区(16个主寄存器集,16个次寄存器集)。DAG自动处理环绕的地址指针,减少开销,提高性能,并简化实现。循环缓冲区可以在任何内存位置开始和结束。

灵活指令集

48位指令字可容纳各种并行操作,以实现简洁的编程。例如,ADSP2106x可以有条件地在一条指令中执行乘法、加法、减法和分支。

ADSP-21060/ADSP-21060L特点

扩充ADSP-21000系列核心,ADSP-21060增加了以下架构功能:

双端口片上存储器

ADSP-21060包含4兆位的片上SRAM,每兆位分为2块,可以配置成不同的代码和数据存储组合。每个内存块都是双端口的,由核心处理器和I/O处理器或DMA控制器进行单周期独立访问。双端口存储器和独立的片上总线允许在一个周期内从内核传输两个数据,从I/O传输一个数据。

在ADSP-21060上,存储器可以配置为最大的128K字的32位数据,256K字的16位数据,80K字的48位指令(或40位数据),或不同的字大小的组合高达四兆比特。所有内存都可以作为16位、32位或48位字访问。

支持16位浮点存储格式,有效地将可存储在芯片上的数据量加倍。32位浮点和16位浮点格式之间的转换是在一条指令中完成的。

虽然每个存储块可以存储代码和数据的组合,但是当一个块存储数据时,使用DM总线进行传输,而另一个块存储指令和数据时,使用PM总线进行传输,访问效率最高。以这种方式使用DM总线和PM总线,每个内存块有一个专用的总线,确保了两次数据传输的单周期执行。在这种情况下,指令必须在缓存中可用。当其中一个数据操作数通过ADSP2106x的外部端口传输到片外或从片外传输时,也保持单周期执行。

片外存储器和外设接口ADSP-2106x的外部端口提供处理器与片外存储器和外围设备的接口。4G的片外地址空间包含在ADSP-2106x的统一地址空间中。用于PM地址、PM数据、DM地址、DM数据、I/O地址和I/O数据的独立片上总线在外部端口上多路复用,以创建具有单个32位地址总线和单个48位(或32位)数据总线的外部系统总线。

通过对高阶地址线的片上解码来产生存储组选择信号,从而方便了外部存储设备的寻址。为了简化页面模式DRAM的寻址,还生成了单独的控制线。ADSP-2106x提供可编程内存等待状态和外部内存确认控制,允许以可变访问、保持和禁用时间要求与DRAM和外围设备进行接口。

主机处理器接口

ADSP-2106x的主机接口允许轻松连接到16位和32位的标准微处理器总线,不需要额外的硬件。支持以高达处理器全时钟速率的速度进行异步传输。主机接口通过ADSP-2106x的外部端口访问,并将内存映射到统一地址空间。主机接口有四个DMA通道;代码和数据传输以较低的软件开销完成。

主机处理器使用主机总线请求(HBR)、主机总线授权(HBG)和就绪(REDY)信号请求ADSP-2106x的外部总线。主机可以直接读写ADSP-2106x的内部存储器,并可以访问DMA通道设置和邮箱寄存器。为有效执行主机命令提供了矢量中断支持。

DMA控制器

ADSP-2106x的片上DMA控制器允许零开销数据传输,无需处理器干预。DMA控制器对处理器核心独立且不可见地操作,允许在核心同时执行其程序指令时进行DMA操作。

DMA传输可以发生在ADSP-2106x的内部存储器和外部存储器、外部外设或主机处理器之间。DMA传输也可以发生在ADSP-2106x的内部存储器与其串行端口或链路端口之间。外部存储器和外部外围设备之间的DMA传输是另一种选择。在DMA传输期间执行16、32或48位字的外部总线打包。

ADSP-2106x-2上有10个DMA通道,通过链路端口,4个通过串行端口,4个通过处理器的外部端口(用于主机处理器、其他ADSP-2106xs、内存或I/O传输)。另外四个链路端口DMA通道与串行端口1和外部端口共享。可以使用DMA传输将程序下载到ADSP-2106x。异步片外外设可以使用DMA请求/授权线(DMAR1-2、DMAG1-2)控制两个DMA信道。其他DMA功能包括在DMA传输完成时生成中断,以及用于自动链接DMA传输的DMA链。

串行端口

ADSP-2106x具有两个同步串行端口,为各种数字和混合信号外围设备提供廉价的接口。串行端口可以在处理器的全时钟速率下工作,提供每个最大的数据速率为40兆位/秒。独立的发送和接收功能为串行通信提供更大的灵活性。串行端口数据可以通过DMA自动地在片上存储器之间传输。每个串行端口都提供TDM多通道模式。

串行端口可以使用小端或大端传输格式,字长可从3位到32位选择。它们提供可选的同步和传输模式以及可选的μ-律或A-律压扩。串行端口时钟和帧同步可以在内部或外部生成。

多处理

ADSP-2106x为多处理DSP系统提供了强大的功能。统一地址空间(见图4)允许处理器间直接访问每个ADSP2106x的内部存储器。分布式总线仲裁逻辑包含在芯片上,用于简单、无胶连接最多包含六个ADSP-2106xs和一个主机处理器的系统。主处理器转换只产生一个周期的开销。总线仲裁可以选择固定优先级或旋转优先级。总线锁允许信号量的不可分割的读-修改-写序列。为处理器间命令提供矢量中断。处理器间数据传输的最大吞吐量是在链路端口或外部端口上的240兆字节/秒。广播写入允许将数据同时传输到所有ADSP-2106xs,并可用于实现反射信号量。

链接端口

ADSP-2106x具有六个4位链路端口,提供额外的I/O功能。链路端口可以每周期时钟两次,允许每个端口每周期传输8位。链路端口I/O对于多处理系统中的点到点处理器间通信特别有用。

链路端口可以独立运行,同时最大吞吐量为240兆字节/秒。链路端口数据被打包成32位或48位字,并且可以由核心处理器直接读取或DMA传输到片上存储器。

每个链路端口都有自己的双缓冲输入和输出寄存器。时钟/应答握手控制链路端口传输。传输可编程为发送或接收。

程序启动

ADSP-2106x的内部存储器可以在系统通电时从8位EPROM、主机处理器或通过其中一个链路端口启动。引导源的选择由BMS(引导内存选择)、EBOOT(EPROM引导)和LBOOT(链接/主机引导)管脚控制。32位和16位主机处理器可用于引导。

开发工具

ADSP-21060支持一整套软件和硬件开发工具,包括EZ-ICE内循环模拟器、EZ工具包和开发软件。SHARC-EZ工具包是一个用于DSP评估和原型制作的完整的低成本软件包。EZ套件包含一个带有ADSP-21062(5 V)处理器的PC插件卡(EZ-LAB?)。EZ工具包还包括一个优化编译器、汇编程序、指令级模拟器、运行时库、诊断实用程序和一整套示例程序。

同样的EZ-ICE硬件可以用于ADSP-21061/ADSP-21062,以完全模拟ADSP-21060,除了显示和修改ADSP-21061特有的两个新运动寄存器。

模拟设备ADSP-21000系列开发软件包括一个基于代数语法的易于使用的汇编程序、汇编库/库、链接器、指令级模拟器、一个ANSI C优化编译器、CBUG™C源代码级调试器和一个C运行库(包括DSP和数学函数)。优化编译器包括基于ANSI数值C扩展组工作的数值C扩展。数值C为C语言提供了数组选择、向量数学运算、复杂数据类型、循环指针和可变维数的扩展阵列。ADSP-21000系列开发软件可用于PC和Sun平台。

ADSP-21060 EZ-ICE仿真器采用ADSP-21060处理器的IEEE1149.1JTAG测试访问端口,在仿真过程中对目标板处理器进行监控。EZ-ICE提供全速仿真,允许检查和修改内存、寄存器和处理器堆栈。通过使用处理器的JTAG接口确保了非侵入式电路内仿真。仿真程序不会影响目标系统的加载或定时。

ADSP-21000系列硬件和软件开发工具数据表(ADDS-210xx-Tools)中提供了更多详细信息和订购信息。本数据表可向任何模拟设备销售办公室或经销商索取。

除了模拟设备提供的软件和硬件开发工具外,第三方还提供了一系列支持SHARC处理器系列的工具。硬件工具包括SHARC-PC插件卡、多处理器SHARC-VME板、具有多个SHARC和附加内存的子模块和模块。这些模块基于SHARCPAC™模块规范。第三方软件工具包括Ada编译器、DSP库、操作系统和框图设计工具。

附加信息

本数据表概述了ADSP-21060的体系结构和功能。有关ADSP-21000系列核心体系结构和指令集的详细信息,请参阅ADSP-2106x SHARC用户手册第二版。

管脚功能说明

ADSP-21060和ADSP-21060L上的所有管脚都相同。被标识为同步的输入必须满足与CLKIN(或与TMS、TDI的TCK)有关的定时要求。标识为异步(A)的输入可以异步断言为CLKIN(或异步断言为TRST的TCK)。

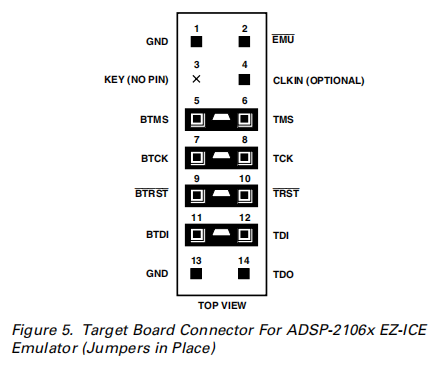

EZ-ICE探头靶板连接器

ADSP-2106x EZ-ICE仿真器采用ADSP-2106x的IEEE1149.1JTAG测试接入端口,在仿真过程中对目标板处理器进行监控。EZ-ICE探头要求ADSP-2106x的CLKIN、TMS、TCK、TRST、TDI、TDO、EMU和GND信号可通过14针连接器(2行×7针条头)在目标系统上访问,如图5所示。EZ-ICE探针直接插在该连接器上,用于板上模拟芯片。如果要使用ADSP-2106x EZ-ICE,则必须将此连接器添加到目标板设计中。EZ之间的总跟踪长度-冰连接器和最远的设备共享的EZ-ICE JTAG引脚应限于15英寸最大的保证操作。此长度限制必须包括路由到一个或多个ADSP-2106x设备的EZ-ICE JTAG信号,或ADSP-2106x设备和链上其他JTAG设备的组合。

14针,两排针条集管在针3的位置键入-必须从收割台上拆下销3。销必须为0.025平方英寸,长度至少为0.20英寸。销间距应为0.1×0.1英寸。可从3M、McKenzie和Samtec等供应商处获得针带头。

提供BTMS、BTCK、BTRST和BTDI信号,测试接入端口也可用于板级测试。当连接器不用于仿真时,在Bxxx引脚和xxx引脚之间放置跳线。如果测试接入端口不用于板测试,将BTRST连接到GND,并将BTCK连接或拉到VDD。必须在通电后(通过连接器上的BTRST)或保持低位以使ADSP-2106x正常工作,才能断言TRST引脚。EZ-ICE探针上未连接任何Bxxx引脚(引脚5、7、9、11)。

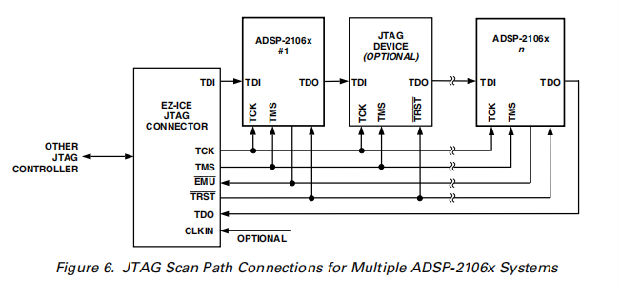

图6显示了包含多个ADSP-2106x处理器的系统的JTAG扫描路径连接。

将CLKIN连接到EZ-ICE割台的插脚4是可选的。仿真器仅在被指示以同步方式执行诸如启动、停止和单步执行多个ADSP-21061的操作时使用CLKIN。如果不需要在多个处理器上同步执行这些操作,只需将EZ-ICE头的引脚4连接到地上。

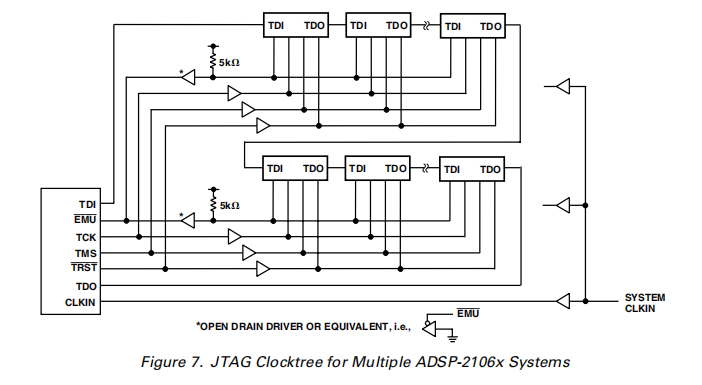

如果需要同步多处理器操作CLKIN已连接,多个ADSP之间的时钟偏移-21061/ADSP-21061L处理器和EZ-ICE头上的CLKIN管脚必须最小。如果偏差过大,同步操作可能会在处理器之间关闭一个或多个周期。对于同步多处理器操作,TCK、TMS、CLKIN和EMU应被视为倾斜方面的关键信号,并应在您的电路板上尽可能短地布置。如果TCK、TMS和CLKIN在您的系统中驱动大量的ADSP-21061(超过8个),那么将它们视为使用多个驱动程序的时钟树,以最小化偏差。(参见ADSP-2106x用户手册第二版“高频设计注意事项”一节中的图7,JTAG时钟树和时钟分布。)

如果不需要同步多处理器操作(即CLKIN未连接),只需在TCK和TMS上使用适当的并行终端。TDI、TDO、EMU和TRST在倾斜方面不是关键信号。

有关SHARC EZ-ICE的完整信息,请参阅ADSP2100系列JTAG EZ-ICE用户指南和参考。

定时规格

ADSP-21060提供两种速度等级:40MHz和33.3MHz。所示规范基于40 MHz的CLKIN频率(tCK=25 ns)。DT降额允许在其他CLKIN频率下的规格(在tCK规格的最小-最大范围内;见下面的时钟输入)。DT是实际CLKIN周期和25 ns CLKIN周期之间的差异:DT = tCK – 25 ns,使用给定的精确计时信息。不要试图从其他的加法或减法中导出参数。虽然加法或减法会对单个设备产生有意义的结果,但本数据表中给出的值反映了统计变化和最坏情况。因此,不能有意义地添加参数以获得更长的时间。

开关特性指定处理器如何更改其信号。您无法控制处理器外部的定时电路必须设计为与这些信号特性兼容。开关特性告诉你处理器在给定的情况下会做什么。您还可以使用切换特性来确保连接到处理器的设备(如内存)的任何计时要求都得到满足。

时间要求适用于由处理器外部电路控制的信号,如用于读取操作的数据输入。时序要求保证处理器与其他设备一起正常工作。

(O/D) = Open Drain

(A/D) = Active Drive

输出驱动电流

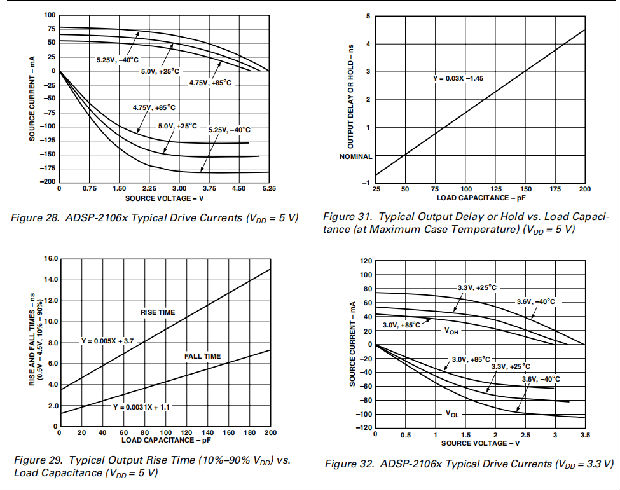

图28显示了ADSP-2106x输出驱动器的典型I-V特性。这些曲线表示输出驱动器的电流驱动能力与输出电压的函数关系。

功耗

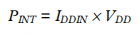

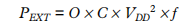

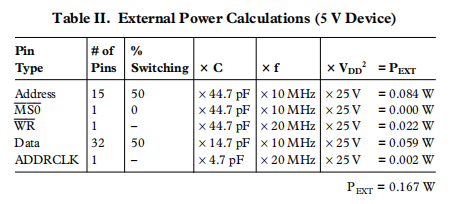

总功耗有两个部分,一个是由于内部电路,另一个是由于外部输出驱动器的切换。内部功耗取决于指令执行序列和所涉及的数据操作数。内部功耗的计算方法如下:

总功耗的外部分量是由输出引脚的切换引起的。其大小取决于:

–每个循环中切换的输出引脚数(O)

-它们可以切换的最大频率(f)

–负载电容(C)

-电压波动(VDD),计算方法如下:

负载电容应包括处理器的封装电容(CIN)。开关频率包括驱动负载升高然后再降低。地址和数据引脚可以驱动高和低的最大速率为1 /(2TCK)。写入选通可以以1/tCK的频率切换每个周期。选择引脚开关在1/(2tCK),但选择可以打开每个周期。

例子:

根据以下假设估算PEXT:

–具有一组外部数据存储器RAM(32位)的系统

–使用四个128K×8 RAM芯片,每个芯片的负载为10 pF

–外部数据存储器写入每隔一个周期发生一次,速率为1/(4tCK),50%的管脚切换

–指令周期速率为40 MHz(tCK=25 ns)。

对于可以驱动以下各项的每类管脚,计算出PEXT方程:

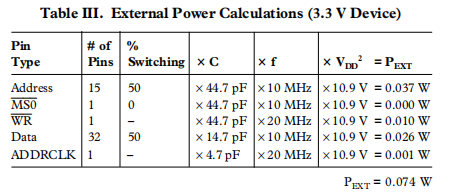

现在可以通过添加典型的内部功耗来计算这些条件下的典型功耗:

请注意,导致最坏情况的PEXT的条件与导致最坏情况的PINT的条件不同。最大的PUT不能发生,而100%的输出引脚从所有的开关切换到所有的零点。还要注意的是,应用程序同时切换100%甚至50%的输出并不常见。

试验条件

输出禁用时间

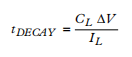

当输出引脚停止驱动,进入高阻抗状态,并开始从其输出的高或低电压衰减时,它们被认为是禁用的。母线上电压衰减∏V的时间取决于电容性负载CL和负载电流IL。这个衰减时间可以用下面的等式来近似:

如图25所示,输出禁用时间tDIS是tMEASURED和tDECAY之间的差值。测量的时间t是从基准信号切换到输出电压从测量的输出高电压或输出低电压衰减∏V的时间间隔。tDECAY是用试验载荷CL和IL计算的,且∏V等于0.5 V。

输出启用时间

当输出管脚从高阻抗状态过渡到开始驱动时,输出管脚被认为是启用的。输出启用时间tENA是指从参考信号达到高或低电压水平到输出达到指定的高或低跳闸点之间的间隔,如输出启用/禁用图(图25)所示。如果启用了多个管脚(如数据总线),则测量值为开始驱动的第一个管脚的测量值。

系统保持时间计算示例

要确定特定系统中的数据输出保持时间,首先使用上面给出的公式计算tDECAY。对于需要保持时间的设备,选择∏V作为ADSP-2106x的输出电压和输入阈值之间的差。典型的∏V为0.4 V。CL为总线总电容(每根数据线),IL为总漏电或三态电流(每根数据线)。保持时间为tDECAY加上最小禁用时间(即,写入周期的tDATRWH)。

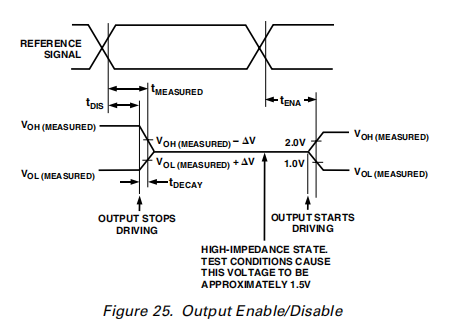

电容性负载

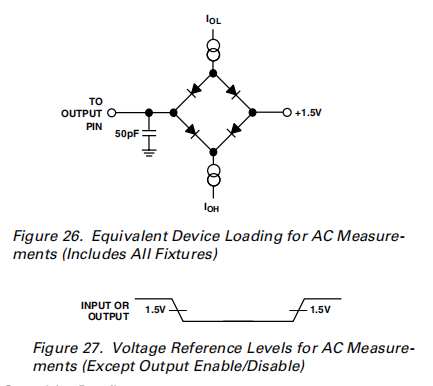

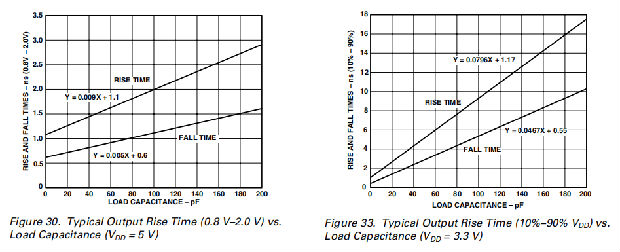

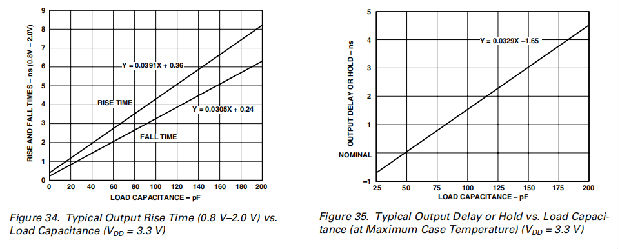

输出延迟和保持基于标准电容负载:所有引脚上50 pF(见图26)。对于额定值50 pF以外的负载,给出的延迟和保持规范应降低1.5 ns/50 pF。图29-30、33-34显示了输出上升时间随电容的变化。图31、35以图形方式显示了输出延迟和保持是如何随负载电容而变化的。(注意,此图或降额不适用于输出禁用延迟;请参阅上一节测试条件下的输出禁用时间。)图29、30和31的图在所示范围之外可能不是线性的。

环境条件

热特性

ADSP-21060KS和ADSP-21060LKS封装在240引线热增强MQFP中。包装的上表面含有一个铜塞,模具的大部分热量从中散发出来。弹头与包装的上表面齐平。请注意,铜段塞通过设备基板内部连接到GND。ADSP-21060KB和ADSP21060LKB是塑料球栅阵列。PBGA封装的θ为1.7°C/Q。

ADSP-2106x是为外壳温度(TCASE)指定的。为确保不超过TCASE数据表规范,可使用散热器和/或气流源。散热器应该用热粘合剂连接。

TCASE=箱温(在包装顶面测量)

PD=功率损耗(W)(该值取决于具体应用;功率损耗下显示了计算局部放电的方法)。

θθ=下表中的值。

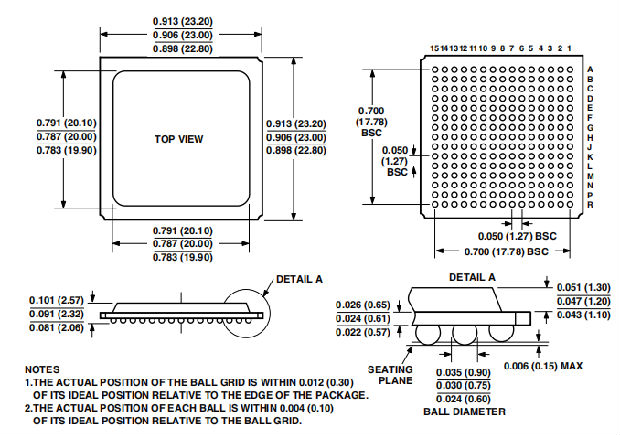

包装尺寸:尺寸单位为英寸和(mm)。

225塑料球栅阵列(PBGA)