AK4543点击型号即可查看芯片规格书

特征

AC'97版本。2.1合规;18位分辨率A/D和D/A;超过PC98/99性能类别:A/D……………90dBA信噪比,D/A……………90dBA信噪比,D/A+混频器……89dBA信噪比,A-A……………95巴信噪比;模拟输入:4个立体声输入:线路、CD、视频、AUX;扬声器和PC蜂鸣音输入;2个独立的麦克风输入;直接PC嘟嘟声传递,降低系统成本;模拟输出:带音量控制的立体声线路输出;带音量控制的实线电平;带音量控制的单声道输出;3D立体声增强;多编解码器功能;AK4543可以作为一级或二级。支持EAPD(外部放大器断电)电源:模拟5.0V,数字3.3V或5.0V;低功耗;满负荷运行时为200兆瓦(模拟:5伏/数字:3.3伏);48针LQFP封装。

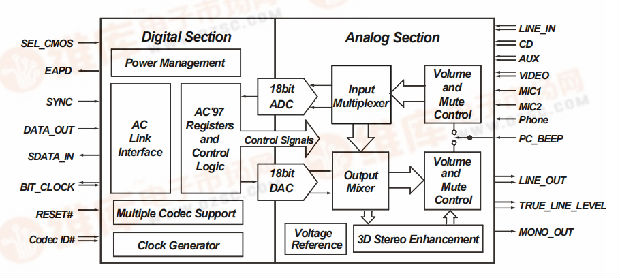

一般说明

AK4543是一种18位高性能编解码器,兼容音频编解码器'97版本2.1要求。交流链路串行接口允许AK4543与数字控制器一起使用,以及定制逻辑加速器以满足PC98和PC99的全部要求对于PCI音频解决方案。

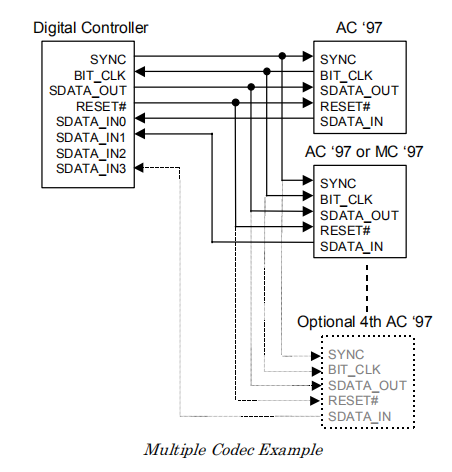

AK4543提供两对独立的立体声输出音量控制以及单声道输出、多立体声和单声道输入,结合,创造灵活的混合,增益和静音功能为PC提供完整的集成音频解决方案。AK4543可以用作主AC'97或辅助编解码器取决于编解码器ID配置(多个编解码器扩展),使AK4543适用于扩展底座应用多个编解码器应用程序,如4扬声器输出或6扬声器输出。

采样频率为48kHz,AK4543提供卓越的音频性能,达到或超过所有标准要求。它提供低功耗和灵活的掉电模式用于笔记本电脑、台式机和售后附加板。像早期的兼容引脚AK4540和AK4542,AK4543提供紧凑型48导LQFP封装。AK4543是AK4540和AK4542,需要进行一些软件更改才能体验AK4543的额外功能。

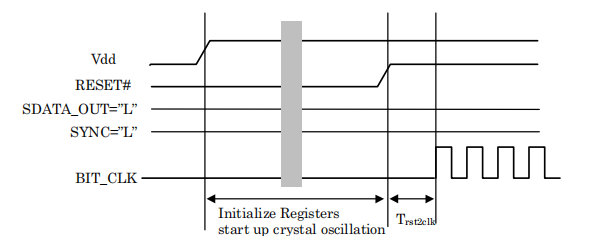

通电

请注意,AK4543必须在通电时处于冷复位状态,并且复位#必须在主时钟稳定之前处于低位,或者必须在主时钟稳定后进行复位。AVdd或DVD可由独立电源供电。

在多编解码器模式下使用AK4543时,所有连接到AC链路的编解码器将同时唤醒。应使用公共复位线,以确保通电后的时钟同步。

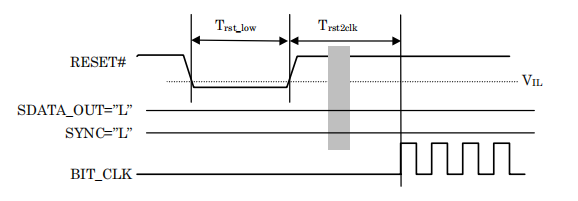

Cold复位定时

请注意,SDATA_OUT和SYNC必须在RESET#的上升沿处于低位,才能进行冷重置。AK4543初始化所有寄存器,包括断电控制寄存器,位CLK被重新激活,每个模拟输出都处于Hi-Z状态,除了复位引脚低时PC蜂鸣音。当AK4543处于冷复位状态时,PC蜂鸣音直接发送至L&R线路输出。这样做是为了允许将系统声音传递给扬声器移除内部冗余扬声器。

在复位上升沿,AK4543启动模拟电路初始化,周期516fs。之后,AK4543的混合器就可以正常工作了。

当AK4543处于复位周期(“L”)或初始化过程中时,插槽0中的状态位为“0”(未就绪)。初始化周期后,状态位变为“1”,表示就绪状态。

当在多编解码器配置下使用AK4543并且发出冷重置时,连接到AC链路的所有AK4543将同时执行冷重置。

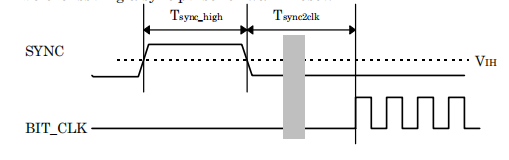

Warm复位

AK4543通过接收同步上的单个脉冲(Pin10)来启动热重置过程。然后AK4543清除掉掉掉电控制寄存器中的PR4位和PR5位。但是,温复位不影响PR0~PR3或断电控制寄存器(26h)中的PR6,7位。注意,在AK4543开始输出位时钟后,同步信号应与位时钟同步。如果使用外部时钟,则应在发出同步脉冲进行热重置之前提供外部时钟。

当AK4543在多编解码器配置下使用时,请参考热重置上多编解码器配置的断电/通电顺序。

注:

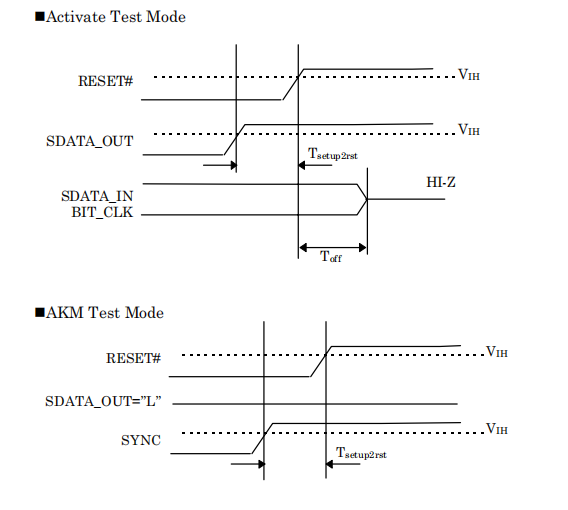

1、所有交流链路信号通常通过复位后缘为低电平。将SDATAŠu调高至复位上升沿,导致AK4543交流链路输出变为高阻抗,这适用于电路内ATE测试。请注意,无论同步是高还是低,AK4543都进入ATE测试模式。

2、将SYNC high和SDATA_OUT low设置为RESET的上升沿会导致AKM测试模式。

3、一旦进入测试模式,返回正常工作状态的唯一方法是发出“冷复位”,在同步和SDATA输出低的情况下发出复位。

一般说明

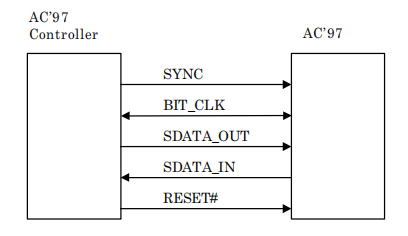

AC'97与数字AC'97控制器的连接

AC'97通过数字串行链路“AC link”与其配套的AC'97控制器通信。所有数字音频流和命令/状态信息都通过点对点串行互连进行通信。下图显示了连接这两者的信号分支。

AC'97数字接口

AK4543集成了一个5针数字串行接口,将其连接到AC'97控制器。交流链路是一种双向、固定速率(48kHz)的串行PCM数字流。它处理多个输入和输出音频流,以及采用时分复用(TDM)方案的控制寄存器访问。AC链路体系结构将每个音频帧分成12个输出和12个输入数据流,每个数据流具有20位采样分辨率。AK4543的DAC和ADC分辨率为18位。AC'97规范当前定义的数据流包括:

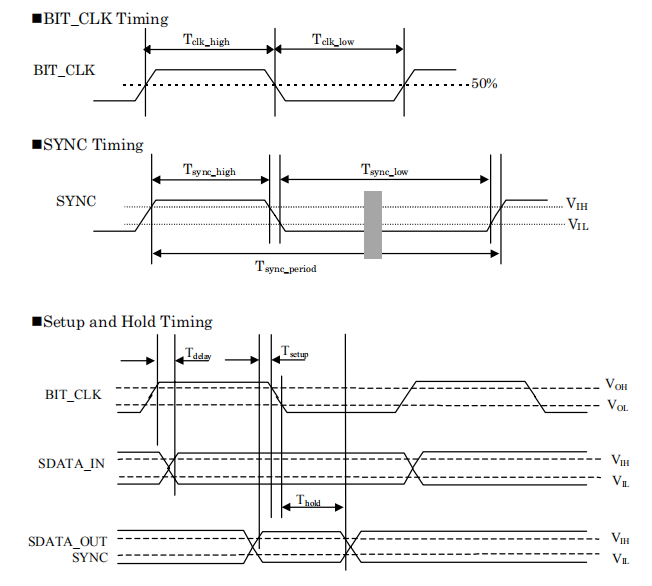

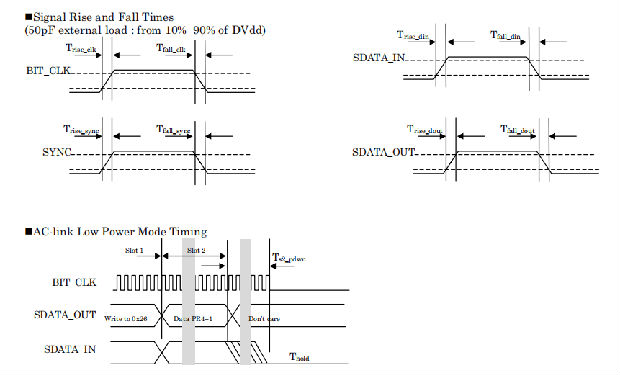

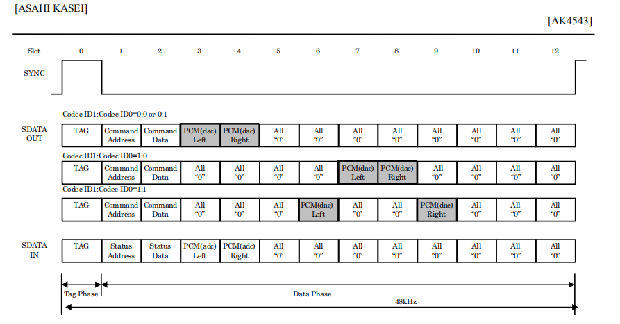

同步,固定在48千赫,是通过除以串行位时钟(位时钟)得到的。位时钟,固定在12.288MHz,提供必要的时钟粒度,以支持12、20位的出站和入站时隙。AC链路串行数据在位时钟的每个上升沿上传输。AC链路数据的接收器、输出数据的AK4543和输入数据的AC'97控制器,对位时钟下降沿上的每个串行位进行采样。

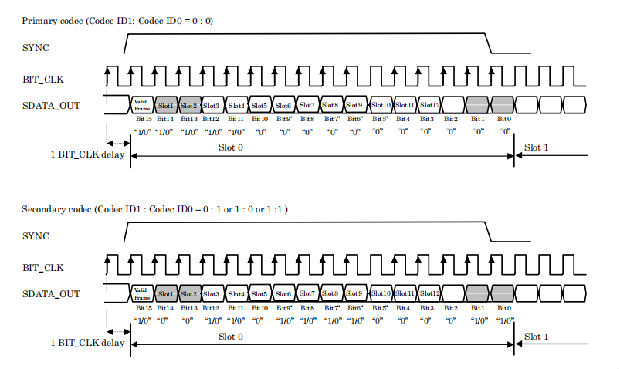

当通过编解码器ID配置ID1#和ID0#将位CLK分配为主编解码器时,AK4543输出位CLK。另一方面,AK4543在被分配为来自主设备的辅助编解码器时接收BIT_CLK。

AC链路协议提供了一个特殊的16位时隙(时隙0),其中每个位在当前音频帧内为其对应的时隙传送一个有效的标签。时隙0的给定位位置中的“1”表示当前音频帧内的对应时隙已被分配给数据流,并且包含有效数据。如果某个时隙被“标记”为无效,则数据源(输入流的AK4543,输出流的AC'97控制器)有责任在该时隙的活动时间内用0填充所有位位置。

在每个音频帧开始时,同步保持在16位时钟的总持续时间内。同步度高的音频帧部分被定义为“标记阶段”。同步低的音频帧的其余部分被定义为“数据阶段”。

注意,SDATA_OUT和SDATA_IN数据延迟一位时钟,因为AC'97控制器在启动帧的位时钟上升沿导致同步信号高。

“输出”流表示从AC'97控制器到AK4543的方向,“输入”流表示从AK4543到AC'97控制器的方向以下所有用斜体小字体写的句子引用了AC'97组件规范。

AC链路协议识别每帧13个数据槽。同步频率固定为48kHz。只有插槽0(标记阶段)是16位,所有其他插槽的长度都是20位。这些插槽将在后面的章节中进行说明。

交流链路音频输出帧(SDATA_-OUT)

a)、插槽0

AK4543检查位15(有效帧位)。注意,当有效帧位为“1”时,至少有一个位14-6(插槽19)或位1-0必须有效,位5-2将为“0”,应忽略。

如果bit15为“0”,则AK4543忽略帧中的所有以下信息。

然后,AK4543检查标记阶段(插槽0)中每个位的有效性。

如果每个位为“0”,AK4543将忽略由“0”指示的插槽。另一方面,如果每个位都是“1”,则插槽有效。

slot10-12(bit5-3)中的所有位都是“0”,bit2也是“0”。

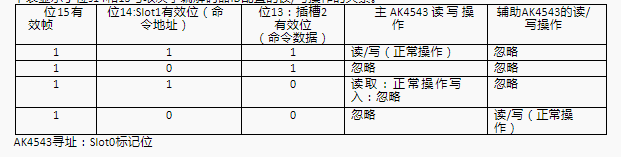

AK4543监视bit1和0,这是多个编解码器实现中使用的编解码器ID配置位。这些位用于标识将帧数据发送到哪个编解码器。

当由编解码器ID配置45/46捆扎管脚(编解码器ID0#和ID1#)设置的编解码器ID配置位1和0设置为零(00)时,帧针对主编解码器。并且当编解码器ID配置位1和0被设置为非零值(01、10或11)时,该帧用于辅助编解码器。

新的音频输出帧从同步的低到高转换开始。同步与位时钟的上升沿同步。在紧接着的BIT_CLK下降沿上,AK4543对SYNC断言进行采样。这个下降沿标志着交流链路的两侧都意识到新音频帧的开始。在下一个位时钟上升时,AC'97控制器将SDATA输出转换到插槽0的第一个位位置(有效帧位)。每一个新的位位置被呈现给位时钟上升沿上的AC链路,随后由位时钟下降沿上的AK4543采样。此序列确保数据转换以及传入和传出数据流的后续采样点是时间对齐的。

数据应首先通过标有SDATA的管脚发送到带有MSB的AC'97编解码器。

下表显示了位s14和13与取决于编解码器ID配置的读/写操作的关系。

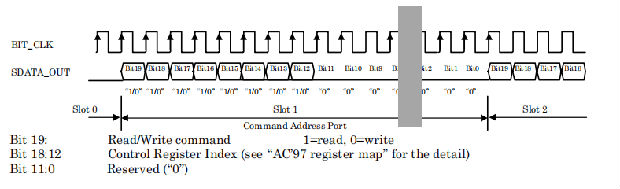

b)、Slot1:命令地址端口

Slot1给出命令数据的地址,在slot 2中给出。AK4543有20个16位数据的有效寄存器。见第17页(见AC'97寄存器图)。

位19:读/写命令1=读,0=写

位18:12控制寄存器索引(详见“AC'97寄存器映射”)位11:0保留(“0”)

位18相当于索引寄存器地址的最高有效位。

AK4543忽略从第11位到第0位。这些位将保留用于将来的增强,并且必须由AC'97控制器填充0。

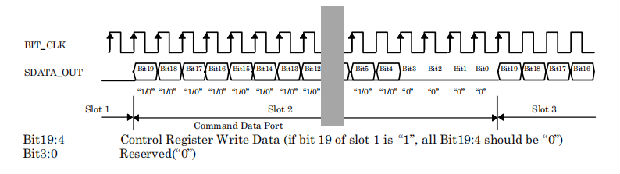

c)、Slot2:命令数据端口

位19:4控制寄存器写入数据(如果插槽1的位19为“1”,则所有位19:4应为“0”)位3:0保留(“0”)

如果slot1中的bit19为“0”,则是一个写命令,AC'97控制器必须在同一帧的slot 2中输出命令数据端口数据。如果slot1中的bit19是“1”,则AK4543将忽略slot2中的任何命令数据端口数据。

位19相当于混频器寄存器值的D15位。

d)、Slot3 PCM回放左声道(18位)

在codec ID1:codec ID0=0:0或0:1的情况下,AK4543使用slot3中的回放(DAC)数据格式作为左声道。

回放数据格式为18bits MSB first 2的补码。AC'97控制器应该用“0”填充位1-0。如果插槽0中的有效位(slot3)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

e)、Slot4 PCM回放右声道(18位)

在codec ID1:codec ID0=0:0或0:1的情况下,AK4543在右侧通道的slot4中使用回放(DAC)数据格式。播放数据格式为MSB优先。数据格式是18位2的补码。AC'97控制器应该用“0”填充位1-0。如果插槽0中的有效位(插槽4)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

f)、AK4543中未使用Slot5

AK4543将忽略此插槽中的填充。

g)、Slot6 PCM回放左声道(18位)

在codec ID1:codec ID0=1:1的情况下,AK4543使用左声道插槽6中的回放(DAC)数据。

回放数据格式为18bits MSB first 2的补码。AC'97控制器应该用“0”填充bit1-0。如果插槽0中的有效位(slot6)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

h)、Slot7 PCM回放左声道(18位)

在codec ID1:codec ID0=1:0的情况下,AK4543使用slot7中的回放(DAC)数据作为左声道。

回放数据格式为18bits MSB first 2的补码。AC'97控制器应该用“0”填充bit1-0。如果插槽0中的有效位(slot7)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

i)、Slot8 PCM回放右声道(18位)

在codec ID1:codec ID0=1:0的情况下,AK4543使用slot8中的回放(DAC)数据作为右声道。

回放数据格式为18bits MSB first 2的补码。AC'97控制器应该用“0”填充bit1-0。如果插槽0中的有效位(slot8)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

j)、Slot9 PCM回放右声道(18位)

在codec ID1:codec ID0=1:1的情况下,AK4543将插槽9中的回放(DAC)数据用于右声道。

回放数据格式为18bits MSB first 2的补码。AC'97控制器应该用“0”填充bit1-0。如果插槽0中的有效位(slot9)无效(“0”),则AK4543将数据解释为所有“0”。

Bit19:2回放数据

位1:0“0”

k)、AK4543中未使用插槽10-12

AK4543将忽略填充在这些数据槽中的数据。

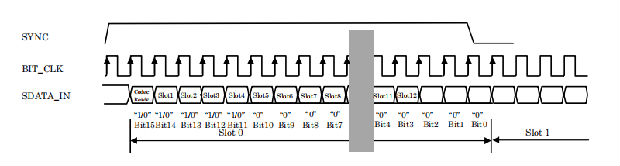

交流链路输入帧(SDATA_-IN)

每个交流链路帧由一个16位标签相位和12个用于数据和控制的20位插槽组成。a)缓慢

Slot0是一个特殊的帧,由16位组成。Slot0也称为“标记阶段”。AK4543支持位15-11和位1-0。每个位表示“1”=有效(正常操作)或就绪,“0”=无效(异常操作)或未就绪。

如果插槽0中的第一位有效,则AK4543可以正常工作。三。AC'97控制器应忽略插槽0和所有其他插槽中的以下位。如果“编解码器就绪”位无效,则以下位和剩余的插槽均为“0”

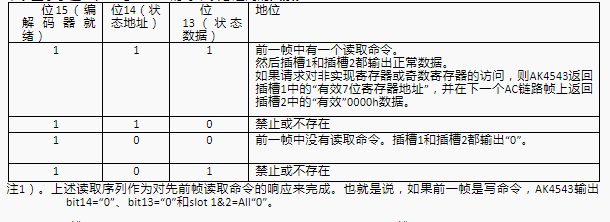

位14表示插槽1(状态地址)输出有效或无效。位13表示插槽2(状态数据)有效或无效。

下表显示了位14、13与AK4543的每个状态之间的关系。

Bit12表示插槽3(左边的PCM(ADC))的输出有效或无效。位11表示插槽4(左边的PCM(ADC))的输出有效或无效。位10-0用“0”填充。

新的音频输入帧从同步的低到高转换开始。同步与位时钟的上升沿同步。在紧接着的BIT_CLK下降沿上,AK4543对SYNC断言进行采样。这个下降沿标志着交流链路的两侧都意识到新音频帧的开始。在位CLK的下一次上升时,AK4543将SDATA转入插槽0的第一位位置(“编解码器就绪”位)。每个新的位位置在位时钟的上升沿上呈现给AC链路,随后由AC'97控制器在位时钟的下一下降沿上采样。此序列确保数据转换以及传入和传出数据流的后续采样点是时间对齐的。

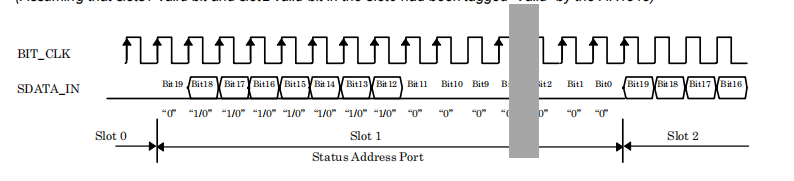

b)、Slot1状态地址端口

音频输入帧slot1的流回显要在slot2中返回的数据的控制寄存器索引,以供历史参考。(假设slot0中的slots1有效位和slot2有效位已被AK4543标记为“有效”)。

当AC'97未准备好正常运行时,本文件中未指定输出位,应视为无效。

这个地址显示在slot2中返回数据的寄存器索引。

这个地址端口是输出帧的slot1的副本,输入到SDATA_OUT的索引地址通过SDATA_IN循环回到AC'97控制器。这允许控制器确保AK4543接收到正确的数据。c)Slot2:状态数据端口输出流的命令地址端口寻址的状态数据通过pin中的SDATA_输出。Bit19:4控制寄存器读取数据(插槽1中索引地址的内容)Bit3:0“0”

注意,状态数据端口数据的地址与同一帧中插槽1的状态地址端口数据一致。如果AC'97控制器在帧N中发出读取操作,则状态数据端口数据通过帧N+1中的SDATA_输出。请注意,数据仅在此帧中可用一次,如果未发出另一个读取操作,则以下帧无效。

d)、Slot3:PCM记录左声道

记录(ADC)数据格式为18bits MSB first 2的补码。忽略框架的下部2位。如果ADC块断电,插槽0中的插槽3有效位无效(“0”),数据与所有“0”一样。

Bit19:2音频ADC左声道输出

位1:0“0”

e)、Slot4:PCM记录右声道

记录(ADC)数据格式为18bits MSB first 2的补码。忽略框架的下部2位。如果ADC块断电,插槽0中的插槽4有效位无效(“0”),数据与所有“0”一样。

Bit19:2音频ADC右声道输出

位1:0“0”

f)、Slot5:调制解调器线路编解码器

AK4543不包含调制解调器编解码器,所有位在此插槽中填充“0”。

位19:0“0”

g)、Slot6:麦克风记录数据

AK4543不包含麦克风的第三个ADC,所有位在此插槽中填充“0”。

位19:0“0”

h)、Slots7-12预留用于未来增强

位19:0“0”

AC'97注册地图

每个寄存器是一个16位字。

注:如果控制器读取未使用或无效的寄存器地址,AK4543输出“有效”0000h。

复位寄存器(索引00h)

<写入>

当任何值写入该寄存器时,AK4543中除寄存器“26h”断电控制/状态寄存器外的所有寄存器都将重置为默认值。这个寄存器的值没有改变。

<阅读>

读取该寄存器将返回“2D50h”,由零件的ID代码、3D增强类型的代码组成,

18位ADC/DAC分辨率,以及一个用于真实线路电平输出的代码。

*设置D14–D10“01011”表示AKM 3D增强功能,已在音频编解码器97组件规范(版本1.03和2.1)中注册。

*设置D8“1”表示18位ADC分辨率,D6“1”表示DAC分辨率。

*设置D4“1”意味着音量控制(索引04h)支持真正的线路电平输出。

播放主音量寄存器(索引02h,06h)和LINVL(实线电平输出)音量寄存器(索引04h)

下表显示了步长为1.5dB时,位与衰减值之间的关系。AK4543的范围为0dB到-46.5dB。AK4543不支持可选MX5位。

AK4543系列检测MX5何时设置,并将所有5个LSB设置为1s。示例:当驱动程序写入“01xxxxx”时,AK4543将其解释为“0011111”。读取该寄存器时,返回值为“0011111”。

PC蜂鸣寄存器(索引0Ah)

下表显示了位与衰减值之间的关系。衰减阶跃为-3dB,范围为0到-45dB。在默认状态下,AK4543的PC嘟嘟声为静音关闭。

当AK4543处于复位状态(复位为“L”)时,PC蜂鸣音直接发送至L&R线输出。这样,当电脑出现硬件问题时,用户就可以听到开机自检(POST)代码。复位后“H”变为“H”后,直接电脑蜂鸣传呼将关闭。

断电控制/状态寄存器(索引26h)

位sd0到D3是只读状态位。对这些位的任何写入都不会影响AK4543的操作。这些位用作AC'97编解码器的子部分的状态位。“1”表示AK4543的子部分“准备就绪”或能够在正常操作中执行。

电源管理/低功率模式

AK4543能够在不需要活动的情况下以多种降低功率模式运行。断电状态由断电寄存器(26h)控制。有8个单独的断电命令。不同模式见下表。由于AK4543在静态模式下工作,即使主时钟仅在通电时停止,寄存器也不会丢失其值。

从正常操作开始,对断电寄存器执行顺序写入,以一次一个地关闭AK4543的子部分。关闭所有设备后,可以执行最终写入(PR4)以关闭AC'97数字接口(AC链路)。部件将保持睡眠模式,其所有寄存器保持其静态值。若要唤醒,AC'97控制器将在同步线上发送脉冲以发出热重置。这将重新启动AK4543数字(将PR4重置为零)。AK4543也可以通过冷复位唤醒。冷复位会导致寄存器值丢失,因为冷复位会将寄存器设置为默认状态。当一个子节重新通电时,在尝试任何需要其正常操作的操作之前,应读取断电控制/状态寄存器(索引26h)以验证该节已准备就绪(即稳定)。

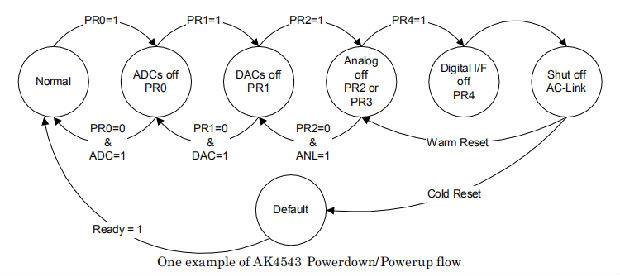

下图展示了一个完成AK4543断电/通电的过程示例。

当PR3位设置为“1”时,即使任何PRx位为“0”,ADC、DAC、混频器、真行电平输出和VREF也将断电。当PR3位被重置为“0”时,AK4543通过引用PRx位恢复先前的状态。在这种情况下,AK4543输出插槽0中对应的slot-x有效位的“0”(无效),直到AK4543的对应块以正常操作操作。

设置PR4位会导致AK4543的断电模式和AK4543的交流链路关闭。在这种情况下,当执行热复位时,PR4位被清除,AC链路被重新激活。发出冷复位,AK4543恢复到默认寄存器设置的操作。

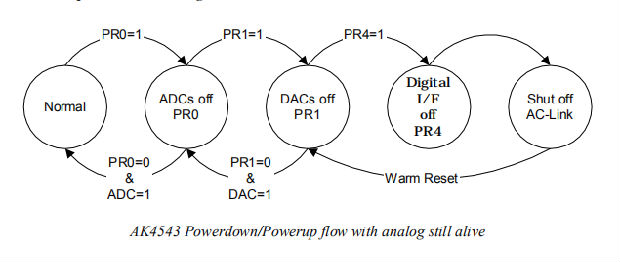

此外,设置PR5位会导致AK4543的断电模式和AK4543的内部时钟停止。在这种情况下,当热复位完成时,PR5位被清除为0,内部时钟和交流链路被重新激活。当执行冷复位时,AK4543被设置为默认寄存器设置的操作,没有激活的断电模式。下一个图说明了所有混频器都应使用其关联寄存器中包含的静态卷设置时的状态。当用户通过AC'97编解码器将CD(或外部线路输入源)播放到扬声器,但大多数系统处于低功耗模式时,使用此选项。除模拟混频器从未关闭外,此过程遵循前面的步骤。

多编解码器配置的断电/通电顺序

扩展AC链路上最多可以有4个编解码器。多个编解码器AC链接实现必须运行在公共位时钟上。主编解码器为AC'97数字控制器和任何辅助编解码器生成主AC链路位时钟。在使用多个编解码器的任何系统中,AK4543可以用作主或从。

在多编解码器情况下,不限制将PR0(ADC)、PR1(DAC)、PR2(混频器)、PR6(LNLVL_-OUT)和PR7(EAPD)设置为“1”或“0”。

如AC'97规范第2.1版所建议,AC链路断电(PR“4”)和Vref,不建议在多编解码器配置下断电(PR5=“1”)以便继续向辅助编解码器提供位时钟。

整体稳定性

激活测试模式

AC'97有两种测试模式。一个用于ATE电路内测试,另一个用于供应商特定的测试。如果在复位后缘对SDATA#u输出进行高采样,AC'97进入电路测试模式下的ATE,而不考虑同步信号(高或低)。如果AC'97在退出复位时进入AKM测试模式,如果同步高,SDATA_out低。在标准操作条件下,这些情况永远不会发生。

无论测试模式如何,AC'97控制器都必须发出“冷”复位,以恢复AC'97编解码器的正常工作。

测试模式功能

ATE电路测试模式

当AC'97处于ATE测试模式时,其数字交流链路输出(即BIT_CLK和SDATA_in)被驱动到高阻抗状态。这允许对AC'97控制器进行ATE电路内测试。

1、接地和电源去耦

AVdd1和AVdd2应连接并派生自同一AVdd。DVdd1和DVdd2也应该连接在同一DVdd上并从同一DVdd派生出来。模拟接地和数字接地应连接在靠近电源连接到印刷电路板的地方。去耦电容器应尽可能靠近AK4543,小值陶瓷电容器最接近,最重要的电容器放置在Vref引脚和AVdd引脚上。

AK4543不需要特定的电源顺序。

2、片上电压基准

片上电压基准输出在VRADDA上,Vref引脚用于解耦。一个小于10uF的电解电容器与一个0.1uf的陶瓷电容器并联在一起,消除了高频噪声的影响。无负载电流可从VRADDA或Vref引脚引出。所有信号,特别是时钟,应远离VRADDA和Vref管脚,以避免不必要的耦合到δ-西格玛调制器。

3、编解码器ID配置引脚45,46。

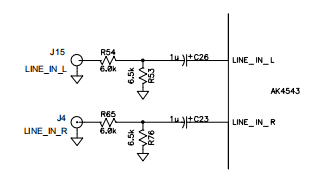

4.日志输入

由于许多模拟电平可以高达2VRMS,下面所示的电路可以用来衰减模拟输入2VRMS到1VRMS,这是所有立体声线路电平输入所允许的最大电压。

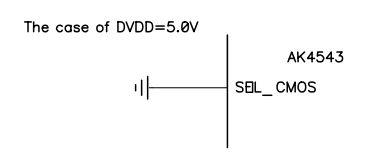

5.选择CMOS(48针)

当支持CMOS电平的DVD为3.3V时,插脚48必须打开。

插脚48必须为DGND,如下图所示,如果DVD的TTL电平为5.0V,则在接通AK4543电源之前,必须固定此选择。

6.PC嘟嘟声

如果不使用PC哔哔声,则该输入引脚应为NC(开路)或通过电容器连接到模拟接地。在这种情况下,PC Beep(04h,D15)的寄存器应设置为静音“1”。(请注意,PC U BEEP的默认设置是静音关闭。)此外,当PC U BEEP通过容量连接到模拟接地时,建议PC U BEEP与其他未使用的输入引脚分开。