235点击型号即可查看芯片规格书

ADV7125点击型号即可查看芯片规格书

特征

330msps吞吐率;三个8位DAC;RS-343A-/RS-170兼容输出;互补输出;DAC输出电流范围:2.0毫安至26.5毫安;TTL兼容输入;内部参考(1.235 V);单电源+5 V/+3.3 V操作;48铅LQFP和LFCSP;低功耗(3V时最小30 mW);低功率备用模式(3V时典型为6MW);工业温度范围(-40°C至+85°C);符合RoHS的软件包;适合汽车应用。

应用

数字视频系统;高分辨率彩色图形;数字无线电调制;图像处理;仪表;视频信号重建;汽车信息娱乐单元。

一般说明

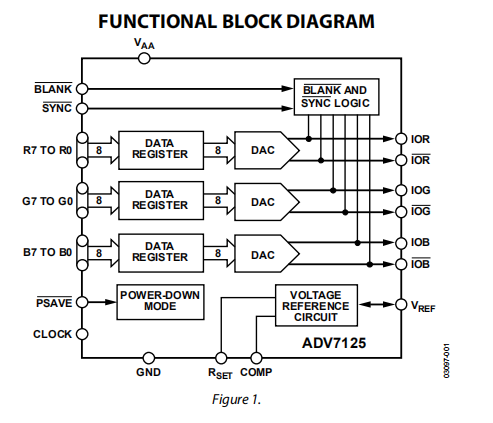

ADV7125(ADV)是一款三重高速、数模转换器单片芯片上的转换器(DAC)。它由三部分组成带互补输出的高速8位视频DAC标准TTL输入接口和高阻抗模拟输出电流源。

ADV7125有三个独立的8位宽输入端口。一个单+5V/+3.3V电源和时钟使设备正常工作所必需的。ADV7125有附加视频控制信号,复合同步和空白,以及省电模式。

ADV7125采用5V CMOS工艺制造。它的单片CMOS结构保证了更大的功能和更低的功耗。ADV7125有48铅LQFP和48铅LFCSP两种包装。

产品亮点

1、330msps(仅3.3v)吞吐量。

2、保证单调到8位。

3、兼容多种高分辨率彩色图形系统,包括RS-343A和RS-170。

术语

消隐电平

将波形的同步部分与视频部分分开的电平。通常称为前廊或后廊。在0 IRE单位,是关闭显像管的电平,从而产生可能最黑的图像。

彩色视频(RGB)

这是指将红色、绿色和蓝色三种原色结合起来,在通常的光谱范围内生成彩色图片的技术。在RGB监视器中,需要三个dac,每种颜色一个。

同步信号(Sync)

同步扫描过程的复合视频信号的位置。

灰度

视频信号在参考黑电平和参考白电平之间的离散电平。8位DAC包含256个不同级别。

光栅扫描

一次扫描一行CRT以生成和显示图像的最基本方法。

参考黑电平

视频信号的最大负极性幅度。

参考白电平

视频信号的最大正极性幅度。

同步级别

同步信号的峰值电平。

视频信号

在参考白和参考黑之间灰度级变化的复合视频信号部分。也被称为图像信号,这是可以被视觉观察到的部分。

电路说明和操作

ADV7125包含三个8位DAC,带有三个输入通道,每个通道都包含一个8位寄存器。该设备还集成了一个参考放大器。CRT控制功能,空白和同步,集成在ADV7125上。

数字输入

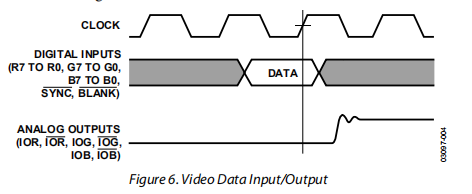

有24位像素数据(颜色信息),R0到R7,G0到G7,B0到B7,锁存在每个时钟周期上升沿的设备中。这些数据呈现给三个8位DAC,然后转换成三个模拟(RGB)输出波形(见图6)。

ADV7125有两个附加控制信号,以类似的方式锁定到模拟视频输出。空白和同步分别锁存在时钟的上升沿上,以保持与像素数据流的同步。

空白和同步功能允许将这些视频同步信号编码到RGB视频输出上。这是通过在模拟输出中添加适当加权的电流源来实现的,由空白和同步数字输入上的逻辑电平来确定。

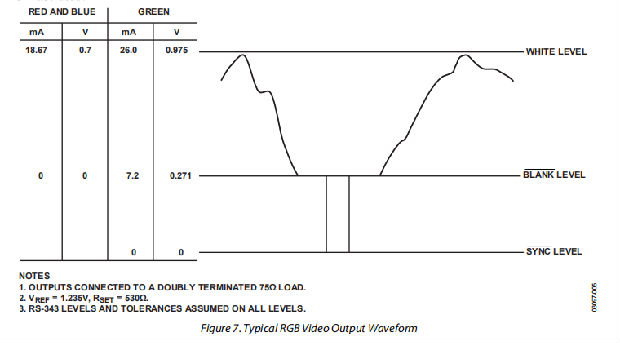

图7显示了ADV7125的模拟输出RGB视频波形。说明了同步和空白对模拟视频波形的影响。

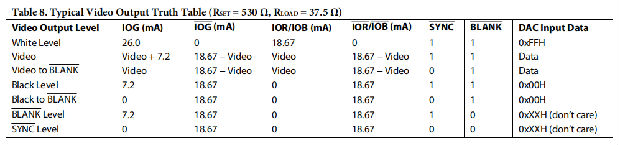

表8详细说明对模拟输出的结果影响

空白并同步。

所有这些数字输入都被指定为接受TTL逻辑电平。

时钟输入

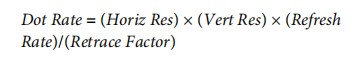

ADV7125的时钟输入通常是系统的像素时钟速率。它也被称为点速率。点速率和所需的时钟频率由屏幕分辨率根据以下等式确定:

水平面是每行的像素数。

垂直分辨率是每帧的行数。

刷新率是水平扫描速率。这是必须刷新屏幕的速率,对于非隔行系统,通常为60赫兹,对于隔行系统,则为30赫兹。回溯因子是总空白时间因子。这考虑到在每帧的总持续时间的某一部分(例如,0.8)中显示为空白。因此,对于分辨率为1024×1024、刷新率为60Hz且回溯系数为0.8的图形系统,Dot Rate = 1024 × 1024 × 60/0.8 = 78.6 MHz,所需时钟频率为78.6MHz。所有视频数据和控制输入都锁定在时钟上升沿的ADV7125中,如前面在数字输入部分中所述。建议ADV7125的时钟输入由TTL缓冲器(例如74F244)驱动。

视频同步与控制

ADV7125有一个复合同步(sync)输入控件。许多图形处理器和CRT控制器能够生成水平同步(HSYNC)、垂直同步(VSYNC)和复合同步。

在不自动生成复合同步信号的图形系统中,包含一些附加逻辑电路能够产生复合同步信号。同步电流在内部直接连接到IOG输出,从而将视频同步信息编码到绿色视频通道上。如果不需要将同步信息编码到ADV7125上,则同步输入应绑定到逻辑低。

参考输入

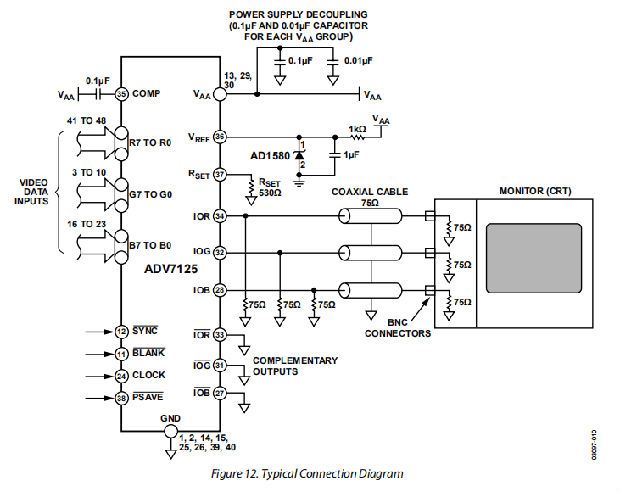

ADV7125包含车载参考电压。VREF引脚的连接应如图12所示。

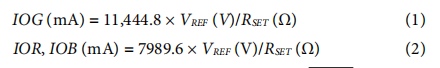

连接在RSET引脚和GND之间的电阻RSET根据ADV7125的等式1和等式2确定输出视频电平的振幅。

方程式1仅适用于ADV7125,当同步正在进行时使用。如果同步未被编码到绿色通道上,则方程式1与方程式2类似。

使用可变的RSET值可以精确地调整模拟输出视频电平。使用固定的560ΩRSET电阻器可产生规范章节中引用的模拟输出电平。这些值通常对应于RS-343A视频波形值,如图7所示。

数据采集卡

ADV7125包含三个匹配的8位DAC。DAC采用先进、高速、分段结构设计。对应于每个数字输入的位电流通过复杂的解码方案路由到模拟输出(位=1)或GND(位=0)。因为所有这些电路都在一个单片设备上,所以优化了三个dac之间的匹配。除了匹配,在单片设计中使用相同的电流源也保证了单调性和低故障。车载运算放大器可稳定满标度输出电流,以防温度和电源变化。

模拟输出

ADV7125有三个模拟输出,分别对应于红色、绿色和蓝色视频信号。

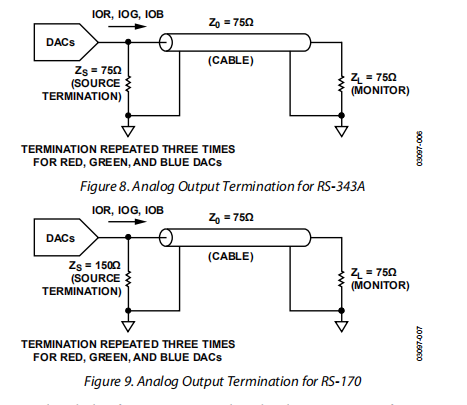

ADV7125的红色、绿色和蓝色模拟输出是高阻抗电流源。这三个RGB电流输出中的每一个都能够直接驱动37.5Ω负载,例如双端75Ω同轴电缆。图8显示了连接到双端接75Ω负载的三个RGB输出中每一个的所需配置。该装置可在75Ω显示器上产生RS-343A视频输出电压水平。

将RS-170视频电平驱动到75Ω监视器中的建议方法如图9所示。DACs的输出电流水平保持不变,但3个DACs上的源端电阻Z从75Ω增加到150Ω。

有关各种输出配置(包括RS-343A和RS-170)的负载终止的更详细信息,请参阅AN-205应用说明、视频格式和所需的负载终止。

图7显示了与三个驱动双端接75Ω负载的RGB输出图8。以及灰度级别(从黑色到白色级别),图7还显示了SYNC和ADV7125为空。这些控制输入将适当加权的电流添加到模拟输出,产生视频应用的特定输出电平要求。

表8详细说明了同步和空白输入如何修改输出级别。

灰度运算

ADV7125可用于独立、灰度(单色)或复合视频应用程序(即,仅一个频道用于视频信息)。三个频道中的任何一个,红色、绿色或蓝色,都可以用来输入数字视频数据。两个未使用的视频数据通道应绑定到逻辑0。未使用的模拟输出端应使用与所用通道相同的负载,即,如果使用红色通道,IOR端接双端75Ω负载(37.5Ω),IOB和IOG端接37.5Ω电阻(见图10)。

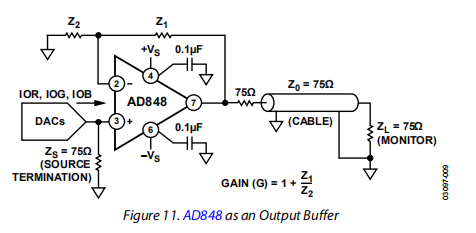

视频输出缓冲区

ADV7125指定用于驱动传输线负载。驱动这种负载的模拟输出配置在模拟输出部分中描述,并在图11中说明。然而,在某些应用中,可能需要驱动长传输线电缆长度。电缆长度超过10米会衰减和扭曲高频模拟输出脉冲。输出缓冲器的加入补偿了一些电缆失真。需要具有大的全功率带宽和2到4之间的增益的缓冲器。这些缓冲器还需要能够在整个输出电压摆幅上提供足够的电流。模拟设备产生一系列适用于此类应用的运算放大器。这些包括AD843、AD844、AD847和AD848系列单片运算放大器。在甚高频应用(80兆赫)中,建议使用AD8061。有关线路驱动器缓冲电路的更多信息,请参阅相关的运放数据表。

除了RS-343A和RS-170之外,使用缓冲放大器还可以实现其他视频标准。改变缓冲电路的增益分量可得到任何所需的视频电平。

PCB布局注意事项

ADV7125经过优化设计,可使辐射和传导噪声的性能降到最低。为了补充ADV7125出色的噪声性能,必须非常注意PCB布局。图12显示了ADV7125的推荐连接图。

在ADV7125电源线和地线上,应优化布局以使噪音最低。这可以通过屏蔽数字输入和提供良好的解耦来实现。缩短V和GND引脚组之间的引线长度,以最小化感应振铃。

建议使用具有单个接地平面的4层印刷电路板。接地面和电源面应分开信号跟踪层和焊料侧层。使用多个去耦电容器可以进一步降低模拟电源平面上的噪声(见图12)。采用0.1μF和0.01μF陶瓷电容器可获得最佳性能。通过将电容器放置在尽可能靠近装置的位置,使电容器引线尽可能短,从而使引线电感最小化,从而将每个V引脚单独地与接地分离。值得注意的是,虽然ADV7125包含抑制电源噪声的电路,但这种抑制随频率而降低。如果使用高频开关电源,应密切注意降低电源噪声。直流电源滤波器(Murata BNX002)在开关电源和主PCB之间提供EMI抑制。或者,可以考虑使用3端电压调节器。

数字信号互连

尽可能将ADV7125的数字信号线与模拟输出和其他模拟电路隔离。数字信号线不应覆盖模拟电源平面。

由于使用的时钟频率很高,应避免到ADV7125的长时钟线,以最大限度地减少噪声拾取。

将数字输入的任何有源上拉终端电阻器连接到常规PCB电源平面(V),而不是模拟电源平面。

模拟信号互连

将ADV7125尽可能靠近输出连接器,从而最大限度地减少由于阻抗不匹配而引起的噪声拾取和反射。

视频输出信号应该覆盖接地平面而不是模拟电源平面,从而使高频电源抑制最大化。

为了获得最佳性能,模拟输出端对地电阻应为75Ω(双端接75Ω配置)。终端电阻应尽可能接近ADV7125,以尽量减少反射。

有关PCB设计的其他信息,请参阅AN-333应用说明、视频图形系统的设计和布局,以减少EMI。

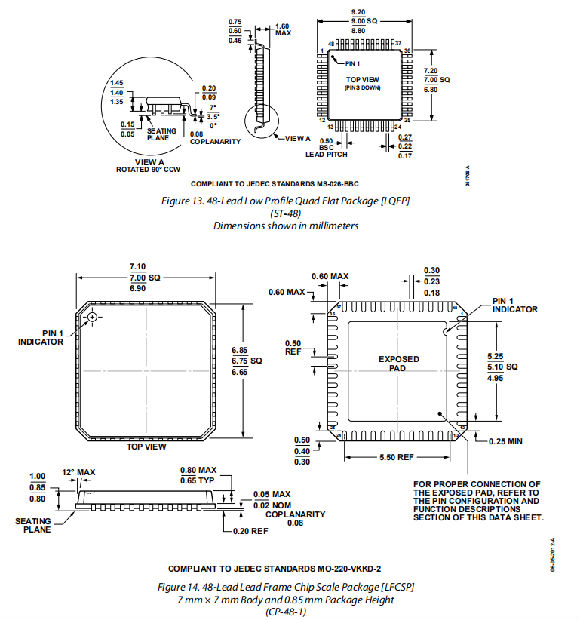

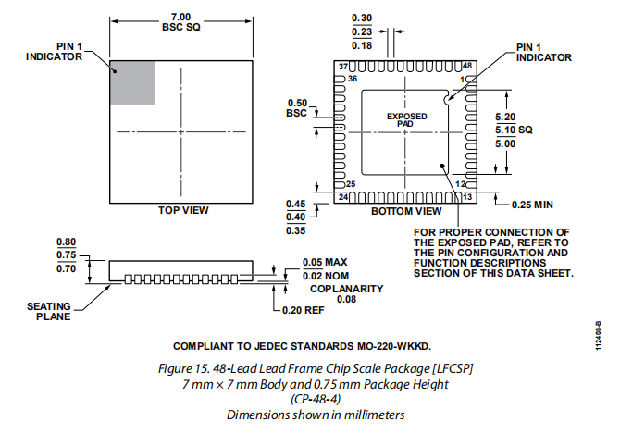

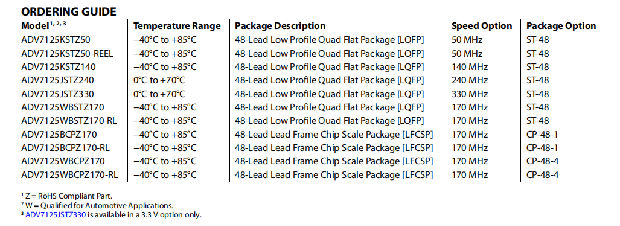

外形尺寸

汽车产品

ADV7125W车型提供受控制造,以支持汽车的质量和可靠性要求应用。请注意,这些车型的规格可能不同于商用车型;因此,设计师应仔细检查本数据表的规格部分。只有所示的汽车级产品可用于汽车应用。有关特定产品订购信息,请联系您当地的模拟设备客户代表,并获取这些车型的特定汽车可靠性报告。