AD5258点击型号即可查看芯片规格书

特征

非易失性存储器保持雨刮器设置;64位数字电位器;紧凑型MSOP-10(3毫米×4.9毫米)I2C兼容接口;VLogic引脚提供了增加的接口灵活性;端到端电阻1 kΩ、10 kΩ、50 kΩ、100 kΩ;存储在EEPROM中的电阻公差(0.1%精度);上电EEPROM刷新时间<1 ms软件写入保护命令;地址解码引脚AD0和地址解码引脚AD1允许每个总线有四个包;55°C下的100年典型数据保留;宽工作温度-40°C至+85°C 3 V至5 V单电源。

应用

液晶面板VCOM调整;液晶面板亮度和对比度控制;新设计中机械电位器的更换;可编程电源射频放大器偏置;汽车电子调整;增益控制和偏移调整;光纤到家庭系统;电子水平设置。

一般说明

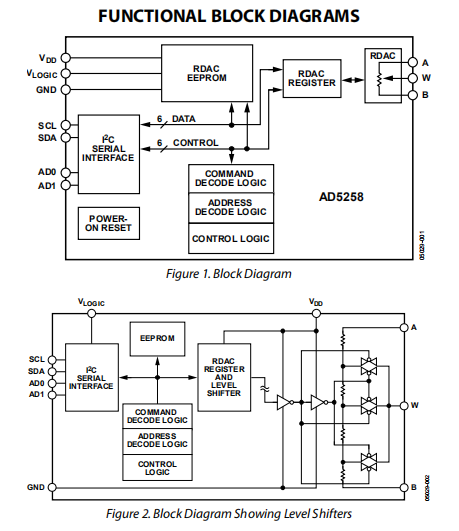

AD5258为64位调整应用提供了紧凑、不易挥发的3 mm×4.9 mm封装解决方案。这些器件执行与机械电位器或可变电阻器相同的电子调节功能,但具有增强的分辨率和固态可靠性。

雨刮器设置可通过IC兼容的数字接口进行控制,该接口还用于读取雨刮器寄存器和EEPROM内容。此外,电阻公差存储在EEPROM中,提供端到端的公差精度占0.1%。还有一个软件写保护功能,确保数据不能写入EEPROM寄存器。

单独的VLogic引脚提供了增加的接口灵活性。对于在一条总线上需要多个部件的用户,地址位AD0和地址位AD1允许在同一条总线上最多有四个设备。

1、术语数字电位计、可变电阻和RDAC可以互换使用。

操作理论

AD5258是一个64位数字控制可变电阻(VR)装置。编程EEPROM之前的雨刮器默认值为中刻度。

可变电阻编程

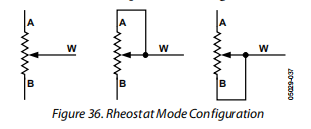

变阻器操作

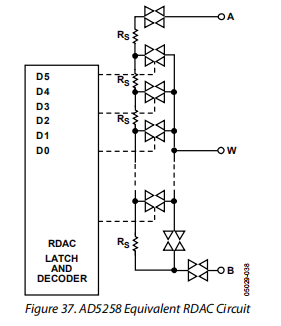

端子A和端子B之间的RDAC的标称电阻(RAB)为1 kΩ、10 kΩ、50 kΩ和100 kΩ。VR的标称电阻有64个触点可通过雨刮器端子接入。RDAC锁存器中的6位数据被解码以选择64种可能的设置之一。

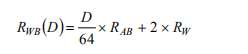

确定刮水器W和端子B之间数字编程输出电阻的一般公式是:

其中:D是加载在6位RDAC寄存器。RAB是端到端的阻力。RW是由每个内部开关。

注意,在零刻度条件下,有一个相对较低的有限雨刮器电阻值。应当注意,在该状态下限制刮水器W和端子B之间的电流流向不大于20毫安的最大脉冲电流。否则,可能会导致内部开关触点退化或损坏。

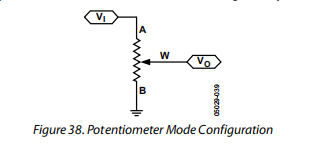

与机械电位器类似,刮水器W和端子A之间的RDAC的电阻产生数字控制的互补电阻R。RWA的电阻值设置在电阻的最大值开始,随着锁存器中加载的数据的值增加而减小。这个操作的一般方程式是:

典型的设备对设备匹配取决于工艺批次,其变化可能高达±30%。因此,电阻公差存储在EEPROM中,这样用户将知道实际RAB在0.1%以内。

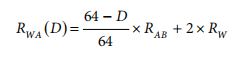

对电位计分压器编程

电压输出操作

数字电位器很容易在雨刮器W至端子B和雨刮器W至端子a处产生与a至端子B处输入电压成比例的分压器。与VDD至GND的极性(必须为正)不同,电压通过端子a至端子B,雨刮器W至端子a,雨刮器W到端子B可以处于任一极性。

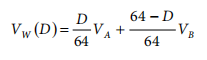

如果忽略擦拭器电阻对近似的影响,将A端子连接到5 V和B端子接地,在刮水器W-B端子处产生输出电压,从0 V到1 LSB,小于5 V。对于施加到端子A的任何有效输入电压,定义在V上相对于地的输出电压的一般方程。端子B是:

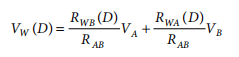

更精确的计算包括雨刮器阻力(VW)的影响:

数字电位器在分压器模式下的操作会导致更精确的超温操作。与变阻器模式不同,输出电压主要取决于内部电阻(RWA和RWB)的比值,而不是绝对值。

集成电路接口

注意,在编程EEPROM之前,雨刮器的默认值是中刻度。

当SCL高时,SDA线路上发生从高到低的转换时,主机通过建立启动条件来启动数据传输(见图3)。下一个字节是从机地址字节,由从机地址(前七位)和一个R/W位组成。当R/W位高时,主设备读取从设备。当R/W位低时,主设备写入从设备。

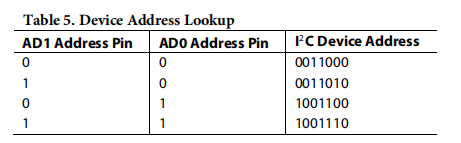

部件的从机地址由两个可配置的地址引脚AD0和AD1决定。这两个管脚的状态在通电时注册并解码成相应的IC7位地址(见表5)。与发送地址位相对应的从机地址通过在第九时钟脉冲期间将SDA线拉低来响应(这称为从机确认位)。

在此阶段,总线上的所有其他设备保持空闲,而所选设备等待数据写入或读取其串行寄存器。

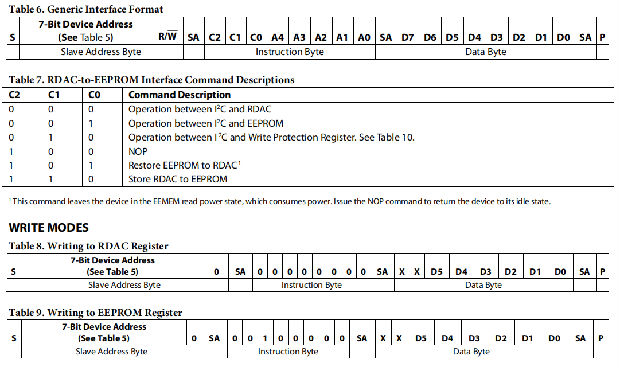

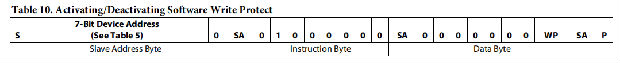

写作

在写模式下,从地址字节的最后一位(R/W)为逻辑低。第二个字节是指令字节。指令字节的前三位是指令位(见表6)。用户必须选择是写入RDAC寄存器还是EEPROM寄存器或激活软件写保护(见表7至表10)。最后五位都是零(见表13和表14)。从机在第九个时钟脉冲期间再次将SDA线拉低。

最后一个字节是数据字节MSB first。不在乎可以高也可以低。在写保护模式的情况下,不会存储数据;相反,LSB中的高逻辑启用写保护。同样,逻辑低禁用写保护。从机在第九个时钟脉冲期间再次将SDA线拉低。

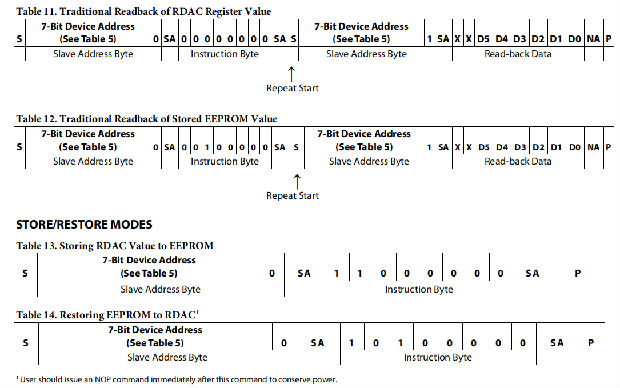

存储/恢复

在这种模式下,只需要地址和指令字节。地址字节的最后一位(R/W)是逻辑低位。指令字节的前三位是指令位(见表6)。这两种选择是将数据从RDAC传输到EEPROM(存储)或从EEPROM传输到RDAC(还原)。最后五位都是零(见表13和表14)。此外,用户应在将EEMEM设置恢复为RDAC后立即发出NOP命令,从而最小化电源电流损耗。

阅读

假设感兴趣的寄存器不是直接写入的,那么有必要编写一个虚拟地址和指令字节。指令字节将根据所需数据是RDAC寄存器、EEPROM寄存器还是公差寄存器而变化。

发送虚拟地址和指令字节后,需要重复启动。在重复启动之后,需要另一个地址字节,但这次R/W位是逻辑高位。此地址字节之后是包含指令字节中请求的信息的回读字节。读取位出现在时钟的负边缘。不在乎可能处于高或低的状态。

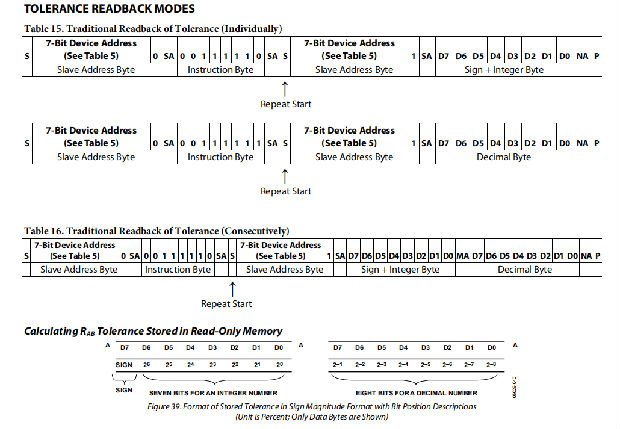

公差寄存器可以单独读取(参见表15)或连续(见表16)。有关解释公差字节的详细信息,请参阅“读取模式”部分。

在读取或写入所有数据位后,主机将建立停止条件。当SCL高时,停止条件被定义为SDA线上的从低到高的转换。在写入模式下,主机在10时钟脉冲期间将SDA线拉高,以建立停止条件(见表8)。在读取模式下,主机对第九个时钟脉冲(即SDA线路保持高电平)发出no应答。然后,主机在10时钟脉冲之前将SDA线调低,并将SDA调高以建立停止条件(见表11)。

重复写入功能为用户提供了在仅寻址和指示该部件一次之后多次更新RDAC输出的灵活性。例如,在RDAC在写模式下确认其从机地址和指令字节后,RDAC输出在每个连续字节上更新,直到接收到停止条件为止。如果需要不同的指令,写入/读取模式必须用新的从机地址、指令和数据字节重新启动。同样,也允许RDAC的重复读取功能。

下面是泛型、写、读和存储/还原控制表5。AD5258的设备地址查找寄存器参考表5中列出的设备地址,下面是模式/条件参考键。

S=启动条件

P=停止条件

SA=从机确认

MA=主确认

NA=无确认

W=写入

R=读取

X=不在乎

AD1和AD0是两个状态地址管脚。

通用接口

在编程EEPROM之前,雨刮器的默认值是中刻度。

要激活写保护模式,表10中的WP位必须为逻辑高。要停用写保护,必须重新发送命令,除非WP处于逻辑零状态。

读取模式

读取模式被称为传统模式,因为所有三种情况下的前两个字节都是虚拟字节,用于将指针指向正确的寄存器。这就是重复开始的原因。理论上,如果用户表11。RDAC寄存器值的传统回读对读以前写过的寄存器感兴趣。例如,如果EEPROM刚刚被写入,用户可以跳过两个伪字节,直接进入从地址字节,然后是EEPROM的读回数据。

AD5258在非易失性存储器中具有专利的RAB公差存储器。公差在工厂生产过程中存储在存储器中,用户可以随时读取。存储公差的知识允许用户精确地计算R。此功能对于精确性、变阻器模式和开环应用非常有用,其中绝对电阻的知识至关重要。AB公司

存储的公差位于只读内存中,并以百分比表示。公差以符号大小二进制形式存储在两个内存位置字节中(见图39)。两个EEPROM地址字节是11110(符号+整数)和11111(十进制数)。这两个字节可以通过两个单独的命令单独访问(见表15)。或者,可以在一个命令中读取第一个字节后接第二个字节(见表16)。在后一种情况下,如果连续读取,则存储器指针从第一个EEPROM位置自动递增到第二个EEPROM位置(从11110递增到11111)。

在第一个内存位置,将MSB指定为符号(0=+和1=-),将七个lsb指定为公差的整数部分。在第二存储器位置,所有八个数据位都被指定为公差的小数部分。请注意,小数部分只有0.1%的有限精度。例如,如果额定R=10 kΩ,从地址11110读取的数据显示0001 1100,从地址11111读取的数据显示:

0000 1111,公差可计算为:

MSB:0=+

下一个7 MSB:001 1100=28

8最小有效位:0000 1111=15×2=0.06–8个

公差=28.06%

四舍五入公差=28.1%,因此

拉布实际值=12.810 kΩ

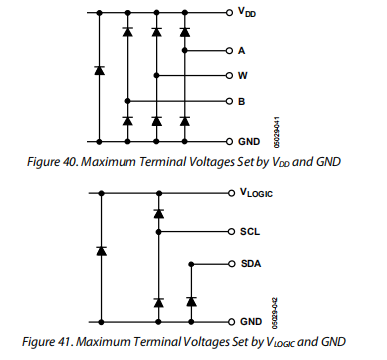

数字管脚和电阻端子的ESD保护

AD5258 VDD、VLOGIC和GND电源定义了正确3端和数字输入操作的边界条件。端子A、端子B和端子W上出现的超过VDD或GND的电源信号被内部正向偏置ESD保护二极管钳制(见图40)。数字输入SCL和数字输入SDA由ESD保护二极管对VLOGIC和GND进行钳位,如图41所示。

通电顺序

由于ESD保护二极管限制了端子A、端子B和端子W处的电压符合性(见图40),因此在对端子A、端子B和端子W施加任何电压之前,必须为GND/VDD/VLOGIC通电;否则,二极管正向偏置,使得VDD和VLOGIC无意中通电,并且可能影响用户电路。理想的通电顺序如下:GND、VDD、VLOGIC、数字输入,然后是VA、VB、VW。相对顺序对VA、VB、VW和数字输入的供电并不重要,只要它们在GND、VDD和VLOGIC之后供电。

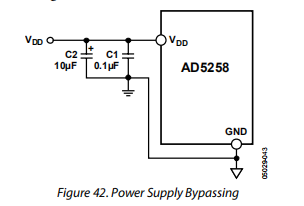

布局和电源旁路

最好采用紧凑、最小引线长度的布局设计。通向输入端的导线应尽可能直接,导线长度应最小。接地路径应具有低电阻和低电感。同样,为了达到最佳的稳定性,用高质量的电容器旁路电源也是一个很好的做法。应使用0.01μF至0.1μF的片状或片状陶瓷电容器绕过设备的电源线。此外,应在电源处使用低ESR 1μF至10μF的钽或电解电容器,以尽量减少任何瞬态干扰和低频波动(见图42)。此外,数字地面应远程连接到模拟地面的一个点,以尽量减少地面反弹。

一条总线上有多个设备

AD5258有两个可配置的地址引脚AD0和AD1。这两个管脚的状态在通电时注册,并解码成相应的IC兼容7位地址(见表5)。这允许总线上多达四个设备独立地写入或读取。2

显示应用程序

电路

AD5258的一个特点是其独特的VLOGIC和VDD电源引脚分离。这样做的原因是在不总是提供所需电源电压的应用中提供更大的灵活性。

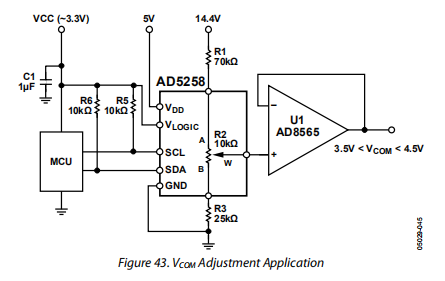

尤其是,液晶面板通常要求VCOM电压在3V到5V之间。图43中的电路是一个罕见的例外,其中5V电源可为数字电位器供电。

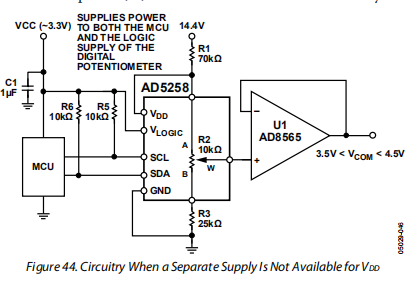

通常,只有模拟14.4V和数字逻辑3.3V电源可用(见图44)。通过在数字电位器的上方和下方放置离散电阻,可以将VDD从电阻串本身抽头。根据所选的电阻值,在这种情况下,VDD处的电压等于4.8 V,允许雨刮器安全运行至4.8V。VDD的电流消耗不会影响该节点的偏压,因为它只在微安量级。VLOGIC与微控制器(MCU)的3.3v数字电源相连,因为VLOGIC将在写入EEPROM时绘制所需的35ma。尝试通过70 kΩ电阻为35毫安供电是不切实际的;因此,VLOGIC没有与VDD连接到同一节点。

出于这个原因,VLogic和VDD被提供为两个独立的电源引脚,它们可以被捆绑在一起或独立处理;VLogic提供逻辑/EEPROM的功率,并且VDD偏置A、B和W端子以增加灵活性。

有关此应用程序的详细信息,请参阅2004年9月30日EDN杂志上的文章“简单VCOM调整使用任何逻辑电源电压”。

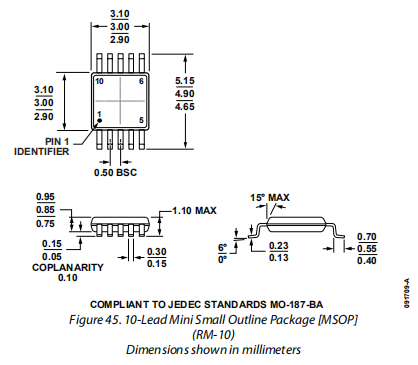

外形尺寸