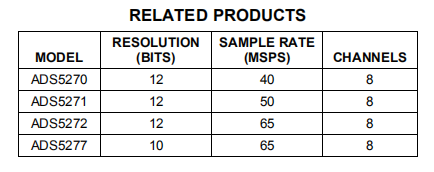

ADS5273点击型号即可查看芯片规格书

4096点击型号即可查看芯片规格书

特征

最大采样率:70MSPS;12位分辨率;没有丢失的代码;总功耗:内部参考:1W;外部参考:937mW;CMOS工艺;同时采样和保持;5MHz中频71dBFS信噪比;3.3V数字/模拟电源;序列化的LVDS输出;集成帧和位模式;双LVDS时钟输出电流选项;LVDS的四种电流模式;针和格式兼容的系列;TQFP-80 PowerPAD8482;组件。

应用

便携式超声系统;试验设备;军事。

说明

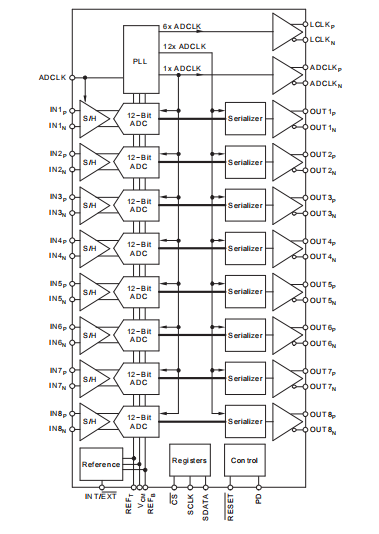

ADS5273是一种高性能CMOS、70MSPS、8通道模数转换器(ADC)。提供了内部参考,简化了系统设计要求。低功耗允许最高的系统集成密度。串行LVDS(低压差分信号)输出减少了接口线的数量和封装尺寸。

集成锁相环(PLL)将输入的ADC采样时钟乘以12倍。这种高频LVDS时钟用于数据串行化和传输过程。每个内部ADC的字输出都是序列化的,并首先传输MSB或LSB。除了八个数据输出外,还发送一个位时钟和一个字时钟。位时钟的速度是采样时钟的6倍,而字时钟的速度与采样时钟的速度相同。

ADS5273提供一个内部参考,或者可以选择使用外部参考驱动。最佳性能是通过内部参考模式实现的。

该设备采用PowerPAD TQFP-80封装,并在-40°C至+85°C的工作范围内进行指定。

规范的定义

模拟带宽

模拟输入频率,在该频率下,基频的谱功率(由FFT分析确定)降低3dB。

孔径延迟

输入采样时钟上升沿与采样发生的实际时间之间的时间延迟。

孔径不确定度(抖动)

孔径延迟的采样-采样变化。

时钟占空比

脉冲宽度高是ADCLK脉冲保持逻辑“1”状态以达到额定性能的最小时间量。脉冲宽度低是ADCLK脉冲应保持低状态的最短时间(逻辑“0”)。在给定的时钟速率下,这些规范定义了可接受的时钟占空比。

微分非线性(DNL)

理想的ADC显示的代码转换正好是1 LSB间隔。DNL是数字输出处任何单个LSB转换与模拟输入处理想1lsb步进的偏差。如果设备声称没有丢失的代码,则意味着所有可能的代码(对于12位转换器,4096个代码)都存在于整个工作范围内。

有效位数(ENOB)

与基于量化噪声的理论极限相比,ENOB是衡量转换器性能的一个指标。

积分非线性(INL)

INL是传递函数与参考线之间的偏差,该参考线以1lsb的分数测量,使用由最小二乘曲线拟合确定的最佳直线或最佳拟合。INL独立于偏移、增益或量化误差的影响。

最大转换率

最小转换率

这是ADC仍然工作的最小采样率。

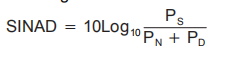

信噪比和失真(SINAD)

SINAD是基波功率(PS)与包括噪声(PN)和失真(PD)在内的所有其他谱分量功率(但不包括dc)的比值。

当基波的绝对功率用作参考时,SINAD以dBc(dB对载波)为单位给出;当基波的功率外推到转换器的满标度范围时,SINAD以dBFS(dB对满标度)为单位给出。

信噪比

SNR是基波功率(PS)与噪声下限功率(PN)之比,不包括直流功率和前八次谐波。

当基波的绝对功率用作参考时,信噪比以dBc(分贝对载波)为单位给出;当基波的功率外推到转换器的满标度范围时,信噪比以dBFS(分贝对满标度)为单位给出。

无杂散动态范围

基波功率与其它最高光谱分量(杂散或谐波)的比值。SFDR通常以dBc(dB到载波)为单位给出。

双音三阶互调失真

双音IMD3是基频(在频率f1和f2处)的功率与在频率2f1-f2或2f2-f1处三阶互调失真的最差频谱分量的功率之比。IMD3以dBc为单位(分贝到载波),当基波的绝对功率用作参考时,IMD3以dBc为单位给出;当基波的功率外推到转换器的满标度范围时,IMD3以dBFS(分贝到满标度)为单位给出。

执行参数测试时的编码速率。这是给定操作的最大采样率。

操作理论

概述

ADS5273是一个8通道高速CMOS ADC。它由一个高性能采样保持电路和一个12位ADC组成。每个通道给出的12位被序列化,并以LVDS格式在一对管脚上发送。ADS5273的所有八个信道都从一个称为ADCLK的时钟运行。八个通道中的每个通道的采样时钟都是从输入时钟生成的,使用匹配的时钟缓冲树。序列化器所需的12x时钟是使用锁相环(PLL)从ADCLK内部生成的。一个6x和一个1x时钟也输出为LVDS格式,与数据一起,以便于数据捕获。ADS5273运行从内部产生的参考电压修剪以将性能提高到准确度。此功能无需参考线的外部布线并改进设备间增益的匹配。名义上的REFT和REFB值分别为1.95V和0.95V。这些值意味着外部数据具有多个优点,例如减少了输出管脚的数量(节省了板上的布线空间)、降低了功耗以及减少了与ADS5273内的模拟电路的数字噪声耦合的影响。

ADS5273由两套电源和接地装置供电。模拟电源/接地装置表示为AVDD/AVSS,数字装置表示为LVDD/LVSS。

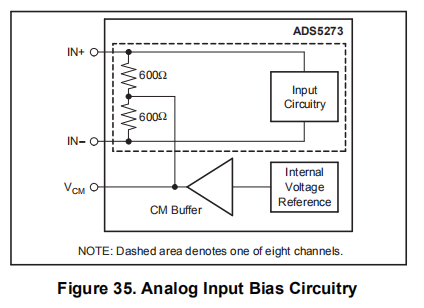

驱动模拟输入

模拟输入偏置如图35所示。使用两个600Ω电阻器对输入进行内部偏置,以启用交流耦合。建议每个输入引脚串联一个大于20Ω的电阻器。

使用4pF取样电容器取样输入。外接交流耦合器的选择电容器由最低的衰减决定所需的操作输入频率。衰减使用10nF交流耦合电容器的结果是输入–1V对应于ADC的零代码,+1V的差分输入对应于满标度代码(4095 LSB)。VCM(REFT和REFB的共模电压)也可通过引脚从外部获得,名义上为1.45V。

ADC采用由多位和单位内部级组合而成的流水线转换器结构。每个级将其数据馈送到数字纠错逻辑中,确保在12位级别上具有优异的差分线性度和无漏码。流水线结构导致6.5个时钟周期的数据延迟。

ADC的输出被发送到序列化程序

由锁相环产生的12倍时钟工作。这个每个通道的12个数据位被序列化先发送LSB。除了序列化数据之外序列化程序还生成一个1x时钟和一个6x时钟。这些时钟的产生方式与生成序列化数据,因此这些时钟保持与数据完美同步。数据和序列化程序的时钟输出在外部缓冲使用LVDS缓冲区。使用LVDS缓冲区传输数据在外部有多种优势,例如减少输出管脚数(节省布线空间在板上),降低功耗,以及数字噪声耦合对模拟信号的抑制效应ADS5273内部的电路。ADS5273由两套电源和理由。模拟电源/接地装置表示为AVDD/AVSS,而数字集由LVDD/LVSS。

驱动模拟输入

模拟输入偏置如图35所示使用两个600Ω电阻器内部偏置输入以启用交流耦合。大于20Ω的电阻是建议与每个输入引脚串联。使用4pF取样电容器取样输入。外接交流耦合器的选择电容器由最低的衰减决定所需的操作输入频率。衰减使用10nF交流耦合电容器的结果是0.04%。

如果输入是直流耦合的,那么输出驱动电路的共模电压ADS5273应与VCM(作为输出引脚)在±50mV范围内。建议驱动电路的输出共模为从设备提供的VCM派生。

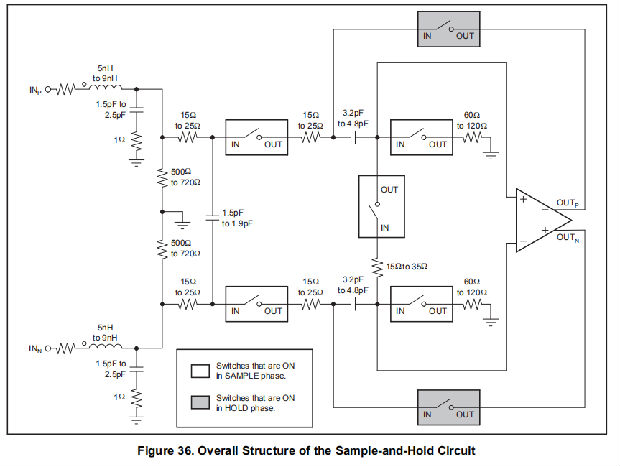

图36显示了采样保持电路。电路分成两部分工作阶段。在采样阶段,对输入进行采样两个标称为4pF的电容器。抽样电路由一个低通RC滤波器组成滤除可能存在差异的噪声成分耦合在输入引脚上。下一阶段是暂停电容器上电压采样的相位被传输(使用放大器)到子序列流水线ADC级。

输入过电压恢复

由ADS5273名义上是2.03V。ADS5273是专为处理过电压而设计差分峰间电压可超过ADC满标度范围的两倍。如果输入共模与过载期间的VCM(在标称值1.45V),从当输入从过载切换到零强度时,两倍于满标度脉冲幅度的过电压脉冲输入预计在三个时钟周期内。采样保持放大器(SHA)和ADC中的所有放大器都是专门为从过载信号中进行良好恢复而设计的。

在大多数应用中,ADC输入由差分正弦输入。而脉冲类型信号保持在峰值过载状态在它的高电平状态下,正弦信号间歇性达到峰值过载,在其最小值和极大值。这种情况对ADC输入和ADC输出的恢复(达到预期代码满量程的1%)。这通常发生在第二个时钟内,当输入以等于ADC差分满标度范围两倍的振幅正弦驱动时。

参考电路设计

数字波束形成算法依赖于所有接收信道的增益匹配。例如,一个典型的系统板上有12个八进制adc。在这种情况下,确保增益匹配至关重要,这基本上要求所有adc看到的参考电压相同。芯片八个通道内的匹配基准是通过使用一个内部基准电压缓冲器来完成的。在生产过程中调整每个芯片上的参考电压,确保不同芯片上的参考电压匹配良好。

设备内部操作所需的所有偏置电流均通过ISET引脚处的外部电阻接地来设置。在ISET上使用56.2kΩ电阻产生20μa的内部参考电流。该电流在内部镜像,以产生内部块的偏置电流。在ISET处使用更大的外部电阻可以降低参考偏置电流,从而降低器件的工作功率。但是,建议外部电阻在规定值56.2kΩ的10%范围内,以便各种块的内部偏置裕度适当。

缓冲内部带隙电压也会产生一个称为VCM的电压,该电压被设置为REFT和REFB的中间电平,并可在管脚上访问。它是作为一个参考电压来推导输入输入直接耦合时的共模。它也可用于派生引用外部参考模式中的共模电压。使用内部参考模式时,a 2Ω应在参考引脚之间添加电阻器(REFT和REFB)和去耦电容器,如如图37所示。如果设备用于外部参考模式,此2Ω电阻不是必修的。

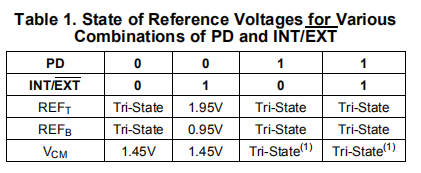

该设备还支持使用外部参考电压。此模式包括强制REFT以及外部参考文献。在这种模式下,内部参考缓冲器是三态的。自转换以来八个ADC的电流来自外部强制引用性能略低于内部使用参考文献。应该注意的是模式、VCM和ISET继续从内部带隙电压,如在内部参考模式。因此,确保共模电压外部强制参考电压与在VCM的50mV范围内。参考文献的状态局部放电和INT/EXT如表1所示。

计时

芯片上的八个通道从一个ADCLK输入。以确保光圈延迟和所有通道的抖动都是一样的,时钟树网络用于生成单个采样每个频道的时钟。所有的时钟路径通道从源点匹配所有到采样保持放大器的路。这确保了所有频道的演出和时间安排都一样。使用时钟树进行匹配引入光圈延迟,定义为ADCLK上升沿与采样的实际瞬间。所有的光圈都延迟了信道匹配到尽可能好的程度。然而,可能存在±20pS(±3)的错配。在八个ADC的光圈瞬间之间在同一芯片内。然而,光圈延迟两个不同芯片上的ADC可以是几个相隔100皮秒。另一个关键规格是孔径抖动,定义为采样瞬间的不确定度。入口时钟路径设计为提供大约1ps。

理想情况下,输入ADCLK应具有50%的负载循环。但是,当将ADCLK路由到不同的机载部件,ADCLK的占空比达到ADS5273可以偏离50%。一个较小(或较大)占空比可缩短时间可用于每个电路的采样或保持相,因此不是最优的。因为这个原因内部锁相环用来产生一个内部时钟占空比为50%。输入采样瞬间,但是,是由外部时钟,不受锁相环抖动的影响。除了产生50%的占空比时钟ADC和PLL也产生一个12倍时钟序列化程序用于从串行数据流的模数转换器。PLL的使用自动指示最小采样率约为20MSPS。锁相环还要求输入时钟自由运行。如果输入时钟暂时停止(持续时间小于300ns),则PLL需要大约10秒来锁定输入时钟频率。

LVDS缓冲区

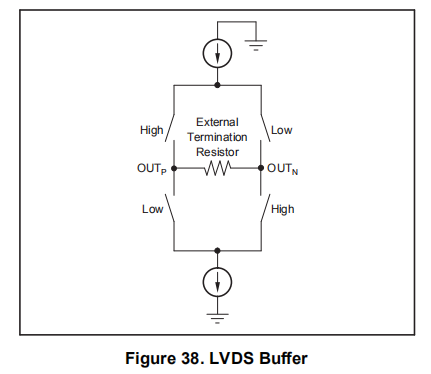

LVDS缓冲区有两个当前源,如图38所示。OUTP和OUTN由理想情况下约为100Ω的电阻负载外部加载。根据数据是0还是1,电流通过电阻器定向到一个方向或另一个方向。LVDS缓冲区有四个当前设置。默认电流设置为3.5mA,在100Ω电阻上提供大约±350mV的差分压降。

LVDS的单端输出阻抗将其序列化为单个数据流。对于70MHz的时钟频率,串行器的数据速率输出为840Mbps。数据首先输出LSB,具有寄存器可编程性,允许它首先还原为MSB。串行器还发送一个1x时钟和一个6x时钟。6x时钟(表示为LCLKP/LCLKN)用于同步LVDS数据的捕获。

也可以使用寄存器设置启用Deskew模式。该模式给出了一个交替0和1的数据流,可用于确定6x时钟和输出数据之间的相对延迟,以实现最佳捕获。序列化程序还生成一个1x时钟,并通过LVDS缓冲区传输。1x时钟(称为ADCLKP/ADCLKN)用于确定12位数据帧的开始。同步模式(通过寄存器设置启用)给出的数据是6 0s后6 1s。使用此模式,1x时钟可用于确定数据帧的开始。除了deskew模式模式和sync模式模式之外,用户还可以定义自定义模式并从LVDS缓冲区输出。LVDS缓冲区在断电模式下进行三次声明。LVDS输出通过10kΩ电阻(从每个输出引脚到1.2V)弱强制到1.2V。

噪声耦合问题

高速混合信号对各种噪声耦合类型。其主要来源之一noise是来自序列化程序和输出缓冲区。最大限度地采取隔离措施这些噪声源来自敏感的模拟块。作为起点,模拟和数字领域芯片上有清晰的界限。AVDD和AVSS用于表示模拟电源节,而LVDD和LVSS用于表示数字设备。注意确保是内部供应集之间的最小交互装置。噪声耦合程度从数字部分传送到模拟部分取决于:

1、每一个的有效电感电源/接地装置。

2、数字和模拟之间的隔离电源/接地装置。电源/接地的有效电感较小引脚导致更好的噪音抑制。为了这个原因是,使用多个管脚来驱动每个管脚电源/接地。还必须确保船上电源线和地线的阻抗保持在可能的最小值。使用板中的接地平面以及大型接地平面电源和之间的去耦电容器接地线是最有必要的设备的信噪比。

建议保持隔离使用单独的电源驱动AVDD和LVDD,以及AVSS和LVSS。使用LVDS缓冲器降低了注入噪声与CMOS缓冲器相比,这是相当可观的。这个LVDS缓冲区中的电流与切换方向。同时,低输出摆幅,如以及LVDS缓冲区的差异性,产生低噪声耦合。

断电模式

ADS5273有一个断电引脚,称为警察局。将PD拉高会导致设备进入关机模式。在这种模式下,引用和时钟电路和所有通道都是关机。设备功耗降至在这种模式下小于100兆瓦。在断电模式下,驱动REFT和REFB的内部缓冲器是三态及其输出被强制电压大约等于AVDD上电压的一半。速度从断电模式恢复取决于REFT和参考销。对于REFT和REFB less上的电容超过1μF时,参考电压稳定在1%以内它们的稳态值小于500微秒。个别通道也可以选择性供电通过编程寄存器关闭。

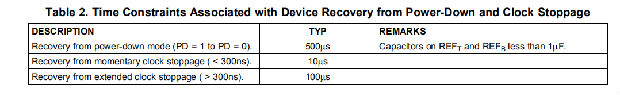

ADS5273还有一个内部电路监视停止时钟的状态。如果ADCLK是停止(或者如果它以低于3MHz的速度运行),这个监控电路产生一个逻辑信号处于关机状态的设备。因此设备的功耗降低到当ADCLK停止时超过100兆瓦。复苏从这样的断电可以大致100微秒;如表2所示。

重置

使用单独的电源驱动AVDD和LVDD,以及独立的地面飞机,在补给稳定后,需要AVSS和LVSS。给设备一个有效的复位脉冲。这个结果在所有内部寄存器中重置为默认值使用LVDS缓冲区可以降低0(非活动)的注入噪声值。如果没有重置,就有可能与CMOS缓冲器相比,这是相当可观的。一些寄存器可能处于非默认状态LVDS缓冲区中的电流与通电无关。这可能会导致设备切换方向。同时,低输出摆幅,作为故障。当重置激活时,设备以及LVDS缓冲区的差异性,在所有通道上输出0代码。然而,LVDS产生低噪声耦合。输出时钟不受重置影响。

PowerPAD热增强封装电路板的版图设计

ADS5273安装在80线电源板中热增强包装。充分利用设计的热效率PowerPAD封装,印刷电路板(PCB)的设计必须考虑到这一技术。请参阅PowerPAD brief SLMA004,使PowerPAD变得简单(可从以下网址下载),它解决了集成时需要考虑的事项将PowerPAD封装成PCB设计。更多详细信息,包括热模拟和维修程序,请参阅技术简介SLMA002,PowerPAD热增强组件()。

接口高速LVDS输出(SBOA104),一个应用程序报告讨论了一个简单的反序列化器的设计,该反序列化器可以反序列化LVDS输出最高840Mbps,可在TI网站()上找到。将高速多通道adc连接到XILINX FPGAs单独的应用程序报告(XAPP774)描述如何连接TI的高速多通道adc通过串行LVDS输出到Xilinx FPGAs可以直接从Xilinx网站下载。