205点击型号即可查看芯片规格书

450点击型号即可查看芯片规格书

AD9888点击型号即可查看芯片规格书

特征

205 MSPS最大转化率;500兆赫可编程模拟带宽;0.5 V至1.0 V模拟输入范围;小于450 ps p-p PLL时钟抖动@205 MSPS;3.3V电源;完全同步处理;同步检测“热插拔”;2:1模拟输入多路复用器;4:2:2输出格式模式;中刻度夹紧;断电模式;低功率:<1W,典型功率,205 MSPS。

应用

RGB图形处理;液晶显示器和投影仪;等离子显示屏;扫描转换器;微型显示器;数字电视。

一般说明

AD9888是一个完整的8位205 MSPS单片模拟接口,优化用于从个人计算机和工作站捕获RGB图形信号。它的205 MSPS编码速率能力和500兆赫的全功率模拟带宽支持高达UXGA(在75赫兹时为1600×1200)的分辨率。

为了便于设计和最小化成本,AD9888是一款完全集成的平板显示器接口解决方案。AD9888包括一个模拟接口和一个205兆赫的三重ADC,内部1.25伏参考电压,PLL从HSYNC和COAST产生像素时钟,中尺度钳位,可编程增益,偏移和钳位控制。用户仅提供3.3V电源、模拟输入、高速同步和滑行信号。

三态CMOS输出可以从2.5v供电到3.3v。

AD9888的片上PLL从HSYNC和COAST输入产生像素时钟。像素时钟输出频率范围从10兆赫到205兆赫。PLL时钟抖动在205 MSPS时通常小于450 ps p-p。当出现海岸信号时,PLL在没有HSYNC的情况下保持其输出频率。提供采样相位调整。保持数据、HSYNC和时钟输出相位关系。可禁用PLL,并提供外部时钟输入作为像素时钟。AD9888还为复合同步和绿色应用程序上的同步提供完全同步处理。

钳位信号是在内部产生的,或者可以由用户通过钳位输入引脚提供。该接口可通过2线串行接口完全编程。

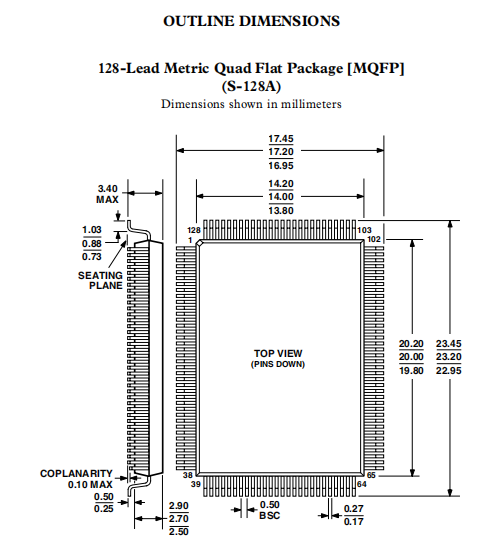

AD9888采用先进的CMOS工艺制造,采用节省空间的128引线MQFP表面贴装塑料封装,并在0°C至70°C的温度范围内指定。

设计指南

一般说明

AD9888是一个完全集成的解决方案,用于捕获模拟RGB信号并将其数字化,以便在平板显示器或投影仪上显示。该电路非常适合为高清晰度电视显示器或高性能视频扫描转换器提供计算机接口。

在高性能CMOS工艺中实现,该接口可捕获像素速率高达205 MHz的信号,并可使用替代像素采样模式捕获高达340mhz的信号。

AD9888包括所有必要的输入缓冲、信号直流恢复(钳位)、偏移和增益(亮度和对比度)调整、像素时钟生成、采样相位控制和输出数据格式化。所有控制都可以通过2线串行接口编程。这些敏感模拟功能的完全集成使得系统设计简单明了,对物理和电气环境的敏感度较低。

该装置的典型功耗仅为650兆瓦,工作温度范围为0°C至70°C,无需特别考虑环境因素。

输入信号处理

AD9888有六个高阻抗模拟输入引脚,分别用于红色、绿色和蓝色通道。它们将容纳0.5 V至1.0 V p-p的信号。

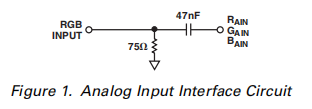

信号通常通过DVI-I连接器、15针D连接器或BNC连接器带到接口板上。AD9888应尽可能靠近输入接头。信号应通过匹配的阻抗轨迹(通常为75Ω)路由到IC输入引脚。

此时,信号应电阻端接(至信号接地回路),并通过47个nF电容器电容耦合至AD9888输入端。这些电容器构成直流恢复电路的一部分。

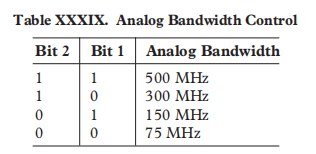

在阻抗完全匹配的理想世界中,尽可能宽的信号带宽可以获得最佳性能。AD9888(500 MHz)的超宽带输入可以在输入信号从一个像素级移动到下一个像素级时连续跟踪该信号,并在长时间的平坦像素时间内对该像素进行数字化。然而,在许多系统中,存在不匹配、反射和噪声,这可能导致输入波形的过度振铃和失真。这使得建立提供良好图像质量的采样阶段变得更加困难。AD9888可以在非常宽的频率范围(10兆赫到205兆赫)上数字化图形信号。通常在一个频率有益的特性在另一个频率有害。模拟带宽就是这样一个特点。对于UXGA分辨率(高达205mhz),由于快速的输入信号转换速率,需要非常高的模拟带宽。对于VGA和较低分辨率(低至12.5 MHz),非常高的带宽是不可取的,因为它允许过多的噪声通过。为了适应这些变化的需要,AD9888包括可变模拟带宽控制。提供四种设置(75兆赫、150兆赫、300兆赫和500兆赫),允许模拟带宽与输入图形信号的分辨率匹配。

同步处理

AD9888包含使其能够接受复合同步输入的电路,例如绿色同步或数字电视信号中的三电平同步。同步切片器和同步分隔符部分提供了同步处理功能的完整说明。

Hsync,Vsync输入

该接口还采用一个水平同步信号,用于产生像素时钟和钳位定时。可以在不应用Hsync(使用外部时钟、外部钳位和单端口输出模式)的情况下操作AD9888,但芯片的许多功能将不可用;建议提供Hsync。这可以是直接来自图形源的同步信号,也可以是经过预处理的TTL或CMOS电平信号。

Hsync输入包括一个Schmitt触发缓冲器,用于抗噪声和长上升时间信号。在典型的基于PC的图形系统中,同步信号只是TTL级驱动程序,在监视器电缆中提供非屏蔽线。因此,不需要或不希望终止。

串行控制端口

串行控制端口设计用于3.3V逻辑。如果有的话总线上的5V驱动器,这些引脚应使用150Ω系列电阻器进行保护,这些电阻器放置在上拉电阻器和输入引脚之间。

输出信号处理

数字输出被设计和指定为从3.3V电源(VDD)。它们还可以与低至2.5V的VDD一起工作,以与其他2.5V逻辑兼容。

夹紧

RGB夹紧

为了正确地数字化输入信号,必须调整输入端的直流偏移量,以适应车载A/D转换器的工作范围。

大多数图形系统在地面产生黑色的RGB信号,在大约0.75 V处产生白色。然而,如果同步信号被嵌入到图形中,同步尖常常在地上,黑色在300毫伏;白色大约为1 V。一些常见的RGB线放大器盒使用射极跟随器缓冲器来分离信号并增加驱动能力。这将向信号引入700 mV的直流偏移量,AD9888必须将其移除以进行正确捕获。

夹紧的关键是在已知图形系统产生黑色时识别信号的一部分(时间)。然后引入一个偏移量,当已知的黑色输入存在时,A/D转换器产生黑色输出(代码00H)。然后,当处理其他信号电平时,偏移保持在原位,并且整个信号被移位以消除偏移误差。

在大多数图形系统中,黑色在活动视频线之间传输。回到阴极射线管显示器,当电子束在屏幕上(右侧)完成水平线的写入时,电子束迅速偏转到屏幕的左侧(称为水平回溯),并提供黑色信号以防止电子束干扰图像。

在具有嵌入式同步的系统中,会短暂地产生比黑信号(Hsync)更黑的信号,向CRT发出开始回溯的信号。由于明显的原因,避免夹持Hsync的尖端是很重要的。幸运的是,Hsync之后几乎总是有一段时间称为后廊,在这里提供了一个很好的黑色参考。此时应进行夹紧。

只需在适当的时间(外部夹=1)使用夹销即可确定夹持正时。该信号的极性由钳位极性(寄存器0FH,位6)设置。

一种更简单的钳位定时方法是使用AD9888内部钳位定时发生器。钳制放置寄存器是用在钳制开始之前HSYNC后缘之后应该经过的像素次数进行编程的。第二个寄存器(钳位持续时间,寄存器06H)设置钳位的持续时间。这些都是8位值,提供了相当大的灵活性钳位生成。钳位定时参考Hsync的后缘,因为尽管Hsync持续时间变化很大,但后廊(黑色参考)始终跟随Hsync。建立箝位的一个好的起点是将箝位设置为08H(在同步后为图形信号提供8个像素周期以使其稳定),并将箝位持续时间设置为14H(为箝位提供20个像素周期以重新建立黑色参考)。

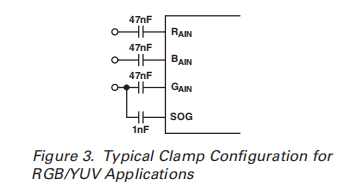

夹紧是通过在外部输入耦合电容器上放置适当的电荷来完成的。这个电容器的值会影响钳位器的性能。如果太小,在水平线时间(夹持间隔之间)内会有明显的振幅变化。如果电容器太大,那么钳位器将需要很长时间才能从输入信号偏移量的大变化中恢复过来。推荐值(47nf)导致在60hz SXGA信号上从100 mV的阶跃误差恢复到10行的1/2 LSB内,钳位持续时间为20像素周期。

YUV夹紧

YUV图形信号与RGB信号略有不同,因为dc参考电平(RGB信号中的黑色电平)可以位于视频信号的中点而不是底部。对于这些信号,可能需要钳制到A/D转换器范围(80H)的中刻度范围,而不是A/D转换器范围(00H)的底部。

通过在串行总线寄存器中设置钳位选择位,可以将钳位设置为中刻度而不是接地。红色和蓝色通道各自有自己的选择位,以便可以将它们单独钳制到中刻度或地面。钳位控制位于寄存器10H的位1和2中。每个A/D转换器夹在RMIDSCV和BMIDSCV引脚上独立提供的中刻度参考电压。应使用0.1μF电容器将这两个引脚旁路接地(即使不需要中刻度夹紧)。

增益和偏移控制

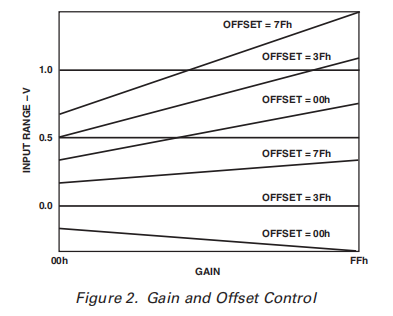

AD9888可容纳输入信号,输入范围为0.5 V至1.0 V满标度。满标度范围设置在三个8位寄存器中(红色增益、绿色增益和蓝色增益;分别为寄存器08H、09H和10H)。请注意,增加增益设置会导致图像的对比度降低。

偏移控制移动整个输入范围,导致图像亮度变化。三个7位寄存器(分别为红色偏移、绿色偏移、蓝色偏移;寄存器0BH、0CH和0DH)为每个通道提供独立设置。

偏移控制提供±63 LSB的调整范围。该范围与满标度范围相连,因此,如果输入范围加倍(从0.5 V到1.0 V),偏移步长也加倍(从2 mV/步到4 mV/步)。

图2说明了增益和偏移控制的相互作用。偏移调整中LSB的大小与满标度范围成比例,因此更改满标度范围也会更改偏移。如果偏移设置接近中刻度,则更改最小。更改偏移量时,满标度范围不受影响,但满标度级别的偏移量与零标度级别的偏移量相同。

绿色同步

绿色同步输入分两步操作。首先,它设置了一个负峰值检测器的基线钳位电平。其次,它设置同步触发电平(名义上比负峰值高150毫伏)。准确的触发电平是可变的,可以通过寄存器11H进行编程。绿色同步输入必须通过自己的电容器与绿色模拟输入进行交流耦合,如图3所示。电容器的值必须为1 nF±20%。如果未使用绿色同步,则不需要此连接,SOGIN管脚应保持未连接状态。(注意:绿色同步信号始终为负极。)有关更多详细信息,请参阅同步处理部分。

时钟产生

采用锁相环(PLL)产生像素时钟。Hsync输入为PLL提供参考频率。压控振荡器(VCO)产生更高的像素时钟频率。该像素时钟除以PLL除以值(寄存器01H和02H)并与Hsync输入相比较。任何错误都被用来转移VCO频率并保持两个信号之间的锁定。

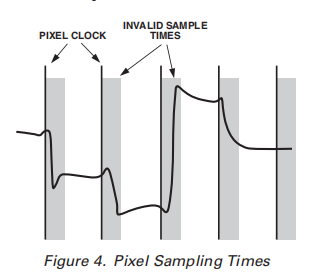

这个时钟的稳定性是提供最清晰和最稳定图像的一个非常重要的因素。在每个像素时间内,存在信号从旧像素振幅旋转并在其新值处稳定的时段。然后有一段时间,当输入电压稳定时,信号必须转换到一个新的值(图4)。回转时间与稳定时间之比是图形DAC带宽和传输系统带宽(电缆和终端)的函数。它也是整体像素率的函数。显然,如果系统的动态特性保持不变,那么回转和稳定时间也同样是固定的。必须从总像素周期中减去此时间,以保留稳定周期。在较高的像素频率下,总循环时间更短,稳定像素时间也更短。

时钟中的任何抖动都会降低确定采样时间的精度,还必须从稳定像素时间中减去。

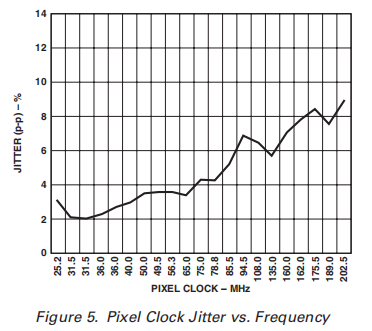

在AD9888的时钟产生电路的设计中,为了使抖动最小化,已经采取了相当谨慎的措施。如图5所示,在所有工作模式下,AD9888的时钟抖动小于总像素时间的9%,使得由抖动引起的有效采样时间的减少可以忽略不计。

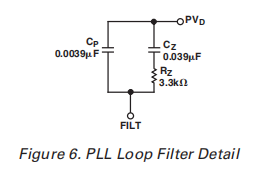

锁相环特性由环路滤波器设计、锁相环电荷泵电流和VCO范围设置决定。环路滤波器的设计如图6所示。表四列出了VESA标准显示模式的VCO范围和电荷泵电流的建议设置。

提供四个可编程寄存器以优化PLL的性能。这些寄存器是:

1、12位除数寄存器。输入的同步频率范围为15 kHz到110 kHz。PLL将Hsync信号的频率相乘,产生10mhz到205mhz范围内的像素时钟频率。除数寄存器控制精确的乘法因子。该寄存器可以设置为221到4095之间的任何值。(实际使用的除法比是编程的除法比加1。)

2、2位VCO范围寄存器。为了降低输出频率对控制信号噪声的灵敏度,将压控振荡器的工作频率范围划分为四个重叠区域。VCO范围寄存器设置此工作范围。因为只有四个可能的区域,所以只使用VCO范围寄存器的两个最低有效位。最低和最高区域的频率范围如表二所示。

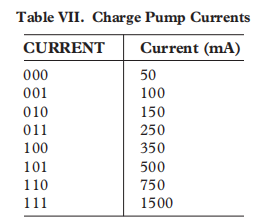

3、3位电荷泵电流寄存器。这会降低驱动低通环路滤波器变化的电流。表三列出了可能的电流值。

4、5位相位调整寄存器。所生成的采样时钟的相位可以偏移以在时钟周期内定位最佳采样点。相位调整寄存器提供32个移相步骤,每个步骤11.25°。具有相同相移的Hsync信号可通过hsout引脚获得。如果在外部提供像素时钟,则相位调整仍然可用。

COAST pin用于允许PLL在没有输入Hsync信号的情况下继续以相同的频率运行。这可以在垂直同步期间或Hsync信号不可用的任何其他时间使用。可通过海岸极性寄存器设置海岸信号的极性。此外,可以通过Hsync极性寄存器来设置Hsync信号的极性。

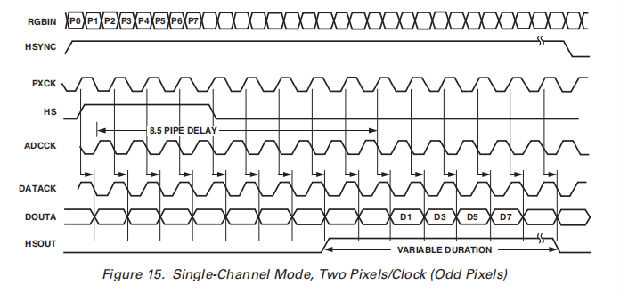

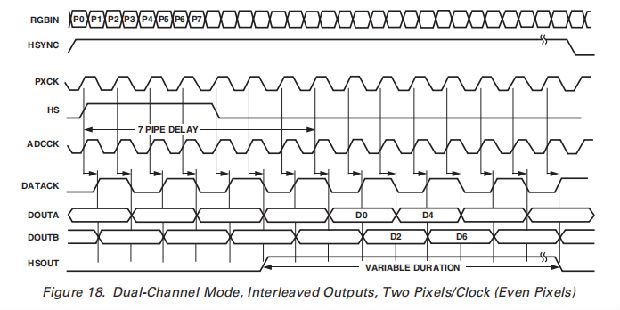

交替像素采样模式

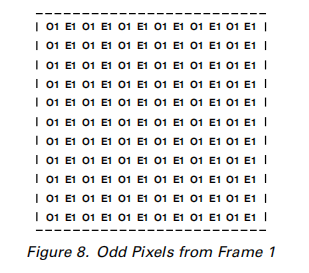

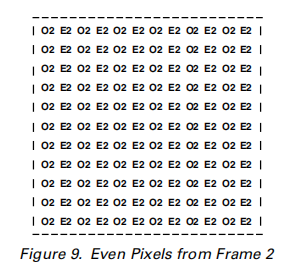

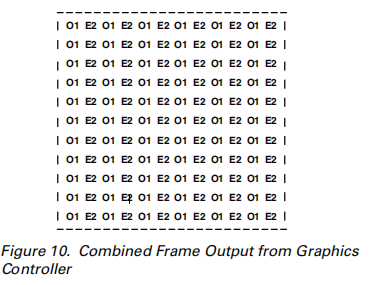

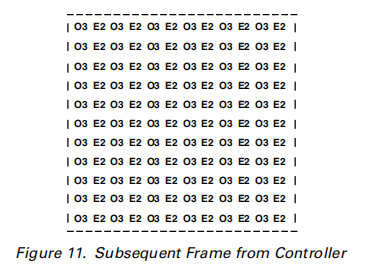

时钟反转(CKINV,引脚29)上的逻辑1输入反转标称ADC时钟。可以在帧之间切换CKINV以实现交替像素采样模式。这允许在较低的像素速率但较低的帧速率下实现更高的有效图像分辨率。

在一帧中,只有偶数像素被数字化。在随后的帧上,奇数像素被采样。通过在图形控制器中重建整个帧,可以重建完整的图像。这类似于广播电视系统中使用的隔行过程,但是隔行是垂直的而不是水平的。帧数据仍然以所需的全部刷新率(通常为60hz)呈现给显示器,因此没有添加闪烁伪影。

时机

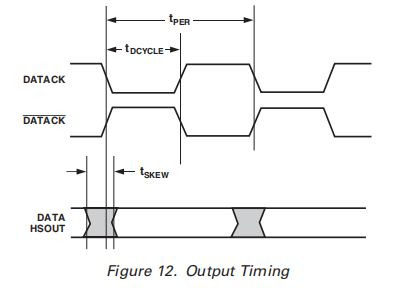

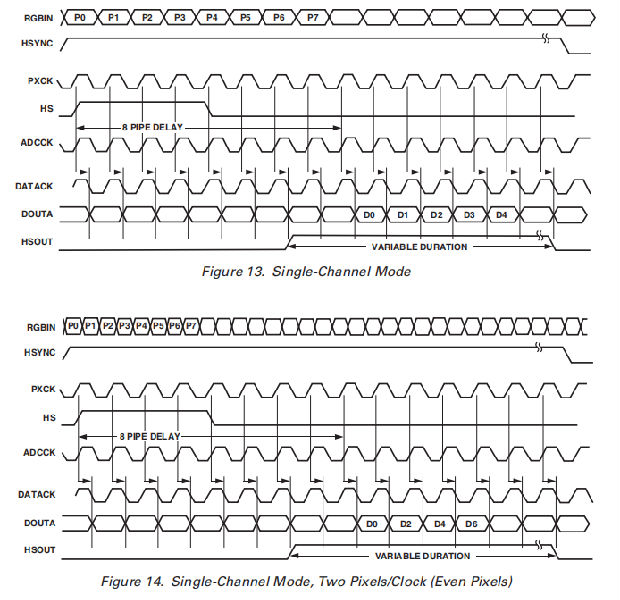

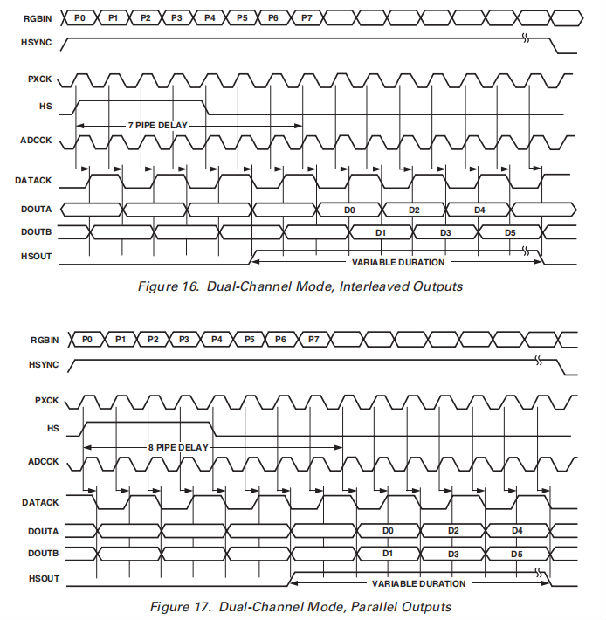

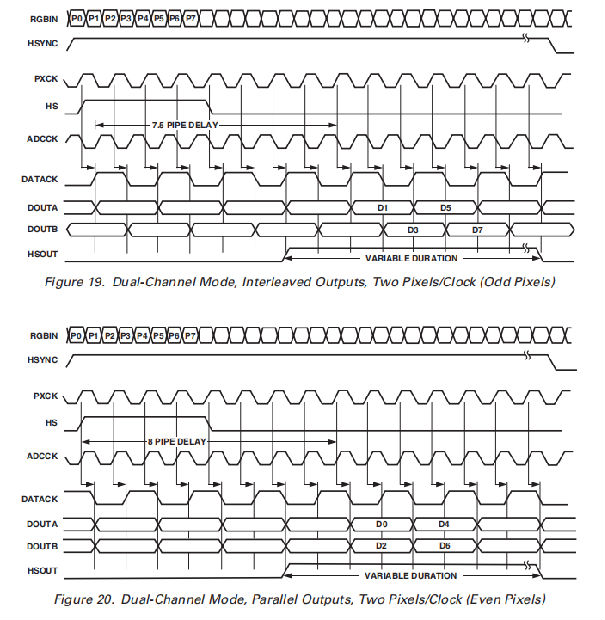

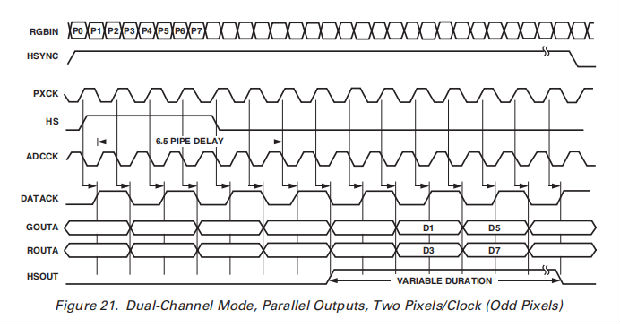

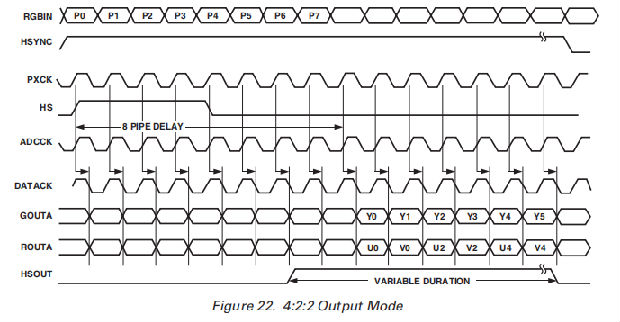

以下时序图显示了AD9888模拟接口在所有时钟模式下的操作。当Hsync的前缘被发送到“A”数据端口时,该部分通过发送与数字化像素对应的样本来建立定时。在双通道模式下,下一个样本是“B”端口。未来的样本在“A”和“B”数据端口之间交替。在单通道模式下,数据只发送到“A”数据端口,“B”端口处于高阻抗状态。

产生输出数据时钟信号,使其上升沿总是发生在“A”数据转换之间,并可用于外部锁定输出数据。

同步定时

在AD9888中处理水平同步,以消除相对于相位延迟像素时钟和数据的前缘定时的模糊性。

Hsync输入用作生成像素采样时钟的参考。可以通过相位调整寄存器(以优化像素采样时间)以32个步骤通过完整的360°来调整相对于Hsync的采样相位。显示系统使用Hsync来调整内存和显示写入周期,因此在Hsync输出(HSOUT)和数据时钟(DATACK)之间保持稳定的时序关系非常重要。

AD9888的水平同步有三种情况。首先,确定Hsync输入的极性,从而具有已知的输出极性。已知的输出极性可编程为高激活或低激活(寄存器0EH,位5)。其次,HSOUT与数据包和数据输出对齐。

第三,HSOUT(像素时钟)的持续时间是通过寄存器07H来设置的。HSOUT是应该用来驱动显示系统其余部分的同步信号。

滑行时间

在大多数计算机系统中,Hsync信号是通过一根专用线连续提供的。在这些系统中,海岸输入和功能是不必要的,不应使用。

然而,在某些系统中,Hsync在垂直同步期间(Vsync)受到干扰。在某些情况下,Hsync脉冲消失。在其他系统中,例如那些采用复合同步(Csync)信号或嵌入绿色同步(SOG)的系统中,Hsync在Vsync期间包括均衡脉冲或其他失真。为了避免在Vsync期间扰乱时钟生成器,忽略这些失真是很重要的。如果像素时钟PLL看到无关脉冲,它将尝试锁定到这个新频率,并在Vsync周期结束时改变频率。然后,需要几行正确的Hsync定时才能在新帧开始时恢复,从而导致显示器顶部的图像“撕裂”。

提供海岸输入以消除此问题。它是一个异步输入,禁用PLL输入,并允许时钟在其当时的频率自由运行。锁相环可以自由运行几条线路,而无明显的频率漂移。

2线串行控制寄存器详细芯片识别

007-0芯片修订

表示硅版本的8位寄存器。版次0=0000 0000,版次1=0000 0001。

分频器控制

01 7-0 PLL除以比MSBs

12位锁相环的8个最高有效位

除以比例PLLDIV。(操作分流比为PLLDIV+1。)

PLL从传入的Hsync信号导出主时钟。然后,主时钟频率除以整数值,使得输出被锁定到Hsync。该PLLDIV值确定每行的像素次数(像素加上水平消隐开销)。这通常比显示中的活动像素数多20%到30%。

PLL除法器的12位值支持从2到4095的除法比。该寄存器中加载的值越高,相对于固定的Hsync频率,得到的时钟频率就越高。

VESA已经建立了标准的定时规范,将有助于确定PLLDIV的值作为水平和垂直显示分辨率和帧速率的函数。

然而,许多计算机系统并不完全符合这些建议,这些数字只应作为指南使用。显示系统制造商应提供自动或手动优化PLLDIV的方法。设置不正确的PLLDIV通常会在显示屏上产生一个或多个垂直噪声条。误差越大,产生的钢筋数量就越多。

PLLDIV的加电默认值为1693(PLLDIVM=69H,PLLDIVL=DxH)。

AD9888仅在更改LSB时更新全除法比。单独写入此寄存器不会触发更新。

02 7-4 PLL分割比LSBs

12位PLL除比PLLDIV的四个最低有效位。操作分流比为PLLDIV+1。

PLLDIV的加电默认值为1693(PLLDIVM=69H,PLLDIVL=DxH)。

AD9888仅在写入该寄存器时才更新全除法比。

时钟发生器控制

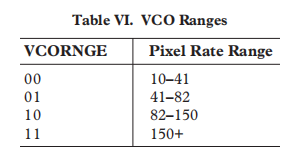

03 7-6 VCO范围选择

确定时钟发生器工作范围的两位。

VCORNGE必须设置为与所需的工作频率(输入像素速率)相对应。

锁相环在高频下具有最佳的抖动性能。由于这个原因,为了输出低像素速率并且仍然获得良好的抖动性能,PLL实际上以更高的频率工作,但是随后将时钟速率除以。表六显示了每个VCO范围设置的像素速率。PLL输出除数由VCO范围设置自动选择。

通电默认值为01。

03 5-3充电泵电流

在时钟发生器中建立驱动环路滤波器的电流的三位。

必须将电流设置为与所需工作频率(输入像素速率)相对应。

通电默认值为CURRENT=001。

04 7-3时钟相位调整

一个5位的值,在一个像素时间内32步调整采样相位。每一步代表取样阶段的11.25°位移。

通电默认值为16。

夹紧正时

05 7-0夹具放置

一种8位寄存器,用于设置内部产生的钳位器的位置。

当外部钳位控制位被设置为0时,在钳位放置所确定的位置和钳位持续时间所设置的持续时间内,在内部生成钳位信号。在Hsync的后缘之后开始钳制(钳制放置)像素周期。夹紧位置可编程为最大255的任何值,0除外。

钳位应该放置在输入信号呈现稳定的黑电平基准的时间段内,通常是Hsync和图像之间的后廊周期。

当外部钳位控制位设置为1时,该寄存器被忽略。

06 7-0夹紧持续时间

一种8位寄存器,用于设置内部产生的钳位的持续时间。

当外部钳位控制位被设置为0时,在钳位放置所确定的位置和钳位持续时间所设置的持续时间内,在内部生成钳位信号。钳制在Hsync的后缘之后开始(钳制放置)像素周期,并持续(钳制持续时间)像素周期。钳位持续时间可编程为1到255之间的任何值。不支持值0。

为了获得最佳结果,应将钳位持续时间设置为包括Hsync信号后缘之后的大部分黑色参考信号时间。夹紧时间不足会在屏幕顶部产生亮度变化,并从平均图像级别(APL)或亮度的大变化中缓慢恢复。

当外部钳位控制位设置为1时,该寄存器被忽略。

同步脉冲宽度

07 7-0同步输出脉冲宽度

一种8位寄存器,用于设置Hsync输出脉冲的持续时间。

Hsync输出的前沿由内部产生的相位调整PLL反馈时钟触发。然后,AD9888计算与该寄存器中的值相等的像素时钟数。这会触发Hsync输出的后缘,该输出也是相位调整的。

输入增益

08 7-0红色通道增益调整

设置红色通道增益的8位字。AD9888可容纳满标度范围在0.5 V和1.0 V p-p之间的输入信号。将REDGAIN设置为255对应于1.0 V的输入范围。REDGAIN设置为0可建立0.5 V的输入范围。请注意,增加REDGAIN会导致图像具有较小的对比度(输入信号使用较少的可用转换器代码)。见图2。

09 7-0绿色通道增益调整

设置绿色通道增益的8位字。见红增益(08)。

0A 7-0蓝色通道增益调整

设置蓝色通道增益的8位字。见红增益(08)。

输入偏移量

0B个

7-1红色通道偏移调整

设置红色通道的直流偏移量的7位偏移二进制字。一个偏移调整的LSB等于ADC偏移中的一个LSB变化。

因此,偏移调整的绝对大小随信道增益的变化而变化。标称设置为63会导致通道名义上将后廊(在夹紧间隔期间)夹紧至代码00。偏移量设置为127将导致信道箝位到ADC的代码64。偏移设置为0卡箍到代码–63(偏离范围底部)。增大“红色偏移”的值会降低通道的亮度。

0度

7-1绿色通道偏移调整

设置绿色通道的直流偏移量的7位偏移量二进制字。请参阅REDOFST(0B)。

0D个

7-1蓝色通道偏移调整

设置蓝色通道直流偏移量的7位偏移二进制字。请参阅REDOFST(0B)。

0E个

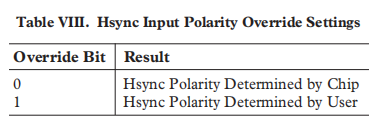

7同步输入极性超控

该寄存器用于覆盖内部电路,该电路确定进入锁相环的Hsync信号的极性

Hsync极性覆盖的默认值是0(极性由芯片决定)。

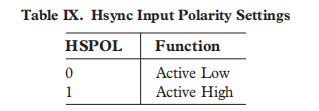

0E 6 HSPOL Hsync输入极性

必须设置的一个位,用于指示应用于PLL Hsync输入的Hsync信号的极性。

激活低表示Hsync脉冲的前沿是负的。所有的计时都基于Hsync的前沿,即下降沿。上升沿没有影响。

激活高表示Hsync脉冲的前沿正向。这意味着计时将基于Hsync的前沿,现在是上升沿。

如果该位设置不正确,设备将运行,但由钳位放置(寄存器05H)建立的内部生成的钳位将不会按预期放置,这可能会产生钳位错误。

通电默认值为HSPOL=1。

0E 5 Hsync输出极性

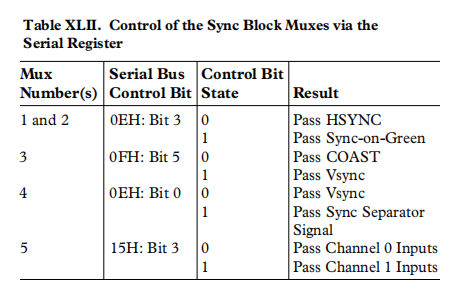

确定Hsync输出和SOG输出极性的一位。表X显示了这个选项的效果。SYNC表示同步脉冲的逻辑状态。

此寄存器的默认设置为0。

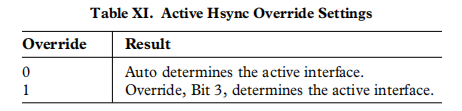

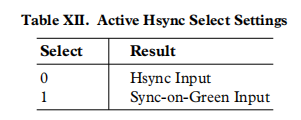

0E 4活动Hsync覆盖

此位用于覆盖自动Hsync选择。要重写,请将该位设置为逻辑1。重写时,活动的Hsync通过该寄存器中的位3设置。

此寄存器的默认值为0。

0E 3活动Hsync选择

此位在两种情况下使用。它用于在设置覆盖位(位4)时选择活动的Hsync。或者,它用于在不重写但同时检测到两个Hsync时确定活动Hsync。

此寄存器的默认值为0。

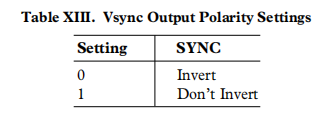

0E 2 Vsync输出反转

反转垂直同步输出极性的位。表十三显示了这一选择的效果。

此寄存器的默认设置为0。

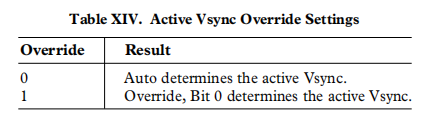

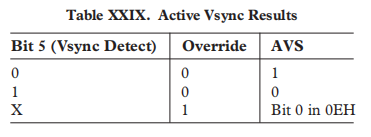

0E 1活动Vsync覆盖

此位用于覆盖自动Vsync选择。要重写,请将该位设置为逻辑1。重写时,活动接口通过该寄存器中的位0设置。

此寄存器的默认值为0。

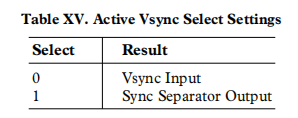

0E 0活动Vsync选择

此位用于在设置超程位(位1)时选择活动的Vsync。

此寄存器的默认值为0。

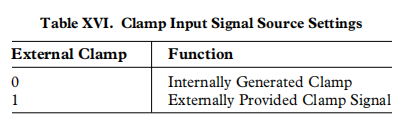

0F 7钳位输入信号源

一种确定钳位定时源的位。

0启用由钳位和钳位持续时间控制的钳位定时电路。夹紧位置和持续时间从Hsync的后缘开始计算。

A 1启用外部夹紧输入引脚。当钳位信号激活时,三个通道被钳位。钳位的极性由钳位极性位(寄存器0FH,位6)决定。

通电默认值为外部钳制=0。

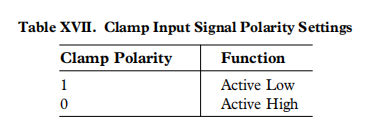

0F 6钳位输入信号极性

一种确定外部提供的钳位信号极性的位。

逻辑1表示当钳位低时电路将钳位,当钳位高时将信号传递给ADC。

逻辑0表示当钳位高时电路将钳位,当钳位低时将信号传递给ADC。

通电默认值为钳制极性=1。

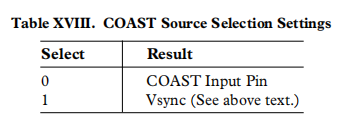

0F 5海岸选择

此位用于选择活动海岸源。可选择coast输入引脚或Vsync。如果选择了Vsync,则需要作出使用Vsync输入管脚或同步分离器输出的附加决定(寄存器0EH,位1,0)。

此寄存器的默认值为0。

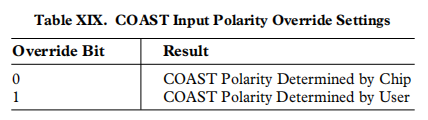

0F 4滑行输入极性超驰

该寄存器用于覆盖确定进入锁相环的海岸信号极性的内部电路。

海岸极性覆盖的默认值为0。

0F 3滑行输入极性

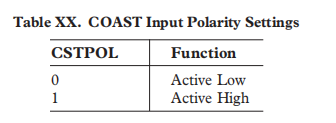

一个位,用于指示应用于PLL滑行输入的滑行信号的极性。

低激活意味着当COAST低时,时钟发生器将忽略Hsync输入,并继续以相同的标称频率运行,直到COAST高。

高激活意味着当COAST高时时钟发生器将忽略Hsync输入,并继续以相同的标称频率运行,直到COAST变低。

此功能需要与海岸极性超控位(位4)一起使用。

通电默认值为CSTPOL=1。

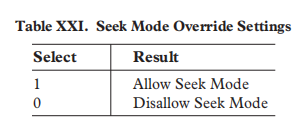

0F 2搜索模式覆盖

此位用于允许或禁止低功耗模式。当任何同步输入上都没有信号时,就会出现低功率模式(寻道模式)。

此寄存器的默认值为1。

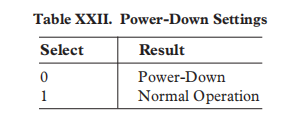

0F 1密码

该位用于将芯片置于断电模式。在这种模式下,芯片的功耗降低到典型功耗的一小部分(具体功耗见电气特性表)。当权时-向下,HSOUT、VSOUT、DATACK、DATACK和所有48个数据输出都进入高阻抗状态。(注意:SOGOUT输出未输入高阻抗。)断电期间继续激活的电路块包括电压参考、同步处理、同步检测和串行寄存器。这些模块有助于从断电状态快速启动。

此寄存器的默认值为1。

10 7-3绿色切片器同步阈值

此寄存器允许调整Syncon Green切片器的比较器阈值。该寄存器以10 mV的步调调整,最小设置等于10 mV,最大设置等于330 mV。

默认设置为15,对应于0.16 V的阈值。

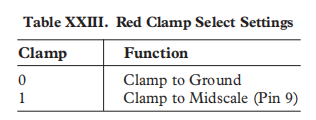

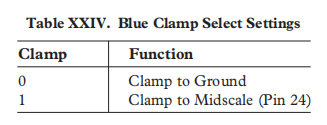

102红色夹钳选择

一种确定红色通道是固定在地面上还是固定在中刻度上的位。对于RGB视频,所有三个频道都参考地面。对于YcbCr(或YUV),Y通道参考地面,但CbCr通道参考中刻度。夹紧到中刻度实际上夹紧到销9。

此寄存器的默认设置为0。

10 1蓝色夹钳选择

一种确定蓝色通道是固定在地面上还是固定在中刻度上的位。夹紧到中刻度实际上夹紧到销24。

此寄存器的默认设置为0。

11 7:0同步分离器阈值

此寄存器用于设置同步分隔符的响应。它设置同步分隔符在切换高或低之前必须计数多少内部5兆赫时钟周期。它的工作原理就像一个低通滤波器,忽略Hsync脉冲以提取Vsync信号。这个寄存器应该设置为大于最大Hsync pulsewidth数。

注意:同步分离器阈值使用一个具有大约5兆赫频率的内部专用时钟。

这个寄存器的默认值是32。

12 7-0预海岸

此寄存器允许在Vsync信号之前应用滑行信号。在存在预均衡脉冲的情况下,这是必要的。此控件的步长为一个Hsync周期。

默认值为0。

13 7-0后海岸

该寄存器允许在Vsync信号之后应用滑行信号。这在存在均衡后脉冲的情况下是必要的。此控件的步长为一个Hsync周期。

默认值为0。

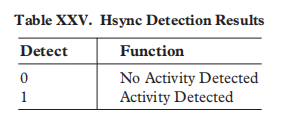

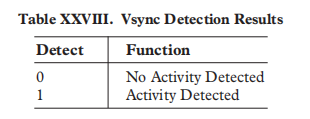

14 7同步检测

此位用于指示何时在选定的Hsync输入引脚上检测到活动。如果HSYNC保持高或低,则不会检测到活动。

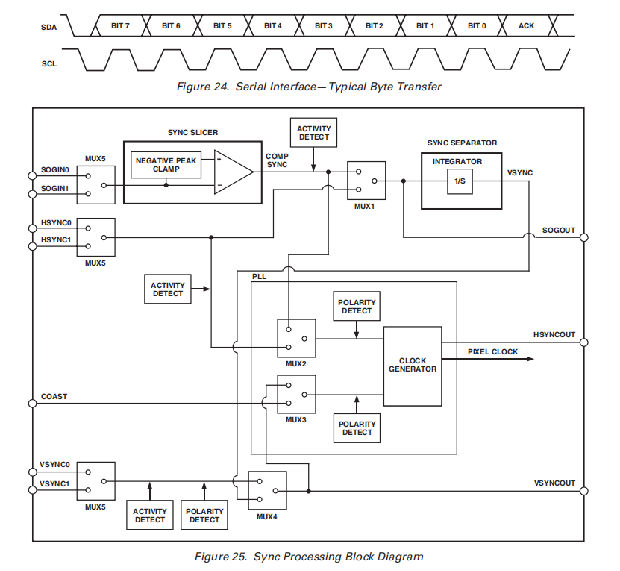

同步处理框图显示了此功能的实现位置。

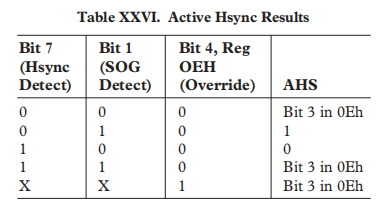

14 6 AHS–主动同步

此位表示PLL正在使用哪个Hsync输入源(Hsync输入或同步为绿色)。这个寄存器中的位7和位1决定使用哪个源。如果同时检测到Hsync和SOG,则用户可以通过寄存器0EH中的位3来确定哪个具有优先级。用户可以通过寄存器0EH中的位4来覆盖该功能。如果覆盖位被设置为逻辑1,则该位将被强制设置为寄存器0EH中位3的任何状态。

AHS=0表示使用HSYNC pin输入进行HSYNC。

AHS=1表示使用HSYNC的SOG pin输入。

重写位在寄存器0EH中,位4。

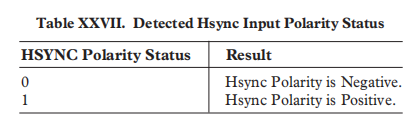

14 5检测到Hsync输入极性状态

该位报告HSYNC输入极性检测电路的状态。它可以用来确定HSYNC输入的极性。检测电路的位置如同步处理框图所示(图25)。

14 4垂直同步检测

此位用于指示何时在选定的Vsync输入管脚上检测到活动。如果Vsync保持高或低,则不会检测到活动。

同步处理框图(图25)显示了该功能的实现位置。

14 3 AVS–活动Vsync

此位表示正在使用哪个Vsync源;Vsync输入或同步分隔符的输出。这个寄存器的第4位决定了哪个是活动的。如果同时检测到Vsync和SOG,则用户可以通过寄存器0EH中的位0来确定哪个具有优先级。用户可以通过寄存器0EH中的位1来覆盖此功能。如果覆盖位被设置为逻辑1,则该位将被强制设置为寄存器0EH中位0的任何状态。

AVS=1表示同步分隔符。

AVS=0表示Vsync输入。

重写位在寄存器0Eh的位1中。

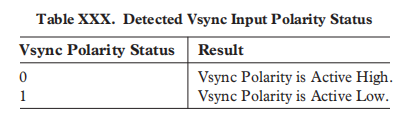

14 2检测到Vsync输出极性状态

该位报告Vsync输出极性检测电路的状态。它可以用来确定Vsync输入的极性。检测电路的位置如同步处理框图所示(图25)。

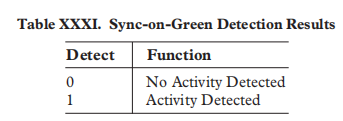

14 1绿色同步检测

此位用于指示何时在绿色输入端的选定同步上检测到同步活动。

同步处理框图(图25)显示了该功能的实现位置。

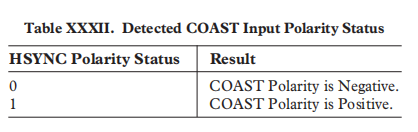

14 0检测到的海岸极性状态

该位报告滑行输入极性检测电路的状态。它可以用来确定海岸输入的极性。检测电路的位置如图25所示。

模式控制1

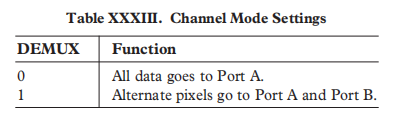

15 7通道模式

一种确定所有像素是呈现给单个端口(A)的位,还是将交替像素解复用到端口A和B的位。

当DEMUX=0时,端口B输出处于高阻抗状态。单端口模式的最大数据速率是110 MHz。从图13开始的时序图显示了这个选项的效果。

通电默认值为1。

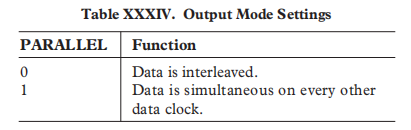

15 6输出模式

确定所有像素是否呈现给

端口A和端口B在每秒钟的数据包上升沿上同时运行,或在连续的数据包上升沿上交替运行。

当处于单端口模式(DEMUX=0)时,该位被忽略。时序图(图17)显示了这个选项的效果。

上电默认值为并行=1。

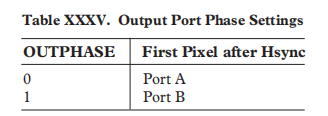

15 5输出端口相位

一位,用于确定是偶数像素还是奇数像素进入端口A。

在正常运行(输出相=0)时,当在双端口输出模式(DEMUX=1)下运行时,Hsync前缘后的第一个样本出现在端口A。随后的每个奇数样本出现在端口A。所有偶数样本都进入端口B。

当OUTPHASE=1时,这些端口颠倒,第一个样本转到端口B。

当DEMUX=0时,该位被忽略,因为数据总是只来自端口A。

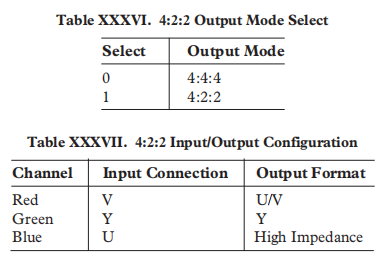

15 4 4:2:2输出模式选择

以4:2:2模式配置输出数据的位。此模式可用于将使用YUV、YCbCr或YPbPr图形信号的应用程序的数据线数量从24减少到16。此模式的时序图如图12所示。建议的输入和输出配置如表XXXVII所示。在4:2:2模式下,红色和蓝色通道可以互换,以帮助满足电路板布局或计时要求,但绿色通道必须为Y配置。

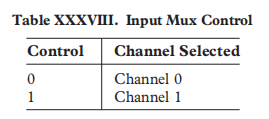

15 3输入多路控制

选择通道0的模拟输入或通道1的模拟输入的一种位。

15 2-1模拟带宽控制

选择模拟带宽的两位。

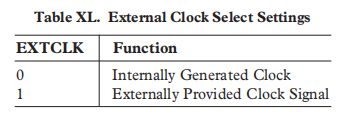

15 0外部时钟选择

一种确定像素时钟源的位。

逻辑0启用从外部提供的HSYNC生成像素时钟的内部PLL。

逻辑1启用外部CKEXT输入引脚。在这种模式下,PLL除法比(PLLDIV)被忽略。时钟相位调整(相位)仍然有效。

通电默认值为EXTCLK=0。

2线串行控制端口

提供2线串行控制接口。最多可将两个AD9888设备连接到2线串行接口,每个设备具有唯一地址。

2线串行接口包括时钟(SCL)和双向数据(SDA)管脚。AD9888用作通过串行接口接收和传输数据的从机。当串行接口未激活时,SCL和SDA上的逻辑电平被外部上拉电阻器拉高。

SDA线上接收或传输的数据必须在SCL正向脉冲期间保持稳定。只有当SCL低时,SDA上的数据才能更改。如果在SCL高时SDA改变状态,串行接口将该操作解释为启动或停止序列。

串行总线操作有五个组件:启动信号;从机地址字节;基址寄存器地址字节;读取或写入数据字节;停车信号。

当串行接口处于非活动状态(SCL和SDA高)时,通过发送启动信号启动通信。当SCL高时,SDA上的启动信号是从高到低的转换。此信号提醒所有从属设备数据传输序列即将到来。

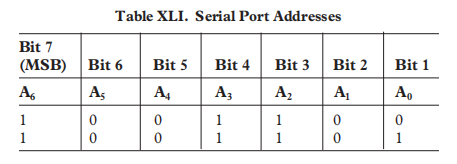

在开始信号之后传输的前8位数据包括7位从机地址(前7位)和单个R/W位(第8位)。R/W位指示从(1)读取或写入(0)从设备的数据传输方向。如果发送的从机地址与设备地址匹配(由表XLI中A0输入引脚的状态设置),则AD9888通过使第九个SCL脉冲的SDA低来进行确认。如果地址不匹配,则AD9888不确认。

通过串行接口传输数据

对于读或写的每个数据字节,MSB是序列的第一位。

如果AD9888在写入序列期间不确认主设备,则SDA保持高,以便主设备可以生成停止信号。如果主设备在读取序列期间不确认AD9888,则AD9888将其解释为“数据结束”。SDA保持高,以便主设备可以生成停止信号。

将数据写入AD9888的特定控制寄存器需要在建立从机地址之后写入感兴趣的控制寄存器的8位地址。此控制寄存器地址是后续写入操作的基址。基址自动递增一个字节,即在为基址准备的数据字节之后写入的每一个字节的数据。如果传输的字节多于可用地址,则地址将不递增,并保持其最大值19H。任何高于19H的基地址都不会产生确认信号。

以类似的方式从AD9888的控制寄存器读取数据。读取需要两个数据传输操作。

基址必须用从地址字节的R/W位低位写入,才能设置顺序读取操作。

读取(从机地址字节高的R/W位)从先前建立的基址开始。读取寄存器的地址在每个字节传输后自动递增。

要终止对AD9888的读/写序列,必须发送停止信号。停止信号包括当SCL高时SDA从低到高的转换。

当驱动串行接口的主设备在不首先生成停止信号以终止当前通信的情况下生成启动信号时,发生重复的启动信号。这用于在不释放串行接口线的情况下更改从机和主机之间的通信模式(读、写)。

串行接口读/写示例

写入一个控制寄存器启动信号

从地址字节(R/W位=低)

基址字节

数据字节到基址停止信号

写入四个连续的控制寄存器启动信号

从地址字节(R/W位=低)

基址字节

数据字节到基址

数据字节到(基址+1)

数据字节到(基址+2)

数据字节到(基址+3)停止信号

从一个控制寄存器读取启动信号

从地址字节(R/W位=低)

基址字节

启动信号

从地址字节(R/W位=高)

来自基地址停止信号的数据字节

从四个连续控制寄存器读取

启动信号

从地址字节(R/W位=低)

基址字节

启动信号

从地址字节(R/W位=高)

来自基地址的数据字节

数据字节从(基址+1)

数据字节从(基址+2)

数据字节从(基址+3)

停车信号

同步处理

同步切片器

同步切片器的目的是从绿色图形通道中提取同步信号。同步信号并不存在于所有图形系统中,只有那些同步为绿色的图形系统。同步信号在两步过程中从绿色通道中提取。首先,SOG输入被钳制到其负峰值(通常比黑电平低0.3v)。接下来,信号进入具有可变触发电平的比较器,名义上比钳位电平高0.15v。“切片”同步通常是包含Hsync和Vsync的复合同步信号。

同步分离器

同步分离器从复合同步信号中提取Vsync信号。它通过一个低通滤波器或积分器样的操作来实现。它的工作原理是Vsync信号比Hsync信号保持活动的时间长得多。因此,它拒绝任何小于阈值的信号,阈值介于Hsync脉冲宽度和Vsync脉冲宽度之间。

AD9888上的同步分离器是一个8位数字计数器,具有5 MHz时钟。它独立于复合同步信号的极性工作。(极性在芯片的其他地方决定)基本思想是当存在Hsync脉冲时计数器计数。但由于Hsync脉冲的宽度相对较短,计数器在脉冲结束前仅达到N的值。然后开始倒计时,最终在下一个Hsync脉冲到达之前达到0。对于不同的视频模式,N的具体值会有所不同,但始终小于255。例如,对于1μs宽的Hsync,计数器将仅达到5(1μs/200 ns=5)。现在,当Vsync出现在复合同步上时,计数器也会计数。但是,由于Vsync信号更长,它将计数到更高的数字M。对于大多数视频模式,M将至少为255。因此,当计数器计数大于N时,可以通过检测复合同步信号来检测Vsync。触发检测(T)的特定计数可以通过串行寄存器(0FH)编程。

一旦检测到Vsync,就有一个类似的过程来检测它何时变为非活动状态。检测时,计数器首先重置为0,然后在Vsync消失时开始计数。与前一种情况类似,当计数器达到阈值计数(T)时,它将检测是否缺少Vsync。这样,它将拒绝噪声和/或锯齿脉冲。一旦检测到Vsync不存在,计数器将重置为0并再次开始循环。

PCB布局建议

AD9888是一种高精度、高速模拟设备为了获得最大性能的部分,重要的是有一个精心布置的董事会。以下是使用AD9888设计电路板的指南。

模拟接口输入

在图形输入端使用以下布局技术是非常重要的。

最小化进入图形输入的跟踪长度。这是通过将AD9888尽可能靠近图形(VGA)接口来实现的。长输入跟踪长度是不可取的,因为它们会从电路板和其他外部源接收更多的噪声。

将75Ω终端电阻器(见图1)尽可能靠近AD9888芯片。终端电阻和AD9888输入端之间的任何额外记录道长度都会增加反射的幅度,这将损坏图形信号。

使用75Ω匹配的阻抗记录道。75Ω以外的跟踪阻抗也会增加反射的机会。

AD9888具有很高的输入带宽(500兆赫)。虽然这对于获取具有快速边缘的高分辨率PC图形信号是可取的,但这意味着它还将捕获存在的任何高频噪声。因此,减少耦合到输入端的噪声是很重要的。避免在模拟输入附近运行任何数字跟踪。

AD9888可以在非常宽的频率范围(10兆赫到205兆赫)上数字化图形信号。通常,在一个频率有益的特性在另一个频率有害。模拟带宽就是这样一个特点。对于UXGA分辨率(高达205mhz),由于快速的输入信号转换速率,需要非常高的模拟带宽。对于VGA和较低分辨率(低至12.5 MHz),非常高的带宽是不可取的,因为它允许过多的噪声通过。为了适应这些变化的需要,AD9888包括可变模拟带宽控制。提供四种设置(75兆赫、150兆赫、300兆赫和500兆赫),允许模拟带宽与输入图形信号的分辨率匹配。

电源旁路

建议使用0.1μF电容器绕过每个电源引脚。例外情况是两个或多个电源插脚彼此相邻。对于这些电源/接地分组,只需要一个旁路电容器。其基本思想是在每个电源引脚的0.5厘米范围内有一个旁路电容器。另外,避免将电容器放置在AD9888的PC板的另一侧,因为它会在路径中插入电阻过孔。

旁路电容器应位于电源平面和电源引脚之间。电流应该从电源平面流出来=>电容器=>电源引脚。不要在电容器和电源引脚之间进行电源连接。把通孔放在电容器垫下面,一直到电源平面,通常是最好的方法。

特别重要的是保持低噪声和良好的稳定性的PVD(时钟发生器电源)。PVD的突变可以导致采样时钟相位和频率的类似突变。这可以通过仔细注意调节、过滤和旁路来避免。最好为每个模拟电路组(VD和PVD)提供单独的稳压电源。

一些图形控制器在活动(在活动画面时间)和空闲(在水平和垂直同步期间)时使用的功率水平相差很大。这会导致提供给模拟电源调节器的电压发生可测量的变化,而模拟电源调节器反过来又会产生被调节模拟电源电压的变化。这可以通过调节来自不同的、更清洁的电源(例如,来自12V电源)的模拟电源或至少PVD来减轻。

还建议对整个电路板使用单个接地平面。经验一再表明,单地面的噪声性能相同或更好。使用多个接地平面可能有害,因为每个单独的接地平面较小,并且可能导致长接地回路。

在某些情况下,使用单独的地平面是不可避免的。对于这些情况,建议在AD9888下至少放置一个单一的接地平面。分割的位置应该在数字输出的接收器处。在这种情况下,更重要的是要明智地放置元件,因为电流回路会更长(电流的路径电阻最小)。电流回路的一个示例:电源平面=>AD9888=>数字输出轨迹=>数字数据接收器=>数字接地平面=>模拟接地平面。

锁相环

将PLL环路滤波器组件尽可能靠近滤波器引脚。

不要在这些部件附近放置任何数字或其他高频记录道。

使用数据表中建议的公差小于等于10%的值。

输出(数据和时钟)

尽量减少数字输出必须驱动的跟踪长度。更长的记录道具有更高的电容,需要更多的电流,并产生更多的内部数字噪声。较短的轨迹减少了反射的可能性。

在AD9888中增加一个22Ω到100Ω的串联电阻可以抑制反射、降低EMI和减小电流尖峰。但是,如果在PCB上使用50Ω记录道,则数据输出不应需要这些电阻器。

数据包输出上的22Ω电阻应提供良好的阻抗匹配,以减少反射。如果EMI或电流尖峰是一个问题,我们建议通过调整寄存器14H使用较低的驱动强度设置。如果使用串联电阻,将它们放置在尽可能靠近AD9888引脚的位置(但避免在输出轨迹中添加过孔或额外长度,以使电阻更接近)。

如果可能,将每个数字输出驱动的电容限制在10 pF以下。这可以很容易地通过保持轨迹短和只将输出连接到一个设备来实现。用过大电容加载输出将增加AD9888内部的电流瞬变,从而在其电源上产生更多的数字噪声。

数字输入

AD9888上的数字输入设计用于3.3V信号,但允许5.0V信号。因此,如果使用5.0v逻辑,则不需要添加额外的组件。

任何进入Hsync输入跟踪的噪声都会给系统增加抖动。因此,尽量减少记录道长度,不要在其附近运行任何数字或其他高频记录道。

电压基准

带0.1μF电容器的旁路。将其尽可能靠近AD9888销。使接地连接尽可能短。