10064点击型号即可查看芯片规格书

FM22LD16点击型号即可查看芯片规格书

特征

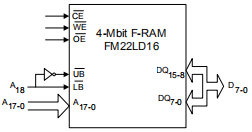

逻辑上4-Mbit铁电随机存取存储器(F-RAM)组织为256K×1610064;使用UB和LB配置为512K×8❐高耐久性100万亿(1014)读/写❐151年数据保留期(见数据保留和耐久表)NoDelay8482;写入页面模式运行至25 ns循环时间先进的高可靠性铁电工艺SRAM兼容行业标准256K×16 SRAM引脚55 ns接入时间,110 ns周期时间先进功能软件可编程块写保护优于电池支持的SRAM模块无电池问题单片可靠性真正的表面贴装解决方案,无返工步骤适用于潮湿、冲击和振动低功耗有功电流8毫安(典型值)备用电流90μA(典型值)低压运行:VDD=2.7 V至3.6 V工业温度:–40℃至+85℃??48球细间距球栅阵列(FBGA)封装符合有害物质限制(RoHS)

功能概述

FM22LD16是一个256K×16的非易失性存储器,它可以读取写的和标准的SRAM类似。铁电随机数存取存储器或F-RAM是非易失性的,这意味着数据在断电后保留。它为151年来,在消除可靠性问题的同时,功能缺陷和系统设计复杂性电池支持的SRAM(BBRAM)。快速写入计时和高写持久性使F-RAM优于其他类型的记忆。FM22LD16的操作与其他RAM设备类似因此,它可以作为系统中的标准SRAM。读写周期可以是由CE触发或通过更改地址触发。F-RAM由于其独特的铁电存储器,存储器是非易失性的过程。这些特性使FM22LD16成为需要频繁或快速的非易失性存储器应用写。FM22LD16包括一个低电压监视器当VDD低于VDD最小值时访问内存阵列。内存受到保护,以防止无意访问和数据在这种情况下腐败。该设备还具有软件控制写保护。内存数组是分为8个均匀的块,每个块可以单独写保护。该设备提供48球FBGA封装。设备规格保证在工业温度以上温度范围-40°C至+85°C。

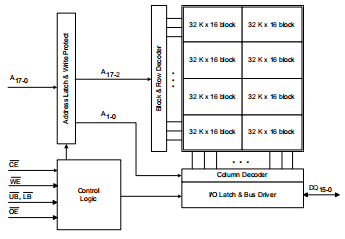

设备操作FM22LD16逻辑上是一个字宽的F-RAM存储器组织为262144×16,并使用工业标准并行接口。写入部件的所有数据是立即不易挥发。设备提供页面模式操作,提供高速访问页(行)中的地址。访问其他页面要求CE转换低位或高位地址(A17-A2)变更。见第17页的功能真值表完整描述读写模式。存储器操作用户访问262144个内存位置,每个位置有16个数据位通过一个并行接口。F-RAM阵列组织为八个街区,每个街区有8192行。每行有四列允许在页面模式下快速访问的位置。当初始地址被CE的下降沿锁住时,无需访问后续列位置切换CE。当CE被解除高压时,预充电手术开始。在立即进入。每次写入时必须切换WE pin操作。写入数据存储在非易失性存储器中立即数组,这是F-RAM特有的一个特性,称为诺德雷写道。读取操作读取操作从CE的下降沿开始。坠落CE的边缘导致地址被锁存并启动内存读取周期,如果我们是高。数据可用于到达访问时间后的总线。当地址被锁定时访问完成,一个新的随机位置访问(不同的行)可能在CE仍然较低时开始。最小值随机地址的循环时间是tRC。注意,与sram不同,FM22LD16的CE启动访问时间比地址访问时间。当运行经验和至少一个运行经验时,FM22LD16将驱动数据总线字节的启用(UB,LB)被断言为低。上层数据当UB低时字节被驱动,低数据字节被驱动当磅低时。如果在内存访问时间之后断言OE如果满足,将使用有效数据驱动数据总线。如果运行经验是在完成内存访问之前断言,数据总线将在有效数据可用之前不驱动此功能将最小化通过消除由驱动到总线的数据无效。当运行经验被解除评估时高,数据总线将保持HI-Z状态。

写操作在FM22LD16中,写入与读取的间隔相同。这个FM22LD16同时支持CE和WE控制的写入周期。在两种情况下,地址A17–A2都锁定在总工程师。在CE控制的写操作中,WE信号在开始内存循环。也就是说,当CE下降时,我们是低的。在这种情况下,设备以写的形式开始内存循环。这个无论处于何种状态,FM22LD16都不会驱动数据总线只要我们是低的当CE为去资产高。在我们控制的写入中,内存周期从CE的下降边缘开始。我们的信号有时会掉下来稍后。因此,存储周期以读开始。数据如果运行效率低,将驱动总线;但是,当我们被断言为低。我们控制了写计时。对数组的写访问从启动内存循环。写入访问在我们或CE的上升沿,以先到者为准。有效的笔迹操作要求用户满足访问时间规范在我们或行政长官离开之前。数据设置时间指示在写访问(WE或CE的上升沿)。与其他非易失性存储器技术不同,它没有写操作F-RAM延迟。

因为底层内存相同,用户体验不到在公共汽车上耽搁。整个内存操作发生在单总线循环。数据轮询,一种用于eeprom的技术不需要确定写入是否完成。页面模式操作F-RAM阵列被组织为八个块,每个块有8192个排。每行有四个列地址位置。地址输入A1–A0定义要访问的列地址。一个访问可以从任何列地址和其他列开始无需切换CE引脚即可访问位置。对于快速访问读取,在第一个数据字节被驱动到总线之后,列地址输入A1–A0可以更改为新的价值。一个新的数据字节在不迟于tAAP,不到初始读取访问时间的一半。快速的访问写,第一个写脉冲定义第一个写访问。当CE较低时,随后的写入脉冲和新的列地址提供页模式写入访问。预充电操作预充电操作是一种内部条件,其中内存状态已准备好进行新的访问。预充电是用户通过驱动CE信号高启动。它必须留下至少在最短预充电时间内为高,tPC。预充电也可以通过改变上面的地址来激活,A17–A2。当前行在访问新的划船。设备自动检测一个高阶地址变更,开始预充电操作。新地址已锁定,新的读取数据在tAA地址内有效访问时间;。类似的序列发生对于写入周期,速度随机地址可以分别是tRC和tWC。

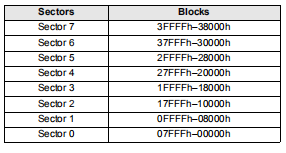

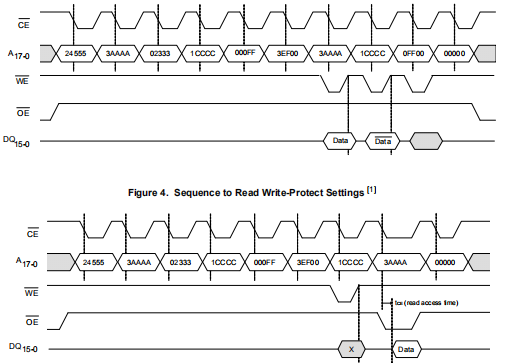

软件写保护256K×16地址空间分为8个扇区(块)每个32K×16。每个部门可以单独软件写保护和设置是非易失性的。一个唯一地址和命令序列调用写入保护模式。要修改写保护,系统主机必须发出六个read命令、三个写入命令和一个最终读取命令。FM22LD16读取地址的特定序列必须提供给访问写保护模式。在读取地址之后序列,主机必须写入一个数据字节,指定各部门所需的保护状态。为了证实这一点然后系统必须写入保护字节的补码紧跟在保护字节之后。发生的任何错误包括按错误顺序读取地址,发出第七个读取地址,或未能补充保护值将保持写保护不变。写保护状态机监视所有地址,获取在这个特定的读/写序列发生之前没有动作。在地址序列,每次读取都将作为有效操作发生相应地址的数据将被驱动到数据总线。任何出现顺序错误的地址都会导致软件保护状态机重新启动。地址之后序列已完成,下一个操作必须是写入循环。较低的数据字节包含写保护设置。这个值不会写入内存数组,因此地址是别在意。而是在下一个周期之前举行必须是对保护设置的数据补充。如果补码正确,写保护设置将为调整。否则,进程中止,地址顺序重新开始。在正确的6之后写入的数据值地址将不会输入内存。保护数据字节由8位组成,每个位与一个扇区的写保护状态。数据字节必须是驱动到数据总线的低8位,DQ7–DQ0。设置“1”写入的位保护相应的扇区;“0”启用为那个部门写作。下表显示了写保护具有控制写保护的相应位的扇区设置。

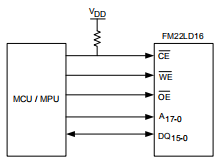

SRAM插入替换FM22LD16的设计是作为标准异步sram。设备不需要CE为每个新地址切换。CE可能无限期地保持在低位。当CE低时,设备自动检测地址更改并开始新的访问。此功能允许CE像你用SRAM那样接地。它还允许页面模式运行速度高达40兆赫。图显示了CE上的一个上拉电阻器,它将保持引脚高功率循环期间,假设MCU/MPU引脚在复位条件下三态。上拉电阻值应选择确保CE管脚轨迹VDD高足够大的值,因此当CE低时所消耗的电流一个问题。当CE低且VDD=3.3伏请注意,如果CE与地面相连,用户必须确保我们没有在上电或断电事件中处于低位。如果CE和我们都是低功率循环期间,数据将损坏。图6显示我们身上有一个上拉电阻器,在功率循环,假设MCU/MPU引脚在复位条件。上拉电阻值应选择为确保WE pin tracks VDD值足够高,以便当我们很低的时候,电流消耗不是问题。10-k当我们处于低电压且VDD=3.3V时,电阻消耗330微安。注意,如果CE与地面相连,用户将放弃执行软件写入保护序列。对于需要最低功耗的应用程序CE信号应仅在内存访问期间激活(低)。当CE较低时,即使地址和控制信号是静态的。当CE值高时设备不超过最大待机电流。CE在每个地址访问上切换到低位是完美的在FM22LD16中可接受。UB和LB字节选择管脚对读和写都有效循环。它们可用于将设备连接为512K×8内存。上下数据字节可以绑定与字节选择一起控制。单个字节启用或下一个更高地址行A18可用从系统处理器。

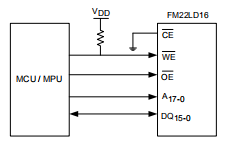

请注意,如果CE与地面相连,用户必须确保我们没有在上电或断电事件中处于低位。如果CE和我们都是低功率循环期间,数据将损坏。图显示我们身上有一个上拉电阻器,在功率循环,假设MCU/MPU引脚在复位条件。上拉电阻值应选择为确保WE pin tracks VDD值足够高,以便当我们很低的时候,电流消耗不是问题。10-k当我们处于低电压且VDD=3.3V时,电阻消耗330微安。

注意,如果CE与地面相连,用户将放弃执行软件写入保护序列。对于需要最低功耗的应用程序CE信号应仅在内存访问期间激活(低)。当CE较低时,即使地址和控制信号是静态的。当CE值高时设备不超过最大待机电流。CE在每个地址访问上切换到低位是完美的在FM22LD16中可接受。UB和LB字节选择管脚对读和写都有效循环。它们可用于将设备连接为512K×8内存。上下数据字节可以绑定与字节选择一起控制。单个字节启用或下一个更高地址行A18可用从系统处理器。