WM8766点击型号即可查看芯片规格书

说明

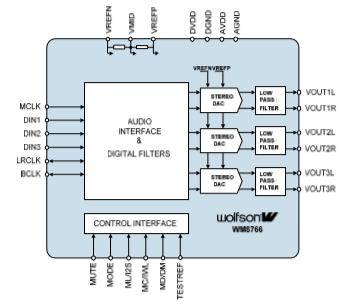

WM8766是一款多声道音频DAC,非常适合家庭高保真、汽车和其他视听设备的DVD和环绕声处理应用。

三个立体声24位多位sigma-delta dac与过采样数字插值滤波器一起使用。支持16-32位的数字音频输入字长和8kHz至192kHz的采样率。每个DAC通道都有独立的数字音量和静音控制。音频数据接口支持I2S、左对齐、右对齐和数字音频格式。设备通过3线串行接口或直接使用硬件接口进行控制。这些接口提供对功能的访问,包括通道选择、音量控制、静音、去强调和电源管理设施。该设备提供28针SSOP。

特点,6通道DAC,音频性能–-103dB SNR('A'加权@48kHz)DAC,DAC采样频率:8kHz–192kHz,3线SPI串行或硬件控制接口,可编程音频数据接口模式–-I 2S,左侧,右对齐或数字信号处理器-16/20/24/32位字长,三个带独立数字音量控制的独立立体声DAC输出,主音频或从音频数据接口,2.7V至5.5V模拟、2.7V至3.6V数字电源操作,28针SSOP封装应用程序,DVD播放器,环绕声AV处理器和高保真系统,汽车音响

绝对最大额定值仅为应力等级。设备的永久性损坏可能是由于在这些极限或超过这些极限的条件下连续运行造成的。在规定的试验条件下,给出了电气特性下的设备功能操作极限和保证性能规范。

静电放电敏感装置。该器件采用CMOS工艺制造。因此,它一般容易受到过大静态电压的损坏。在搬运和储存本设备时,必须采取适当的ESD预防措施。

Wolfson根据IPC/JEDEC J-STD-020B测试其包装类型的水分敏感性,以确定表面安装组装前的可接受储存条件这些级别是:

MSL1=在<30°C/85%相对湿度下的无限地板寿命。通常不储存在防潮袋中。MSL2=在<30°C/60%相对湿度下袋外贮存1年。防潮袋提供。MSL3=在<30°C/60%相对湿度下,袋外贮存168小时。防潮袋提供。

注:1。1kHz满标度输入的输出电平与数字输入中所有零点的输出电平之比,测量“A”加权。2。所有的性能测量都是用20kHz低通滤波器完成的,如果注意到,则使用A-权重滤波器。如果不使用这种滤波器,将导致比电气特性中的高THD+N、低SNR和动态范围读数。低通滤波器消除带外噪声;虽然听不见,但可能会影响动态规格值。三。VMID与10uF和0.1uF电容器分离(较小的值可能导致性能降低)。

术语1。信噪比(dB)-信噪比是测量满标度输出和无信号输出之间的电平差。(不使用自动调零或自动静音功能来实现这些结果)。2。动态范围(dB)-DNR是测量信号最高和最低部分之间的差异。通常在低于满标度60dB时测量THD+N。然后,通过向测量信号添加60dB对其进行校正。(例如THD+N@-60dB=-32dB,DR=92dB)。三。THD+N(dB)-THD+N是(噪声+失真)/信号的rms值的比率。四。阻带衰减(dB)-是频谱衰减的程度(音频频带外)。5个。信道分离(dB)-也称为串扰。这是测量一个通道与另一个通道隔离的量。通常通过向一个通道发送满标度信号并测量另一个通道来测量。6。通带纹波-通带区域频率响应的任何变化。

设备描述

导言

WM8766是一个完整的6通道DAC,包括数字插值和抽取滤波器和开关电容多位sigma-delta DAC,每个通道上都有数字音量控制和输出平滑滤波器。

该装置在单个封装中实现为3个独立的立体声dac,并由单个接口控制。

每个立体声DAC都有自己的数据输入DIN1/2/3。DAC字时钟LRCLK、DAC位时钟BCLK和DAC主时钟MCLK在它们之间共享。

音频接口可以配置为在主模式或从模式下工作。在从机模式下,LRCLK和BCLK都是输入。在主模式下,LRCLK和BCLK都是输出。

每个DAC都有自己的数字音量控制,可以以0.5dB的步长进行调节。数字音量控制可以独立操作。此外,为数字音量控制的每个DAC提供零交叉检测电路。数字音量控制在更新音量之前检测到通过零点的转换。随着增益值的变化,这会将可听到的咔哒声和“拉链”噪声降至最低。

通过3线串行或引脚可编程控制接口控制设备的内部功能。软件控制接口可以与音频数据接口异步,因为控制数据将在内部与音频处理重新同步。

为DAC提供使用128fs、192fs、256fs、384fs、512fs或768fs的主时钟的操作。在从模式中,时钟速率之间的选择是自动控制的。在主模式下,采样率由控制位数据率设置。如果输入了适当的主时钟,DAC允许音频采样率(fs)从小于8ks/s到192ks/s。音频数据接口支持右、左、I2S接口格式,并具有高度灵活的DSP串行端口接口。

音频数据采样率在典型的数字音频系统中,只有一个中央时钟源产生一个参考时钟,所有音频数据处理都与之同步。这个时钟通常被称为音频系统的主时钟。外部主系统时钟可通过DAC MCLK输入引脚直接应用,无需软件配置。

WM8766的DAC主时钟支持从128fs到768fs的音频采样率,其中fs是音频采样频率(LRCLK),通常为32kHz、44.1kHz、48kHz、96kHz或192kHz。主时钟用于操作数字滤波器和噪声整形电路。

在从模式下,WM8766有一个主时钟检测电路,自动确定系统时钟频率和采样率之间的关系(在正负32个主时钟范围内)。如果存在大于32个时钟错误,则接口默认为768fs模式。WM8766能够容忍主时钟上的相位变化或抖动。表5显示了WM8766的典型主时钟频率输入。

WM8766的信号处理通常以128fs的过采样率工作。例外情况是,当过采样率为64fs时,对于128/192fs系统时钟的操作,例如对于192kHz操作。

音频接口格式音频数据通过数字音频接口应用于内部DAC滤波器。支持5种流行的接口格式:

所有5种格式都先发送MSB,并支持16、20、24和32位的字长,但不支持32位右对齐模式。在左对齐、右对齐和I2S模式下,数字音频接口通过DIN1/2/3输入接收DAC数据。每个立体声声道的音频数据与LRCLK进行时间复用,LRCLK指示左声道或右声道是否存在。LRCLK还用作指示数据字的开始或结束的定时参考。在左对齐、右对齐和I2S模式下,每个LRCLK周期的最小bclk数是所选字长的2倍。LRCLK对于最小字长BCLKs必须为高,对于最小字长BCLKs必须为低。只要满足上述要求,LRCLK上的任何标记空间比都是可接受的。

在DSP早期或DSP晚期模式下,所有6个DAC通道都被时间复用到DIN1上。LRCLK用作帧同步信号来标识第一个字的MSB。每个LRCLK周期的最小bclk数是所选字长的6倍。只要上升沿位置正确,LRCLK上的任何标记空间比都是可以接受的。

左对齐模式

在左对齐模式下,在LRCLK转换之后,WM8766在BCLK的第一个上升沿上对DIN1/2/3的MSB进行采样。左采样时LRCLK为高,右采样时LRCLK为低

建议的模拟低通后DAC滤波器-建议对每个DAC通道的输出应用低通滤波器,用于高保真应用。通常,二阶滤波器是合适的,并且提供足够的高频分量衰减(在WM8766中使用的独特的低阶、高比特计数的多比特sigma-delta DAC结构比普通sigma-delta DAC产生的高频输出噪声小得多)。该滤波器通常还用于提供所需的2x增益,以提供大多数用户设备的标准2Vrms输出电平。

图28显示了一个合适的后DAC滤波器电路,增益为2倍。也可以使用替代的反向滤波器结构,并取得良好的效果。