216点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

特点

8通道可编程差分或单端多路复用器;可编程采集时间和用户可控吞吐量;可编程数据总线宽度(8/13位);内置采样和保持;可编程自动校准和自动调零周期;低功耗待机模式;没有丢失的代码。

应用

医疗器械;过程控制系统;试验设备;数据记录;惯性制导。

主要规格

(fclk=12兆赫);分辨率:12位+符号;13位转换时间:3.6μs,最大;13位吞吐率:216 ksamples/s,min;积分线性误差(Ile):±1 LSB,最大;单电源:+5 V±10%;车辆识别号范围:接地至VA+8226;功耗–正常运行:最大34兆瓦–待机模式:最大75μW。

说明

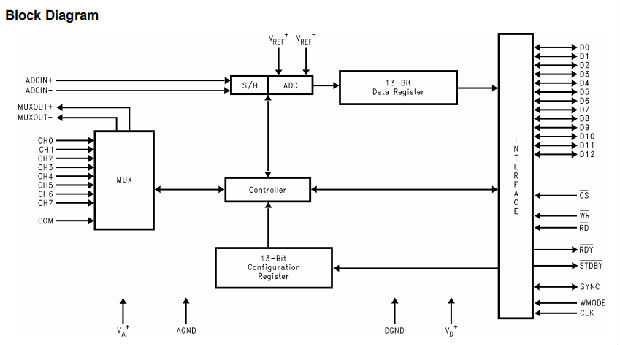

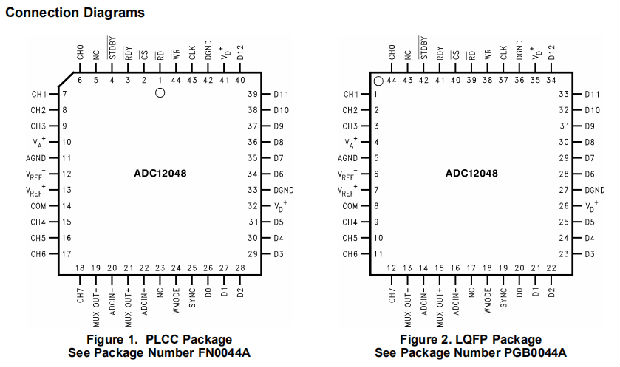

在一个5V电源上运行,ADC12048是一个12位+符号,并行I/O,自-校准、采样模数转换器(ADC)八输入全差分模拟多路复用器。最大采样速率为216 kHz。应要求,ADC进行自校准调整线性、零和满标度误差的过程。ADC12048的8通道多路复用器是软件可编程以多种组合方式操作单端差分或伪差分模式。全差分mux和12位+符号ADC允许两者之间的差异信号要数字化。

ADC12048可以配置为与许多流行的微处理器/微控制器和DSP包括TL的HPC系列,Intel386和8051,tms320c25、摩托罗拉mc68hc11/16、日立64180以及模拟设备ADSP21XX。

功能描述

ADC12048通过支持8位或16位数据总线的数字接口编程。数字接口包括一个13位数据输入/输出总线(D12–d0)、数字控制信号和两个内部寄存器:一个只写13位配置寄存器和一个只读13位数据寄存器。

配置寄存器编程ADC12048的功能。配置寄存器的13位被分为7个字段。每个字段控制ADC12048的特定功能:多路复用器的信道选择、采集时间、同步或异步转换、操作模式和数据总线大小。

特点和操作模式

可选总线宽度

ADC12048可编程为与8位或16位数据总线接口。中的BW位(B12)配置寄存器控制总线大小。如果bw位被清除,则总线宽度设置为8位(d7–d0处于活动状态,d12–d8处于三态);如果bw位被设置,则总线宽度设置为13位(d12–d0处于活动状态)。通电时,总线宽度默认为8位,ADC12048的任何初始编程都应考虑到这一点。

在8位模式下,配置寄存器是字节可访问的。配置寄存器下字节中的hb位用于访问上字节。如果hb位设置为向低字节写入,则写入adc的下一个字节将放在配置寄存器的高字节中。数据写入配置寄存器的上字节后,hb位将自动清除,导致写入adc的下一个字节转到配置寄存器的下一个字节。在8位模式下读取ADC时,第一个读取周期将数据寄存器的下一个字节放在数据总线上,然后在下一个读取周期中放上一个字节。

在13位模式下,HB位是一个不需要关心的条件,数据寄存器和配置寄存器的所有位都可以通过一个读或写周期访问。由于ADC12048的总线宽度在通电后默认为8位,因此当需要13位模式时的第一个操作必须设置为总线宽度为13位。

W模式

wmode管脚用于确定写入脉冲的有效边缘。该引脚的状态决定wr信号的哪个边缘将导致adc锁定数据。这取决于处理器。如果处理器在wr信号下降沿期间总线上有有效数据,则wmode引脚必须绑定到vd+。这将导致adc在wr信号的下降沿上锁定数据。如果数据在wr信号的上升沿上有效,则wmode引脚必须绑定到dgnd,从而使adc锁定wr信号上升沿上的数据。

输入多路复用器

ADC12048具有八通道输入多路复用器,其COM输入可用于单端、伪差分或全差分模式。配置寄存器中的mux选择位(b3–b0)确定在muxout+和muxout多路复用器输出管脚处出现的通道。带有固定增益放大器、可编程增益放大器、滤波器和其他处理电路的模拟信号调节可在应用于ADC输入之前用于多路复用器的输出。ADCIN+和ADCIN-是ADC12048的模数转换器(ADC)的全差分非逆变(正)和逆变(负)输入。如果多路复用器的信号输出不需要外部信号调节,则muxout+应连接到adcin+,muxout-应连接到adcin-。

模拟输入多路复用器可以设置为在八种差分或八种单端(COM输入作为零参考)模式中的一种工作。在差分模式下,模拟输入按如下方式配对:ch0与ch1,ch2与ch3,ch4与ch5,ch6与ch7。输入通道对可以按任意顺序连接到muxout+和muxout-管脚。在单端模式下,可以将一个输入通道ch0到ch7分配给muxout+,而muxout-始终分配给com输入。

待机模式

ADC12048具有低功耗模式(75μW@5V)。当在配置寄存器的命令字段中写入备用命令时,进入此模式。stdby输出引脚上出现逻辑低表示ADC12048处于待机模式。写入配置寄存器的备用命令以外的任何命令都将使ADC12048脱离备用模式。一旦ADC12048被请求退出待机模式,STDBY引脚将立即切换到逻辑“1”。当ADC实际脱离待机模式并准备好正常工作时,RDY引脚将被断言为低。ADC12048在硬件通电后默认为待机模式。这可以通过检查stdby引脚的逻辑低状态来验证。

同步/异步模式

ADC12048可编程为以同步(sync-in)或异步(sync-out)模式工作。要进入同步模式,必须设置配置寄存器中的同步位。硬件通电后,ADC12048处于同步模式。在此模式下,同步管脚被编程为输入,转换被同步到应用于同步管脚的信号上升沿。在同步模式下,采集时间也可以由同步信号控制。参见图14和图18。当同步位被清除时,ADC处于异步模式,同步管脚被编程为输出。在异步模式下,同步管脚处的信号指示转换器的状态。当转换器执行转换时,此引脚高。参见图17和图15。

可选择的采集时间

ADC120 48的内部采样/保持电路通过将输入连接到内部采样电容器(大约70 pF)来采样输入电压,该有效电阻等于多路复用器“on”电阻(300Ωmax)加上模拟开关在采样/保持电路(2500Ω典型)的输入端上的“on”电阻。以及电源的有效输出电阻。为了使转换结果准确,采样电容器连接到电源的周期(“采集时间”)必须足够长,以便将电容器充电到输入电压lsb的一小部分内。当外部电源电阻小于1kΩ且任何有源或无功电源电路在小于500ns的时间内沉降到12位时,750ns的采集时间就足够了。当源电阻或源稳定时间超过这些限制时,还必须增加采集时间以保持精度。

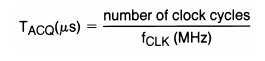

在异步(同步)模式下,采集时间由内部计数器控制。最小捕获周期为9个时钟周期,对应于时钟频率为12mhz时750ns的标称值。配置寄存器的位b4和b5用于从四个可能值(9、15、47或79个时钟周期)中选择采集时间。由于异步模式下的采集时间基于时钟周期的计数,因此它也与时钟频率成反比:

注意,实际采集时间将比tacq长,因为采集在多路复用器信道改变时或rdy变低时开始,如果多路复用器信道没有改变。执行读取后,RDY变高,启动TACQ计数器(见图13)。

在同步(sync-in)模式下,位b4和b5被忽略,采集时间取决于在sync pin上应用的同步信号。如果在转换开始时选择了新的mux信道,则采集周期从锁定在新mux信道中的wr信号的激活边缘开始。如果没有选择新的mux信道,则采集周期从rdy的下降沿开始,该下降沿发生在上一个转换结束时(或在自动调零或自动校准过程结束时)。当同步变高时,采集周期结束。

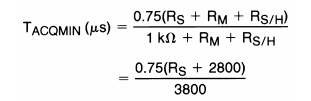

要估计源电阻大于1kΩ时精确转换所需的采集时间,请使用以下表达式:

其中:Rs是源电阻;rm是mux“开”电阻;RS/H是样品/保持“开”电阻。

如果源的沉降时间大于500ns,则对于“良好的”平稳沉降特性,采集时间应比沉降时间长约300ns。

全校准周期

整个校准周期补偿ADC的线性和偏移误差。只有在进行完全校准后,才能指定转换器的直流规格。通过向ADC12048写入fulcal命令来启动整个校准周期。在完全校准期间,测量八次偏移误差,取平均值,并创建校正系数。偏移校正系数存储在内部偏移校正寄存器中。

通过校正内部dac的电容失配来实现整体线性校正。将每个电容器与所有剩余的较小值电容器进行8次比较。对误差进行平均,并生成校正系数。

一旦转换器被校准,算术逻辑单元(alu)使用偏移和线性校正系数将转换偏移和线性误差减小到指定的范围内。

自动归零循环

在自动调零周期中,仅测量一次偏移量,并创建校正系数并将其存储在内部偏移寄存器中。通过向ADC12048写入自动归零命令来启动自动归零循环。

数字接口

数字控制信号为cs、rd、wr、rdy和stdby。特定的时序关系与这些信号的相互作用有关。有关详细的正时技术规格,请参阅数字正时图。活动的低rdy信号指示某个事件何时开始和结束。建议仅在RDY信号低时访问ADC12048。正是在这种状态下,ADC12048准备接受新命令。这将最小化开关数据总线对adc产生的噪声的影响。唯一的例外是当ADC12048处于待机模式时,此时RDY为高,而STDBY信号为低。ADC12048在通电或发出待机命令时处于待机模式。ful cal、auto zero、reset或start命令将使ADC12048脱离待机模式。这可以通过监视rdy和stdby信号的状态来观察。当ADC12048离开待机模式时,RDY信号将变低,而STDBY信号将变高。

以下描述了8位和13位模式下每个编程事件的数字控制信号的状态。在发出每个命令之前,RDY应为低,除非设备处于待机模式。

ful-cal或auto-zero命令

8位模式:对ADC12048的第一次写入将把数据放在配置寄存器的低字节中。该字节必须设置hb位(b7),以便在下一个写入周期中访问配置寄存器的上字节。在第二个写入周期中,必须发出ful cal或auto zero命令。wr引脚上第二个写入脉冲的边缘将迫使rdy信号升高。此时,转换器开始执行完全校准或自动调零循环。当完成完全校准或自动调零循环时,RDY信号将自动变低。

13位模式:在单个写入周期中,必须将ful cal或auto zero命令写入ADC12048。wr信号的边缘将迫使rdy升高。此时,转换器开始执行完全校准或自动调零循环。当完成完全校准或自动调零循环时,RDY信号将自动变低。

启动转换:start命令

为了完整地描述与start命令相关的事件,必须同时考虑sync-out和sync in模式。

同步/异步

8位模式:写入ADC12048的第一个字节应设置MUX通道、采集时间和HB位。第二个字节应该清除sync位,写入start命令并清除bw位。为了启动转换,必须从ADC12048执行两次读取。第二个读取脉冲的上升沿将强制RDY引脚升高,并开始由配置寄存器的位B5和B4选择的编程采集时间。同步管脚将变高,表示采集周期结束后已开始转换序列。转换完成后,RDY和同步信号将降低。此时,新的信息,例如新的mux信道、采集时间和操作命令,可以写入配置寄存器,也可以保持不变。假设start命令在配置寄存器中,则可以读取先前的转换。第一次读取将数据寄存器中包含的转换结果的低位字节放在数据总线上。第二次读取将把转换结果的高位字节存储在数据总线上的数据寄存器中。第二个读取脉冲的上升沿将开始另一个转换序列,并适当地提高rdy和同步信号。

13位模式:应设置多路复用器信道和采集时间,清除同步位,并在向ADC12048单次写入时发出启动命令。为了启动转换,必须从ADC12048执行一次读取。读取信号的上升沿将迫使rdy信号升高,并开始由配置寄存器的位b5和b4选择的编程采集时间。同步管脚将变高,表示采集周期结束后已开始转换序列。转换完成后,RDY和同步信号将降低。此时,新的信息,例如新的mux信道、采集时间和操作命令,可以写入配置寄存器,也可以保持不变。使用配置寄存器中的START命令,从ADC12048读取的数据将把存储在数据总线上的数据寄存器中的整个13位转换结果放置在数据总线上。读取脉冲的上升沿将立即强制RDY输出高。然后,随着配置寄存器位b5和b4中编程采集时间的流逝,同步将变高。

同步/同步

对于sync-in情况,假设在adc12048的sync管脚处应用以期望采样率的一系列sync脉冲。

8位模式:写入ADC12048的第一个字节应设置MUX通道和HB位。第二个字节应该设置sync位,编写start命令并清除bw位。

同步管脚上的上升沿或从ADC12048连续读取两次的第二上升沿将强制RDY信号高。建议使用从ADC12048(而不是同步信号的上升沿)读取的动作来提升RDY信号。在同步模式下,只有同步信号的上升沿将开始转换周期。同步的上升沿也结束了采集周期。采集周期开始于包含mux信道信息的写入周期之后。选定的mux信道在wr信号的上升沿之后采样,直到同步脉冲的上升沿,此时信号将被保持并开始转换。转换完成后,RDY信号将变低。如果需要,此时可以将新的mux信道和/或操作命令写入配置寄存器。从ADC12048的数据寄存器中检索整个13位转换结果需要两个连续的读取周期。第一次读取将把包含在数据总线上的数据寄存器中的转换结果的下字节放在数据总线上。第二次读取将把转换结果的高位字节存储在数据总线上的数据寄存器中。使用配置寄存器中的START命令,第二个读取脉冲的上升沿将使RDY信号升高,并在同步管脚的上升沿之后开始转换循环。

13位模式:应选择MUX通道,设置同步位,并在向ADC12048单次写入时发出启动命令。同步管脚或RD管脚上的上升沿将迫使RDY信号升高。建议使用从ADC12048(而不是同步信号的上升沿)读取的动作来提升RDY信号。这将确保在下一个转换周期的获取期间读取转换结果,从而在adc12048执行转换时消除对其的读取。在adc12048转换时访问它所产生的噪声可能会降低转换结果。在同步模式下,只有同步信号的上升沿将开始转换周期。转换周期结束时,RDY信号将变低。采集时间由同步信号控制。采集周期开始于包含mux信道信息的写入周期之后。选定的mux信道在wr信号的上升沿之后采样,直到同步脉冲的上升沿,此时信号将被保持并开始转换。如果需要,此时可以将新的mux信道和/或操作命令写入配置寄存器。使用配置寄存器中的START命令,从ADC12048读取将把存储在数据寄存器中的整个转换结果放在数据总线上,读取脉冲的上升沿将迫使RDY信号升高。选定的mux通道将被采样,直到同步管脚上出现上升沿,此时采样信号将被保持并开始转换循环。

备用命令

8位模式:写入ADC12048的第一个字节应在配置寄存器(位B7)中设置HB位。第二个字节必须发出备用命令(位b11、b10、b9=0、0、0)。

13位模式:必须以单次写入(位b11、b10、b9=0、0、0)的方式向ADC12048发出备用命令。

重置

reset命令将ADC12048置于就绪状态,并强制RDY信号处于低位。复位命令可用于在ADC12048执行转换、完全校准或自动调零循环时中断ADC12048。它还可用于使ADC12048脱离待机模式。

模拟应用信息

参考电压

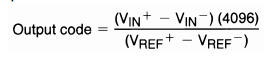

ADC12048有两个参考输入,VREF+和VREF-。它们定义了模拟输入信号的零到满量程范围,其中存在4095个正和4096个负码。参考输入可以连接到整个电源电压范围(VREF-=AgNd,VREF+=VA+),或者当需要其他输入范围时,它们可以连接到不同的电压。ADC12048的参考输入具有瞬时电容开关电流。驱动VREF+和VREF-的电压源必须具有非常低的输出阻抗和噪声,并且必须充分旁路。图48中的电路是一个非常稳定的参考源的例子。

ADC12048可用于比率测量或绝对参考应用。在比率测量系统中,模拟输入电压与模数转换器参考电压成正比。由于模拟输入电压随adc基准的变化而变化,该技术放宽了系统基准要求。通过将VREF+引脚连接到VA+和VREF-引脚连接到AGND,系统电源可以用作参考电压。对于绝对精度,当模拟输入电压在非常特定的电压限制之间变化时,可以将时间和温度稳定的电压源连接到参考输入。通常,参考电压的大小需要对零参考电压引起的满标度误差进行初始调整。

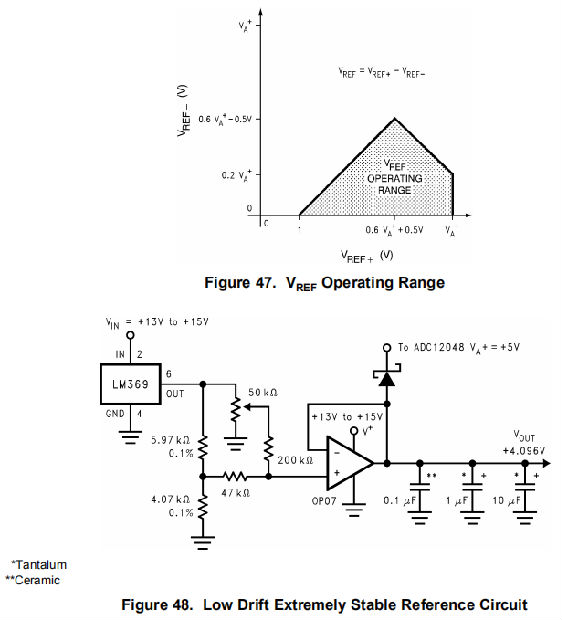

参考电压输入不是完全差分的。如果(VREF+–(VREF-)低于1V,ADC12048将不会生成正确的转换。图47显示了VREF+和VREF-)之间的允许关系。

输出数字代码与模拟输入电压

ADC12048的全差分12位+符号ADC产生一个2的补码输出,该输出通过使用下面所示的等式找到:

将结果舍入到-4096和4095之间最接近的整数值。

输入电流

在采集窗口(tacqsynout)开始时,充电电流(由于电容开关)流过模拟输入引脚(ch0–ch7、adcin+和adcin-,以及com)。该输入电流的峰值将取决于所施加输入电压的振幅和频率、源阻抗和输入接通电阻。当MUXOUT+连接到ADCIN+且MUXOUT-连接到ADCIN-时,通电电阻通常为2800Ω。绕过MUX,仅使用ADCIN+和ADCIN-输入,通电电阻通常为2500Ω。

对于低阻抗电压源(12 MHz工作时小于1000Ω),输入充电电流将衰减到在默认采样和保持(s/h)采集时间(9个时钟周期)结束前不会产生任何转换误差的值。对于较高的源阻抗(12MHz工作时大于1000Ω),应增加S/H采集时间,以使充电电流稳定在规定的范围内。在异步模式下,采集时间可以增加到15、47或79个时钟周期。如果需要不同的采集时间,可以使用同步模式来完全控制采集时间。

输入旁路电容

外部电容器(0.01μf–0.1μf)可连接在模拟输入引脚(CH0–CH7)和模拟接地之间,以过滤与长引线相关的非导电拾波引起的任何噪声。

电源注意事项

高分辨率adc的电源去耦和旁路是一项重要的设计任务。VA+(模拟电源)或VD+(数字电源)上的噪声峰值可能会导致转换错误。adc中使用的模拟比较器将对电源噪声作出响应,并将做出错误的转换决定。ADC对自动调零或线性校准周期中出现的电源峰值特别敏感。

ADC12048设计为在单个+5V电源上运行。电路模拟和数字部分的单独电源和接地引脚允许单独的外部旁路。为了尽量减少电源噪声和纹波,应在电源引脚及其相关接地之间直接放置足够的旁路电容器。两个电源引脚应连接到同一个电源。在具有独立模拟和数字电源的系统中,ADC应通过模拟电源供电。建议至少并联10μf钽电解电容器和0.1μf单片陶瓷电容器,以绕过每个电源。这些电容器的关键考虑因素是具有低串联电阻和电感。电容器应尽可能靠近电源和接地插脚,较小的电容器应靠近设备。电容器还应具有尽可能短的引线,以最小化串联引线电感。表面贴装芯片电容器在这方面是最佳的,应尽可能使用。

当电源调节器不在板上时,应在电源入口点放置足够的旁路(高值电解电容器)。电容器的值取决于PC板上电路的总供电电流。所有的供电电流应由电容器供电,而不是从外部供电线路引出,同时外部供电以稳定的速率向电容器充电。

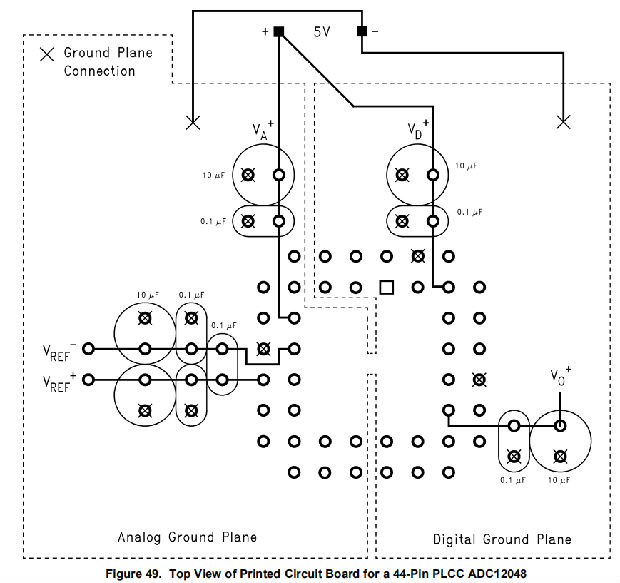

adc有两个vd+和dgnd管脚。建议使用0.1μf加10μf电容器将这些vd+管脚中的每一个单独旁路至dgnd。图49的布局图显示了电源旁路电容器的建议位置。

PC板布局和接地注意事项

为了从ADC12048获得最佳性能,印刷电路板应具有单独的模拟和数字接地平面。使用两个接地平面的原因是为了防止数字和模拟接地电流共享同一路径,直到它们达到一个非常低阻抗的电源点。这将防止噪声数字开关电流注入模拟地面。

图49说明了一个良好的布局为地面,电源和参考输入旁路电容器。它显示了使用44针PLCC插座和通孔组件的布局。pqfp包也应该使用类似的方法。

模拟接地平面应包括模拟管脚和任何其他模拟元件(如参考电路、输入放大器、信号调节电路和模拟信号轨迹)下的区域。

数字接地平面应包括数字电路和ADC12048的数字输入/输出引脚下的区域。拥有一个连续的数字地面下的数据和时钟轨迹是非常重要的。这减少了这些线路上的过冲/过冲和高频振铃,这些线路可以通过杂散电容与模拟电路部分进行电容耦合。

ADC12048中的agnd和dgnd没有内部连接在一起。它们应该在芯片的PC板上连接在一起。这将为adc内部模拟和数字部分之间交换的信号提供最短的返回路径。

在pc板上有电源板层也是一个很好的设计实践。这将改善电源旁路(电源和接地平面层之间的有效分布电容)和电源线上的电压降。然而,动力飞机并不像地面飞机那样具有令人满意的性能。如果使用动力平面,则应将其分为两个平面,并且区域和连接应遵循与地平面相同的指南。每个电源平面应布置在其相关接地平面上,避免电源平面和不同类型接地平面之间的任何重叠。不使用电源板时,建议从低阻抗电源点(调节器输出或PC板的电源入口点)为VA+和VD+引脚使用单独的电源线。这将有助于确保噪声数字电源不会损坏模拟电源。

测量交流输入信号时,模拟输入/输出线和参考线(CH0–CH7,muxout±,ADC in±,vref±)之间的任何串扰都应最小化。通过减少线路之间的杂散电容,串扰最小化。这可以通过增加记录道之间的间隙、保持记录道尽可能短、通过将记录道放置在agnd平面的不同侧面或在它们之间运行agnd记录道来实现。

图49还显示了参考输入旁路电容器。这里的参考输入被认为是差分的。通过在vref+和vref-之间具有0.1μf电容器,以及通过以与所述电源引脚类似的方式旁路,性能得到改善。当使用单端基准时,VREF-连接到AGND,VREF+和VREF-之间仅使用两个电容器(0.1μf+10μf)。建议直接将这些电容器的agnd侧连接到vref-而不是将vref-和电容器的接地侧分别连接到接地平面。这在使用表面安装技术时提供了显著降低的踏板连接。