功能特色

逻辑上为16kbit铁电随机存取存储器(F-RAM)按2K×8组织高耐久性100万亿(1014)读/写151年数据保留期(见数据保留和耐久表)nodelay8482;写入先进的高可靠性铁电工艺快速2线串行接口(I2C)高达1兆赫的频率串行(I2C)EEPROM的直接硬件替换支持100 kHz和400 kHz的传统计时低功耗100μA 100 kHz时的有功电流3μA(典型)备用电流电压运行:VDD=2.7 V至3.65 V工业温度:–40°C至+85°C■包装8针小外形集成电路(SOIC)封装8针双扁平无引线(DFN)封装符合有害物质限制(RoHS)

功能描述

fm24cl16b是一个16kbit的非易失性存储器,采用先进的铁电工艺。铁电随机存取存储器或f-ram是非易失性的,执行读写操作。类似它提供了151年的可靠数据保留在消除复杂性、开销和系统级别的同时eeprom等非易失性引起的可靠性问题。与eeprom不同,fm24cl16b在公车速度。不会造成写入延迟。数据写入每个字节成功后的内存数组转移到设备上。下一个公交循环可以开始了不需要数据轮询。此外,该产品还提供与其他非易失性相比,具有相当大的写持久性回忆。此外,f-ram在写操作期间显示出更低的功耗因为写入操作不需要内部写入电路的电源电压升高。这个FM24CL16B能够支持1014个读/写周期,或比eeprom多1亿倍的写入周期。这些功能使FM24CL16B成为非易失性的理想选择需要频繁或快速写入的内存应用程序。示例包括数据日志记录,其中对于要求工业控制的地方来说,周期可能是至关重要的EEPROM的长写时间会导致数据丢失。这个功能组合允许更频繁的数据写入减少系统开销。FM24CL16B为串行用户提供了实质性的好处(I2C)EEPROM作为硬件替换。装置在工业温度范围内保证规格温度范围为-40℃至+85℃。

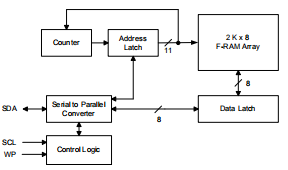

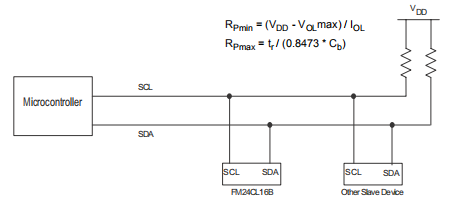

概述:FM24CL16B是一个串行F-RAM存储器。内存数组逻辑组织为2048×8位,并使用工业标准I2C接口。的功能操作F-RAM类似于串行(I2C)EEPROM。主要区别在FM24CL16B和串行(I2C)EEPROM之间同样的引脚分配是f-ram优越的写性能,高持久性,低功耗。存储器结构当访问FM24CL16B时,用户地址为2K每个8个数据位的位置。这八个数据位移位连续进出。使用I2C访问地址协议,包括一个从机地址(用于区分其他非内存设备)、行地址和段地址。行地址由8位组成,指定256排。3位段地址指定8个段中的一个在每一行中。11位的完整地址指定每个字节地址唯一。存储器操作的访问时间基本上为零,超过串行协议所需的时间。也就是说,存储器以I2C总线的速度读取或写入。不像串行(I2C)EEPROM,无需轮询设备就绪状态,因为写入以总线速度发生。到…的时候一个新的总线事务可以转移到设备中,写入操作完成。这在接口部分。注意,FM24CL16B不包含电源管理除简单的内部通电复位外的电路。它是用户确保VDD在数据表内的责任防止错误操作的公差。I2C接口FM24CL16B采用双向I2C总线协议很少的针或板空间。图展示了一个典型的系统基于单片机的fm24cl16b配置系统。工业标准I2C总线为许多用户所熟悉但在这一节中有描述。按照惯例,向总线发送数据的任何设备当此数据的目标设备是接收器时的发射器。控制总线的设备是主设备。主要负责为所有操作生成时钟信号。总线上任何被控制的设备都是从机。这个FM24CL16B始终是从设备。总线协议由sda和SCL信号。有四个条件包括开始,停止,数据位或确认。

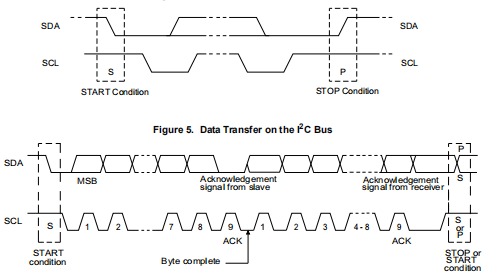

停止条件(P)当总线主驱动器驱动sda时,指示停止状态。SCL信号高时从低到高。所有操作使用FM24CL16B应以停止状态结束。如果操作正在进行当断言停止时将被中止。为了断言停止条件。启动条件当总线主驱动器驱动sda时,指示启动条件SCL信号高时从高到低。所有命令前面应该有一个开始条件。手术进程可以通过在任何时间。使用启动条件中止操作将准备就绪新操作的FM24CL16B。如果在运行期间,电源低于规定值VDD最小值,系统应在去做另一个。

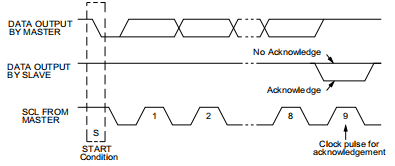

数据/地址传输所有数据传输(包括地址)在SCL信号高。除非在上述两种情况下以上,当SCL高时,SDA信号不应改变。确认/不确认确认发生在第8个数据位在任何交易中转移。在此状态下,发射器应释放SDA总线以允许接收器驱动它。这个接收器驱动SDA信号低,以确认收到字节。如果接收器未将SDA驱动低,则是“否”确认,操作被中止。接受者会因为两个不同的原因而不承认。首先是字节传输失败。在这种情况下,不承认停止当前操作,以便设备可以再次致辞。这允许在通信错误事件。第二,也是最常见的,接收者不承认故意结束手术。例如,在读取期间操作时,FM24CL16B将继续将数据放在总线只要接收器发送确认(和时钟)。当读取操作完成且不需要更多数据时,接收器不能确认最后一个字节。如果接收器确认最后一个字节,这将导致FM24CL16B尝试在下一个时钟上驱动总线,而主机是发送新命令,如stop。

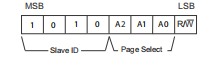

从设备地址fm24cl16b在启动后期望的第一个字节条件是从机地址。如图所示,从机地址包含设备类型,内存页为已访问,以及一个指定事务是读取还是一封信。位7-4是设备类型,对于FM24CL16B。这些位允许其他函数类型驻留在相同地址范围内的I2C总线。位3-1是页面选择。它指定256字节的内存块,即针对当前操作。位0是读/写位(右转)。R/W='1'表示读取操作,R/W='0'表示写入操作。

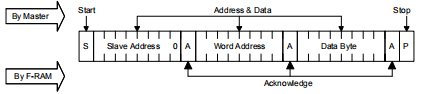

寻址概述(字地址)在FM24CL16B(作为接收器)确认从机之后地址,主机可以在总线上放置写操作。单词address是地址与3位页面组合选择指定正是要写入的字节。完整的11位地址是内部锁定。读取操作不会出现字地址,尽管3位页面选择在内部锁定。总是阅读使用地址锁存器内部的低8位。也就是说,读取总是从前一个地址之后的地址开始进入。可以通过执行写操作加载随机读取地址操作说明如下。在传输每个数据字节之后,就在确认,FM24CL16B递增内部地址门闩。这允许使用没有附加地址。在最后一个地址(7ffh)之后到达时,地址闩锁将滚动到000小时。没有限制一次读取可以访问的字节数或写操作。数据传输地址字节传输后,数据传输在总线主机和FM24CL16B之间可以开始。为了一个读取操作FM24CL16B将在总线上放置8个数据位然后等待确认。如果确认后,FM24CL16B将传送下一个顺序字节。如果未发送确认,则FM24CL16B将结束读取操作。对于写操作,FM24CL16B将接受来自主机的8个数据位,然后发送。所有数据传输发生msb(最高有效位)第一。存储器操作FM24CL16B的设计运行方式非常相似其他I2C接口存储器产品。主要区别由于F-RAM具有更高的性能写入能力技术。这些改进导致了一些差异在FM24CL16B和类似配置的EEPROM之间写的时候。写入和读取的完整操作。

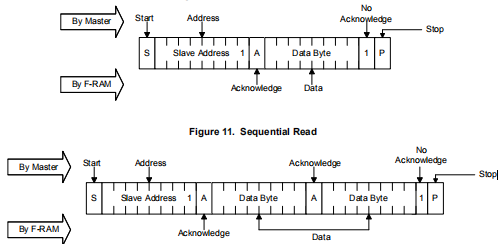

读取操作有两种基本类型的读取操作。它们是最新的地址读取和选择性地址读取。在当前地址中读取,FM24CL16B使用内部地址锁存器提供较低的8个地址位。在选择性读取中,用户执行将这些较低地址位设置为特定值的过程。当前地址和顺序读取如上所述,FM24CL16B使用内部锁存器为读取操作提供较低的8位地址。电流地址读取使用地址锁存器中的现有值作为读取操作的起始位置。系统从紧接着上次操作的地址。要执行当前地址读取,总线主设备提供LSB设置为“1”的从属地址。这表示读取请求操作。从机中的三页选择位地址指定用于读取的内存块操作。在接收到完整的从机地址之后,FM24CL16B将开始从当前地址移出数据下一个时钟。当前地址是从机的3位地址与内部的8位相结合地址锁存器。从当前地址开始,总线主机可以读取任何字节数。因此,顺序读取只是一个电流通过多字节传输读取地址。在每个字节之后内部地址计数器将递增。注意每次总线主服务器确认一个字节时指示FM24CL16B应在下一个顺序字节。有四种方法可以正确终止读取操作。如果未能正确终止读取,很可能会创建一个总线当FM24CL16B试图读取附加的数据到总线上。四种有效方法是:1.总线主控在9点钟发出一个禁止应答在第10个时钟周期内循环和停止。如图所示下面的图表。这是首选。2.总线主控在9点钟发出一个禁止应答在10号开始循环。3.巴士主控在第九个时钟周期内发出停止指令。4.总线主控在第9个时钟周期发出启动。如果内部地址达到7ffh,它将环绕到000h在下一个读取周期。下面的图显示了当前地址读取的正确操作。

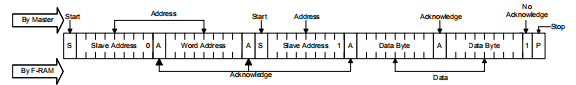

选择性(随机)读取有一种简单的技术允许用户随机选择地址位置作为读取操作的起点。这个包括使用写操作的前两个字节设置后跟后续读取操作的内部地址。为了执行选择性读取,总线主设备发送从设备LSB(R/W)设置为0的地址。指定写入操作。根据写协议,总线主机发送加载到内部地址锁存器。在FM24CL16B确认单词后地址,总线主机发出启动条件。这将同时中止写入操作并允许读取将从机地址lsb设置为“1”时发出的命令。操作现在是读取当前地址。

耐力FM24C16B在内部运行,具有读取和恢复功能机制。因此,耐久性循环适用于读或写循环。内存结构基于行和列的数组。每次读或写访问都会导致一整排的耐力循环。在FM24C16B中,一行是64有点宽。每8字节的边界标志着一个新的划船。通过频繁地确保访问的数据位于不同的行中。不管怎样,弗拉姆在1MHz I2C下,读写耐久性实际上是无限的速度。即使每秒有3000次访问同一行,10年后,1万亿个耐力周期才会出现。