特点和优点

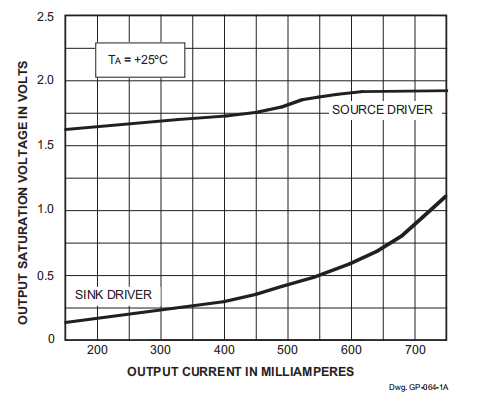

±750毫安,30伏输出额定值;Satlington®水槽驱动器;自动电流衰减模式检测/选择;3.0至5.5 V逻辑电源电压范围;混合、快速和慢速电流衰减模式;内部uvlo和热关机电路;交叉电流保护。

说明

A3967是一个完整的微步进电机驱动器与内置翻译。它设计用于在全、半、四、八阶模式下操作双极步进电机,输出驱动能力为30V和±750MA。a3967包括一个固定关闭时间的电流调节器,它能够在慢、快或混合电流衰减模式下工作。这种电流衰减控制方案可以降低电机的可听噪声,提高步进精度,降低功耗。

翻译是A3967易于实现的关键。通过简单地在步进输入端输入一个脉冲,电机将执行一个步进(完全、半、四分之一或八分之一取决于两个逻辑输入)。没有相序表、高频控制线或复杂的编程接口。a3967接口非常适合复杂μp不可用或负担过重的应用。

内部电路保护包括滞后热关机、欠压锁定(uvlo)和交叉过电流保护。不需要特殊的通电顺序。

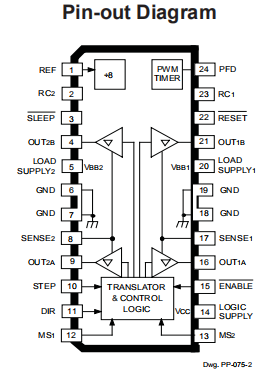

A3967采用24针SOIC,100%哑光镀锡引线框架,不含铅。四个引脚内部熔合,以增强散热。引脚处于接地电位,无需绝缘。

功能描述

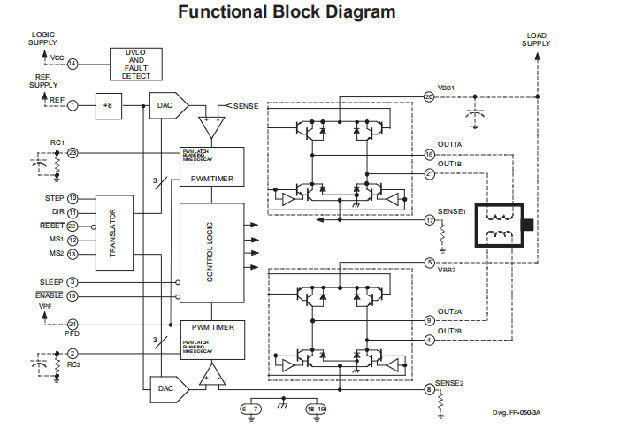

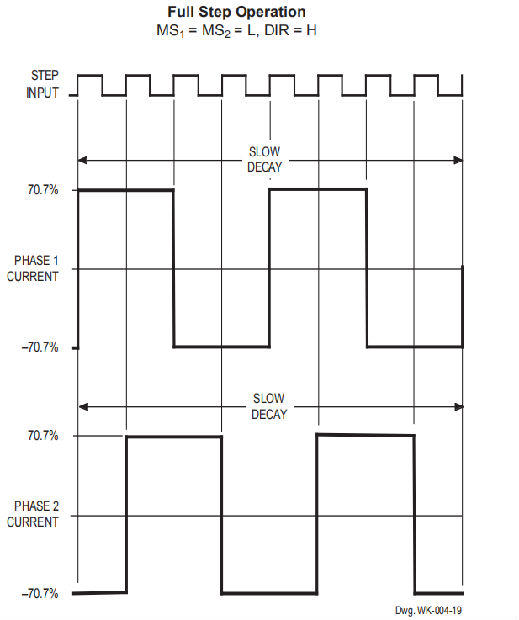

A3967是一个完整的微步进电机驱动器,内置翻译,操作简单,控制线最少。它被设计成在全步、半步、四步和八步模式下操作双极步进电机。两个输出全桥中的每一个电流都由固定时间脉冲宽度调制(pwm)控制电路调节。每个步骤的全桥电流由外部电流检测电阻器(RS)、参考电压(VREF)和由转换器输出控制的DACS输出电压的值设置。

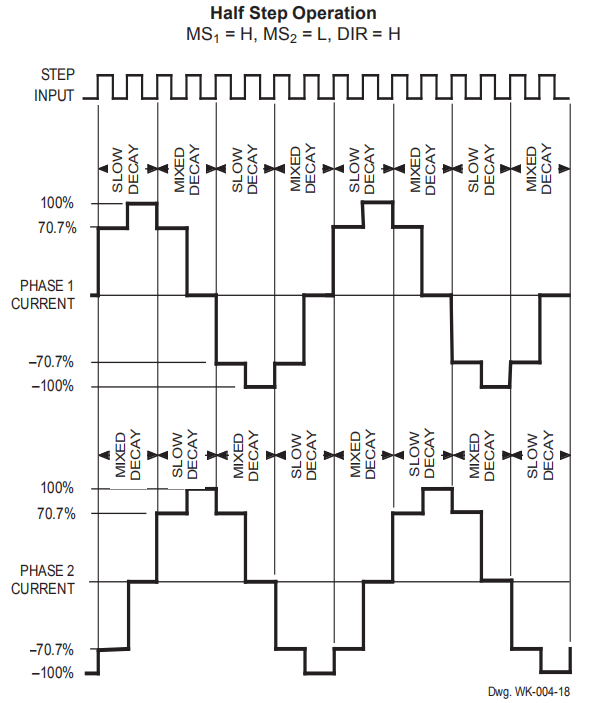

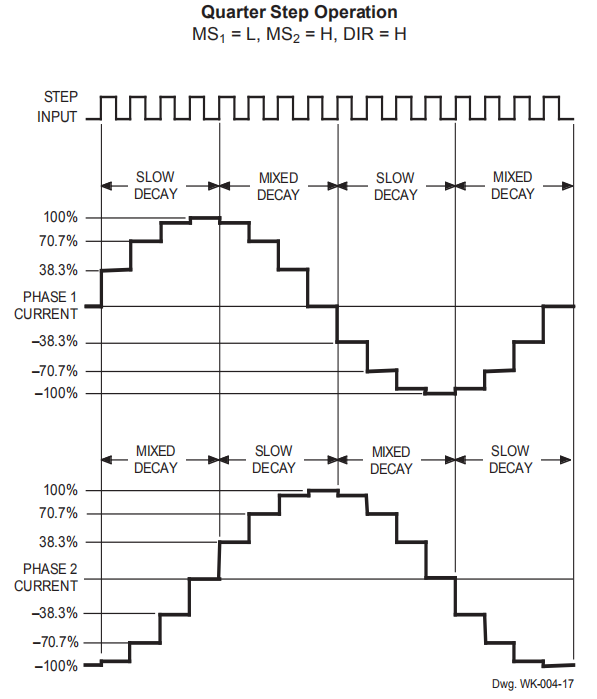

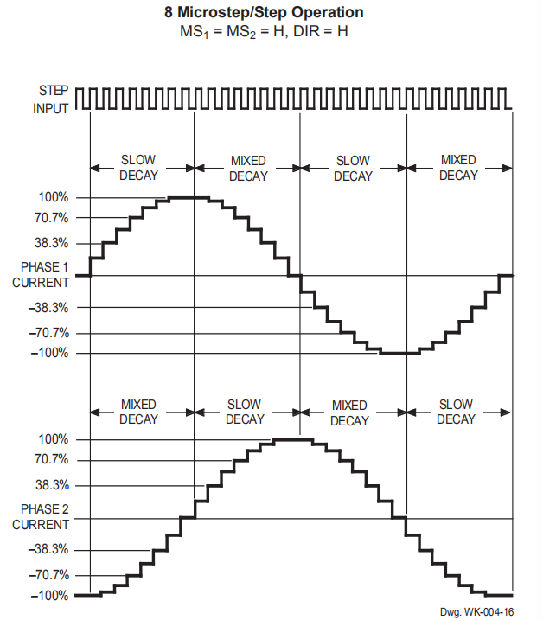

在通电或复位时,转换器将DAC和相电流极性设置为初始初始状态(见初始状态条件图),并将两相电流调节器设置为混合衰减模式。当阶跃输入上出现阶跃指令信号时,转换器自动将DAC排序到下一级(有关电流级顺序和电流极性,请参见表2)。微步分辨率由输入ms1和ms2设置,如表1所示。如果新的dac输出电平低于前一电平,则该全桥的衰减模式将由pfd输入设置(快速、慢速或混合衰减)。如果新的dac电平高于或等于前一电平,则该全桥的衰减模式将是慢衰减。这种自动电流衰减选择将通过减少由电机BEMF引起的电流波形失真来改善微步进性能。

复位输入(复位)。复位输入(激活低)将转换器设置为预定义的主状态(请参阅主状态条件图),并关闭所有输出。在复位输入变高之前,步骤输入被忽略。

步骤输入(步骤)。从低到高的转变步进输入使翻译器按顺序排列,并使马达前进一个增量。转换器控制DAC的输入和每个绕组的电流方向。增量的大小由输入ms1和ms2的状态决定(见表1)。

微步选择(ms1和ms2)。输入端子ms1和ms2根据表1选择微步格式。对这些输入的更改直到STEP命令生效(参见图)。

方向输入(DIR)。方向输入的状态将决定电机的旋转方向。

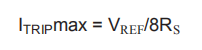

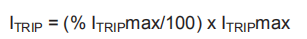

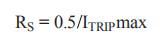

内部脉宽调制电流控制。每个全桥由一个固定的断开时间的pwm电流控制电路控制,该电路将负载电流限制在所需值(itrip)。最初,一对对角的源和汇输出被启用,电流流过电机绕组和RS。当电流检测电阻器上的电压等于DAC输出电压时,电流检测比较器重置PWM锁存器,关闭源驱动程序(慢衰减模式)或接收器和源驱动程序(快衰减模式或混合衰减模式)。限流的最大值是通过选择RS和VRF输入处的电压来实现的,其跨导函数近似为:

DAC输出以精确的步骤将VREF输出减少到电流感应比较器(每一步的%ITRIMPax见表2)。

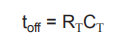

固定的休息时间。内部的脉宽调制电流控制电路使用一次触发来控制驱动器保持关闭的时间。一次关断时间toff取决于从rc定时端子到接地连接的外部电阻(rt)和电容(ct)的选择。关断时间,在CT值=470 pF到1500 pF和rT=12 KΩ到100 KΩ的范围内近似于:

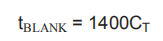

钢筋混凝土下料。除了固定的关闭时间pwm控制电路中,ct元件设置比较器的消隐时间。当内部电流控制电路切换输出时,此功能将使电流感应比较器的输出为空白。比较器输出被屏蔽,以防止由于钳位二极管的反向恢复电流和/或与负载电容有关的开关瞬态而导致的假过电流检测。空白时间可以近似为:

启用输入(启用)。此低输入激活所有输出。当逻辑高时,输出被禁用。转换器的输入(步骤、方向、ms1、ms2)都是活动的,与启用输入状态无关。

关闭。如果发生故障(结温过高),设备的输出将被禁用,直到故障条件消除。通电时,如果VCC低,欠压锁定(UVLO)电路将禁用驱动器并将转换器重置为初始状态。

快速衰减输入百分比(pfd)。当阶跃输入信号从上一步指令较低的输出电流时,它根据pfd输入的电压电平将输出电流衰减切换为慢、快或混合衰减。如果pfd输入端的电压大于0.6vcc,则选择慢衰减模式。如果pfd输入上的电压小于0.21vcc,则选择快速衰减模式。混合衰变介于这两个水平之间。

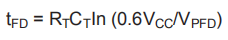

混合衰变操作。如果pfd输入端的电压介于0.6vcc和0.21vcc之间,则电桥将根据步进顺序以混合衰减模式工作(参见图)。当达到触发点时,装置将进入快速衰减模式,直到RC端子上的电压衰减到施加到PFD端子上的电压。设备在快速衰减中运行的时间近似为:

在这个快速衰减部分tfd之后,设备将在固定的关闭时间段的剩余部分切换到慢速衰减模式。

睡眠模式(睡眠)。一种有效的低控制输入,用于在不使用时使功耗最小化。这会使包括输出在内的大部分内部电路失效。逻辑高允许设备在初始位置正常运行和启动。

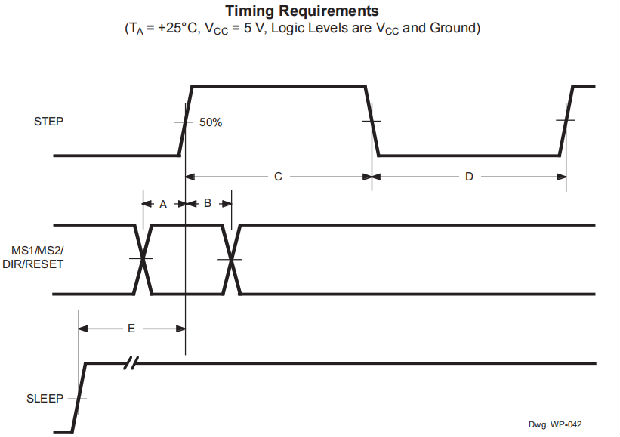

a、最小命令激活时间阶跃脉冲(数据设置时间)之前…200纳秒

b、最小命令激活时间步进脉冲后(数据保持时间)………200纳秒

c、最小阶跃脉冲宽度…………1.0μs

d、最小步进低时间…………1.0μs

E、最大唤醒时间………… 1.0 ms

布局。印刷线路板应使用重型接地板。为了获得最佳的电气和热性能,驱动器应该直接焊接到电路板上。

负载电源端子vbb应与放置在尽可能靠近装置的电解电容器(建议大于47μf)分离。

为了避免由于高dv/dt开关瞬态的电容耦合而产生的问题,将电桥输出轨迹从敏感的逻辑输入轨迹中移开。始终以低源阻抗驱动逻辑输入以提高抗噪性。建议使用靠近驾驶员的星型接地系统。接地。

24线SOIC具有模拟接地和电源接地,电源接地内部连接到封装的电源卡舌(导线6、7、18和19)。

电流感应。为了最大限度地减少由地面跟踪红外下降引起的对输出电流水平的不精确感测,电流感测电阻器(RS)应该有一个独立的接地回路,返回到设备的星形接地。这条路应该尽可能短。对于低值感测电阻器,印制电路板感测电阻器的迹线中的红外压降是显著的,应予以考虑。应避免使用插座,因为插座的接触电阻会导致RS的变化。Allegro Microsystems建议:

热保护。通常,当结温达到165°C时,电路会关闭所有驱动器。其目的仅在于保护装置不受过度连接温度导致的故障影响,不应意味着允许输出短路。热关断具有约15°C的滞后现象。

混合衰减模式由快速衰减电压百分比(vpfd)控制。如果pfd输入端的电压大于0.6vcc,则选择慢衰减模式。如果pfd输入上的电压小于0.21vcc,则选择快速衰减模式。混合衰变介于这两个水平之间。

混合衰减模式由快速衰减电压百分比(vpfd)控制。如果pfd输入端的电压大于0.6vcc,则选择慢衰减模式。如果pfd输入上的电压小于0.21vcc,则选择快速衰减模式。混合衰变介于这两个水平之间。

混合衰减模式由快速衰减电压百分比(vpfd)控制。如果pfd输入端的电压大于0.6vcc,则选择慢衰减模式。如果pfd输入上的电压小于0.21vcc,则选择快速衰减模式。混合衰变介于这两个水平之间。