FDMF6823A点击型号即可查看芯片规格书

150点击型号即可查看芯片规格书

X7R点击型号即可查看芯片规格书

系统效率带最小振铃的干净开关波形大电流处理

特征

93%以上的峰值效率大电流处理:60A高性能PQFN铜夹包装三态5V脉冲宽度调制输入驱动器跳过模式SMOD(低侧门关闭)输入过热警告标志条件驱动输出禁用功能(解除引脚)内部上拉和下拉以防烟雾分别取消输入飞兆电力公司技术mosfet干净的电压波形和减少振铃飞兆同步场效应晶体管(集成肖特基二极管)低边mosfet技术集成自举肖特基二极管自适应射穿门驱动定时保护电压过低锁定(UVLO)优化开关频率,最高可达1MHz薄型SMD封装飞兆绿色包装和RoHS合规性基于英特尔4.0 DRMOS标准

说明

XS8482;DRMOS系列是Fairchild的下一代,完全优化,超紧凑,集成mosfet plus适用于大电流、高频、同步降压DC-DC应用的驱动器功率级解决方案。这个FDMF6823A集成了一个驱动芯片,双电源mosfet和自举肖特基二极管热增强,超紧凑6x6mm封装。通过一种集成的方法功率级根据驱动器和mosfet动态性能,系统电感,和功率mosfet rds(开)。XS™DRMOS使用Fairchild的高性能PowerTrench™mosfet技术,大大减少了交换机铃声,消除了大多数buck中对缓冲电路的需要转换器应用。一种减少死区和传播的驱动芯片延迟进一步提高了性能。热的警告功能警告潜在温度过高情况。FDMF6823A还包含一个跳过模式(SMOD)可提高轻载效率。这个FDMF6823A还为与广泛的pwm控制器兼容。应用 :高性能游戏主板紧凑型刀片服务器,V核和非V核DC-DC转换器台式计算机,V核和非V核DC-DC转换器工作站大电流DC-DC点负载转换器网络和电信微处理器电压调节器小型电压调节器模块

功能描述

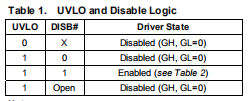

FDMF6823A是经过优化的驱动加场效应管模块对于同步buck变换器拓扑。单曲正确驱动所需的就是脉宽调制输入信号高边和低边mosfet。每个部分都是能够以高达1兆赫的速度行驶。vcin和disable(解散)vcin引脚由欠压锁定监控(uvlo)电路。当vcin高于~3.1v时,驱动器已启用。当vcin低于~2.7v时,驱动器禁用(gh,gl=0)。驱动程序也可以通过将DISB引脚拉低(DISB不管脉宽调制如何,保持gl和gh低输入状态。可以通过提升解散引脚电压高(解散>解散)。

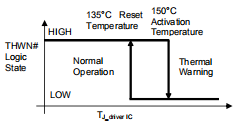

热警告标志(THWN)FDMF6823A提供热警告标志(thwn)警告温度过高的情况。这个热警告标志使用开放漏极输出激活温度(150°C)时拉至cgnd已到达。一旦温度降到复位位置,THWN输出返回高阻抗状态温度(135°C)。使用时,thwn输出需要一个上拉电阻器,可以连接到vcin。THWN不禁用DRMOS模块。

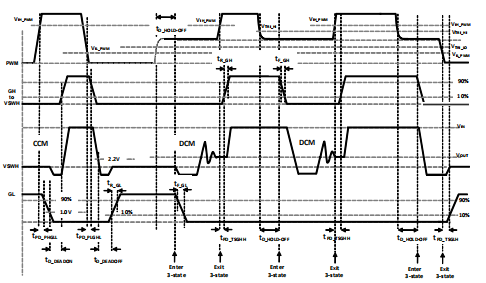

三态pwm输入FDMF6823A包含一个三态5V脉宽调制输入门驱动设计。三态门驱动器逻辑高电平和低电平,以及三态关闭窗口。当脉宽调制输入信号进入并保持在三态窗口内对于规定的等待时间(td_hold-off),gl和gh被拉低。这使门驱动器能够关闭从高侧和低侧的mosfet向下支撑例如相位脱落,这在多相电压调节器。退出三态条件当退出一个有效的三状态条件时,FDMF6823A遵循PWM输入命令。如果脉宽调制输入从三种状态变为低,低侧mosfet已打开。如果脉冲宽度调制输入来自三态到高,高边mosfet被转动打开。如图所示。FDMF6823A设计允许短的传播延迟时退出三态窗口(见电气特性)。低端驱动器低端驱动器(gl)设计用于驱动一个接地参考、低rds(on)、n沟道mosfet。偏见因为GL在VDRV和cgnd管脚。当驱动程序启用时,输出与pwm输入相差180°。什么时候?驱动程序被禁用(DISB=0V),GL保持在低位。高端驱动器高端驱动器(GH)设计用于驱动浮动n沟道mosfet。高压侧的偏压驱动程序由自举电源电路开发由内部肖特基二极管和外部肖特基二极管组成自举电容器(CBoot)。在启动过程中,保持VSWH在pgnd,允许cboot通过内部二极管。当pwm输入变高时,gh开始对高侧mosfet的栅极充电(q1)。

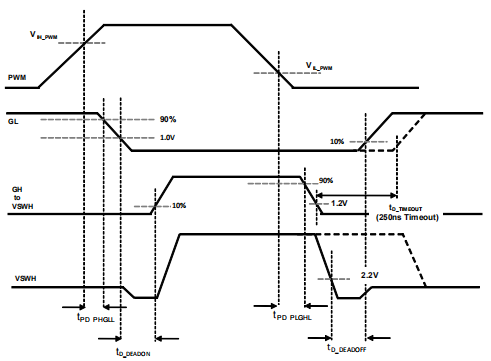

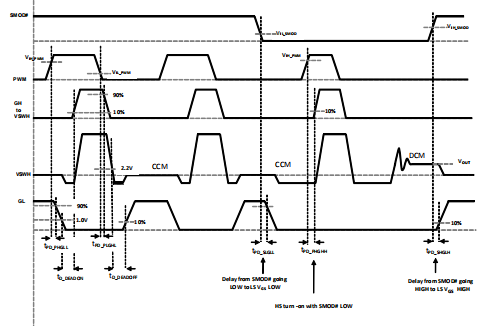

在这个转换过程中,电荷从cboot中移除送到第一季度门口。当q1打开时,vswh上升到vin,强制引导pin到vin+vboot,这为第一季度提供足够的VGS增强。完成切换周期q1通过将gh拉至甚高频。当VSWH降至pgnd.gh输出与pwm输入同相。这个当驾驶员被禁用或脉冲宽度调制信号保持在超过三个州的等待时间,td_-hold-off。自适应门驱动电路驱动芯片的先进设计确保了最小mosfet死区时间,同时消除潜在的穿透(交叉传导)电流。它能感觉到状态并自适应调整栅极驱动以确保它们不会同时进行。图提供相关的定时波形。防止从低到高转换期间的重叠(q2关闭到q1打开),自适应电路监视GL引脚处的电压。当脉冲宽度调制信号消失时高,传播延迟后q2开始关闭(tpd_phgll)。一旦GL引脚放电低于1.0V,q1在自适应延迟td_deadon之后开始打开。在高低过渡期间防止重叠(Q1关闭到Q2打开),自适应电路监视GH到相引脚对的电压。当脉冲宽度调制信号变低,Q1在传播延迟(tpd_plghl)。一旦电压通过GH至相位低于2.2V,Q2开始开启自适应延迟后td_死区。

跳过模式(smod)跳过模式功能允许更高的转换器在轻载条件下工作时的效率。什么时候?Smod被拉低,低边的mosfet栅极信号被禁用(保持低位),防止输出电容作为滤波电感电流尝试反向电流流-称为“二极管模拟模式。当SMOD引脚被拉高时,同步buck变换器工作在同步模式。此模式允许在低侧mosfet上选通。当SMOD引脚被拉低,低边mosfet被拉低关了门。如果SMOD引脚连接到脉宽调制控制器,控制器可以主动启用或禁用烟雾当控制器检测到轻载情况时输出电流感应。正常情况下,该引脚处于激活状态低。时序延迟见图。

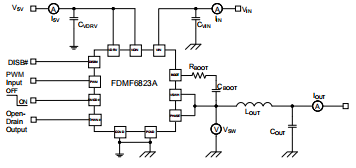

应用程序信息 :供电电容器选择对于电源输入(vcin),本地陶瓷旁路建议使用电容器来降低噪音和提供峰值电流。使用至少1μf x7r或x5r电容器。把这个电容器放在vcin引脚附近用过孔连接到GND平面。自举电路自举电路使用电荷存储电容器(cboot),如图所示。自举电容100nF X7R或X5R电容器通常足够。一个可能需要串联自举电阻器提高开关噪声抗扰度的应用。这个当在上面操作时,可能需要启动电阻器15vin,有效控制高端mosfet开关转换率和vshw超调。阿尔伯特从0.5到3.0Ω的值通常在减少VSWH超调。vcin滤波器VDRV销为高边和低边功率mosfet。在大多数情况下,它可以直接连接到vcin,为驱动程序的逻辑部分提供电源。为了附加的抗噪性,可以插入RC滤波器在vdrv和vcin引脚之间。推荐数值应为10Ω和1μF。

印刷电路板布局指南图提供了一个FDMF6823A和关键部件的布局。全部高电流路径,如vin,vswh,vout,接地铜线,应该是短而宽的电感和电阻。这有助于实现更稳定和均匀分布的电流具有增强的热辐射和系统性能。印刷电路板设计师的建议1.必须放置输入陶瓷旁路电容器靠近vin和pgnd管脚。这有助于减少大电流功率回路电感及输入功率mosfet引起的电流纹波切换操作。2.vswh铜记录道有两个用途。在除了高频电流路径从drmos封装到输出电感用作低侧mosfet的散热片drmos包。痕迹应该很短足够宽以呈现低阻抗路径在drmos和电感。短而宽的痕迹最大限度地减少电损耗和drmos温度上升。注意,vswh节点是一个高压高频开关节点噪声势。应注意尽量减少耦合到相邻记录道。因为这铜的痕迹用作较低mosfet的散热片,平衡利用最大面积改进drmos冷却同时保持可接受的噪音排放。3.输出电感应靠近FDMF6823A,以最小化由VSWH铜痕迹。还应注意电感耗散不会加热drmos。

4.输出中使用了PowerTrench®mosfet能够有效地减少由于快速切换。在大多数情况下,没有VSWH缓冲器必修的。如果使用减震器,则应放置减震器靠近VSWH和PGND引脚。选定的电阻器和电容器的尺寸必须适合功耗。5.vcin、vdrv和引导电容器应尽可能靠近vcin和cgnd,vdrv到cgnd,引导到相位管脚对到确保电源清洁稳定。布线宽度和长度也应该考虑。6.包括从相位引脚到vswh引脚的轨迹以提高噪声裕度。把这个痕迹保持在可能的。7.布局应该包含插入启动之间的小值串联启动电阻器电容器和保护针。启动循环大小,包括rboot和cboot,应该小到可能的。当工作在15vin以上,控制有效高侧mosfet开关转换率与vshw超过。RBOOT可改善噪音运行同步降压设计中可能有由于地面弹跳或高正极引起的噪音问题和负的VSWH铃声。插入靴子电阻降低了drmos的效率。效率必须考虑与噪音的权衡。阿尔伯特从0.5Ω到3.0Ω的值通常在减少VSWH超调。8.vin和pgnd引脚处理大电流频率分量大于100兆赫。如果可能的话,这些插脚应该连接直接到车辆识别号和登上地面飞机。使用与这些管脚串联的散热痕迹是不鼓励,因为这会增加功率的电感路径。这增加了串联电感vin或pgnd管脚降低系统抗噪性通过增加正向和负向vswh振铃。

9.接地垫和PGND引脚应连接到多通孔稳定的gnd铜平面接地。接地不良会产生噪音cgnd与pgnd.这可能导致闸门的错误操作司机和mosfets。10.在引导销处振铃最有效由引导电容器的紧密位置控制。不要向pgnd添加额外的引导电容器。这可能导致电流过大通过引导二极管。11.SMOD和DISB引脚内部薄弱分别为上拉和下拉电流源。这些引脚不应该有任何噪声滤波器电容器。不要浮动这些销,除非绝对必要。12.在车辆识别号和输出铜上使用多个过孔连接顶层、内层和底层的区域分配电流和热传导。做不要在vswh铜管上放置过多孔以避免附加寄生电感和噪声开关波形。只要效率和热性能可接受,仅限地点顶层有一个VSWH铜,不使用过孔在vswh铜缆上最小化交换节点寄生噪声。过孔应相对较大相当低的电感。关键高频部件,如RBOOT、CBOOT、RC缓冲电容器和旁路电容器;应位于与相应的DRMO模块引脚一样可能在PCB的顶层。如果这不是可行,可以从背面连接通过低电感过孔网络。